## UK Patent Application (19) GB (11) 2 078 061 A

- (21) Application No 8118081

- (22) Date of filing 12 Jun 1981

- (30) Priority data

- (31) 8003476

- (32) 16 Jun 1980

- (33) Netherlands (NL)

- (43) Application published 23 Dec 1981

- (51) INT CL<sup>3</sup> H03K 13/00

- (52) Domestic classification **H4P** DBB

- (56) Documents cited

None

- (58) Field of search

- (71) Applicants

N.V. Philips'

Gloeilampenfabrieken,

Pieter Zeemanstraat 6,

NL-5621 CT,

Eindhoven,

The Netherlands.

- (72) Inventors

Hubertus Franciscus

Maria Beckers

- (74) Agents

R.J. Boxall,

Mullard House,

Torrington Place,

London, WC1E 7HD.

- (54) Method of encoding data bits on a record carrier, device for carrying out the method, record carrier provided with an information structure and device for decoding the signal read from the record carrier

- (57) An encoding system in which starting from the Miller code a specific word type in the bit series is detected and two bits within said word type are encoded in a different manner in order to obtain an information signal without the d.c. component.

More specifically data bits of a first type are normally encoded by a level transition at a first predetermined point, e.g. the middle, of the relevant bit cell; data bits of a second type are normally encoded by a level transition at a second predetermined point, e.g. the beginning, of the relevant bit cell unless a data bit of the second type immediately follows a transition at the first predetermined point in the immediately preceding bit cell in which case the level transition is suppressed, wherein in the case of a word having one data bit of the second type followed by an even number of bits of the first type then the transitions at the first predetermined points in the bit cells corresponding to the first and second data bits of the first type are suppressed and a transition is provided at the second predetermined point of the bit cell associated with said second data bit.

Moreover, an encoding device, a record carrier provided with such an information signal and a read apparatus provided with a suitable decoding device are described.

FIG.1

FIG.4

FIG.5

FIG.6

FIG.7

| T <sub>0</sub>    | T_1                                      | 39                          |

|-------------------|------------------------------------------|-----------------------------|

| b <sub>0</sub> =1 | -                                        | 1                           |

| a <sub>0</sub> =1 | c-1=0<br>c <sub>-1=</sub> 1              | 0<br>Q <sub>-1</sub>        |

| c <sub>0</sub> =1 | a <sub>-1</sub> =0<br>a <sub>-1</sub> =1 | 0<br>\arraycal{\alpha}_{-1} |

FIG.8

## **SPECIFICATION**

Method of encoding data bits on a record carrier, device for carrying out the method, record carrier 5. provided with an information structure, and device for decoding the signal read from the record carrier

. The invention relates to a method of encoding a stream of data bits in consecutive bit cells in a 10 transmission system for recording and reproducing a recording signal of a record carrier, the bit stream being assumed to comprise consecutive words of a first and a second type and the data bits being of a first or a second type, the second type of words 15 comprising at least a sequence of one data bit of the second type followed by m ( $m \ge 0$ ) data bits of the first type, the data bits of the first type normally being encoded by a level transition in the middle of the relevant bit cell and data bits of the second type 20 normally being encoded by a transition at the beginning of the relevant bit cell, whilst each transition at the beginning of a bit cell followed by a transition in the middle of the immediately preceding bit cell is suppressed and words of the second 25 type with an even number m transitions of data bits of the first type are modified so as to reduce the d.c. component in the binary signal.

Such a method is known from United States Patent Specification 3,810,111.

30 Binary data comprise data bits which contain information in the form of either the one or the other of two types. The one type is sometimes represented as "logic one", as "true", as "yes" or as "+" and the other type is also represented as "logic zero", as

35 "not true", as "no" or as "-". In order to transfer these data bits via a transmission channel or to record them on a magnetic tape or an optical disk, the data bits are generally modified - a process which is known as channel coding. The purpose of

40 this channel coding is, for example, to obtain a maximum information density on the record carrier or to make the d.c. content of the encoded signal zero without enlarging the required bandwidth.

The encoded data bits are each accommodated in

45 an interval referred to as bit cell. This bit cell may be

a time interval (in the case of transmission *via* an

information channel) or a spatial interval (in the case

of recording on a tape or disk).

A known method of channel coding is the socalled Miller modulation. The code rules of this

modulation are: a "one" data is encoded as a level

transition in the middle of a bit cell, and a "zero"

data yields a transition at the beginning of the bit

cell, except in the case that a logic zero follows a

logic one. The Miller code, also known as "delay

modulation", is consequently a binary code in which

the location of the transitions between two levels

defines the meaning of the binary information.

For the purposes of the invention it is indifferent

60 which transition is associated with a "logic one" and

which transition with a "logic zero". Furthermore, it

is irrelevant where the transitions are exactly located

in the bit cell, provided that one transition is situated

comparatively early and one transition comparative65 ly late in the bit cell and that they can be disting-

uished unambiguously from each other. For simplicity all these possibilities will be referred to hereinafter as "in the middle of the bit cell" and "at the beginning of the bit cell".

Said Miller modulation has the drawback that the 70 signal which is obtained is not free of d.c. components. In order to mitigate this drawback it is proposed in said United Stated Patent Specification 3,810,111 to modify the Miller modulation. For this 75 purpose the stream of data bits is regarded as comprising sequences of words of two types, namely of type (a) 011 ... 110 (one zero, n ones and one zero, with  $n \ge 0$ ) and of type (b) 111 ... 111 (m ones). The words of type (b) and the words of type (a) if n is odd do not contribute to a d.c. component and are therefore encoded by the customary Miller method. Only the words of type (a) where n is even give rise to a d.c. component and are subject to a modified coding. In accordance with said United States Patent 85 Specification the modification consists in the ones of such a type-(a) word being divided into pairs and a transition being introduced for each pair at the beginning and the end of said pair. This ensures that a type-(a) word thus encoded no longer contains a 90 d.c. component.

The Miller code thus modified has a frequency spectrum which is d.c. free and whose content of very low frequencies is reduced to a certain extent in comparison with the frequency spectrum of the 95 Miller code.

When an optical disk is employed as record carrier, for example as an optically readable audio disk, this reduced content of low frequency components is of particular importance.

In this respect an optical record carrier is to be understood to mean a record carrier, disk tape etc., in which the information is recorded in an information track in an optically readable manner. This information track may then inter alia have a high-low structure or a black-white structure. For both structures reference will be made hereinafter to two possible levels in order to indicate that the respective structure is high or low and black or white.

In handling such a record carrier the surface may 110 for example become scratched, which when the record carrier is played may give rise to spurious low-frequency signals in the signal being read. If the content of low-frequency signals in the recording signal is very small, any spurious signals can be 115 extracted from the information signal by filtering. On the other hand, for reading an optical disk servosystems are employed which inter alia serve to ensure that the optical scanning spot remains focussed at the information surface and that said scanning 120 spot follows the information track. These servosystems employ control signals which are derived from signals obtained via the scanning spot. Said control signals have a frequency which is situated in a frequency band which coincides with the low-125 frequency portion of the frequency spectrum of the recording signal, so that strong signal components in this frequency range may give rise to spurious signals in the control signals.

It is the object of the invention to provide a method 130 of encoding data bits on a record carrier, which

yields a d.c. free recording signal with greatly reduced content of low-frequency components.

It is a further object of the invention to provide a method of encoding data bits on a record carrier, 5 yielding a record carrier with an information signal which can very simply be decoded during read-out.

According to the present invention there is provided a method of encoding a stream of data bits in consecutive bit cells in a transmission system for 10 recording and reproducing a recording signal on a record carrier, the bit stream being assumed to comprise consecutive words of a first and a second type and the data bits being of a first or a second type, the second type of words comprising at least a 15 sequence of one data bit of the second type followed by m ( $m \ge 0$ ) data bits of the first type, the method comprising normally encoding the data bits of the first type by a level transition in the middle as herein defined of the relevant bit cell, normally encoding 20 the data bits of the second type by a transition at the beginning (as herein defined) of the relevant bit cell, suppressing each transition at the beginning of a bit cell following a transition in the middle of the immediately preceding bit cell, and modifying words 25 of the second type with an even number m of transitions of data bits of the first type in order to reduce the d.c. component in the binary signal, said

associated with said second data bit. In one embodiment of the method in accordance with the invention the words of the first type

35 comprise a sequence of n ( $n \ge 1$ ) data bits of the second type and for words of the second type  $m \ge 1$ .

modifying comprising suppressing the transitions in

the middle of the bit cells corresponding to the first

providing a transition at the beginning of the bit cell

30 and the second data bit of the first type and

The method in accordance with the invention first of all ensures that a record carrier with an information signal thus encoded can be read by means of a very simple decoding device, whilst moreover the content of lower frequencies in the information signal is very small over a comparatively wide band.

The invention furthermore relates to a device for carrying out the method in accordance with the 45 invention, which device comprises a first input for receiving the binary data bits, a second input for receiving a clock signal which is in synchronism with the data bits, an output for supplying the encoded signal to a recorded device for a record carrier, 50 means for generating a signal transition in the middle of a clock interval in the case of a data bit of the first type, means for generating a signal transition at the beginning of a clock interval in the case of a data bit of the second type, means for suppressing 55 a transition at the beginning of a clock interval following a transition in the middle of the immediately preceding clock interval, means for detecting a word of the second type where m is even, means for suppressing the transitions in the middle of the clock 60 interval corresponding to said first and second bit of the first type in a word of said second type where mis even, and means for generating a transition at the beginning of the clock interval corresponding to said second bit of the first type in a word of the second

65 type where m is even.

The invention also relates to a record carrier provided with an information structure comprising sequences of bit cells, which bit cells each contain an information bit, whose information content is repre-70 sented by the presence or absence of a level transition in the middle or at the beginning of the bit cell. The record carrier in accordance with the invention is characterized in that the minimum distance between two consecutive level transitions 75 is equal to the length of one bit cell, that the maximum distance between two consecutive transitions is equal to the length of three bit cells, that a transition in the middle (as herein defined) of a bit cell represents a "logic one" and a transition at the 80 beginning (as herein defined) of a bit cell normally represents a "logic zero" unless the same level appears in two consecutive bit cells, in which case

the second one of said consecutive bit cells and the bit cell preceding it each represent a "logic one", and that the running integral of the information structure assumes a value of at most 2T, T being the length of the bit cells and that the level transitions which are spaced from each other by a maximum distance of three bit cells mark the beginning of the bit cell.

90 Finally, the invention also relates to an apparatus

Finally, the invention also relates to an apparatus for reading such a record carrier, the apparatus comprising detection means for detecting the pairs of modified bit cells and converting said two bit cells into two data bits of logic value one, and means for converting the other bit cells into data bits in accordance with the normal Miller decoding rules.

An embodiment of this reading apparatus, by means of which decoding is effected in a very simple manner, comprises means for converting a bit cell 100 with a transition in the middle (as herein defined) of the bit cell into a data bit of logic value "one", means for converting a bit cell with a transition at the end into a data bit with a logic value which is the inverse of that of the decoded preceding data bit if the 105 preceding data bit has no transition in the middle, and no transition at the end, and into a data bit of logic value "zero" if the preceding bit cell does exhibit one of said transitions, and means for converting a bit cell without transition in the middle 110 and at the end into a data bit with a logic value identical to that of the decoded preceding data bit if the preceding bit cell exhibits a transition at the end and into a data bit of the logic value "zero" if said preceding bit cell does not exhibit said transition at 115 the end.

The present invention will now be described, by way of example, with reference to the accompanying drawings, in which

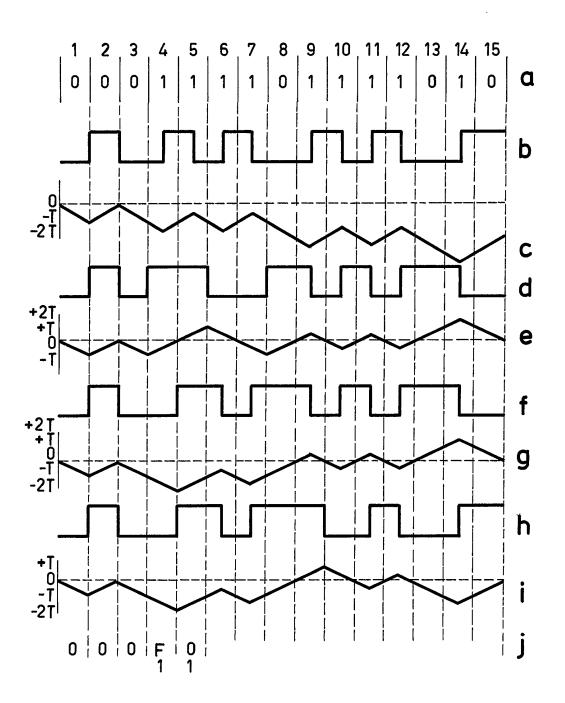

Figure 1 represents a number of signal wave-

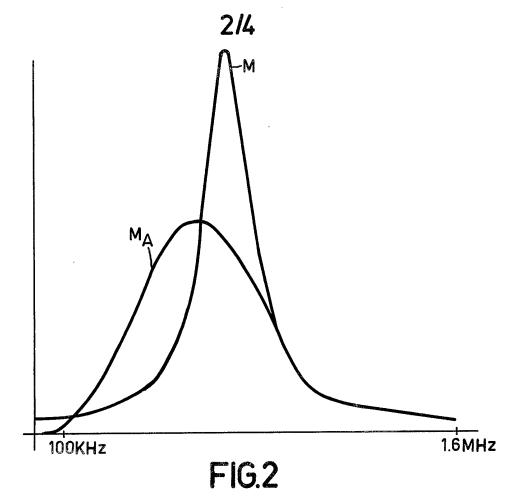

Figure 2 represents the frequency spectrum of two information signals,

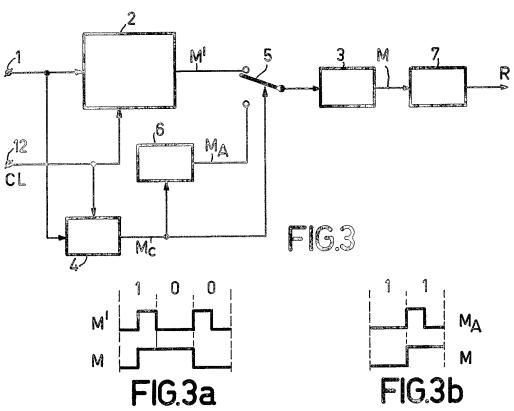

Figure 3 shows an embodiment of an encoding device in accordance with the invention, and Figures 3a and 3b are signal waveforms which serve to facilitate the understanding of the operation of the encoding device shown in Figure 3,

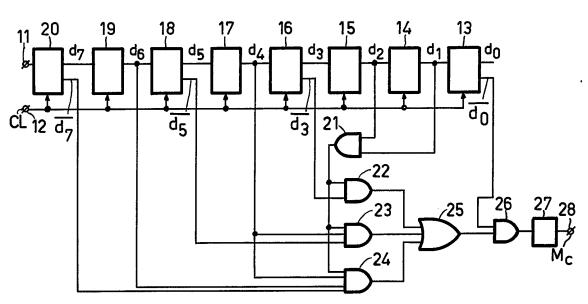

Figure 4 shows an example of detector employed in said encoding device,

130 Figure 5 by way of illustration shows an embodi-

ment of a record carrier in accordance with the invention,

Figure 6 is a sectional view of the record carrier shown in Figure 5,

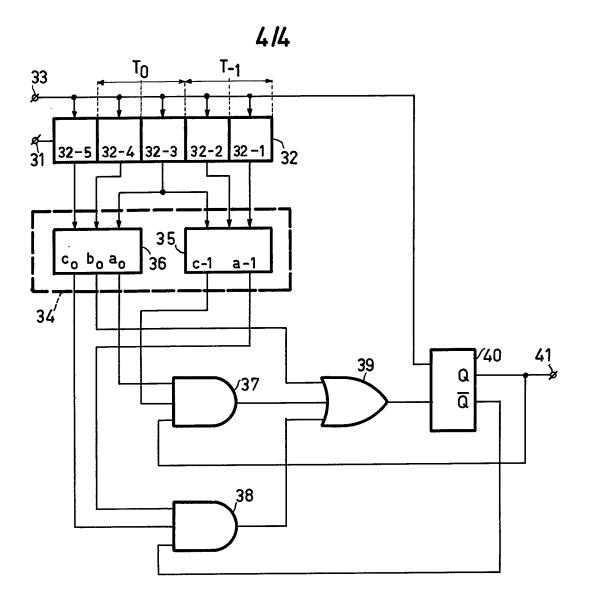

5 Figure 7 shows an embodiment of the decoding device in accordance with the invention, and

Figure 8 shows an associated decision table.

Figure 1a represents a plurality of consecutive bits cells 1,2,3 ... 15 in which binary information signals

can be stored, namely one bit per bit cell. By way of illustration a sequence "0" and "1" bits is shown.

Figure 1b by way of illustration shows the information signal which is obtained if the binary sequence of Figure 1a is encoded in accordance with the Miller code. An information bit of logic "1" content is then encoded as a signal transition in the middle of the relevant bit cell and an information bit of logic "0" content as a level transition at the beginning of the bit cell, except when said "0" bit immediately

The Miller code illustrated in Figure 1*b* is not d.c. free, that is it may contain a d.c. component. Figure 1*c* represents the so-called d.s.v. (digital sum variation) of the signal of Figure 1*b*, that is the running 25 integral of the area underneath the encoded data, the binary levels being +1 and -1 respectively. The length of each bit cell is T. It is evident from the Figure that in the case of the bit series shown a certain growing d.c. component is produced.

In order to eliminate this d.c. component United 30 States Patent Specification 3,810,111 has proposed a modification to the Miller coding. A stream of data bits is then regarded as comprising consecutive words of a type (a) and a type (b). A type-(a) word 35 comprises n ones bounded on both sides by a 0, hence 011 ... 110 ( $n \ge 0$ ) and a type-(b) word comprises a number of ones, i.e. 11 ... 11 ( $n \ge 1$ ). Both the type-(a) words where n is odd and the type-(b) words do not contribute to the d.c. compo-40 nent and are consequently encoded in accordance with the normal Miller code. Only type-(a) words where n is even give rise to a d.c. component. In order to eliminate this d.c. component a modification to the Miller code is adopted for this type of 45 word. Specifically, the series of ones in this type of word is divided into consecutive pairs and a transision is introduced at the beginning and end of each pair. For the bit series in accordance with Figure 1a

the following word organisation is valid: type-(a) n = 50 0 (bits 1 and 2); type (a) n = 4 (bits 3 to 8); type (b) n = 4 (bits 9 to 12); type (a) n = 1 (bits 13 to 15). This organisation results in an information signal in accordance with Figure 1d, the word comprising the bits 3 to 8 being modified as indicated. As is apparent from the d.s.v. of said information signal represented in Figure 1e, said information signal does not contain a d.c. component.

Apart from the absence of a d.c. component in the information signal recorded on a record carrier other factors play an important part with respect to the coding used. Especially for consumer applications it is desirable that the coding is such that in the read apparatus by means of which the record carrier is read the decoding circuit which is employed is as 65 simple as possible. Furthermore, especially in the

case of optical record carriers, it is not just the d.c. component itself which is of importance but, in view of cross-talk between the information signal and the servo-signals of comparatively low frequency for the various servo-systems employed for the optical read process and the influence of surface flaws on the quality of the information signal being read, it is of importance that the low-frequency content of said information signal is very small over a comparative-

For this purpose the invention proposes a different modification to the Miller code. Figures 1f and 1h represent two information signals as obtained in accordance with two possibilities of the Miller-code modification in accordance with the invention.

The information signal of Figure 1h is obtained by employing exactly the same division of the bit series as for the known Miller modification in accordance with said United States Patent Specification. However, a type-(a) word where n is even (bits 3 to 8) is modified in a different manner. Specifically, only the two first "1" bits (bits 4 and 5) of such a word are modified, said two bits being encoded with one transition at the boundary of the two bits. The remaining "1" bits (bits 6 and 7) of this type-(a) word are encoded in accordance with the normal Miller code, in contradistinction to the known modification. It follows from the d.s.v. represented in Figure 1g of

this information signal of Figure 1f that the d.c. 95 component is zero. Apart from the deviating modification a deviating division of the bit series into word types is used in the coding of the information signal illustrated in Figure 1h. For the word organization essentially only 100 one specific word type is detected namely a word comprising one zero, followed by an even number (n) of ones, that is 011 ... 11 (n even). Each word of this type is modified regardless of the position of said word within the bit series. In the bit series of 105 Figure 1a taken as an example this means that both the word comprising the bit cells 3 to 7 and the word comprising the bit cells 8 to 12 is modified, the latter in contradistinction to the code modifications in accordance with Figures 1d and 1f. The modification

in contradistinction to the code modifications in accordance with Figures 1d and 1f. The modification in itself is identical to that applied to the information signal of Figure 1f, that is the first two "1" bits (bits 4 and 5 and bits 9 and 10 respectively) are modified. It is apparent from Figure 1f that for the signal thus modified the d.c. component is also zero. In contradistinction to the known code modification the d.s.v. is not reduced to zero per word, but it is ensured that the mean d.s.v. remains zero.

The code modification in accordance with the invention first of all enables a very simple decoding 20 in the read apparatus. Specifically it is found possible to achieve a non-ambiguous decoding, for which only the information content of two consecutive bits must be detected, which will be explained hereinafter.

Moreover, it is found that the information signal obtained via the method in accordance with the invention has a very small content of comparatively low frequencies over a wide band. It appears in particular that the frequency spectrum of the information signal rises only very slowly from the

frequency 0 to approximately 100 kHz. Figure 2 by way of illustration represents the spectrum of the normal Miller code (M) measured at a bit frequency of 2Mbit/sec and the spectrum obtained with the coding in accordance with the invention ( $M_A$ ), which clearly shows the differences.

Figure 3 by way of example represents a block diagram of an encoding device for obtaining an information signal in accordance with Figure 1h. In 10 this case the word organisation only requires a detection of the occurrence of a word type 011 ... 11 (with an even number of ones).

The device comprises an input terminal 1, to which the binary bit series to be encoded is applied. Said 15 bit series is first of all applied to an encoding device 2, which is adapted to encode the applied bit series in accordance with the normal Miller code.

Via an input 12 the device 2 receies a clock signal CL of bit frequency for the bitwise shifting and 20 encoding of the applied bit series.

It is of course possible to employ any known Miller encoding circuit in order to form such an encoding device. By way of illustration reference is made to United States Patent Specification 3,108,261, which 25 describes said Miller code and a suitable encoding device.

Although it is not essential, it has been assumed for the encoding device in accordance with Figure 3 that the device 2 does not directly supply an 30 information signal encoded in accordance with the Miller code, but an information signal which does not yield said Miller-coded information signal until it has been processed by a NRZ (non-return-to-zero) encoding device 3. For this purpose the device 2 35 supplies a signal M', shown in Figure 3a, each bit being divided in two bit halves and the logic value in each bit half being indicative of the fact whether via the Miller coding a transition should exist in the information signal at the beginning of the relevant 40 bit half. Thus, a 1-bit does not always result in a 01-level structure of the relevant bit cell, but a "0" bit normally is a 10-level structure, except when said "0" bit is immediately preceded by a "1" bit, in which case a "00"-level structure of the two bit 45 halves is obtained. Figure 3a shows that after said signal M' has been subject to an NRZ operation, a signal M encoded in accordance with the Miller code is obtained.

In order to carry out the method in accordance

50 with the invention the device of Figure 3 comprises a

detector 4, which detects the beginning of a word

011 ... 11 with an even number of ones. However, it is

obvious that for the practical realization of such a

detector there are may possibilities. One of these

possibilities will be described later with reference to

Figure 4.

The detector 4 supplies a control signal M<sub>c</sub> to the switch 5 with a delay of one bit period after detection of the relevant word type, that is at the beginning of the first "1" bit of said word type, so that said switch is switched over from the output of the encoding device 2 to the output of the signal generator 6 for a time interval corresponding to two bit periods. The signal generator 6 is activated by the detector 4 simultaneously with the change-over of the switch 5

and then supplies a signal M<sub>A</sub>, as shown in Figure 3b within the two-bit time interval. During the first two "1" bits of the word-type to be modified the NRZ encoding device 3 consequently receives said signal 70 M<sub>A</sub>, resulting in the desired modified Miller code represented in Figure 3b. After said two-bit period the switch 5 is reset and the applied signal is again processed in accordance with the normal Miller code. The information signal M which is ultimately 75 obtained in this way is applied to a recording device 7, which records said signal in a suitable manner on a record carrier R, for example a magnetic tape, a magnetic disk or an optical disk.

Figure 4 by way of example shows a version of the detector 4 in the encoding device of Figure 3. The detector comprises an input terminal 11 to which the binary bit series is applied. Furthermore, the device comprises a number of flip-flops 13 to 20, which are connected in series and are clocked by a clock CL (input 12) having a frequency corresponding to the desired bit frequency. The flip-flops 13 to 20 consequently contain the signal contents of eight consecutive bits and function as cells of a shift register.

The eight flip-flops 13 to 20 shown essentially 90 form part of a larger number of series-connected flip-flops. Indeed, if each type-(a) word with an even number of ones is to be detected, this essentially demands the use of an infinitely long shift register, that is an infinite number of flip-flops. However, in practice the required length of the shift register is substantially smaller. For example, generally a synchronization word is inserted at equidistant positions in the bit series of the information signal. If this known synchronization word contains a "0" bit, this means that the series of consecutive "1" bits can 100 never be longer than the number of bits between said "0" bits of two consecutive synchronization words. Furthermore, the chance of a comparatively large series of consecutive "1" bits is very small, 105 depending on the type of information signal, for example in the case of an audio signal. This means that the length of the shift register, that is the number of flip-flops, can be reduced on purpose with the risk that in the case of very long words of 110 type (a) an incorrect modification may take place. If a comparatively short shift register is to be used, it is of course also possible to insert dummy "0" bits at equal distances in the binary bit series.

For simplicity of the Figure only eight flip-flops of 115 the complete row are shown. The outputs of said flip-flops represent the levels of eight consecutive bit cells, designated by the outputs do to do. In order to detect the occurrence of a type-(a) word with an even number of ones, the detector comprises a number of 120 logic gates, which are connected to the outputs of the flip-flops. The outputs d1 and d2 of the flip-flops 14 and 15 are connected to an AND-gate 21, whose output is coupled to three further AND-gates 22, 23 and 24. Furthermore, the AND-gate 22 is coupled to 125 the inverse output  $\overline{d}_3$  of the flip-flop 16, the ANDgate 23 to the output d4 of the flip-flop 17 and the inverse output  $\overline{d}_5$  of the flip-flop 18, and the ANDgate 24 is furthermore coupled to the outputs d4 of the flip-flop 17 and de of the flip-flop 19 and the 130 inverse output  $\overline{d_7}$  of the flip-flop 20. The outputs of

the AND-gates 22, 23 and 24 are connected to an OR-gate 25, whose output is connected to an AND-gate 26, which is furthermore coupled to the inverse output  $\overline{d}_0$  of the flip-flop 13. The output of the 5 AND-gate 26 drives a flip-flop 27, on whose output 28 the control signal  $M_c$  is available.

As is apparent from Figure 4, the output signal of the AND-gate 22 is indicative of the bit series d<sub>1</sub>d<sub>2</sub>d<sub>3</sub> = 110. In conjunction with the AND-function of the 10 gate 26 this yields a logic "1" for the flip-flop 27 upon the occurrence of the bit series d<sub>0</sub>d<sub>1</sub>d<sub>2</sub>d<sub>3</sub> = 0110, which is to be modified. Similarly, the AND-gate 26 in conjunction with the output signal of the AND-gate 23 yields a logic signal "1" upon the occurrence 15 of the bit series d<sub>0</sub> to d<sub>5</sub> = 011110 and in conjunction with the output signal of the AND-gate 24 upon the occurrence of the bit series 01111110.

Flip-flop 27 is adapted to supply a squarewave control signal M<sub>c</sub> having a duration equal to two bit 20 periods for switching over the switch 5 in Figure 3 and activating the modification signal generator 6 in Figure 3 when its input signal assumes a logic "1" level, delayed by one bit period, *i.e.* coinciding with the beginning of the first "1" bit of the type-(a) word 25 with an even number of ones.

It will be evident that if longer words of type (a) are to be detected the number of flip-flops 13 to 20 and the number of AND-gates 22 to 24 should be increased, which additional AND-gates should be coupled to the flip-flops of the shift register in accordance with the same pattern as for the AND-gates 22 to 24. As is evident from the Figure the AND-gates 22 to 24 perform the logic funtions  $d_1d_2\overline{d_3}$ ;  $d_1d_2d_4\overline{d_5}$  and  $d_1d_2d_4d_6\overline{d_7}$  respectively. Thus, 35 the next additional AND-gates should perform the logic functions  $d_1d_2d_4d_6d_8\overline{d_9}$ ;  $d_1d_2d_4d_6d_8d_{10}\overline{d_{11}}$  etc.

The method of coding in accordance with the invention is by no means limited to the use of the encoding decive as shown in Figures 3 and 4. On the basis of the coding rules defined in the coding it is of course possible to realize a multiplicity of logic circuits which in response to an applied bit series ultimately yield an information signal which is encoded in the desired manner. For example, the

45 Miller encoding device 2 and the modification signal

generator 6 of Figure 3 will generally not be

separated completely, but the logic circuits for the

two devices will be combined in a suitable manner,

as may also be the case with the detector 4.

50 As already stated with reference to Figure 3 the ultimately obtained encoded signal is recorded on a record carrier. Figure 5 by way of illustration represents the plan view of an optical disk provided with such a signal and Figure 6 a sectional view of the 55 information structure of such a disk.

The disk 21 shown in Figure 5, in whose centre, a hole 22 is formed, comprises a plurality of concentric tracks or a spiral track 23. Figure 5 shows only one circular track, the bit cells being represented - not to scale - by a plurality of sub-division marks. Where said bit cells form a time division in the information signal, they constitute a spatial structure on the disk. The structure as such depends on the modulation used for the record carrier. An optical audio disk

information structure comprising a sequence of pits and intermediate areas, as shown in Figure 6, the pits 24 for example representing the logic "1" level and the intermediate areas the logic "0" level of the encoded information signal. The structure of the pit and the intermediate area thus directly represents the information signal. Such a record carrier is particularly suitable for being copied and can cimply be read in an optical manner, the optimum pit depth depending on the read process (reading in reflection; in transmission; single-spot reading; divided spot reading).

Regardless of the contents of the information signals the record carrier exhibits a number of 80 special features. These special freatures will be describecd hereinafter for a record carrier provided with an information structure which is encoded in accordance with the method of the present invention. For example, the minimum distance between 85 two consecutive transitions from pit/non-pit to nonpit/pit is equal to one bit cell (see the bit cells 2 and 6/7 in Figure 1h). The maximum distance between two consecutive transitions is equal to three bit cells. Furthermore, distance occur which are situated 90 between said two extremes, namely distances of 11/2, 2 and 21/2 times the length of one bit cell. As the maximum distance is comparatively short, the signal read from the carrier always contains a sufficient number of transitions, so that the coding may be 95 regarded as self-clocking. Since on the other hand the minimum distance is not smaller than the length of one bit cell, it is possible to realize a suitable information density on the carrier. Another characteristic of the patterns on the record carrier is that the 100 transition which marks the beginning of the maximum distance of three bit cells is always situated at the beginning of a bit cell. This also applies to the transition which marks the end of the maximum distance. Thus, it is possible to ascertain unambi-105 guously which transitions on the carrier should be regarded as situated in the middle of a bit cell and at the beginning of a bit cell. Furthermore, it is essential that the modification used in order to obtain a d.c. free coding with a small low-frequency content can 110 be decoded unambiguously. However, this can be done unambiguously using transition/non-transition patterns which are only present on the carrier. If in the case of a decoding as that in accordance with Miller an "impossible" bit value is found, a value 115 "one" should be assigned to said bit and to the next bit. This is illustrated in Figure 1j. The waveform shown in Figure 1h is decoded in accordance with

the Miller method and then yields the result 000 for the bit cells 1 through 3 and a 0 for the bit cell 4,

120 which cannot be a zero because in accordance with the Miller code a zero following a zero should have a transition at the beginning of the bit cell, which transition is missing in the present case. The decoding result of bit cell 4 is designated F in Figure 1j. By substituting a "one" for the bit cell marked F and a "one" for the bit cell immediately following it, as is shown in Figure 1j, the decoded data signal becomes identical to the encoded data signal.

Figure 6 is a sectional view perpendicular to the 130 carrier shown by way of example in Figure 5, which

sectional view follows the track direction. In the information surface of the carrier 1 a plurality of pits 24 are formed and the pattern of pit (24)/non-pit (25) thus represents the binary information recorded in 5 this track.

As already stated in the foregoing, a possible decoding method effects decoding in accordance with the normal Miller rules, whilst in the case of an "impossible" bit said bit and the next bit are 10 interpreted as a "1".

However, the method of coding in accordance with the invention makes it possible to employ a very simple decoding. An embodiment of a device for carrying out this decoding method is represented 15 in Figure 7.

The device of Figure 7 first of all comprises a shift register 32 with 5 register cells, to which the information signal read is applied via an input terminal 31. The shift register is adapted to take up 20 the signal content of  $2\frac{1}{2}$  bit cell, each bit cell 32-1 through 32-5 containing the signal level of one bit-cell half. The shift register is clocked in such a way that the register cells 32-1 and 32-2 contain the levels of the two bit halves of a first bit  $(T_{-1})$ , the 25 register cells 32-2 and 32-4, the levels of the two bit halves of the next bit cell  $(T_0)$  and the register cell 32-5 the level of the first bit half of a subsequent bit cell  $(T_1)$ .

The register cells 32-1 through 32-5 are connected 30 to a detection device 34. Said detection device 34 comprises a first decision circuit 35, which is connected to the register cells 32-1 through 32-3 and a second decision circuit 36, which is connected to the register cells 32-3 through 32-5. Each of the decision 35 circuits 35 and 36 is adapted to detect whether and, if so, where in the relevant bit cell  $T_{-1}$  or  $T_0$  a transition occurs. For this purpose the signal levels of the relevant register cells are compared with each other. If the signal levels of the register cells 32-3 and 32-4 40 are unequal, this means that the data bit To exhibits a transition in the middle of the bit cell. The decision circuit 36 then supplies a logic "1" on its output bo. If the signal levels in the register cells 32-4 and 32-5 are unequal, this means that the data bit To has a 45 transition at the end of the bit cell. The decision circuit 36 then supplies a logic "1" on its output co. Finally, if the signal levels of the register cells 32-3, 32-4 and 32-5 are all equal, this means that the data bit T<sub>0</sub> contains no transition. The decision circuit 36 50 then supplies a logic "1" on its output ao. The decision circuit operates identically for the register cells 32-1 through 32-3, i.e. with respect to the data bit T\_1, with the proviso that said decision circuit need not comprise an output  $b_{-1}$ .

need not comprise an output b<sub>-1</sub>.

The data signal is decoded on the basis of the signals on the outputs of said decision circuits 35 and 36. For this purpose the decoding device comprises an AND-gate 37, whose two inputs are connected to the output c<sub>-1</sub> of the decision circuit 35 and the output a<sub>0</sub> of the decision circuit 36. The two inputs of a second AND-gate are connected to the respective outputs a<sub>-1</sub> and C<sub>0</sub> of the decision circuits 35 and 36. The outputs of said AND-gates 37 and 38 are connected to two inputs of an OR-gate 39, of 65 which a third input is connected to the output b<sub>0</sub> of

the decision circuit 36. The output of said OR-gate 39 is connected to a flip-flop 40, which is clocked by the clock signal from input 33 and whose output signal Q consequently corresponds to its input signal during the preceding data bit. Said Q-output is connected to an input of the AND-gate 37 and to an output terminal 41. The inverse output Q of the flip-flop 40 is connected to an input of the AND-gate 38.

The device shown in Figure 7 realizes the decoding 75 of the applied data bits in accordance with the diagram of Figure 8. If the decision circuit 36 supplies an output signal  $b_0 = 1$  for the data bit  $T_0$ , the OR-gate 39 will always supply a logic "1" level regardless of the output of the decision circuit 35, i.e. 80 a decoded "1" bit. If the decision circuit 36 supplies an output signal  $a_0 = 1$ , the output signal of the OR-gate 39 also depends on the preceding bit  $T_{-1}$ , specifically on the output  $c_{-1}$ . If for said bit  $T_{-1}$  the output c\_1 is zero, the output signal of the OR-gate 85 will also be zero. If the output  $c_{-1}$  is equal to one, the output signal of the OR-gate 39 will become equal to that occurring during the preceding bit. The decoded bit thus becomes equal to the previously decoded bit. If the output co of the decision circuit 36 is "1", 90 the output of the OR-gate 39 will be "zero" if  $a_{-1} = 0$ and equal to  $\overline{\mathbb{Q}}_{-1}$ , i.e. equal to the inverse logic level of the preceding bit  $T_{-1}$ , if  $a_{-1} = 1$ .

As can be demonstrated by means of an arbitrary bit pattern, this yields an unambiguous and very simple method of decoding the information signal encoded in accordance with the invention, which provides a correct decoding both of the data bits encoded in accordance with the normal Miller method and of the modified data bits with a minimum of logic circuitry.

## CLAIMS

1. A method of encoding a stream of data bits in 105 consecutive bit cells in a transmission system for recording and reproducing a recording signal on a record carrier, the bit stream being assumed to comprise consecutive words of a first and a second type and the data bits being of a first or a second 110 type, the second type of words comprising at least a sequence of one data bit of the second type followed: by  $m(m \ge 0)$  data bits of the first type, the method comprising normally encoding the data bits of the first type by a level transition in the middle as herein 115 defined of the relevant bit cell, normally encoding the data bits of the second type by a transition at the beginning (as herein defined) of the relevant bit cell, suppressing each transition at the beginning of a bit cell following a transition in the middle of the 120 immediately preceding bit cell and modifying words of the second type with an even number m of transitions of data bits of the first type in order to reduce the d.c. component in the binary signal, said modifying comprising suppressing the transitions in the middle of the bit cells corresponding to the first and the second data bit of the first type and providing a transition at the beginning of the bit cell associated with said second data bit.

2. A method as claimed in Claim 1, wherein the 130 words of the first type comprise a sequence of n ( $n \ge 1$

1) data bits of the second type and for words of the second type  $m \ge 1$ .

- 3. An encoding device for carrying out the method as claimed in Claim 1 or 2, comprising a first 5 input for receiving the binary data bits, a second input for receiving a clock signal which is in synchronism with the data bits, an output for supplying the encoded signal to a recording device for a record carrier, means for generating a signal transition in 10 the middle of a clock interval in the case of a data bit of the first type, means for generating a signal transition at the beginning of a clock interval in the case of a data bit of the second type, means for suppressing a transition at the beginning of a clock 15 interval following a transition in the middle of the immediately preceding clock interval, means for detecting a word of the second type where m is even, means for suppressing the transitions in the middle of the clock interval corresponding to said 20 first and second bit of the first type in a word of said second type where m is even and means for generating a transition at the beginning of the clock interval corresponding to said second bit of the first type in a word of the second type where m is even.

- 4. A record carrier provided with an information 25 structure comprising sequences of bit cells, which bit cells each contain one information bit, whose information content is represented by the presence or absence of a level transition in the middle or at the 30 beginning of the bit cell, wherein the minimum distance between two consecutive level transitions is equal to the length of one bit cell, the maximum distance between two consecutive transitions is equal to the length of three bit cells, a transition in 35 the middle (as herein defined) of a bit cell represents a "logic one" and a transition at the beginning (as herein defined) of a bit cell normally represents a "logic zero" unless the same level appears in two consecutive bits cells, in which case the second one

- 40 of the said consecutive bit cells and the bit cell preceding it represent a "logic one", the running integral of the information structure assumes a maximum value of 2T, T being the length of the bit cells and wherein the level transitions which are

- 45 spaced from each other by a maximum distance of three bit cells mark the beginning of the bit cell.

- 5. An apparatus for reading and decoding a record carrier as claimed in Claim 4, the apparatus comprising detection means for detecting the pairs of modified bit cells and converting said two bit cells into two data bits of a logic value one, and means for converting the other bit cells into data bits in accordance with the normal Miller decoding rules.

- 6. An aparatus as claimed in Claim 5, wherein the 55 detection means comprise a detector for detecting bit cells, which in combination with the preceding bit cells, do not comply with the normal Miller code.

- 7. An apparatus as claimed in Claim 5, further comprising means for converting a bit cell with a 60 transition in the middle (as herein defined) of the bit cell into a data bit of logic value "one", means for converting a bit cell with a transition at the end into a data bit with a logic value which is the inverse of that of the decoded preceding data bit if the preceding bit 65 cell does not have a transition in the middle and no

- transition at the end, and into a data bit of logic value "zero" if the preceding bit cell does exhibit one of said transitions, and means for converting a bit cell without transition in the middle and at the end into a data bit of a logic value identical to that of the decoded preceding data bit if the preceding bit cell exhibits a transition at the end and into a data bit of the logic value "zero" if said preceding bit cell does not exhibit said transition at the end.

- 8. A device as claimed in Claim 6, further comprising a storage device for storing at least two consecutive bit cells, a first detector for detecting the presence of a transition in a first bit cell and the position of said transition and supplying a first logic output signal which is representative thereof, a second detector for detecting the presence of a transition in a bit cell which immediately precedes the first one and the position of this transition and supplying a second logic output signal which is

85 representative thereof, and a logic circuit for deriving the decoded data signal from the first and the second logic output signal of the first and the second detector.

- A method of encoding a stream of data bits in consecutive bit cells in a transmission system for recording and reproducing a recording signal on a record carrier, substantially as hereinbefore described with reference to the accompanying drawings.

- 95 10. An encoding device for carrying out the method as claimed in Claim 1 or 2, substantially as hereinbefore described with reference to Figures 3 and 4 of the accompanying drawings.

- 11. A record carrier substantially as hereinbefore100 described with reference to Figures 5 and 6 of the accompanying drawings.

- 12. An apparatus for reading and decoding a record carrier as claimed in Claim 4, substantially as hereinbefore described with reference to Figures 7

105 and 8 of the accompanying drawings.

Printed for Her Majesty's Stationery Office by Croydon Printing Company Limited, Croydon, Surrey, 1981. Published by The Patent Office, 25 Southampton Buildings, London, WC2A 1AY, from which copies may be obtained.