# (19) 日本国特許庁(JP) (12) 特許公報(B2)

(11)特許番号

特許第4471748号 (P4471748)

(45) 発行日 平成22年6月2日(2010.6.2)

(24) 登録日 平成22年3月12日(2010.3.12)

| (51) Int.Cl. |               |           | F I  |       |              |

|--------------|---------------|-----------|------|-------|--------------|

| HO4N         | 5/232         | (2006.01) | HO4N | 5/232 | $\mathbf{Z}$ |

| HO4N         | <i>5/21</i>   | (2006.01) | HO4N | 5/21  | В            |

| HO4N         | <i>5/33</i> 5 | (2006.01) | HO4N | 5/335 | R            |

| HO4N         | 9/07          | (2006.01) | HO4N | 9/07  | Α            |

請求項の数 10 (全 15 頁)

| (21) 出願番号 | 特願2004-188689 (P2004-188689) |

|-----------|------------------------------|

| (22) 出願日  | 平成16年6月25日 (2004.6.25)       |

| (65) 公開番号 | 特開2006-13948 (P2006-13948A)  |

| (43) 公開日  | 平成18年1月12日 (2006.1.12)       |

| 審査請求日     | 平成19年6月1日 (2007.6.1)         |

|           |                              |

||(73)特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

|(74)代理人 ||110000154|

特許業務法人はるか国際特許事務所

|(72)発明者 中莖 俊朗

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

審査官 高野 美帆子

最終頁に続く

## (54) 【発明の名称】画像信号処理装置

## (57)【特許請求の範囲】

### 【請求項1】

撮像素子により生成された画像信号を処理する画像信号処理装置において、

画像内に配置される対象点に対して所定の位置関係にあるn個の参照画素(nは3以上 の整数である)に基づき、当該対象点に対応付ける変換画素値を生成するフィルタ回路で あって、前記n個の参照画素の画素値のうち、上位 画素及び下位 画素(ここで 、 1及びn - -2 を満たす 0 以上の整数である)を除いた(n - -個の残余参照画素の前記画素値の平均値を前記変換画素値として算出する画素補正フィル 夕回路を有し、

前記撮像素子で発生する暗電流によって前記画素値が増加する場合に、

前記画素補正フィルタ回路は、除去される前記上位 画素及び前記下位 画素に関し、

> なる関係を有することを特徴とする画像信号処理装置。

#### 【請求項2】

請求項1に記載の画像信号処理装置において、

前記残余参照画素は、複数の前記残余参照画素それぞれの代表点の座標の重心が、前記 対象点の近傍周囲に位置する複数の前記参照画素それぞれの前記代表点を結んで形成され る多角形領域内に存在するように設定されること、

を特徴とする画像信号処理装置。

## 【請求項3】

請求項2に記載の画像信号処理装置において、

前記残余参照画素は、前記重心が前記多角形領域の周を除いた内側部分に位置するように設定されること、

を特徴とする画像信号処理装置。

#### 【請求項4】

請求項1から請求項3のいずれか1つに記載の画像信号処理装置において、

前記画素補正フィルタ回路を備え、当該画素補正フィルタ回路による画素補正処理を伴う第1信号処理と、前記画素補正処理を伴わない第2信号処理とを選択的に行う処理部と

前記画像信号を取得する際の前記撮像素子での露光制御に応じて、前記処理部での前記 第1信号処理と前記第2信号処理との切り換えを制御する制御部と、

を有することを特徴とする画像信号処理装置。

#### 【請求項5】

請求項1から請求項3のいずれか1つに記載の画像信号処理装置において、

前記画素補正フィルタ回路を備え、当該画素補正フィルタ回路による画素補正処理を伴う第1信号処理と、前記画素補正処理を伴わない第2信号処理とをそれぞれ行い、前記第1信号処理による出力と前記第2信号処理による出力とを、可変な合成比率で合成する処理部と、

前記画像信号を取得する際の前記撮像素子での露光制御に応じて、前記合成比率を制御 する制御部と、

を有することを特徴とする画像信号処理装置。

#### 【請求項6】

請求項4又は請求項5に記載の画像信号処理装置において、

前記処理部は、ノイズ抑制されたノイズ抑制画像信号を生成して出力し、

前記第1信号処理は、前記画素補正処理後の画像信号に対し、第1低域通過特性に基づく低域通過フィルタ処理を行って前記ノイズ抑制画像信号を生成し、

前記第 2 信号処理は、前記画素補正処理を施さない画像信号に対し、前記第 1 低域通過特性とは異なる第 2 低域通過特性に基づく低域通過フィルタ処理を行って前記ノイズ抑制画像信号を生成すること、

を特徴とする画像信号処理装置。

## 【請求項7】

請求項4から請求項6のいずれか1つに記載の画像信号処理装置において、

前記処理部は、前記画像信号に基づいて、画像の輪郭に応じた輪郭補正信号を生成して出力し、

前記第1信号処理は、前記画素補正処理後の画像信号を用いて、第1帯域通過特性に基づく前記輪郭補正信号を生成し、

前記第2信号処理は、前記画素補正処理を施さない画像信号を用いて、前記第1帯域通過特性とは異なる第2帯域通過特性に基づく前記輪郭補正信号を生成すること、

を特徴とする画像信号処理装置。

### 【請求項8】

請求項6に記載の画像信号処理装置において、

前記第1低域通過特性は前記第2低域通過特性よりもカットオフ周波数が低いことを特徴とする画像信号処理装置。

### 【請求項9】

請求項7に記載の画像信号処理装置において、

前記第1帯域通過特性は前記第2帯域通過特性よりも通過帯周波数が低いことを特徴とする画像信号処理装置。

#### 【請求項10】

撮像素子により生成された画像信号を処理する画像信号処理方法において、

画像内に配置される対象点に対して所定の位置関係にあるn個の参照画素(nは3以上の整数である)の画素値のうち、上位 画素及び下位 画素(ここで 、 は + 1

10

20

30

40

及びn - 2 を満たす 0 以上の整数である)を除いた(n - - ) 個の残余参照 画素の前記画素値を取得するステップと、

(n - - )個の前記残余参照画素の画素値の平均値を算出するステップと、

前記平均値を前記対象点に変換画素値として対応付けるステップと、

を有し、新たな画像信号を生成するものであって、

前記撮像素子で発生する暗電流によって前記画素値が増加する場合に、除去される前記上位 画素及び前記下位 画素に関し、 > なる関係を有することを特徴とする画像信号処理方法。

【発明の詳細な説明】

#### 【技術分野】

[0001]

本発明は、撮像素子により生成された画像信号に含まれる暗電流等のノイズを抑制する処理を行う画像信号処理装置に関する。

#### 【背景技術】

#### [0002]

デジタルカメラ等の撮像装置においては、被写体の明るさに応じて露光時間や増幅回路のゲインを調節することにより、好適な信号レベルの画像信号を得ることができる。しかし、露光時間を長くすると、画像信号に含まれる暗電流ノイズが増加し、また増幅ゲインを上げると、ノイズ成分までも増幅される。

[0003]

そこで従来より、フィルタ回路を用いて画像信号からノイズを除去することが行われている。

## [0004]

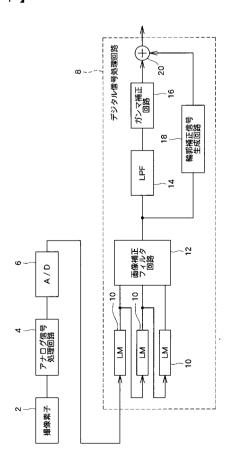

図11は、撮像素子により生成された画像信号を処理する従来の画像信号処理装置の構成を示すブロック図である。 C C D (Charge Coupled Device:電荷結合素子)イメージセンサ等の撮像素子 2 から出力された画像信号は、アナログ信号処理回路 4 での処理後、A / D 変換回路 6 にてデジタルデータに変換され、デジタル信号処理回路 8 に入力される。デジタル信号処理回路 8 では、複数ライン分の画像データを保持するラインメモリ10、及び画素補正フィルタ回路12により二次元フィルタ処理が行われる。図11では、ラインメモリ10を3ライン分備える構成を示している。

[0005]

画素補正フィルタ回路12の出力は低域通過フィルタ(LPF)14に入力される。撮像素子2が一般的なベイヤー配列のカラーフィルタを備えるとき、LPF14は、カラーフィルタ毎の出力レベル段差を除去するために、垂直、水平各方向に関してサンプリング周波数の1/2の周波数成分をトラップする。LPF14の出力はガンマ補正回路16にて階調補正処理を施される。

## [0006]

また、画素補正フィルタ回路12の出力は、輪郭補正信号生成回路18にも入力される。輪郭補正信号生成回路18は、画像中のエッジ部にて大きく振れる画像信号の二次微分波形を求め、これに適当なゲインを乗じることにより輪郭補正信号を生成する。生成された輪郭補正信号は加算器20で、画像信号に合成され、これにより画質調整の一つである輪郭強調処理が実現される。

[0007]

従来、画素補正フィルタ回路12は、メディアンフィルタ(median filter)やミーンフィルタ (mean filter)を構成し、ノイズ除去に供せられている。

## 【発明の開示】

【発明が解決しようとする課題】

#### [0008]

画素補正フィルタ回路 1 2 は、対象画素とその周囲の所定の位置の画素とからなる複数の参照画素の画素値を、ラインメモリ 1 0 に保持された画像データから取得する。

10

20

30

40

#### [0009]

ミーンフィルタは、複数の参照画素の画素値の平均値を求め、この平均値を対象画素の画素値として置き換える。ミーンフィルタは、フィルタサイズ内の画素値を平滑化する作用を有し、よって、フィルタサイズ内でまばらに発生するノイズの除去に効果が期待される。ここで、暗電流は、画素欠陥等から持続的に発生しやすく、露光時間が長くなるにつれて暗電流の影響を受ける画素範囲が広がる。また、暗電流は、正負両極性を持つものではなく、例えば画素値を増加させるといった一方向にしか作用しない。これらの性質から、ミーンフィルタは、暗電流ノイズを好適に除去しにくいという問題があった。例えば、暗電流成分の影響を受けている画素が、5画素の参照画素のうち1画素だけであれば、ミーンフィルタにより、暗電流ノイズはある程度、低減されるが、参照画素のうちの暗電流の影響を受ける画素の割合が増加するにつれて、ノイズ低減効果は低下する。

[0010]

一方、メディアンフィルタは、複数の参照画素の画素値のうちの中央値を求め、この中央値を対象画素の画素値として置き換えるものである。メディアンフィルタは、ミーンフィルタよりは暗電流ノイズを除去しやすくはなるが、やはり参照画素のうちの暗電流の影響を受ける画素の割合が高くなると、中央値として選択される画素が暗電流の影響を受けたものである可能性が高くなる。また、フィルタを構成する参照画素数を増加すれば、暗電流の領域的な広がりの影響を受けにくくなるが、中央値を検出する回路の大規模化が顕著になるという問題があった。

[0011]

本発明は上記問題点を解消するためになされたもので、撮像素子により生成された画像信号を処理する画像信号処理装置において、暗電流等の発生領域が広がりやすいノイズを抑制する構成を提供することを目的とする。

【課題を解決するための手段】

#### [0012]

本発明に係る画像信号処理装置は、画像内に配置される対象点に対して所定の位置関係にあるn個の参照画素(nは3以上の整数である)に基づき、当該対象点に対応付ける変換画素値を生成するフィルタ回路であって、前記n個の参照画素の画素値のうち、上位画素及び下位 画素(ここで 、 は + 1及びn - 2を満たす0以上の整数である)を除いた(n - - )個の残余参照画素の前記画素値の平均値を前記変換画素値として算出する画素補正フィルタ回路を有するものである。

[0013]

本発明によれば、 1かつ 1の場合には、画素値の上位 画素及び下位 画素が除かれ、一方、 = 0の場合には上位 画素だけ、 = 0の場合には下位 画素だけが除かれ、残余参照画素が定められる。ノイズの影響を受けた画素値は上位、下位に位置することが期待され、それらを除くことで、複数の残余参照画素における、ノイズの影響を受けていない、又は影響が比較的小さい画素の割合が高まることが期待される。上位、下位のいずれを除くか、またそれらの画素数は、ノイズの性質に応じて設定される。さらに、複数の残余参照画素の画素値を平均処理することで、残余参照画素の一部にノイズの影響を受けたものが含まれている場合に、その影響を軽減することができる。

[0014]

他の本発明に係る画像信号処理装置は、前記撮像素子で発生する暗電流によって前記画素値が増加する場合に、前記画素補正フィルタ回路が、除去される前記上位 画素及び前記下位 画素に関し、 > なる関係を有するものである。

#### [0015]

暗電流の影響は画素値を一定の方向にシフトさせるように作用する。いずれの方向にシフトするかは画像信号や画素値の定義に依存するが、通常、画素に蓄積される信号電荷が増加すると画素値が増加するように定められ、一方、暗電流は信号電荷を増加させるので、この場合、暗電流の影響を受けると、画素値は上位側にシフトする。そこで、下位側より上位側に画素除去の重きを置くことで、残余参照画素における暗電流の影響を低減する

10

20

30

40

ことができる。

#### [0016]

別の本発明に係る画像信号処理装置においては、複数の前記残余参照画素それぞれの代表点の座標の重心が、前記対象点の近傍周囲に位置する複数の前記参照画素それぞれの前記代表点を結んで形成される多角形領域内に存在するように、前記残余参照画素の数が設定される。

#### [0017]

代表点は、所定の広がりを有する画素内の所定座標であり、画像のサンプリング点に対応付けられる。参照画素は対象点を幾重にも取り囲むように配列され得るが、その場合には、対象点の近傍周囲の参照画素は、最も内側にて対象画素を取り囲む参照画素群を意味する。残余参照画素の数を増やすと、重心の平均的な位置は対象点に近づく。この重心は変換画素値のサンプリング点に相当する。本発明によれば、この重心と対象点とのずれを、例えば、対象点に近接する参照画素の代表点までの距離以下とすることが可能となり、ジャギーノイズ等が抑制され画質が向上する。本発明の好適な態様は、前記重心が前記多角形領域の周を除いた内側部分に位置するように、前記残余参照画素の数が設定される画像信号処理装置である。

#### [0018]

また他の本発明に係る画像信号処理装置は、前記画素補正フィルタ回路を備え、当該画素補正フィルタ回路による画素補正処理を伴う第1信号処理と、前記画素補正処理を伴わない第2信号処理とを選択的に行う処理部と、画像信号を取得する際の前記撮像素子での露光制御に応じて、前記処理部での前記第1信号処理と前記第2信号処理との切り換えを制御する制御部と、を有するものである。

#### [0019]

暗電流等のノイズ量は、露光時間や増幅ゲインによる露光制御に応じて変化する。本発明によれば、例えば、ノイズが多いことが期待される露光制御条件では第1信号処理を行って、画素補正フィルタ回路による画素補正処理でノイズ低減を図る一方、ノイズが少ないことが期待される露光制御条件では第2信号処理を行うこととして、画素補正処理の副作用である解像度低下を回避する。

### [0020]

さらに他の本発明に係る画像信号処理装置は、前記画素補正フィルタ回路を備え、当該画素補正フィルタ回路による画素補正処理を伴う第1信号処理と、前記画素補正処理を伴わない第2信号処理とをそれぞれ行い、前記第1信号処理による出力と前記第2信号処理による出力とを、可変な合成比率で合成する処理部と、画像信号を取得する際の前記撮像素子での露光制御に応じて、前記合成比率を制御する制御部と、を有するものである。

#### [0021]

本発明によれば、例えば、露光制御条件に基づき、ノイズが多い場合には第1信号処理の出力の比率を連続的、又は段階的に高め、反対にノイズが少ない場合には第2信号処理の出力の比率を高めることとして、ノイズ抑制と解像度の確保とを図る。

### [0022]

別の本発明に係る画像信号処理装置においては、前記処理部が、ノイズ抑制されたノイズ抑制画像信号を生成して出力し、前記第1信号処理が、前記画素補正処理後の画像信号に対し、第1低域通過特性に基づく低域通過フィルタ処理を行って前記ノイズ抑制画像信号を生成し、前記第2信号処理が、前記画素補正処理を施さない画像信号に対し、前記第1低域通過特性とは異なる第2低域通過特性に基づく低域通過フィルタ処理を行って前記ノイズ抑制画像信号を生成する。本発明の好適な態様は、前記第1低域通過特性が前記第2低域通過特性よりもカットオフ周波数が低い画像信号処理装置である。

#### [0023]

さらに別の本発明に係る画像信号処理装置においては、前記処理部が、前記画像信号に基づいて、画像の輪郭に応じた輪郭補正信号を生成して出力し、前記第1信号処理が、前記画素補正処理後の画像信号を用いて、第1帯域通過特性に基づく前記輪郭補正信号を生

10

20

30

40

成し、前記第2信号処理が、前記画素補正処理を施さない画像信号を用いて、前記第1帯域通過特性とは異なる第2帯域通過特性に基づく前記輪郭補正信号を生成する。本発明の好適な態様は、前記第1帯域通過特性が前記第2帯域通過特性よりも通過帯周波数が低い画像信号処理装置である。

### [0024]

本発明に係る画像信号処理方法は、画像内に配置される対象点に対して所定の位置関係にあるn個の参照画素(nは3以上の整数である)の画素値のうち、上位 画素及び下位画素(ここで 、 は + 1及びn - 2を満たす0以上の整数である)を除いた(n - - )個の残余参照画素の前記画素値を取得するステップと、(n - -

)個の前記残余参照画素の画素値の平均値を算出するステップと、前記平均値を前記対象点に変換画素値として対応付けるステップとを有し、新たな画像信号を生成するものである。

#### 【発明の効果】

#### [0025]

本発明によれば、暗電流等の発生領域が広がりやすいノイズを好適に抑制することが可能となる。

【発明を実施するための最良の形態】

#### [0026]

以下、本発明の実施の形態(以下実施形態という)について、図面に基づいて説明する .

[0027]

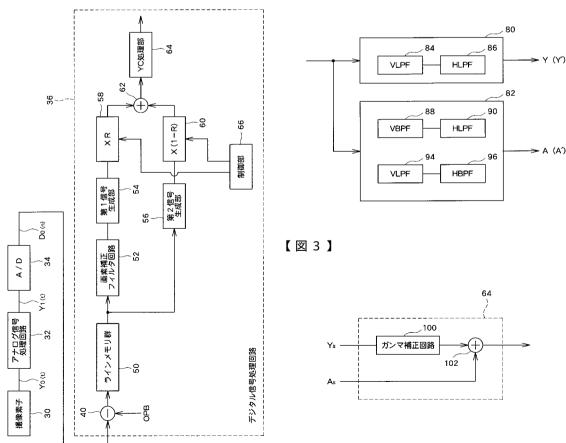

図1は、本発明の実施形態である画像信号処理装置の構成を示す概略のブロック図であり、撮像素子30から出力された画像信号に基づいて、階調補正、輪郭補正及びノイズ抑制された画像データを生成する。ここでは撮像素子30はCCDイメージセンサであり、撮像素子30から出力される画像信号Y0(t)は、アナログ信号処理回路32に入力される。アナログ信号処理回路32は、サンプルホールド、自動利得制御(AGC:Auto Gain Control)等の処理を画像信号Y0(t)に施し、所定のフォーマットに従う画像信号Y1(t)を生成する。A/D変換回路34はアナログ信号処理回路32から出力される画像信号Y1(t)をデジタルデータに変換して、画像データD0(n)を出力する。デジタル信号処理回路36はA/D変換回路34から画像データD0(n)を取り込み、各種の処理を行う

[0028]

デジタル信号処理回路 3 6 は、減算器 4 0 、ラインメモリ群 5 0 、画素補正フィルタ回路 5 2 、第 1 信号生成部 5 4 、第 2 信号生成部 5 6 、乗算器 5 8 ,6 0 、加算器 6 2 、 Y C 処理部 6 4 及び制御部 6 6 を含んで構成される。

#### [0029]

減算器40は、画像データD0(n)からオプティカルブラック信号成分OPBを除去する。

### [0030]

ラインメモリ群 5 0 は 7 ラインのラインメモリからなり、垂直方向に連続する 7 ライン 分の画像データを保持し、画素補正フィルタ回路 5 2 及び第 2 信号生成部 5 6 での処理に 画像データを供する。現在保持されている 7 ラインのデータに対する画素補正フィルタ回 路 5 2 及び第 2 信号生成部 5 6 の処理が完了すると、最先に読み込まれた 1 ラインと入れ 替えに後続の 1 ラインが新たにラインメモリ群 5 0 に読み込まれる。

#### [0031]

画素補正フィルタ回路 5 2 は、ラインメモリ群 5 0 に保持された画像データに基づいて後述する二次元フィルタ処理を行う。この二次元フィルタ処理では、対象画素とその周辺に配置された複数画素とからなる参照画素に基づいて、後述する処理を行い、得られた結果値が対象画素の変換画素値として出力される。画素補正フィルタ回路 5 2 はラインメモリ群 5 0 に保持された各ラインにそれぞれ対象画素を設定し、それら 7 個の対象画素に対

10

20

30

40

して二次元フィルタ処理を並列に実行し、変換画素値で構成される 7 ラインの画像信号を 並列に第 1 信号生成部 5 4 へ出力する。

#### [0032]

第1信号生成部54は、画素補正フィルタ回路52から並列に出力される7ラインの画像信号に基づいて、垂直、水平両方向にLPF処理を施した輝度信号Yと、輪郭補正信号Aとを生成し出力する。第2信号生成部56は、ラインメモリ群50から並列に読み出される7ラインの画像信号に基づいて、同様にLPF処理を施した輝度信号Y'と、輪郭補正信号A'とを生成し出力する。

#### [0033]

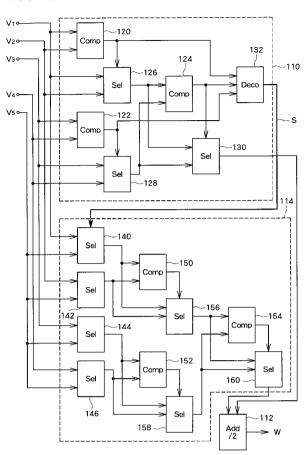

図2は、第1信号生成部54、第2信号生成部56の概略の構成を示すブロック図であり、LPF80と輪郭補正信号生成回路82とを含んで構成される。LPF80は、垂直方向に関するLPF処理を行うVLPF84と水平方向に関するLPF処理を行うHLPF86とを備え、輝度信号Y又はY'を生成する。ここで、VLPF84は画素補正フィルタ回路52又はラインメモリ群50からの7ラインをそれぞれタップに入力され、LPF処理結果として1ラインの画像信号を出力する。また、HLPF86はこの画像信号に対し、設定されたタップ係数に基づくLPF処理を行う。

#### [0034]

輪郭補正信号生成回路82は、輪郭補正信号Aとして垂直方向に関する輪郭補正信号Avと水平方向に関する輪郭補正信号Ahとを生成する。信号Avは、画素補正フィルタ回路52又はラインメモリ群50から得た画像信号に対し、垂直方向に関する帯域通過フィルタ(BPF)処理を行うVBPF88とHLPF90とで順次、処理を行って生成される。信号Ahは、画素補正フィルタ回路52又はラインメモリ群50から得た画像信号に対し、VLPF94と水平方向に関するBPF処理を行うHBPF96とで順次、処理を行って生成される。なお、BPF処理により、画像中のエッジ部にて大きく振れる画像信号の二次微分波形が得られる。また、輪郭補正信号生成回路82はA,A,に適当なゲインを乗じて出力するように構成することができる。

#### [0035]

第1信号生成部54及び第2信号生成部56は図2に示す共通のブロック構成を有するが、各LPF84,86,90,94及びVBPF88、HBPF96に設定されるタップ係数は後述するように相違させることができる。

#### [0036]

乗算器58は、第1信号生成部54の出力信号に係数Rを乗じ、一方、乗算器60は、 第2信号生成部56の出力信号に係数(1-R)を乗じる。ここでRの値は、制御部66 が撮像素子30に対する露光制御条件に基づいて制御する。

# [0037]

加算器62は、乗算器58,60の出力を加算合成して、YC処理部64へ出力する。 具体的には、輝度信号Y,Y'に基づいて合成された輝度信号Ysと、輪郭補正信号A、A'に基づいて合成された輪郭補正信号Asが加算器62からYC処理部64へ出力される。

#### [0038]

YC処理部64は、輝度信号Ys及び輪郭補正信号Asを用いて階調補正処理及び輪郭補正処理を行う。図3は、YC処理部64の概略のブロック構成であり、ガンマ補正回路100及び加算器102を含んで構成される。ガンマ補正回路100は画像信号Ysに対して、非線形変換特性に基づいて信号レベルを変換する処理を行う。ガンマ補正回路100から出力された輝度信号は、加算器102にて輪郭補正信号Asを加算合成され、これにより輪郭補正された輝度信号が生成される。なお、YC処理部64はさらに、色分離等の他の信号処理を行い色信号を生成することができるが、ここでは説明を省略する。

#### [0039]

次に画素補正フィルタ回路52が行う二次元フィルタ処理について説明する。図4は、二次元フィルタの処理に用いられる画像領域(以下、窓と称する)での画像データの配置

10

20

30

40

10

20

30

40

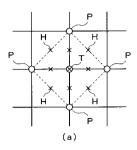

50

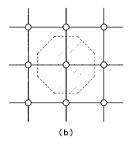

及び参照画素の位置の一例を示す模式図である。ここで、窓は垂直7画素×水平5画素である。ちなみにこの垂直方向の7画素はラインメモリ群50に保持されるライン数に対応している。また、図中のR,G,Bは各画素に対応付けられる色を表しており、それで、ここでは色の配列はベイヤー配列である。参照画素は窓内に5画素又は4画素、設定される。図4(a)には、フィルタ処理により値が定められる対象点が窓の中央の画素に対応である。回4(a)には、フィルタ処理により値が定められる対象点が窓の中央の画素に対応である1回素とその上下左右方向に位置する4画素との合計5画素である。これら参照画素の配置が示されている。この場合の参照画素に設定される。例えば、図4に示す対象点に対応する中央の参照画素に設定される。例れている。なり、その周囲の4つの参照画素は中央の参照画素からそれぞれ上下左右に2両ずれた位置に設定される。この配置の5つの参照画素がらそれぞれ上下左右に2方であり、その周囲の4つの参照画素は、図4の例では第3、第5ラインのか平中央3ラインにおいて設定可能である。すなわち、上記第4ラインの水平中央画素のG画素が設定である場合と同様に、対象点とその上下左右とに位置する合計5つの参照画素が設定される。

#### [0040]

一方、窓を構成する 7 ラインのうち上側、下側各 2 ラインについては、 4 つの参照画素が設定される。図 4 ( b ) は、この場合の例であり、対象点が上から 2 番目のラインの水平中央画素の G 画素である場合の参照画素の配置が示されている。この場合の参照画素は、対象点に対応する 1 画素、対象点の左右方向に位置する 2 画素、及び対象点の上又は下のいずれかに位置する 1 画素の合計 4 画素である。この場合も参照画素は同じ色の画素に設定される。

## [0041]

画素補正フィルタ回路 5 2 は、各対象点に対して設定される 5 画素(又は 4 画素)の参照画素のうち画素値が大きい順序での上位 3 画素(又は 2 画素)を無視し、残り 2 つの参照画素の画素値の平均値を求めて、当該平均値を変換画素値として対象点に割り付ける。画素補正フィルタ回路 5 2 での処理はプログラムを用いて実現することもできるが、ここではより高速処理が可能なハードウェア回路として実現する例を説明する。図 5 、図 6 はその概略の構成を示す回路図である。図 5 は上述の参照画素が 5 つの場合の処理を行う回路構成であり、図 6 は参照画素が 4 つの場合の処理を行う回路構成である。窓の中央 3 ライン上にそれぞれ設定される対象点に対する処理、及び窓の上側、下側の各 2 ライン上にそれぞれ設定される対象点に対する処理を並列して行うために、画素補正フィルタ回路 5 2 は、図 5 に示す回路を 3 個、図 6 に示す回路を 4 個備える。

## [0042]

図5の回路は、5つの参照画素の画素値 V 1 ~ V 5を入力される。ブロック 1 1 0 は V 1 ~ V 4を入力され、それらのうちの最小値 M 1を求めて加算平均回路 1 1 2 へ出力する。またブロック 1 1 0 は当該最小値を有する画素に応じてセレクタ信号 S を生成して、ブロック 1 1 4 に与える。ブロック 1 1 4 は、セレクタ信号 S に基づいて、 V 1 ~ V 4 から最小値画素を外して、代わりに V 5 を加えた 4 画素の値を取り込み、それらのうちの最小値 M 2 を求めて加算平均回路 1 1 2 は M 1 , M 2 の平均値を求め、これを対象点に対応する画素値 W として出力する。

#### [0043]

プロック110は、3つの比較器120~124、3つのセレクタ126~130及びデコーダ132を含んで構成される。比較器120はV1,V2の大小を比較し、比較結果に応じた信号をセレクタ126及びデコーダ132に入力する。この比較結果に基づき、セレクタ126はV1,V2のうち小さい方を選択して、比較器124及びセレクタ130へ出力する。比較器122はV3,V4の大小を比較し、比較結果に応じた信号をセレクタ128及びデコーダ132に入力する。この比較結果に基づき、セレクタ128はV3,V4のうち小さい方を選択して、比較器124及びセレクタ130へ出力する。比較器124はセレクタ126,128から入力された2つの画素値の大小を比較し、比較

10

20

30

40

結果に応じた信号をセレクタ130及びデコーダ132に入力する。この比較結果に基づき、セレクタ130は2つの入力データのうち小さい方を選択して出力する。この出力値がM1となる。デコーダ132は、各比較器120~124から入力された比較結果に基づいて、ブロック114の入力に設けられた4つのセレクタ140~146のいずれかを選択する信号Sを生成する。

## [0044]

プロック 1 1 4 は、入力側に設けられた 4 つのセレクタ 1 4 0 ~ 1 4 6 の他に、 3 つの比較器 1 5 0 ~ 1 5 4 及び 3 つのセレクタ 1 5 6 ~ 1 6 0 を含んで構成される。セレクタ 1 4 0 ~ 1 4 6 は、一方の入力端にそれぞれ V 1 ~ V 4 を入力され、もう一方の入力端には V 5 が共通に入力される。セレクタ信号 S は、セレクタ 1 4 0 ~ 1 4 6 のうち、一方の入力データとして V 1 ~ V 4 の最小値が入力されるいずれか 1 つのセレクタに対して、他方の入力データ V 5 を出力させ、残りの 3 つのセレクタに対して、 V 5 ではない側の入力データを出力させる。すなわち、上述したようにセレクタ 1 4 0 ~ 1 4 6 からは、 V 1 ~ V 4 のうちの最小値を除く 3 つの画素値と V 5 とが出力される。セレクタ 1 4 0 ~ 1 4 6 から出力される 4 つの画素値に対する比較器 1 5 0 ~ 1 5 4 及びセレクタ 1 5 6 ~ 1 6 0 の処理は、上述したプロック 1 1 0 における比較器 1 2 0 ~ 1 2 4 及びセレクタ 1 2 6 ~ 1 3 0 の処理と同様であり、セレクタ 1 6 0 からは当該 4 つの画素値のうちの最小値、すなわ5 M 2 が出力される。

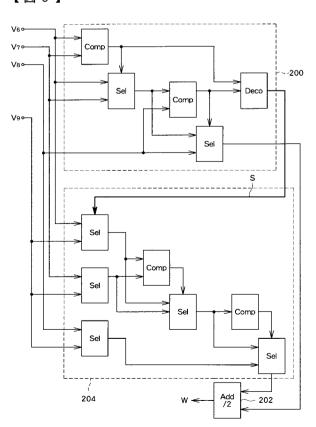

#### [0045]

図6の回路は、4つの参照画素の画素値 V6~V9を入力される。V6~V8を入力されるブロック 2 0 0 は、処理対象の画素が 1 つ少ない分、ブロック 1 1 0 の構成を簡単にしたものと見れば、その構成及び動作は容易に理解される。ブロック 2 0 0 は V6~V8 のうちの最小値 V1 を求めて加算平均回路 2 0 2 へ出力する。一方、ブロック 2 0 4 も、処理対象の画素が 1 つ少ない分、ブロック 1 1 4 の構成を簡単にしたものと見れば、その構成及び動作は容易に理解される。ブロック 2 0 4 は、ブロック 2 0 0 が生成するセレクタ信号 V1 に V2 を V3 から最小値画素を外して、代わりに V3 を加えた 3 画素の値を取り込み、それらのうちの最小値 V3 を求めて加算平均回路 2 0 2 へ出力する。加算平均回路 2 0 2 は V1 ,V2 の平均値を求め、これを対象点に対応する画素値 V2 として出力する。

## [0046]

画素補正フィルタ回路52は、ラインメモリ群50に保持された7ラインの画像データに対し、垂直7画素×水平5画素の窓を水平方向に1画素ずつ順次移動させながら処理を行う。画素補正フィルタ回路52は、図5及び図6に示す回路を上述したように複数備え、窓の各位置にて、窓の水平方向の中央に垂直に並ぶ7画素を対象点とする処理を並列して行い、それら7画素に対応する変換画素値を生成する。

#### [0047]

第1信号生成部54は、画素補正フィルタ回路52から出力される垂直方向に並ぶ7画素の変換画素値を垂直方向に関するフィルタであるVLPF84,94及びVBPF88に取り込む。これら垂直方向に関するフィルタは次々と垂直7画素のセットを入力され、各フィルタは各セット毎に1つの画素データを生成する。そして、窓の水平方向の移動に伴って、垂直方向に関するフィルタから順次出力される画像データの連続する複数個を対象として、後段の水平方向に関するフィルタHLPF86,90及びHBPF96が処理を行う。

## [0048]

第2信号生成部56は、画素補正フィルタ回路52が対象点とする垂直方向に並ぶ7画素の画像データをラインメモリ群50から直接取り出して、VLPF84,94及びVBPF88での処理を行い、次いでHLPF86,90及びHBPF96での処理を行う。この第2信号生成部56の処理は、第1信号生成部54での処理に連動して行われ、互いに同じ位置の画素に対する処理結果を同期して出力する。

## [0049]

10

20

30

40

50

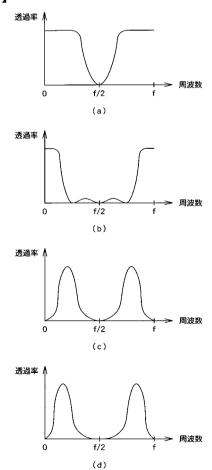

さて、上述したように各LPF84,86,90,94及びVBPF88、HBPF96に設定されるタップ係数に応じて、第1信号生成部54と第2信号生成部56とでそれら各フィルタの通過特性を相違させることができる。図7に示す模式的な通過特性図は、その一例である。図7(a)及び(b)はLPFの特性例であり、例えば、第2信号生成部56の各LPFの特性を図7(a)に示すような比較的カットオフ周波数が高いものとし、その一方で第1信号生成部54の各LPFの特性を図7(b)に示すような比較的カットオフ周波数が低いものとする。また、図7(c)及び(d)はBPFの特性例であり、例えば、第2信号生成部56の各BPFの特性を図7(c)に示すような通過帯域幅が比較的広いものとし、その一方で第1信号生成部54の各BPFの特性を図7(d)に示すような比較的、通過帯周波数が低いものとすることができる。

[0050]

このような特性差を設けることにより、暗電流に起因するショット雑音が露光時間に応じて変化することに好適に対応することが可能となる。すなわち、第1信号生成部54には、図7(b)及び(d)に示すようなノイズ成分に対する減衰能力が比較的高い特性を設定することにより、露光時間が長くなった場合のノイズによる画質劣化が好適に抑制された画像信号が得られる。一方、第2信号生成部56には、図7(a)及び(c)に示すようなノイズ成分に対する減衰能力が比較的低い特性を設定することにより、ノイズ成分が許容される露光時間での撮影条件にて好適な解像度が維持された画像信号が得られる。

このように本装置では、画素補正フィルタ回路 5 2 の有無、及び第 1 信号生成部 5 4 と第 2 信号生成部 5 6 との特性差により、第 1 信号生成部 5 4 及び第 2 信号生成部 5 6 からはノイズの抑制効果及び解像度の異なる画像信号が得られる。そして、それら画像信号を制御部 6 6 が露光条件に連動して混合比率を制御して混合することで、露光条件に応じた好適な画質を実現可能となる。

[0052]

撮像素子 30 に対する露光制御は、画像を明るくするために、例えば、まず露光時間が伸張され、露光時間が上限に達すると次に自動利得制御(AGC: Auto Gain Control)によるアナログ的なゲインを増加させる制御が行われ、そのゲインが上限に達すると、自動デジタルゲイン制御(ADG: Auto Digital Gain control)のゲインを増加させる制御が行われる。制御部 66 は、これら露光時間や各ゲインに基づき、露光制御が現在どの状態にあるかに応じて乗算器 58, 60 にそれぞれ設定される乗算係数を定めるパラメータ Rを変化させる。例えば、露光制御が画像を明るくする側にシフトするほど、暗電流は増加しやすいため、Rを連続的に、又は段階的に増加させる。これにより、ノイズ除去効果の高い第 1 信号生成部 54 側の画像信号の比重が高まり、好適なノイズ抑制効果が期待できる。

[0053]

また、露光制御条件の所定の基準点を境にして、第1信号生成部54側の信号と第2信号生成部56側の信号とが切り替えて出力されるように構成することもできる。さらに、露光制御条件の所定の基準点までは、第2信号生成部56側の画像信号を100%出力し、基準点を超えると上述の連続的又は段階的な混合比率の調整制御を開始するように構成することもできる。

[0054]

上述の構成では、例えば、参照画素は対象点を中心として上下左右に配置される合計 5 画素であったが、参照画素の配置はこれに限られない。また上述の構成では、暗電流に応じて画素値が増加することに対応して、画素値の順位のうち上位の数画素を除去し、残り 2 画素での平均を取る例を示した。しかし、例えば、画素値を負の値で定義する場合には、暗電流の増加に応じて画素値が減少する場合もあり得、その場合には画素値の大小の順位のうち下位の画素を除去するように構成され得る。また、上位下位両方の画素を除去することとしてもよい。その際、例えば、暗電流の増加で画素値が増加する場合には、下位より上位の除去画素数を多くし、逆に暗電流の増加で画素値が減少する場合には、上位よ

り下位の除去画素数を多くすることが、暗電流ノイズの除去に好適である。なお、上位下位の両方を除去することとすれば、一方側の除去で暗電流の影響の大きい画素を除去し、 他方側の除去で例えば信号電荷を生じない欠陥画素を除去して、画質の向上を図ることが 可能である。

### [0055]

ラインメモリ群 5 0 では上述のように、参照画素のうち残す参照画素(残余参照画素)の平均値を求め、これを対象点に割り当てる。当該平均値は実質的に、残余参照画素の座標の重心でのサンプリング値に相当する。以下、当該重心を平均値サンプリング点と称する。なお、ここで各残余参照画素の座標として所定の代表点、例えば当該画素に対応するサンプリング点の位置を用いることができる。

[0056]

残余参照画素の数は、平均値を求めるために2画素以上であることが前提となるが、さらに平均値サンプリング点が、対象点から所定距離内に位置するように配慮して定めることができる。このような配慮により、平均値サンプリング点でのサンプリング値を対象点のサンプリング値とみなすことによる解像度の低下を抑制することが可能となる。

[0057]

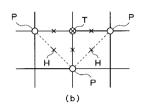

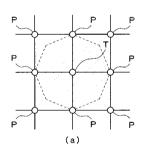

図8~図10は参照画素及び平均値サンプリング点の配置のいくつかの例を示す模式図 である。図において、 印は参照画素のサンプリング点の位置を示し、一方、平均値サン プリング点は×印で示す点、又は斜線を施した領域内に位置する。図8(a)は上述の図 4 (a)の配置及び図5の回路構成の場合に対応するもので、参照画素が5画素かつ残余 参照画素が2画素の場合を示している。また、図8(b)は上述の図4(b)の配置及び 図6の回路構成の場合に対応するもので、参照画素が4画素かつ残余参照画素が2画素の 場合を示している。これらの場合、平均値サンプリング点は、対象点Tを取り囲む参照画 素Pのサンプリング点を結ぶ四角形又は三角形の辺上又はこれら多角形の内側に位置する 。ここで、撮像素子30の垂直方向の画素間隔と水平方向の画素間隔とは基本的にほぼ同 等に設定される。対象点Tから最も遠い平均値サンプリング点である点Hは、点P同士を 結ぶ辺の中間点である。この平均値サンプリング点Hは、対象点の最寄りの参照画素Pよ り対象点Tに近くに位置する。ちなみに、上記の参照画素に対して、従来技術となるメデ ィアンフィルタを適応する場合、対象画素Tを、参照画素のうちの信号レベルの順序が中 央となる画素で置き換えることになる。つまり、対象画素Tが周りのいずれかの参照画素 Pで置き換えられる場合がある。これに対して、本装置では上述したように対象画素Tに 置き換わり得る最も遠い点は、参照画素Pよりも対象画素Tに近い平均値サンプリング点 Hである。すなわち、本装置によれば、メディアンフィルタを用いる場合に比べ、対象画 素Tをより対象画素Tに近い点で置き換えることができる。

[0058]

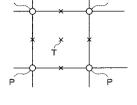

図9は参照画素が4画素で、そのうちの2画素を残余参照画素とする場合を示している。この場合の対象点Tは4つの参照画素Pの重心点とされる。この場合も、平均値サンプリング点は対象点Tを取り囲む参照画素Pのサンプリング点を結ぶ四角形の辺上又は当該多角形の内側に位置する。

[0059]

図10(a)(b)はそれぞれ参照画素が3行3列の画素群である場合である。そして、同図(a)は残余参照画素が3画素の場合であり、この場合、平均値サンプリング点の存在する領域は、対象点Tを取り囲む参照画素Pを結ぶ四角形に接する。一方、同図(b)は残余参照画素が4画素の場合であり、この場合、平均値サンプリング点の存在する領域は、対象点Tを取り囲む参照画素Pを結ぶ四角形より内側に含まれる。

【図面の簡単な説明】

[0060]

【図1】本発明の実施形態である画像信号処理装置の構成を示す概略のブロック図である

【図2】第1信号生成部、第2信号生成部の概略の構成を示すブロック図である。

20

10

30

- 【図3】YC処理部の概略のブロック構成である。

- 【図4】二次元フィルタの処理に用いられる画像領域での画像データの配置及び参照画素の位置の一例を示す模式図である。

- 【図5】画素補正フィルタ回路において5つの参照画素に対して二次元フィルタ処理を行う部分の概略の回路図である。

- 【図 6 】画素補正フィルタ回路において 4 つの参照画素に対して二次元フィルタ処理を行う部分の概略の回路図である。

- 【図7】第1信号生成部、第2信号生成部を構成するLPF,BPFの模式的な通過特性図である。

- 【図8】参照画素及び平均値サンプリング点の配置を示す模式図である。

- 【図9】参照画素及び平均値サンプリング点の他の配置の例を示す模式図である。

- 【図10】参照画素及び平均値サンプリング点の他の配置の例を示す模式図である。

- 【図11】撮像素子により生成された画像信号を処理する従来の画像信号処理装置の構成を示すプロック図である。

## 【符号の説明】

#### [0061]

3 0 撮像素子、3 2 アナログ信号処理回路、3 4 A / D変換回路、3 6 デジタル信号処理回路、4 0 減算器、5 0 ラインメモリ群、5 2 画素補正フィルタ回路、5 4 第 1 信号生成部、5 6 第 2 信号生成部、5 8 , 6 0 乗算器、6 2 , 1 0 2 加算器、6 4 Y C 処理部、6 6 制御部、8 0 L P F 、8 2 輪郭補正信号生成回路、8 4 , 9 4 V L P F 、8 6 , 9 0 H L P F 、8 8 V B P F 、9 6 H B P F 、1 0 0 ガンマ補正回路、1 1 0 , 1 1 4 , 2 0 0 , 2 0 4 ブロック、1 1 2 加算平均回路、1 2 0 , 1 2 2 , 1 2 4 , 1 5 0 , 1 5 2 , 1 5 4 比較器、1 2 6 , 1 2 8 , 1 3 0 , 1 4 0 , 1 4 2 , 1 4 4 , 1 4 6 , 1 5 6 , 1 5 8 , 1 6 0 セレクタ、1 3 2 デコーダ。

【図1】

【図2】

20

# 【図4】

# 【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

# フロントページの続き

(56)参考文献 特開平02-141069(JP,A)

特開2001-069377(JP,A)

特開2001-078085(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 4 N 5 / 2 3 2 H 0 4 N 5 / 2 1 H 0 4 N 5 / 3 3 5 H 0 4 N 9 / 0 7