# (12) UK Patent Application (19) GB (11) 2 238 674(13)A

(43) Date of A publication 05.06.1991

(21) Application No 9021827.2

(22) Date of filing 08.10.1990

(30) Priority data (31) 07418890

(32) 10.10.1989

(33) US

(71) Applicant Teledyne Industries Inc

(Incorporated in the USA - California)

1901 Avenue of the Stars, Los Angeles, California 90067, United States of America

(72) Inventor Ciro Guajardo

(74) Agent and/or Address for Service Haseltine Lake & Co Hazlitt House, 28 Southampton Buildings, Chancery Lane, London, WC2A 1AT, United Kingdom (51) INT CL5 H02M 1/08, H03K 17/722 // H03K 17/725

(52) UK CL (Edition K) H2F FSX F12 F9L3 F91TR

(56) Documents cited **GB 1525701 A** GB 2087172 A GB 2099243 A EP 0144977 A2 US 4339670 A EP 0144978 A2 US 4578596 is equivalent to EP 0144978 US 4578595 is equivalent to EP 0144977

(58) Field of search UK CL (Edition K) H2F FSC FSX INT CL5 HO2M, HO3K

#### (54) Control circuit for SCR AC relay

(57) In a zero voltage switching circuit for controlling current to a serially arranged load 18, AC voltage source 16 and first and second inverse parallel connected photosensitive silicon controlled rectifiers 20, 22 apparatus 24 applies input light signals to enable the first and second photosensitive silicon controlled rectifiers 20, 22, apparatus 36, 38, 40 provides a voltage range within which the photosensitive silicon controlled rectifiers operate and apparatus 60, 62 clamps the gate terminals of each of the photosensitive silicon controlled rectifier's to its cathode in the absence of input light signals to the photosensitive silicon controlled rectifiers, and opens the circuit between the gate and cathode in the presence of input light signals.

FIGURE 1

# IMPROVED ZERO VOLTAGE SWITCHING AC RELAY CIRCUIT

#### Field of the Invention:

This invention relates to relay circuits and, more particularly, to relay circuits which utilize photosensitive silicon-controlled rectifiers as active switching elements which are triggered into conduction only when the value of the AC voltage being controlled is within predetermined limits of zero volts.

#### History of the Prior Art:

5

10

15

20

25

A number of circuits have been devised in the prior art to provide an AC relay consisting of a pair of inverse-parallel-connected photosilicon controlled rectifiers which are triggered into conduction by light emitting diode light sources optically coupled thereto through a transparent dielectric path. The light emitting diodes are in turn energized by an input signal and provide light output to impinge on the photosilicon controlled rectifiers to cause them to conduct and complete an output circuit between an AC power source and a load. Such relay circuits are widely used for the control of AC loads by computer generated logic signals such as are found in microcomputer based control systems. The optical coupling between the input signal circuit and the load circuit provide excellent electrical isolation between the logic signals and the AC loads. In addition, the photosilicon controlled rectifier relay circuit requires few components for its implementation. This simplicity permits the use of hybrid circuit construction techniques to provide solid state AC relay circuits which may be inexpensively mass produced in a very small package size.

For most applications, it is desirable to have an AC relay which switches on only at those points in time when the value of the AC voltage being controlled is

close to zero. This eliminates a great deal of the transient problem which occurs if the relay is switched on at an instant when the AC voltage being controlled has a substantial value. This type of circuit action is known to those skilled in the art as zero voltage switching, although the actual switching action may occur within a range of voltages around zero. In general, circuits of the prior art providing zero voltage switching for AC relays using photosilicon controlled rectifiers possess a large number of components in order to achieve acceptable performance. Such circuits are expensive and thus obviate one of the main benefits of their use. In an effort to provide a zero voltage switching circuit using a minimum number of components, prior art designs have employed a transistor having its collector and emitter connected to the gate and cathode, respectively, of the photosilicon controlled rectifier. The transistor base is connected through a series currentlimiting resistor to the anode of the silicon controlled rectifier so that the anode to cathode voltage of the silicon controlled rectifier controls the transistor. This circuit uses the transistor to clamp the gate to cathode circuit of the photosilicon controlled rectifier whenever the voltage across the silicon controlled rectifier anode-cathode circuit exceeds a predetermined value to prevent the silicon controlled rectifier from being triggered into conduction.

20

25

5

10

15

Unfortunately, the silicon controlled rectifier gate clamping circuit described has the effect of significantly increasing the level of light required to trigger the photosilicon controlled rectifier into conduction. Such an increase requires an increase in the light emitting diode current supplied by the input signal source to the point that prior art AC relay circuits employing zero voltage switching configurations could not be used in such an arrangement and be directly controlled by computer generated logic signals. These computer logic circuits are limited by the amount of current they can supply to drive the input of the AC relay

circuit, so in order to work require additional amplifiers and power drivers to interface the prior art relay circuits to the computer logic.

For this and for other reasons, a new relay circuit including a pair of photosilicon controlled rectifiers connected in inverse parallel to provide full wave control of an AC voltage was devised and described in U.S. Patent No. 4,339,670. This arrangement provides zero voltage switching by using the collector-emitter circuit of a transistor to shunt the gate-cathode circuit of the photosilicon controlled rectifier. The bases of transistors thus used with each silicon controlled rectifier are connected to each other by a single current limiting resistor. The emitter-base breakdown voltage of each transistor sets a predetermined zero voltage switching level and results in a zero voltage switching AC relay circuit which does not require high levels of input current for operation. Such a circuit functions well with computer generated logic signals.

15

10

5

Although this last described circuit provides improved performance, there are certain conditions in which some AC power sources generate abnormal amounts of electrical noise which, even using zero crossing circuitry such as described in the above-mentioned U.S. patent, causes the silicon controlled rectifiers to fail to turn on in response to input signals and cause so-called "dropout" half cycles.

### SUMMARY OF THE INVENTION

It is, therefore, an object of the present invention to provide an improved solid state relay circuit for controlling alternating current loads.

5

It is another object of this invention to provide solid state relay circuits utilizing two photosilicon controlled rectifiers connected in inverse parallel to provide full wave control of an AC voltage and zero voltage switching circuitry which is impervious to transients in the load which might cause half cycle dropouts.

10

L5

20

These and other objects of the invention are realized in a zero voltage switching circuit for controlling current to a serially arranged load and AC voltage source including first and second photosensitive silicon controlled rectifiers each having a gate, anode, and cathode terminals, the anode-cathode terminals being connected in inverse parallel across the load and AC voltage source, means for applying input signals to generate light to enable the first and second photosensitive silicon controlled rectifiers, means for providing a voltage range within which the photosensitive silicon controlled rectifiers operate, means for clamping the gate terminals of each of the photosensitive silicon controlled rectifiers to its cathode in the absence of input light signals to the photosensitive silicon controlled rectifier of each photosensitive silicon controlled rectifier in the presence of input light signals.

25

These and other features and objects of the invention will be better understood by those skilled in the art by reference to the detailed description

which follows taken together with the drawings in which like designation refer to like elements through the several views.

# DETAILED DESCRIPTION OF THE INVENTION

5

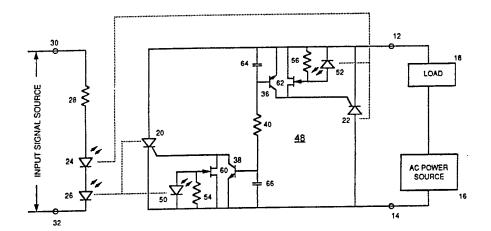

FIGURE 1 illustrates the prior art circuit shown in U.S. Patent No. 4,339,670. In the zero voltage switching AC relay circuit 10, an AC power source 16 and a load 18 are connected in series between output terminals 12 and 14. The function of the circuit 10 is to provide an effectively open circuit between the output terminals 12 and 14 when the relay is not actuated so that the voltage 16 is not applied to the load 18 and to provide an effectively short circuit between the output terminals 12 and 14 when the relay is actuated, allowing AC voltage from the source 16 to be connected through the relay circuit to the load 18.

15

20

10

To accomplish this, a pair of photosilicon controlled rectifiers 20 and 22 are placed in inversed parallel between the terminals 12 and 14 to form a circuit which can conduct current in either direction and is thus suitable for full wave AC control. The two silicon controlled rectifiers 20 and 22 are arranged so that (when conducting) conducting during the positive half cycles of AC power source 16 when the voltage at terminal 12 is positive with respect to the voltage at the terminal 14, the load current flows through the anode-cathode circuit of the photosilicon controlled rectifier 20. Conversely, during the negative half cycles of the AC power source 16, the load current flows through the anode-cathode circuit of the photosilicon controlled rectifier 22.

25

The photosilicon controlled rectifiers 20 and 22 are, respectively, placed in the conducting condition by two light emitting diodes 24 and 26 which are

positioned adjacent to them. The light emitting diodes 24 and 26 are connected in series with a current limiting resistor 28 and an input signal source 34. When the input signal source 34 provides an input signal to the light emitting diodes 24 and 26, they generate light which is optically coupled to the photosilicon rectifiers 20 and 22. This triggers the rectifiers 20 and 22 into conduction providing a full wave conduction path from the AC power source 16 to the load 18. When the input signal source 34 is removed, the rectifiers 20 and 22 are transferred to the non-conducting state by the current reversals of the AC power source 16.

10

5

As so far described, the circuit 10 permits the input signal source 34 to trigger the photosilicon controlled rectifiers 20 and 22 into conduction at any voltage level of AC source 16. To prevent the relay circuit 10 from being switched on when the AC voltage source 16 has a substantial value and transients are a major problem, a zero voltage switching arrangement is provided by transistors 36 and 38 and a current limiting resistor 40. The NPN transistor 36 is connected with its collector and emitter at the gate and cathode, respectively, of the rectifier 20; and the NPN transistor 38 is connected with its collector and emitter at the gate and cathode, respectively, of the rectifier 22.

20

25

15

A photosilicon controlled rectifier device may be rendered non-responsive to input light sources by shunting the gate-cathode circuit through a low impedance path. These low impedance paths are provided by the transistors 36 and 38 when they are biased into conduction. This occurs when the voltage across the AC power source 16 exceeds predetermined voltage limits so that the rectifiers 20 and 22 are prevented from being triggered into conduction except within the predetermined voltage limits. During positive half cycles of the AC power source 16, the voltage across the anode-cathode circuit of the rectifiers 20

and 22 increases to the point where it exceeds the emitter-base breakdown voltage of the transistor 38. This causes bias current to be supplied through the base-emitter junction of the transistor 38 and the resistor 40 to the base of the transistor 36, causing the transistor 36 to conduct. In a like manner, during negative half cycles of the AC power source 16, when the voltage across the anode-cathode circuit of the rectifier 22 exceeds the emitter-base breakdown voltage of the transistor 36 causes bias current to be supplied through the resistor 40 to the base of the transistor 38 causing the transistor 38 to conduct. The typical emitter-base breakdown voltage of NPN transistors 36 and 38 is approximately 9 to 12 volts. Accordingly, placing the resistor 40 between the bases of the transistors 36 and 38 permits the photosilicon controlled rectifiers 20 and 22 to be triggered into conduction for voltages provided by the AC power source 16 ranging between plus and minus 9 to 12 volts.

15

10

5

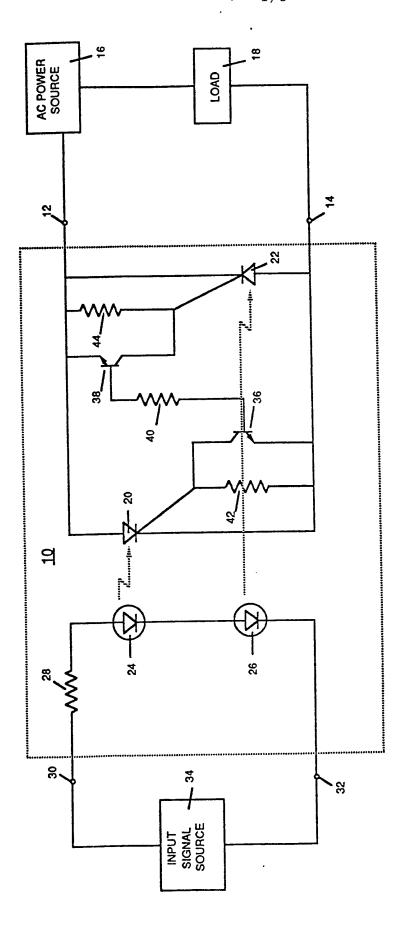

Unfortunately the circuit 10 illustrated in Figure 1 misses certain half cycles of operation when used with some power sources which generate abnormal amounts of electrical noise. The reason for this may be demonstrated by reference to Figure 2 which illustrates a sine wave form of the voltage provided by the power source 16. The equation for the sine wave is given by v=Vmax sine  $(2\pi ft)$ , where V is the instantaneous voltage, Vmax is the maximum peak voltage of the sine wave, F is the frequency of the sine wave, T is the time. Solving for T, T=1/ $2\pi F$  x arc sine of v/Vmax. T is the time in which the relay must turn on before the zero turn-on circuit clamps the rectifiers 20 and 22 of Figure 1.

25

20

As may be seen, T is inversely proportional to both the frequency F and the maximum voltage Vmax. Typical line voltages used with these circuits provides for a maximum voltage of 115 volts at a frequency of 400 Hz, and a window of plus or

minus 12 volts for the switching range so that T equals approximately 30 microseconds. If the relay 10 of Figure 1 does not turn on during this time, it must wait for the next half cycle, causing what is called a dropout.

5

Now, the silicon controlled rectifiers 20 and 22 may be rendered insensitive to noise disturbances by clamping their gate terminals to ground. This obviously cannot be done during the turn-on time during the period of the zero voltage window, so the values for resistors 42 and 44 in the prior art are chosen to be such that the rectifiers 20 and 22 are not easily turned on too. However, apparently a very large amount of noise in the AC power source of the load can render the silicon controlled rectifiers 20 and 22 insensitive to the input light signals so that the dropouts occur. This invention has been devised to eliminate the dropout problem.

15

10

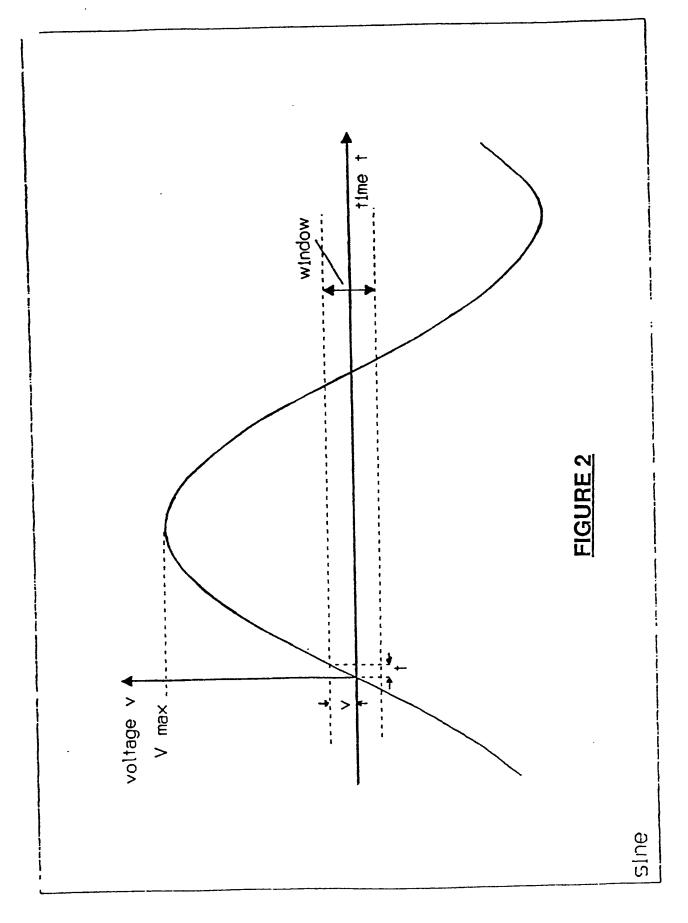

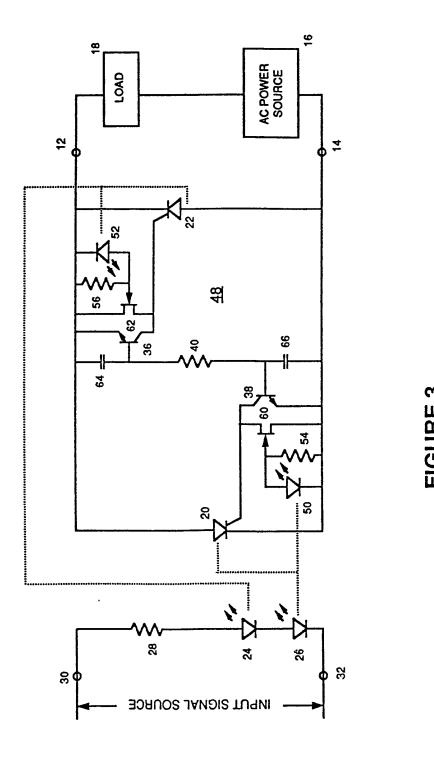

The circuit 48 of Figure 3 is similar to that illustrated in Figure 1 except that the resistor 42 has been replaced by a junction FET transistor 60 having a gate biased by a resistor 54 connected in parallel with an LED 50, the resistor 44 has been replaced by a junction FET transistor 62 having its gate biased by resistor 56 connected in parallel with an LED 52, and capacitors 64 and 66 are connected at opposite sides of the resistor 40 to the output terminals 12 and 14.

20

In the circuit 48 of Figure 3, the junction FET transistors 60 and 62 are normally conducting between source and drain. Thus, during the general operating condition of the circuit, the gates of each of the rectifiers 20 and 22 are essentially directly connected to the cathodes. In the absence of an input signal from the light emitting diodes 24 and 26, neither of the rectifiers 20 or 22 will be influenced by transients in the load to any extent even during the period in which

the load voltage 16 is in the window area. In general, the impedance of the junction FET transistors 60 and 62 is less than 1,000 ohms, while that of the resistors which they replace is typically 25k ohms to 50k ohms.

5

On the other hand, the LEDs 50 and 52 are directly coupled to receive the light from the light emitting diodes 26 and 24, respectively, so that when input signals are provided from the input signal source to the rectifiers 20 and 22, the LEDs 50 and 52 generate a negative voltage at the gate of the respective junction transistors 60 or 62 which turns that transistor off. Turning off the transistor 60, for example, causes the gate of the silicon controlled rectifier 20 to float so that it is essentially an open circuit. This allows the silicon controlled rectifier 20 to turn on only in response to the signal provided by the light emitting diode 26 during the period of the window and entirely eliminates the effect of transients in the output load.

15

10

The transistor 62 operates in a similar manner in response to a negative voltage at its gate provided by the light emitting diode 52 to turn off the transistor 62 and provide an infinite impedance at the gate terminal of the silicon controlled rectifier 22 during the negative half cycles of the AC power source 16.

20

25

The transistors 36 and 38 respond in the same manner (as in Figure 1) to the provision of current through the resistor 40 and the base-emitter junction of the transistors 36 or 38 to provide the limiting window so that zero voltage switching may occur. The capacitors 64 and 66 are arranged to bypass high frequency transients so that the transistors 36 and 38 will not turn on and clamp the gate terminals of the silicon controlled rectifiers 22 and 20 prematurely.

The circuit of this invetion essentially eliminates dropy-outs. It has been found that the new circuit illustrated in Figure 3 is much less sensitive to transient noise, even in the zero voltage window area in the absence of input signals from the LEDs 24 and 26 because of the better clamping provided by the junction FETs 60 and 62. Moreover, the silicon controlled rectifiers 20 and 22 have better maximum sensitivity because the junction FETs 60 and 62 provide a virtually open circuit in the presence of input signals provided by the LEDs 26 and 24 coupled through the LEDs 50 and 52. Moreover, the interference of high frequency premature clamping has been minimized by means of the bypass capacitors 66 and 64.

Although the relay circuit of this invention has been disclosed in the presently preferred embodiment, it will be obvious to those skilled in the art that various modifications and variations may be made without departing from the spirit and scope of the invention. It is therefore intended that the invention be defined only in terms of the claims which follow.

# WHAT IS CLAIMED IS:

arranged load and AC voltage source comprising first and second photosensitive silicon controlled rectifiers each having a gate, anode, and cathode terminals, the anode-cathode terminals being arranged to be connected in inverse parallel across the load and AC voltage source, means for applying input signals to generate light to enable the first and second photosensitive silicon controlled rectifiers, means for providing a voltage range within which the photosensitive silicon controlled rectifiers operate, means for clamping the gate terminals of each of the photosensitive silicon controlled rectifiers to its cathode in the absence of input light signals to the photosensitive silicon controlled rectifiers, and means for opening the circuit between the gate and rectifier of each photosensitive silicon controlled rectifier in the presence of input light signals.

15

10

5

2. A zero voltage switching circuit as claimed in Claim 1 in which the means for providing a voltage range within which the photosensitive silicon controlled rectifiers operate comprises means for clamping the gate terminal of the first photosensitive silicon controlled rectifier to its cathode in response to preselected positive AC voltages provided by the AC voltage source, and means for clamping the gate terminal of the second photosensitive silicon controlled rectifier to its cathode in response to preselected negative AC voltages provided by the AC voltage source.

- 3. A zero voltage switching circuit as claimed in Claim 2 in which the means for clamping the gate terminal of the first photosensitive silicon controlled rectifier to its cathode in response to preselected positive AC voltages provided by the AC voltage source and the means for clamping the gate terminal of the second photosensitive silicon controlled rectifier to its cathode in response to preselected negative AC voltages provided by the AC voltage source each comprise a resistance, and one of a pair of junction transistors each having its emitter and base terminals connected between the gate and cathode of the associated photosensitive silicon controlled rectifier and its base terminal connected through the resistance to the the base terminal of the other junction transistor.

- 4. A zero voltage switching circuit as claimed in Claim 3 further comprising a pair of capacitors, each connecting the base terminal of one of the junction transistors to the cathode of the associated photosensitive silicon controlled rectifier.

- 5. A zero voltage switching circuit as claimed in Claim 1 in which the means for clamping the gate terminals of each of the photosensitive silicon controlled rectifiers to its cathode in the absence of input light signals to the photosensitive silicon controlled rectifiers comprises a pair of junction field effect transistors each having its source and drain terminals connecting the gate and cathode terminals of one of the photosensitive silicon controlled rectifiers.

20

5

10

- 6. A zero voltage switching circuit as claimed in Claim 5 in which the means for opening the circuit between the gate and rectifier of each photosensitive silicon controlled rectifier in the presence of input light signals comprises a light emitting diode connected between the gate and source terminals of the junction field effect transistor associated with one of the photosensitive silicon controlled rectifier and coupled to receive the light actuating the associated photosensitive silicon controlled rectifier.

- 7. A zero voltage switching circuit as claimed in Claim 6 in which the means for providing a voltage range within which the photosensitive silicon controlled rectifiers operate comprises means for clamping the gate terminal of the first photosensitive silicon controlled rectifier to its cathode in response to preselected positive AC voltages provided by the AC voltage source, and means for clamping the gate terminal of the second photosensitive silicon controlled rectifier to its cathode in response to preselected negative AC voltages provided by the AC voltage source.

- 8. A zero voltage switching circuit as claimed in Claim 7 in which the means for clamping the gate terminal of the first photosensitive silicon controlled rectifier to its cathode in response to preselected positive AC voltages provided by the AC voltage source and the means for clamping the gate terminal of the second photosensitive silicon controlled rectifier to its cathode in response to preselected negative AC voltages provided by the AC voltage source each comprise a resistance, and one of a pair of junction transistors each having its emitter and base terminals connected between the gate and cathode of the associated photosensitive silicon controlled rectifier and its base terminal

25

20

.

5

10

connected through the resistance to the base terminal of the other junction transistor.

- 9. A zero voltage switching circuit as claimed in Claim 8 further comprising a pair of capacitors, each connecting the base terminal of one of the junction transistors to the cathode of the associated photosensitive silicon controlled rectifier.

- 10. A zero voltage switching circuit, substantially as

10 herein described with reference to, and as shown in, Figure 3

of the accompanying drawings.

15

5

20