## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5496548号 (P5496548)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

| (51) Int.Cl. | F 1                           |                     |

|--------------|-------------------------------|---------------------|

| GO6F 13/32   | (2006.01) GO6F                | F 13/32             |

| GO6F 13/28   | (2006.01) GO6F                | F 13/28 3 1 O P     |

| HO4N 5/76    | <b>(2006.01)</b> HO4N         | N 5/76 A            |

| HO4N 7/173   | ( <b>2011.01</b> ) HO4N       | N 7/173 630         |

| HO4B 1/16    | ( <b>2006.01</b> ) HO4B       | 3 1/16 Z            |

|              |                               | 請求項の数 9 (全 37 頁)    |

| (21) 出願番号    | 特願2009-130939 (P2009-130939)  | (73) 特許権者 302062931 |

| (22) 出願日     | 平成21年5月29日 (2009.5.29)        | ルネサスエレクトロニクス株式会社    |

| (65) 公開番号    | 特開2010-277434 (P2010-277434A) | )                   |

| (43) 公開日     | 平成22年12月9日 (2010.12.9)        | (74) 代理人 100089071  |

| 審査請求日        | 平成24年2月27日 (2012.2.27)        | 弁理士 玉村 静世           |

|              |                               | (72) 発明者   阿部   博茂  |

|              |                               | 東京都千代田区大手町二丁目6番2号 株 |

|              |                               | 式会社ルネサステクノロジ内       |

|              |                               | (72) 発明者 望月 勇       |

|              |                               | 東京都千代田区大手町二丁目6番2号 株 |

|              |                               | 式会社ルネサステクノロジ内       |

|              |                               | (72) 発明者 水谷 美加      |

|              |                               | 東京都千代田区大手町二丁目6番2号 株 |

|              |                               | 式会社ルネサステクノロジ内       |

|              |                               |                     |

|              |                               | 最終頁に続く              |

# (54) 【発明の名称】半導体集積回路

# (57)【特許請求の範囲】

# 【請求項1】

受信インターフェースと、メモリインターフェースと、データ転送ユニットと、処理ユニットとを具備する半導体集積回路であって、

前記受信インターフェースは、複数の受信パケットデータを逐次に蓄積可能なバッファと、計数動作を行うタイマとを含むものであり、

前記メモリインターフェースは、外部メモリと接続可能とされており、

前記データ転送ユニットは、前記バッファに蓄積される前記複数の受信パケットデータを、前記メモリインターフェースに接続される前記外部メモリに転送可能とされており、

前記処理ユニットは、前記外部メモリに転送され格納される前記複数の受信パケットデータを処理可能とされており、

前記データ転送ユニットが所定のパケット数の前記複数の受信パケットデータの前記バッファから前記外部メモリへのデータ転送を完了すると、前記データ転送ユニットはデータ転送完了割り込みを前記処理ユニットに通知可能とされており、

前記データ転送ユニットからの前記データ転送完了割り込みの発生に応答して、前記処理ユニットは前記外部メモリに格納された前記複数の受信パケットデータの<u>第1</u>処理を開始可能とされたものであり、

前記受信インターフェースへの前記複数の受信パケットデータの受信中断<u>により</u>、前記タイマは前記計数動作を実行するものであり、

前記受信中断による前記計数動作による所定のカウント時間の間に前記所定のパケット

数を有した前記複数の受信パケットデータの前記データ転送が未完了の場合には、前記タイマはタイマ割り込みを前記処理ユニットに通知可能とされており、

前記タイマからの前記タイマ割り込みの発生に応答して、前記処理ユニットは前記受信中断の前に前記外部メモリに格納された受信パケットデータの<u>第2</u>処理を開始可能とされたものであり、

前記受信インターフェースは、前記データ転送ユニットによる前記外部メモリに転送済みの受信パケットデータの転送パケット数を格納するパケットカウンタ更に含むものであり、

前記データ転送完了割り込みの<u>前記</u>発生に応答して前記処理ユニットが前記外部メモリに格納された前記複数の受信パケットデータの<u>前記第1</u>処理を開始する以前に、前記処理ユニットは前記パケットカウンタから前記転送パケット数を取得可能とされたものであり

前記タイマ割り込みの<u>前記</u>発生に応答して、前記処理ユニットが前記受信中断の前に前記外部メモリに格納された前記受信パケットデータの<u>前記第2</u>処理を開始する以前に、前記処理ユニットは前記パケットカウンタから前記転送パケット数を取得可能とされたものであり、

前記処理ユニットによる前記パケットカウンタからの前記転送パケット数の取得の後に、前記パケットカウンタの値はゼロにリセットされるものであり、

前記受信中断の後の受信再開後に、前記パケットカウンタは前記データ転送ユニットにより前記外部メモリに転送再開される再開受信パケットデータの転送再開パケット数を格納するものであり、

前記受信中断の前に前記外部メモリに格納された前記受信パケットデータの前記転送パケット数を、前記タイマ割り込みの前記発生に応答して、前記処理ユニットが前記パケットカウンタから取得した後に、前記データ転送完了割り込みの前記発生が生じるものであり、

前記タイマ割り込みの前記発生に応答して前記処理ユニットが前記パケットカウンタから取得した前記転送パケット数<u>の大きさ</u>に従って、前記外部メモリに格納された前記受信パケットデータの前記タイマ割り込みの前記発生に応答する前記<u>第2</u>処理もしくは前記外部メモリに格納された前記複数の受信パケットデータの前記データ転送完了割り込みの前記発生に応答する前記第1処理のいずれかの処理の実行が省略され、

前記タイマ割り込みの前記発生に応答して前記処理ユニットが前記パケットカウンタから取得した前記転送パケット数が前記所定のパケット数よりも小さい場合には、前記受信中断の前に前記外部メモリに格納された前記受信パケットデータの前記タイマ割り込みの前記発生に応答する前記第2処理の実行が省略される一方、前記外部メモリに格納された前記複数の受信パケットデータの前記データ転送完了割り込みの前記発生に応答する前記第1処理が実行されるものであり、

前記タイマ割り込みの前記発生に応答して前記処理ユニットが前記パケットカウンタから取得した前記転送パケット数が前記所定のパケット数と等しい場合には、前記受信中断の前および前記受信再開後に前記外部メモリに格納された前記受信パケットデータの前記タイマ割り込みの前記発生に応答する前記第2処理が実行される一方、前記外部メモリに格納された前記複数の受信パケットデータの前記データ転送完了割り込みの前記発生に応答する前記第1処理の実行が省略されることを特徴とする半導体集積回路。

## 【請求項2】

<u>前記処理ユニットは中央処理ユニットを含み、前記データ転送ユニットはダイレクトメ</u> モリアクセスコントローラである請求項 1 に記載の半導体集積回路。

## 【請求項3】

前記受信インターフェースは、MPEGのトランスポートストリームの形態である複数の受信パケットデータを受信可能とされている請求項2に記載の半導体集積回路。

## 【請求項4】

前記処理ユニットの前記中央処理ユニットは前記MPEGのトランスポートストリーム

10

30

20

40

の形態で前記外部メモリに格納された前記複数の受信パケットデータをデマルチプレック スの処理よって映像および音声のエレメンタリー・ストリームに分離するものである請求 項3に記載の半導体集積回路。

## 【請求項5】

前記処理ユニットは、MPEGデコーダと、表示制御装置と、音声出力制御部とを更に 含み、

前記中央処理ユニットによって分離された前記映像および音声のエレメンタリー・ストリームは、前記MPEGデコーダによって映像再生信号と音声再生信号とに復号化され、前記映像再生信号の出力同期が前記表示制御装置で実行され、前記音声再生信号の出力同期が前記音声出力制御部で実行されるものである請求項4に記載の半導体集積回路。

#### 【請求項6】

前記データ転送完了割り込みの優先度は前記タイマ割り込みの優先度よりも高く設定されたものである請求項1乃至請求項5のいずれかに記載の半導体集積回路。

## 【請求項7】

<u>入力インターフェースと、第1処理ユニットと、第2処理ユニットとを具備する半導体</u> 集積回路であって、

<u>前記入力インターフェースは、複数の入力パケットデータを逐次に蓄積可能なバッファ</u>と、計数動作を行うタイマとを含むものであり、

前記第1処理ユニットは前記バッファに蓄積される前記複数の入力パケットデータを処理可能とされ、前記第2処理ユニットは前記第1処理ユニットの処理結果を処理可能とされており、

前記第1処理ユニットが所定のパケット数の前記複数の入力パケットデータを前記バッファから読み出して、前記第1処理ユニットが読み出しデータの第1処理を完了すると、前記第1処理ユニットは第1処理完了割り込みを前記第2処理ユニットに通知可能とされており、

前記第1処理ユニットからの前記第1処理完了割り込みの発生に応答して、前記第2処理ユニットは前記第1処理ユニットの前記処理結果の第2処理を開始可能とされたものであり、

前記入力インターフェースへの前記複数の入力パケットデータの入力中断により、前記 タイマは前記計数動作を実行するものであり、

前記入力中断による前記計数動作による所定のカウント時間の間に前記所定のパケット数を有した前記複数の入力パケットデータの前記第1処理が未完了の場合には、前記タイマはタイマ割り込みを前記第2処理ユニットに通知可能とされており、

前記タイマからの前記タイマ割り込みの発生に応答して、前記第2処理ユニットは前記入力中断の前に前記第1処理ユニットによって前記第1処理に関して処理された処理済みデータの前記第3処理を開始可能とされたものであり、

前記入力インターフェースは、前記第1処理ユニットによって前記第1処理に関して処理された処理済みデータの処理済みパケット数を格納するパケットカウンタを更に含むものであり、

前記第1処理完了割り込みの前記発生に応答して前記第2処理ユニットが前記第2処理 を開始する以前に、前記第2処理ユニットは前記パケットカウンタから前記処理済みパケット数を取得可能とされたものであり、

前記タイマ割り込みの前記発生に応答して、前記第2処理ユニットが前記入力中断の前に前記第2処理ユニットが前記第3処理を開始する前に前記第1処理ユニットによって処理された前記処理済みデータの処理済みパケット数を前記パケットカウンタから取得可能とされたものであり、

<u>前記第2処理ユニットによる前記パケットカウンタからの前記処理済みパケット数の取</u>得の後に、前記パケットカウンタの値はゼロにリセットされるものであり、

<u>前記入力中断の後の入力再開後に、前記パケットカウンタは入力再開される再開入力パ</u>ケットデータの入力再開パケット数を格納するものであり、

10

20

30

40

前記タイマ割り込みの前記発生に応答して、前記入力中断の前に入力された前記入力パケットデータの前記パケット数を、前記第2処理ユニットが前記パケットカウンタから取得した後に、前記第1処理完了割り込みの前記発生が生じるものであり、

前記タイマ割り込みの前記発生に応答して前記第2処理ユニットが前記パケットカウンタから取得した前記処理済みパケット数の大きさに従って、前記第1処理ユニットによって処理された前記処理済みデータの前記第2処理ユニットによる前記タイマ割り込みの前記発生に応答する前記第3処理もしくは前記第1処理ユニットによって処理された前記処理済みデータの前記第2処理ユニットによる前記第1処理完了割り込みの前記発生に応答する前記第2処理のいずれかの処理の実行が省略され、

前記タイマ割り込みの前記発生に応答して前記第 2 処理ユニットが前記パケットカウンタから取得した前記処理済みパケット数が前記所定のパケット数よりも小さい場合には、前記入力中断の前に前記第 1 処理ユニットによって処理された前記処理済みデータの前記第 2 処理ユニットによる前記タイマ割り込みの前記発生に応答する前記第 3 処理の実行が省略される一方、前記第 1 処理ユニットによって処理された前記処理済みデータの前記第 2 処理ユニットによる前記第 1 処理完了割り込みの前記発生に応答する前記第 2 処理が実行されるものであり、

前記タイマ割り込みの前記発生に応答して前記第 2 処理ユニットが前記パケットカウンタから取得した前記処理済みパケット数が前記所定のパケット数と等しい場合には、前記入力中断の前および前記入力再開後に前記第 1 処理ユニットによって処理された前記処理済みデータの前記第 2 処理ユニットによる前記タイマ割り込みの前記発生に応答する前記第 3 処理が実行される一方、前記第 1 処理ユニットによって処理された前記処理済みデータの前記第 2 処理ユニットによる前記第 1 処理完了割り込みの前記発生に応答する前記第 2 処理の実行が省略されることを特徴とする半導体集積回路。

#### 【請求項8】

前記第2処理ユニットは中央処理ユニットを含み、前記第1処理ユニットは他の処理ユニットを含むものである請求項7に記載の半導体集積回路。

71

## 【請求項9】

前記第1処理完了割り込みの優先度は前記タイマ割り込みの優先度よりも高く設定されたものである請求項7乃至請求項8のいずれかに記載の半導体集積回路。

【発明の詳細な説明】

# 【技術分野】

## [0001]

本発明は、半導体集積回路に関し、特に複数の割り込み要因に対する処理での重複処理の矛盾を解消する際の負担を軽減するのに有効な技術に関するものである。

#### 【背景技術】

# [0002]

2006年4月1日、日本国内で移動端末等を主たる対象とした地上デジタルテレビ放送の1セグメント部分受信サービス「ワンセグ」が開始された。ワンセグでは、地上デジタルテレビ放送の13チャンネル~62チャンネルまでの物理チャンネルの1チャンネル当たりの周波数帯域6MHzを13セグメントに分割した1つのセグメントを使用して放送することで、情報量を必要最小限に制限している。従って、移動端末等の情報処理能力が比較的小さな端末でも、適切な受信が可能とされる。特徴としては、映像、音声以外にデータ放送を同時に受信可能なものである。

#### [0003]

ISDB-Tmmと呼ばれる次世代ワンセグ放送は、ワンセグよりも、高画質・高音質のストリーム放送だけではなく、映像コンテンツのダウンロード・サービス等の新しいサービスの実現を目指している。尚、ISDB-Tmmは、Integrated Service Digital Broadcasting-Terrestrial for mobile multimediaの略である。

## [0004]

50

10

20

30

移動端末向けの地上ディジタル・テレビ放送では、動画像符号化の国際規格MPEG-2に準拠したトランスポートストリームTS(Transport Steam)が使用されて、このMPEG-2に準拠したトランスポートストリームTSの1つのパケットは188バイトのビットストリームデータによって構成される。

## [0005]

一方、下記特許文献1には、携帯電話機に搭載されて、ディジタル・テレビ放送を受信するディジタル・テレビチューナーから出力されるMPEG2-トランスポートストリーム(以下、MPEG2-TSと言う)を処理するアプリケーションCPUが記載されている。アプリケーションCPU外部には記憶部が接続可能とされ、アプリケーションCPU内部にCPUコアに代わって外部の記憶部と内部の制御部との間のデータ転送を実行するDMACが含まれている。尚、DMACは、ダイレクトメモリアクセスコントローラ(Direct Memory Access Controller)の略である。DMACは設定されたデータ量のデータ転送が完了するとDMAC転送完了割り込みをCPUコアに供給して、このDMAC転送完了割り込みに応答してCPUコアは内部の制御部の処理を開始するものである。

【先行技術文献】

【特許文献】

[0006]

【特許文献 1 】特開 2 0 0 7 - 2 0 1 9 8 3 号 公報

【発明の概要】

【発明が解決しようとする課題】

[0007]

本発明者等は、本発明に先立って、上述したISDB-Tmmと呼ばれる次世代ワンセグ放送を受信可能な携帯電話機端末に搭載されるアプリケーションプロセッサと呼ばれる 半導体集積回路の開発に従事した。

[00008]

このISDB-Tmmと呼ばれる次世代ワンセグ放送では、映像コンテンツのダウンロード・サービスに対応することが必要なことから、標準ワンセグ放送と比較して、次世代ワンセグ放送のMPEG2-TSのビットレートが非常に高くなることが予想された。

[0009]

一方、本発明に先立った開発において本発明者等によって検討されたアプリケーションプロセッサでも、上記特許文献 1 に記載のように、ダイレクトメモリアクセスコントローラ(DMAC)の内蔵が検討された。この内蔵 DMACは、外部デジタルテレビチューナーと外部メモリとの間のデータ転送を内蔵 CPUの低い負荷状態で実行するものである。MPEG2-TSの1つのパケットの外部デジタルテレビチューナーから外部メモリへのデータ転送が完了した時点で、DMAC転送完了割り込みをダイレクトメモリアクセスコントローラ(DMAC)が内蔵 CPUに供給するものである。

[0010]

一方、標準ワンセグ放送と比較して次世代ワンセグ放送のMPEG2-TSのビットレートが非常に高くなることによって、次世代ワンセグ放送の受信時でのアプリケーションプロセッサの内蔵DMACから内蔵CPUへのDMAC転送完了割り込み間隔が短くなり、内蔵CPUの負荷が増加すると言う問題が本発明者等による検討によって明らかとされた。

[0011]

標準ワンセグ放送のMPEG2-TSの最大ビットレートが624kbpsの場合にMPEG2-TSの1つのパケットのデータ転送の完了の時点でDMAC転送完了割り込みを発生すると想定すると、DMAC転送完了割り込み間隔は、2.4msecとなる。それに対して、ISDB-Tmmの次世代ワンセグ放送の最大ビットレートが7Mbpsの場合にMPEG2-TSの1つのパケットのデータ転送の完了の時点でDMAC転送完了割り込みを発生すると想定すると、DMAC転送完了割り込み間隔は、214µsecと短くなるものである。

10

20

30

40

#### [0012]

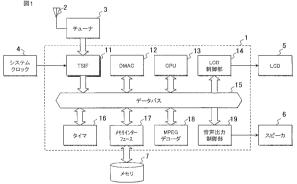

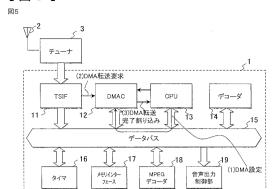

図1は、本発明に先立って本発明者等によって検討されたアプリケーションプロセッサの構成を示す図である。

## [0013]

図 1 に示したアプリケーションプロセッサ 1 は、トランスポートストリームインターフェース(以下、TSIFと言う) 1 1、ダイレクトメモリアクセスコントローラ(以下、DMACと言う) 1 2、中央処理ユニット(以下、CPUと言う) 1 3、液晶表示(以下、LCDと言う)制御部 1 4、データバス 1 5 を含んでいる。更に、アプリケーションプロセッサ 1 は、タイマ 1 6、メモリインターフェース 1 7、MPEGデコーダ 1 8、音声出力制御部 1 9 を含んでいる。

## [0014]

携帯電話端末に搭載されるデジタルテレビアンテナ2によってISDB-Tmmの次世代ワンセグ放送が受信され、外部デジタルテレビチューナー3の出力端子からアプリケーションプロセッサ1のTSIF11の入力端子にMPEG2-TSのパケットデータが供給される。外部のシステムクロック発生器4からTSIF11に、基準クロックとしてのシステムクロック信号が供給される。

#### [0015]

TSIF11に供給されたMPEG2-TSのパケットデータは、内蔵DMAC12によって実行されるDMA転送によってデータバス15とメモリインターフェース17とを介して外部のメモリ7に転送される。外部メモリ7としては、高速・大容量の同期DRAMが使用可能である。

#### [0016]

内蔵 C P U 1 3 は、アプリケーションプロセッサ 1 の内部動作の制御を実行する。内蔵 C P U 1 3 によるデマルチプレックス (D E M U X )処理の制御によって、外部メモリ 7 に蓄積された M P E G 2 - T S のパケットデータは、映像エレメンタリー・ストリームと音声エレメンタリー・ストリームとに分離される。分離された映像エレメンタリー・ストリームと 6 テコーダ 1 8 によって映像再生信号と音声再生信号とに復号化される。映像再生信号の出力同期が L C D 制御部 1 4 で実行され、音声再生信号の出力同期が音声出力制御部 1 9 で実行され、外部の液晶表示装置 (以下、L C D と言う) 5 と外部のスピーカ 6 とによって映像表示と音声出力とが可能となる。

# [0017]

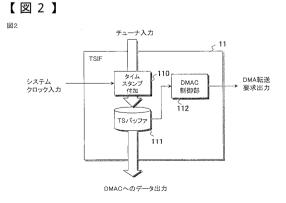

図 2 は、図 1 に示したアプリケーションプロセッサ 1 に含まれるトランスポートストリームインターフェース(TSIF) 1 1 の構成を示す図である。

# [0018]

図 2 に示す T S I F 1 1 は、タイムスタンプ付加部 1 1 0 と、 T S (トランスポートストリーム) バッファ 1 1 1 と、 D M A C 制御部 1 1 2 によって構成されている。

## [0019]

タイムスタンプ付加部110は、外部デジタルテレビチューナー3の出力端子から供給されるMPEG2・TSのパケットデータに外部のシステムクロック発生器4から供給される基準クロックとしてのシステムクロック信号から生成したタイムスタンプを付加するものである。タイムスタンプ付加部110の出力から生成されるタイムスタンプが付加されたMPEG2・TSはTSバッファ111に一時的に蓄積された後にDMAC制御部112に供給されて、DMAC制御部112はTSバッファ111でのMPEG2・TSのデータ蓄積量によってDMAC12にDMAC転送要求を出力するように構成されている。尚、デジタルテレビ放送のデータフォーマットとして使用されているMPEG2・TSは、1パケットが188バイトで構成されている。タイムスタンプ付加部110は188バイトで構成された1パケットのMPEG2・TSを受信すると、4バイトのタイムスタンプ情報を1パケットのMPEG2・TSに付加して192バイトのタイムスタンプトランスポートストリーム(TTS: Timestamp Transport Stream)を生成する。

10

20

30

40

20

30

50

## [0020]

TSバッファ111は、タイムスタンプ付加部110で生成されたタイムスタンプトランスポートストリーム(TTS)を蓄積するために小容量メモリで構成される。例えば、TSバッファ111は、192バイトの2面の内蔵RAM、もしくは192バイトの4面の内蔵RAMによって構成されることが可能である。

#### [0021]

DMAC制御部112は、TSバッファ111におけるMPEG2-TSのデータ蓄積量によりDMAC12にDMAC転送要求を出力するように構成されている。例えば、192バイトで構成された1パケットのタイムスタンプトランスポートストリーム(TTS)がTSバッファ111に蓄積されると、DMAC制御部112はDMAC12にDMAC転送要求を出力する。

[0022]

ところで、携帯電話機端末によってISDB-Tmm等の次世代ワンセグ放送を受信する場合には、電波状態が変化するので、電波の受信可能な状態(強電界)と電波の受信不可能な状態(弱電界)が生じることがある。携帯電話機端末が次世代ワンセグ放送のMPEG2-TSを逐次的に受信していれば、TSバッファ111が空になることはないが、弱電界になるとMPEG2-TSを受信できずにTSバッファ111が空となる可能性が高い

#### [0023]

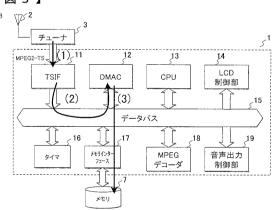

図 3 は、図 1 に示したアプリケーションプロセッサ 1 の内部での M P E G 2 - トランスポートストリーム(M P E G 2 - T S)の流れを説明する図である。

#### [0024]

外部デジタルテレビチューナー 3 にて受信された M P E G 2 - T S はフロー(1)によって T S I F 1 1 に供給されて、フロー(2)によって T S I F 1 1 から D M A C 1 2 に D M A 転送されて、フロー(3)によって D M A C 1 2 から外部メモリ 7 に D M A 転送されるものである。

#### [0025]

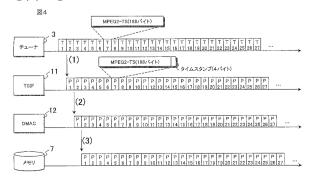

図 4 は、図 3 に示したMPEG2-TSの流れを図 1 に示したアプリケーションプロセッサ 1 の外部デジタルテレビチューナー 3 、TSIF 1 1 、DMAC 1 2 、外部メモリ 7 の各点で観測した図である。

[0026]

外部デジタルテレビチューナー 3 で受信された M P E G 2 - T S は 1 パケット 1 8 8 バイトの構成であり、フロー(1)によりチューナー 3 から T S I F 1 1 に供給される。

[0027]

TSIF11では1パケット188バイトの構成のMPEG2-TSに4バイトのタイムスタンプ情報が付加されて、192バイトのタイムスタンプトランスポートストリーム(TTS)が生成されて、フロー(2)によってTSIF11からDMAC12にDMA転送される。

[0028]

DMAC12に供給されたタイムスタンプトランスポートストリーム(TTS)は、フロ  $^{40}$  -(3)によって外部メモリ7に DMA 転送される。

[0029]

図4に示したMPEG2-TSの流れを形成するフロー(1)とフロー(2)とフロー(3)とは、パイプラインデータ転送処理フローとなっている。すなわち、外部デジタルテレビチューナー3、TSIF11、DMAC12、外部メモリ7の各処理部は、1パケットのデータ受信処理の後に次の処理部へ1パケットのデータ送信処理を実行する。従って、弱電界等の理由によりTSIF11がMPEG2-TSを受信できなければ、TSIF11からDMAC12にDMA転送によってデータが転送されることはない。

## [0030]

図5は、図1に示したアプリケーションプロセッサ1の内部のMPEG2-TSの流れ

の制御を説明する図である。

# [0031]

最初の(1) D M A 設定では、 D M A C 1 2 が T S I F 1 1 から外部メモリ 7 に D M A 転送されるデータのバイト数を C P U 1 3 の D M A 制御処理部 1 3 1 が D M A C 1 2 に設定するものである。

#### [0032]

次に(2) D M A 転送要求では、TSIF11から外部メモリ7へのDMA転送をTSIF11がDMAC12に要求するための信号が生成される。

## [0033]

最後の(3) DMA転送完了割り込みでは、上述の(1) DMA設定にて設定されたバイト数分の DMA転送が完了すると、 DMAC12はCPU13の DMA制御処理部131に DMA転送完了を通知して、 CPU13への割り込みが開始される。

#### [0034]

図6は、強電界の場合でのMPEG2-TSの流れの制御を図1に示したアプリケーションプロセッサ1のTSIF11、DMAC12、CPU13、外部メモリ7の各点で詳細に観測した図である。

## [0035]

最初にCPU13のDMA制御処理部131は、DMAC12に上述の(1)DMA設定を実行する。すると、DMAC12は、TSIF11からのDMAC転送要求を待っている状態となる。

#### [0036]

次に、TSIF11のTSバッファ111へのMPEG2-TSの最初のパケットP1の受信が完了すると、TSIF11はDMAC12に(2)DMA転送要求を出力する。

#### [0037]

次に、DMAC12は上述の(2)DMA転送要求に応答してTSIF11のTSバッファ111に一時的に格納された最初のパケットP1を読み出して、外部メモリ7へのDMA転送を実行する。

## [0038]

次に、DMAC12はCPU13のDMA制御処理部131に上述の(3)DMA転送完了割り込みを通知して、このDMA転送完了割り込みの通知に応答してCPU13のTS解析データ処理部132はトランスポートストリーム解析とデータ処理とによる(4)デコード処理を実行する。

#### [0039]

このようにして2番目のパケットP2から5番目のパケットP5までのMPEG2-TSに関して、TSIF11のTSバッファ111へのパケット受信とパケット読み出しとDMAC12による外部メモリ7へのDMA転送とによって上述の(1)DMA設定で設定されたサイズのバイト数のDMA転送データの転送が完了する。更に2番目のパケットP2から5番目のパケットP5までのMPEG2-TSに関して、CPU13によるデコード処理も完了する。また更にMPEG2-TSの後続のパケットP6~P10に関しても、上述と同様な処理が繰り返される。

# [0040]

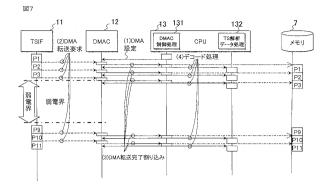

図7は、弱電界の場合でのMPEG2-TSの流れの制御を図1に示したアプリケーションプロセッサ1のTSIF11、DMAC12、CPU13、外部メモリ7の各点で詳細に観測した図である。

#### [0041]

図 7 では、弱電界の前の強電界の間に図 6 と同様に 1 番目のパケット P 1 から 3 番目のパケット P 3 までのM P E G 2 - T S に関して、 T S I F 1 1 の T S バッファ 1 1 1 へのパケット受信とパケット読み出しと D M A C 1 2 による外部メモリ 7 への D M A 転送が完了する。

# [0042]

10

20

30

すなわち、図7でも図6と同様に、最初にCPU13のDMA制御処理部131は、DMAC12に上述の(1)DMA設定を実行する。するとDMAC12は、TSIF11からのDMAC転送要求を待っている状態となる。次に、TSIF110のTSバッファ111000TS00TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10TS10T

#### [0043]

次に図7でも、DMAC12は上述の(2)DMA転送要求に応答してTSIF11のTSバッファ111に一時的に格納された最初のパケットP1を読み出して、外部メモリ7へのDMA転送を実行する。次に、DMAC12はCPU13のDMA制御処理部131に上述の(3)DMA転送完了割り込みを通知するので、この割り込の通知に応答してCPU13のTS解析データ処理部132はトランスポートストリーム解析とデータ処理とによる(4)デコード処理を実行する。

#### [0044]

このようにして2番目のパケットP2から3番目のパケットP3までのMPEG2-TSに関して、TSIF11のTSバッファ111へのパケット受信とパケット読み出しとDMAC12による外部メモリ7へのDMA転送によって上述の(1)DMA設定で設定されたサイズのバイト数のDMA転送データの転送が完了する。更に2番目のパケットP2から3番目のパケットP3までのMPEG2-TSに関して、CPU13によるデコード処理も完了する。

# [0045]

しかし、図 7 の弱電界では、 4 番目のパケット P 4 から 8 番目のパケット P 8 までの M P E G 2 - T S は受信されない。従って、この弱電界の期間では、 T S I F 1 1 は D M A C 1 2 に(2) D M A 転送要求を出力することができない。

#### [0046]

その後、弱電界から強電界に復帰して、9番目のパケットP9以降のMPEG2-TSのパケットの受信を開始すると、TSIF11はDMAC12に(2)DMA転送要求の出力を再開する。その結果、(2)DMA転送要求にDMAC12は応答してTSIF11のTSバッファ111に一時的に格納された9番目のパケットP1を読み出して、外部メモリ7へのDMA転送を実行する。

# [0047]

すると、DMAC12はCPU13のDMA制御処理部131に(3)DMA転送完了割り込みを通知するので、この割り込の通知に応答してCPU13のTS解析データ処理部132はトランスポートストリーム解析とデータ処理とによる(4)デコード処理を実行する。

# [0048]

このようにして、9番目のパケットP9から10番目のパケットP10までのMPEG2-TSに関して、TSIF11のTSバッファ111へのパケット受信とパケット読み出しとDMAC12による外部メモリ7へのDMA転送とCPU13によるデコード処理が実行される。それによって、上述の(1)DMA設定で設定された合計5パケット分のサイズのバイト数のDMA転送データの転送とデコード処理が完了する。

# [0049]

しかし、図6および図7のパケット処理フローによって標準ワンセグ放送と比較してビットレートが非常に高い次世代ワンセグ放送のMPEG2-TSを受信して処理する場合には、上述の(2)DMAC転送完了割り込み間隔が短くなると言う問題が本発明者等の検討によって明らかとされた。

# [0050]

この問題を解決するために、本発明に先立って本発明者等は複数のパケットのDMA転送が完了したタイミングで1回の(3)DMA転送完了割り込みを通知すると言う複数パケット単位の割り込み通知方式を着想したものである。

# [0051]

50

40

10

20

20

30

40

50

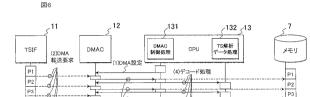

図 8 は、次世代ワンセグ放送の受信に際して割り込み間隔が短くなると言う問題を解決するため複数パケット単位の割り込み通知方式を採用して強電界の場合のMPEG2-TSの流れの制御を図1に示したアプリケーションプロセッサ1の各部で詳細に観測した図である。

# [0052]

図 8 でも図 6 と同様に、最初に C P U 1 3 の D M A 制御処理部 1 3 1 は、 D M A C 1 2 に(1) D M A 設定を実行する。この(1) D M A 設定では、例えば、 5 パケット(1 9 2 バイト×5)の D M A 転送データサイズが指定される。すると、 D M A C 1 2 は、 T S I F 1 1 からの D M A C 転送要求を待っている状態となる。

## [0053]

次に、TSIF11のTSバッファ111へのMPEG2-TSの最初のパケットP1の受信が完了すると、TSIF11はDMAC12に(2)DMA転送要求を出力する。更に、DMAC12は上述の(2)DMA転送要求に応答してTSIF11のTSバッファ111に一時的に格納された最初のパケットP1を読み出して、外部メモリ7へのDMA転送を実行する。同様に、TSIF11のTSバッファ111へのMPEG2-TSの2番目のパケットP2、3番目のパケットP3、4番目のパケットP4、5番目のパケットP5の受信がそれぞれ完了すると、各受信完了時点でTSIF11はDMAC12に(2)DMA転送要求をそれぞれ出力する。更にDMAC12は(2)各DMA転送要求に応答してTSIF11のTSバッファ111に一時的に格納された2番目のパケットP2から5番目のパケットP5までのデータを読み出し、外部メモリ7へのDMA転送を実行する。

# [0054]

このようにして最初のパケットP1から5番目のパケットP5までのデータ80aのDMAC12によるTSIF11から外部メモリ7へのDMA転送が完了すると、DMAC12はCPU13のDMA制御処理部131に(3)5パケット単位のデータ80aのDMA転送完了割り込みを通知する。するとCPU13のTS解析データ処理部132は、5パケット単位のDMA転送完了割り込みに応答して、5パケット単位のデータ80aのトランスポートストリーム解析とデータ処理とによる(4)デコード処理を実行する。また更に、MPEG2-TSの後続の5パケット単位のパケットP6~P10、P11~P15のデータ80b、80cに関しても、上述と同様な5パケット単位のデータのDMA転送完了割り込みおよび5パケット単位のデータのTS解析とデータ処理とによる(4)デコード処理が繰り返されるものである。

# [0055]

図9は、図8に示した複数パケット単位の割り込み通知方式を採用した際に強電界から弱電界に変化する場合のMPEG2-TSの流れの制御を図1に示したアプリケーションプロセッサ1の各部で詳細に観測した図である。

## [0056]

図9でも、図8と同様に、最初の5パケット単位のパケットP1~P5までのデータ90aに関して、TSIF11への受信と、DMAC12によるTSIF11から外部メモリ7へのDMA転送と、CPU13によるTS解析とデータ処理とによるデコード処理とが実行される。すなわち、図9でも最初の5パケット単位のパケットP1~P5の各パケットがTSIF11に受信されると、各パケットに関してTSIF11からDMAC12によってTSIF11から外部メモリ7へDMA転送要求が出力され、各パケットはDMAC12によってTSIF11から外部メモリ7へDMA転送されることができる。その後に、DMAC12はCPU13のDMA制御処理部131に(3)5パケット単位のデータ90aのDMA転送完了割り込みを通知するので、5パケット単位のデータのCPU13によるTS解析とデータ処理とによる(4)デコード処理が実行される。

#### [0057]

また図 9 では、 2 番目の 5 パケット単位のデータ 9 0 b の 3 個のパケット P 6 ~ P 8 までに関して、 T S I F 1 1 への受信と、 D M A C 1 2 による T S I F 1 1 から外部メモリ 7 への D M A 転送とが実行される。それは、 T S I F 1 1 が各パケット単位の受信によっ

て D M A C 1 2 へ(2) D M A 転送要求を出力するためである。

## [0058]

その後に、TSIF11への受信の間に強電界から弱電界に変化するので、データ90 bに含まれるパケットP9~P16のMPEG2-TSは、TSIF11によって受信されることができない。従って、この間にはTSIF11がDMAC12へ(2)DMA転送要求を出力できないので、DMAC12は待機状態となる。

#### [0059]

弱電界から強電界へ復帰すると、データ90bの後続の2個のパケットP17、P18が、TSIF11によって受信されるようになる。従って、受信された2個のパケットP17、P18の各パケットに関してTSIF11からDMAC12へ(2)DMA転送要求が出力され、各パケットはDMAC12によってTSIF11から外部メモリ7へDMA転送されることができる。

#### [0060]

すると、やっとDMAC12はCPU13のDMA制御処理部131に(3)5パケット単位のデータ90bのDMA転送完了割り込みを通知して、弱電界前の3個のパケットP6、P7、P8と弱電界後の2個のパケットP17、P18の合計5パケットの単位のデータのCPU13によるTS解析とデータ処理による(4)デコード処理が開始される。しかし、このデコード処理では、弱電界によって受信が中断された5パケット単位のデータ90bの古い3個のパケットP6~P9のデータは破棄される必要がある。それは、下記のような理由によるものである。

#### [0061]

すなわち、ディジタルTV放送受信機では、同期用の番組時刻基準値情報と音声および映像の再生用出力時刻情報とを比較して、受信機の再生動作と放送局の同期が取られるものである。尚、番組時刻基準値情報は、プログラム・クロック・リファレンス(PCR:Program Clock Reference)と呼ばれている。また、音声や映像の再生用出力時刻情報は、プレゼンテーションタイムスタンプ(PTS: Presentation Time Stamp)と呼ばれている

## [0062]

従って、弱電界前の古い3個のパケットP6~P9に番組時刻基準値情報PCRが含まれていた場合には、この古い時刻情報の無視が実行されなければならない。そうでないと、弱電界後の新しい2個のパケットP17、P18に含まれる現在の番組時刻基準値情報PCRに古い時刻情報が反映されて、誤動作の原因となる。例えば、新しい2個のパケットP17、P18に含まれる新しい音声および映像の情報が、弱電界前の古い3個のパケットP6~P9の古い時刻情報の影響によって出力(プレゼンテーション)されない場合も想定される。

#### [0063]

このように、次世代ワンセグ放送の受信で複数パケット単位の割り込み通知方式を採用した場合に弱電界になった際には、弱電界による受信中断前に受信されたパケットの早期のTS解析とデータ処理によるデコード処理を開始する必要があることが本発明者等によって明らかとされた。

# [0064]

本発明者等は、本発明に先立って受信中断時の受信パケットの早期のTS解析とデータ処理とによるデコード処理の開始を可能とするために、複数パケット単位のDMA転送完了割り込みにタイマ割り込みを追加すると言う着想に至ったものである。

#### [0065]

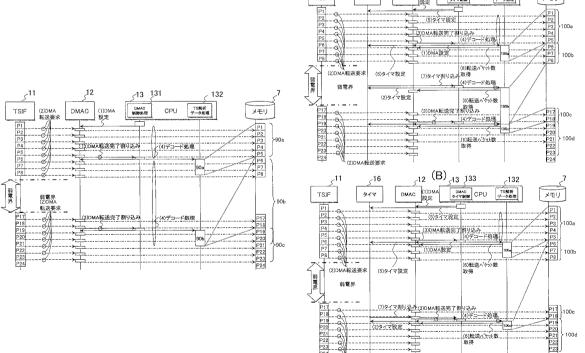

図10は、複数パケット単位のDMA転送完了割り込みとタイマ割り込みを採用した際に強電界から弱電界に変化する場合のMPEG2-TSの流れの制御を図1に示したアプリケーションプロセッサ1の各部で詳細に観測した図である。

# [0066]

図 1 0 (A)は(7)タイマ割り込みと(3)DMA転送完了割り込みの時間差が比較的大き

20

10

30

40

20

30

40

50

く、タイマ割り込みによるデコード処理が滞った場合の処理を説明する図であり、図10(B)は(7)タイマ割り込みと(3)DMA転送完了割り込みの時間差が比較的小さな場合の処理を説明する図である。

## [0067]

図1に示したアプリケーションプロセッサ1に含まれたタイマ16は、このタイマ割り込みに使用可能とされている。しかし、このタイマ16は、他の計時動作に兼用可能で有ることは言うまでもない。この図1に示されたアプリケーションプロセッサ1に含まれたタイマ16は、タイマ割り込みに関して下記のように制御されるものである。

## [0068]

すなわち、図10(A)、(B)に示すように、外部デジタルテレビチューナー3からMPEG2-TSの最初のパケットP1がアプリケーションプロセッサ1のTSIF11にて受信されることによって生成される(2)DMA転送要求に応答して、CPU13のDMACタイマ制御部133はタイマ16に(5)タイマ設定に基づく計数動作(タイマ動作)を開始する。例えば、タイマ16はカウンターにより構成されているので、タイマ16はCPU13のDMACタイマ制御部133によってタイマ設定されることによって計数動作(タイマ動作)を実行する。この計数動作による所定のカウント時間の間にMPEG2-TSの所定数の複数パケットのDMAC12によるDMAC転送が完了されない場合には、タイマ16はCPU13のDMACタイマ制御部133に(7)タイマ割り込みを実行する。この(7)タイマ割り込みに応答して、CPU13は外部メモリ7にDMAC転送済みのパケットの早期のトランスポートストリーム(TS)解析とデータ処理による(4)デコード処理を開始するものである。このタイマ16への(5)タイマ設定に先立って、CPU13のDMACタイマ制御部133はDMAC転送数は割り込み通知の単位である複数パケット、例えば5個のパケット数に設定される。

#### [0069]

図10(A)、(B)でも、図9と同様に最初の5パケット単位のパケットP1~P5のデータ100aに関して、TSIF11への受信、DMAC12によるTSIF11から外部メモリ7へのDMA転送、CPU13によるTS解析とデータ処理による(4)デコード処理が実行される。図10(A)、(B)のこの動作は、図9と全く同様であるので、詳細な説明を省略する。

## [0070]

また図10(A)、(B)でも、図9と同様に、2番目の5パケット単位のデータ100bの3個のパケットP6~P8に関して、TSIF11への受信とDMAC12によるTSIF11から外部メモリ7へのDMA転送とが実行された後、強電界から弱電界に変化して、データ100bに含まれるパケットP9~P16のMPEG2-TSがTSIF11によって受信不可能の受信中断状態となる。

# [0071]

図9の処理では、この受信中断状態の間には、TSIF11がDMAC12へ(2)DMA転送要求を出力できないので、DMAC12は待機状態となり、強電界へ復帰した後の受信再開にて誤った再生時刻情報が出力され、誤動作の原因となっていた。

# [0072]

それに対して図10(A)、(B)の処理では、弱電界による受信中断状態の前に受信された2番目の5パケット単位のデータ100bの1番目のパケットP6の受信で生成される(2)DMA転送要求に応答した(5)タイマ設定に基づく計数動作(タイマ動作)により、受信中断状態の間にタイマ16による(7)タイマ割り込みが発生する。すなわち、2番目の受信パケットデータ100cとの間の弱電界による受信中断状態の間に、タイマ16の計数動作による所定のカウント時間の間にDMAC 2による所定の転送数のDMAC転送が完了されないものである。従って、受信中断状態の間のタイマ16による(7)タイマ割り込みに応答して、CPU13は外部メモリ7にDMAC転送済みの2番目の受信パケットデータ100b中に含まれた3個のパケットP

20

30

40

50

6、P7、P8の早期のTS解析とデータ処理による(4)デコード処理を開始するものである。尚、この(4)デコード処理の開始に先立って、CPU13のTS解析データ処理部132は(6)転送パケット数取得を行って、外部メモリ7にDMAC転送済みの2番目の受信パケットデータ100b中に含まれたパケットP6、P7、P8の個数を認識する。【0073】

図10(A)、(B)でも、図9と同様に弱電界から強電界へ復帰すると、3番目の受信パケットデータ100cの2個のパケットP17、P18がTSIF11によって受信されるようになる。従って、受信された2個のパケットP17、P18の各パケットに関して、TSIF11からDMAC12へ(2)DMA転送要求が出力されて、各パケットはDMAC12によってTSIF11から外部メモリ7へDMA転送されることができる。このようにして、2個のパケットP17、P18のDMAC12による外部メモリ7へのDMA転送が完了すると、DMAC12はCPU13のDMA制御処理部131に(3)DMA転送完了割り込みを通知する。この時の(3)DMA転送完了割り込みは、弱電界による受信中断状態前と受信再開後の合計5個のパケットのDMA転送の完了を示している。すなわち、DMA転送が完了した合計5個のパケットのDMA転送の完了を示している。する目の受信パケットデータ100cの2個のパケットP17、P18である。すると、CPU13のTS解析データ処理部132は、合計5個のパケットのうち未処理分の3番目の受信パケットデータ100cの2個のパケットP17、P18に関してトランスポートストリーム解析とデータ処理とによる(4)デコード処理を実行する。

[0074]

図10(A)、(B)で説明したように、複数パケット単位のDMA転送完了割り込みとタイマ割り込みとの複数の割り込み方式を採用する場合には、複数の割り込みが略同時に発生した際の処理の競合を回避するために、複数の割り込みに優先順位を持たせることが一般的に採用されるものである。しかし、複数の割り込みが略同時に発生しても、実際は時間差が発生する。優先度の高い割り込みが先に発生した場合には処理の矛盾が発生しないが、優先度の低い割り込みが先に発生した場合には処理の矛盾が発生することが本発明者等の検討によって明らかとなった。

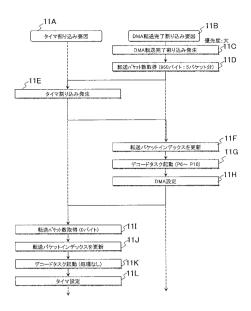

[0075]

図11は、図10の処理でタイマ割り込みよりもDMA転送完了割り込みの優先度を高く設定した場合に、優先度の高いDMA転送完了割り込みがタイマ割り込みよりも先に発生した場合の処理を説明する図である。

[0076]

図11に示すように、複数の割り込み要因として、タイマ割り込み要因11AとDMA転送完了割り込み要因11Bが存在しているが、優先度が低いタイマ割り込み発生11Eよりも先に優先度が高いDMA転送完了割り込み発生11Cが生じている。

[0077]

優先度が高いDMA転送完了割り込み発生11Cに応答してCPU13のTS解析データ処理部132は(6)転送パケット数取得11Dを行って、外部メモリ7にDMAC転送済みの受信パケットデータに含まれたパケットの個数を認識する。例として、2番目の受信パケットデータ100bの合計960バイトである5個のパケットP6~P10が外部メモリ7にDMAC転送済みであるとする。従って、この転送パケット数取得11Dによって、転送パケット数としてパケットの5個が取得される。この際に、前回の転送パケットインデックスと今回取得した転送パケットインデックスの差分から、転送パケット数が取得される。今回は、5個のパケットP6~P10が受信されているため、960バイトの転送パケット数が取得される。

[0078]

転送パケット数取得11Dの後、優先度の低いタイマ割り込み発生11Eが生じるが、 優先度が高いDMA転送完了割り込み発生11Cの処理が終了するまで、タイマ割り込み 処理は待機状態となる。次のステップ11Fで、次回の割り込みで使用するため、転送パ ケットインデックスを更新する。

# [0079]

更に次のステップ11GでCPU13のTS解析データ処理部132は、5個のパケットP6~P10のトランスポートストリーム解析とデータ処理とによる(4)デコード処理のタスクを起動してデコード処理を実行する。またその次のステップ11Hでは、CPU13のDMACタイマ制御部133は(1)DMA設定を実行する。

#### [0080]

以上のように優先度が高いDMA転送完了割り込み発生11Cの処理が終了すると、次のステップ11Iで優先度の低いタイマ割り込みの処理が開始される。このステップ11 I で、CPU13のTS解析データ処理部132は(6)転送パケット数取得を実行する。しかし、この時には外部メモリ7にDMAC転送済みの受信パケットデータのパケットの個数はゼロであるので、転送パケット数取得は0パイトとなる。従って、次のステップ11Jで転送パケットインデックスを0パイトに更新して、更にステップ11Kで、CPU13のTS解析データ処理部132は、トランスポートストリーム解析とデータ処理とによる(4)デコード処理のタスクを起動する。しかし、この時にはステップ11Iで取得された転送パケット数は0パイトとなっているので、(4)デコード処理は実際には実行されない。

# [0081]

このようにして、優先度の低いタイマ割り込みの処理が実行されたので、次のステップ 1 1 L にて C P U 1 3 の D M A C タイマ制御部 1 3 3 は(5)タイマ設定を実行する。

#### [0082]

図12は、図10の処理でタイマ割り込みよりもDMA転送完了割り込みの優先度を高く設定した場合に、優先度の低いタイマ割り込みがDMA転送完了割り込みよりも先に発生した場合の処理を説明する図である。

#### [0083]

図12(A)は優先度が低いタイマ割り込み発生12Cと優先度が高いDMA転送完了割り込み発生12Eとの時間差が比較的大きく、タイマ割り込みによるデコード処理が滞った場合の処理を説明する図であり、図12(B)は優先度が低いタイマ割り込み発生12Cと優先度が高いDMA転送完了割り込み発生12Eとの時間差が比較的小さな場合の処理を説明する図である。

#### [0084]

まず図12(A)では図11と同様に、複数の割り込み要因としてタイマ割り込み要因1 2AとDMA転送完了割り込み要因12Bとが存在しているが、優先度が高いDMA転送 完了割り込み発生12Eよりも先に優先度が低いタイマ割り込み発生12Cが生じている

#### [0085]

優先度が低いタイマ割り込み発生12Cに応答してCPU13のTS解析データ処理部132は(6)転送パケット数取得12Dを行って、外部メモリ7にDMAC転送済みの受信パケットデータに含まれたパケットの個数を認識する。例としては、図10に示した受信中断状態前の2番目の受信パケットデータ100bの合計576バイトの3個のパケットP6~P8が外部メモリ7にDMAC転送済みであるとする。従って、この転送パケット数取得12Dによって、転送パケット数として3個のパケット分の576バイトが取得される。

# [0086]

しかし、優先度が低いタイマ割り込み発生12Cに応答した転送パケット数取得12Dの直後に、タイマ割り込みによるデコード処理が滞っているときに優先度が高いDMA転送完了割り込み発生12Eが発生するものである。従って、優先度が高いDMA転送完了割り込み発生12Eの処理が終了するまで、タイマ割り込み発生12Eの処理は待機状態とされる。その結果、優先度が高いDMA転送完了割り込み発生12Eの処理が開始される。例として、図10に示した受信再開後の3番目の受信パケットデータ100cの合計

10

20

30

40

20

30

40

50

384バイトの2個のパケットP17、P18である。

# [0087]

この優先度が高いDMA転送完了割り込み発生12Eに応答してCPU13のTS解析データ処理部132は転送パケット数取得12Fを行って、外部メモリ7にDMAC転送済みの3番目の受信パケットデータ100cの合計384バイトのパケットP17、P18の2個のパケット個数を取得する。

#### [0088]

転送パケット数取得12Fで取得された転送パケット数に従って、ステップ12Gで転送パケットインデックスを384バイトに更新して、更に、次のステップ12Hで、CPU13のTS解析データ処理部132は2個のパケットP17、P18のトランスポートストリーム解析とデータ処理とによる(4)デコード処理のタスクを起動する。また、その次のステップ12Iでは、CPU13のDMACタイマ制御部133は(1)DMA設定を実行する。

# [0089]

その後、優先度が低いタイマ割り込み発生12Cの処理に戻り、ステップ12Jにて転送パケットインデックスの更新が実行される。しかし以前の転送パケット数取得12Dにて、転送パケット数として3個のパケットP6~P8の分の576バイトが取得されていた。従って、ステップ12Jでの転送パケットインデックスの更新によって、転送パケットインデックスは以前の転送パケット数取得12Dで取得された古い3個のパケットP6~P8の分の576バイトに更新されることになる。

#### [0090]

その結果、次のステップ12KでCPU13のTS解析データ処理部132は、古い3個のパケットP6~P8のトランスポートストリーム解析とデータ処理による(4)デコード処理のタスクを起動してデコード処理を実行する。またその次のステップ12Lで、CPU13のDMACタイマ制御部133は(5)タイマ設定を実行する。

## [0091]

このようにして、優先度の低いタイマ割り込みの処理が実行されたので、次のステップ 1 2 L にて C P U 1 3 の D M A C タイマ制御部 1 3 3 は(5)タイマ設定を実行する。

## [0092]

以上説明したように、図12(A)に示すように優先度の低いタイマ割り込み12Dが優先度の高いDMA転送完了割り込み12Eよりも先に発生した場合に、割り込み処理が実行されるものである。

#### [0093]

しかし、図12(A)に示した複数の割り込み要因に対する処理には、以下のような問題が有ることが本発明者等による検討によって明らかとされた。

#### [0094]

最初は、先の低優先度のタイマ割り込み発生12Cに応答する転送パケット数取得12 Dにより取得される転送パケット数(576バイト)と後の高優先度のDMA転送完了割り 込み発生12Eに応答する転送パケット数取得12Fにより取得される転送パケット数(384バイト)とが、図12(A)の12Mに示すように値が異なることである。

# [0095]

次は、ステップ 1 2 Hの(4)デコード処理とステップ 1 2 Kの(4)デコード処理とが実行されて、図 1 2 (A)の 1 2 Nに示すように逆転処理が行われることである。

# [0096]

後の高優先度の D M A 転送完了割り込み発生 1 2 E に応答する転送パケット数取得 1 2 F により取得される転送パケット数によって、受信中断後の受信再開による受信パケットデータ 1 0 0 c の合計 3 8 4 バイトの 2 個のパケット P 1 7 、 P 1 8 の(4) デコード処理をステップ 1 2 H で実行することができる。

## [0097]

しかし、先の低優先度のタイマ割り込み発生12Cに応答する転送パケット数取得12

20

30

40

50

Dにより取得される転送パケット数によって、受信中断前の受信パケットデータ100bの古い3個のパケットP6~P8もステップ12Kで(4)デコード処理が実行されてしまう。一方、冒頭で説明したように、弱電界前の古い3個のパケットP6~P9に番組時刻基準値情報PCRが含まれていた場合には、この古い時刻情報の無視が実行されなければならない。そうでないと、弱電界後の新しい2個のパケットP17、P18に含まれる現在の番組時刻基準値情報PCRに古い時刻情報が反映されて、誤動作の原因となる。具体的に言えば、古い音声や映像が2度出力され、新しい音声や映像が出力されないような誤動作が発生するものである。

# [0098]

優先度が低いタイマ割り込み発生12Cと優先度が高いDMA転送完了割り込み発生12Eとの時間差が比較的小さな場合の図12(B)でも、時間差が比較的大きく、タイマ割り込みによるデコード処理が滞った場合の図12(A)と同様に、複数の割り込み要因としてタイマ割り込み要因12AとDMA転送完了割り込み要因12Bとが存在しているが、優先度が高いDMA転送完了割り込み発生12Eよりも少し先に優先度が低いタイマ割り込み発生12Cが生じている。

#### [0099]

優先度が低いタイマ割り込み発生12Cに応答してCPU13のTS解析データ処理部132は(6)転送パケット数取得12Dを行って、外部メモリ7にDMAC転送済みの受信パケットデータに含まれたパケットの個数を認識する。例としては、図10において、タイマ割り込み発生直前に、強電界に復帰して、DMA転送完了割り込みが発生したとする。この時に、5パケット取得して、タイマ割り込みとDMA転送完了割り込みが同時に発生したとする。図10に示した受信中断状態前の2番目の受信パケットデータ100bと100cの合計960バイトの5個のパケットP6~P8、P17,P18が外部メモリ7にDMAC転送済みであるとする。従って、この転送パケット数取得12Dによって、転送パケット数として5個のパケット分の960バイトが取得される。

## [0100]

しかし、優先度が低いタイマ割り込み発生12Cに応答した転送パケット数取得12Dの直後に、優先度が高いDMA転送完了割り込み発生12Eが発生するものである。従って、優先度が高いDMA転送完了割り込み発生12Eの処理が終了するまで、タイマ割り込み発生12Cの処理は待機状態とされる。その結果、優先度が高いDMA転送完了割り込み発生12Eの処理が開始される。例として、図10に示した受信中断状態前の2番目の受信パケットデータ100bと受信再開後の3番目の受信パケットデータ100cの合計960バイトの5個のパケットP6~P8、P17、P18である。

#### [0101]

この優先度が高いDMA転送完了割り込み発生12Eに応答してCPU13のTS解析データ処理部132は転送パケット数取得12Fを行って、外部メモリ7にDMAC転送済みの2番目の受信パケットデータ100bと3番目の受信パケットデータ100cの合計960バイトのパケットP6~P8、P17、P18の5個のパケット個数を取得する

## [0102]

転送パケット数取得12Fで取得された転送パケット数に従って、ステップ12Gで転送パケットインデックスを更新して、更に、次のステップ12Hで、CPU13のTS解析データ処理部132は5個のパケットP6~P8、P17、P18のトランスポートストリーム解析とデータ処理とによる(4)デコード処理のタスクを起動する。また、その次のステップ12Iでは、CPU13のDMACタイマ制御部133は(1)DMA設定を実行する。

#### [0103]

その後、優先度が低いタイマ割り込み発生12Cの処理に戻り、ステップ12Jにて転送パケットインデックスの更新が実行される。しかし以前の転送パケット数取得12Dにて、転送パケット数として5個のパケットP6~P8、P17、P18の分の960バイ

トが取得されていた。その結果、次のステップ12KでCPU13のTS解析データ処理部132は、5個のパケットP6~P8、P17,P18のトランスポートストリーム解析とデータ処理とによる(4)デコード処理のタスクを起動してデコード処理を実行する。またその次のステップ12Lで、CPU13のDMACタイマ制御部133は(5)タイマ設定を実行する。

# [0104]

このようにして、優先度の低いタイマ割り込みの処理が実行されたので、次のステップ 12 LにてCPU13のDMACタイマ制御部133は(5)タイマ設定を実行する。

## [0105]

以上説明したように、図12(B)に示すように優先度の低いタイマ割り込み12Dが優先度の高いDMA転送完了割り込み12Eよりも先に発生した場合に、割り込み処理が実行されるものである。

#### [0106]

しかし、図12(B)に示した複数の割り込み要因に対する処理には、以下のような問題が有ることが本発明者等による検討によって明らかとされた。

#### [0107]

最初は、先の低優先度のタイマ割り込み発生12Cに応答する転送パケット数取得12 Dにより取得される転送パケットP6~8、P17、P18と後の高優先度のDMA転送 完了割り込み発生11Cに応答する転送パケット数取得12Fにより取得される転送パケットP6~8、P17、P18とが、図12(B)の12Mに示すように同じパケットになることである。

#### [0108]

次は、ステップ 1 2 Hの(4)デコード処理とステップ 1 2 Kの(4)デコード処理とが実行されて、図 1 2 (B)の 1 1 2 Nに示すように重複処理が行われることである。

#### [0109]

後の高優先度のDMA転送完了割り込み発生11Cに応答する転送パケット数取得12 Fにより取得される転送パケット数によって、受信中断状態前の受信パケットデータ10 0 b と受信中断後の受信再開による受信パケットデータ100cの合計960バイトの5 個のパケットP6~P8、P17、P18の(4)デコード処理をステップ12Hで実行することができる。

## [0110]

要するに、タイマ割込みとデータ転送完了割込みが同時に発生すると同一の5パケットをタイマ割込みによるデコード処理とデータ転送割込みによるデコード処理を重複処理してしまい、例えば、同じ画像が2度出力される等の誤動作が起きる。

## [0111]

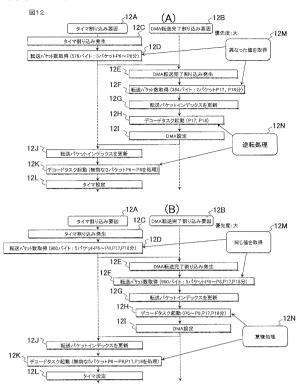

図13は、図12に示す複数の割り込み要因に対する処理での重複処理の問題を解決するために、本発明に先立って本発明者等によって検討された処理を説明する図である。

## [0112]

図13でも図12と同様に、複数の割り込み要因としてタイマ割り込み要因13AとDMA転送完了割り込み要因13Bが存在しており、優先度が高いDMA転送完了割り込み発生13Fよりも先に優先度が低いタイマ割り込み発生13Cが生じている。

#### [0113]

しかし、図13に示す処理は、上述の重複処理の問題を解決するために、ステップ13 Dのセマフォ設定の処理を含むものである。セマフォは、並列処理において矛盾を解消す るための排他処理を意味するものである。

# [0114]

すなわち、先の優先度が低いタイマ割り込み発生13Cに応答してステップ13Dのセマフォ設定が実行されることによって、先に優先度が低いタイマ割り込みの処理(ステップ13E、13G~13J)の方を先に実行するものである。このようにして、後の優先度が高いDMA転送完了割り込み発生13Fに応答する処理(13K~13N)の方を後に

10

20

30

40

実行することにより、上述した重複処理の矛盾を解消するものである。

#### [0115]

図13の処理では、先の低優先度のタイマ割り込み発生13Cに応答してステップ13 Dのセマフォ設定が実行される。すると、セマフォ処理の間に、ステップ13Eの転送パケット数取得が実行される。例として、図10に示す受信中断状態前の2番目の受信パケットデータ100bの合計576バイトの3個のパケットP6~P8が外部メモリ7にDMAC転送済みとする。従って、この転送パケット数取得13Eにより、転送パケット数として3個のパケット分の576バイトが取得される。

## [0116]

ステップ13Eの転送パケット数取得の後に、後の高優先度のDMA転送完了割り込み発生13Fが生じる。しかし、ステップ13Dのセマフォ設定によって、図13のその後の処理がDMA転送完了割り込みの処理13K~Nの方が先に実行することが禁止され、タイマ割り込みの処理のステップ13E、13G~Jの方が先に実行されるものである。

## [0117]

ステップ13Dのセマフォ設定によって、後の高優先度のDMA転送完了割り込み発生13Fが生じたのにもかかわらず、先の低優先度のタイマ割り込み発生13Cに応答してCPU13のTS解析データ処理部132は(6)転送パケット数取得13Eを実行して、外部メモリ7にDMAC転送済みの受信パケットデータに含まれたパケットの個数を取得する。例として、図10に示した受信中断状態前の2番目の受信パケットデータ100bの合計576バイトの3個のパケットP6~P8が外部メモリ7にDMAC転送済みであるとする。従って、この転送パケット数取得13Eによって、転送パケット数として3個のパケットP6~P8の576バイトが取得される。

#### [0118]

転送パケット数取得13Eで取得された転送パケット数に従って、ステップ13Gで転送パケットインデックスを576バイトに更新する。更に次のステップ13Hで、CPU13のTS解析データ処理部132は3個のパケットP6~P8のトランスポートストリーム解析とデータ処理とによる(4)デコード処理のタスクを起動する。また、その次のステップ13Iで、CPU13のDMACタイマ制御部133は(5)タイマ設定を実行して、更に次のステップ13Jで、セマフォの開放が実行される。

# [0119]

ステップ 1 3 J でセマフォの開放が実行されると、図 1 3 の処理は D M A 転送完了割り込みの処理 1 3 K ~ 1 3 N に移行される。まずステップ 1 3 K の(6)転送パケット数取得が実行され、外部メモリ 7 に D M A C 転送済みである 3 番目の受信パケットデータ 1 0 0 c の合計 3 8 4 バイトのパケット P 1 7 、 P 1 8 の 2 個のパケット 個数を取得する。

## [0120]

転送パケット数取得13Kで取得された転送パケット数に従って、ステップ13Lで転送パケットインデックスを384バイトに更新して、更に次のステップ13Mで、CPU13のTS解析データ処理部132は2個のパケットP17、P18のトランスポートストリーム解析とデータ処理による(4)デコード処理のタスクを起動する。また、その次のステップ13Nでは、CPU13のDMACタイマ制御部133は(1)DMA設定を実行する。

#### [0121]

このように図13に示す処理の実行により、古い方の2番目の受信パケットデータ10 0 b の合計 5 7 6 バイトの3個のパケットP6~P8の(4)デコード処理が先に実行され 、新しい方の3番目の受信パケットデータ100cの合計384バイトのパケットP17 、P18の(4)デコード処理が後に実行される。このように、図13に示す処理の実行に よれば、図12に示す複数の割り込み要因に対する処理での重複処理の矛盾を解消するこ とが可能となる。

## [0122]

しかし、本発明に先立った本発明者等による検討によって、図13に示した処理のステ

10

20

30

40

ップ13Dのセマフォ設定とステップ13Jのセマフォ開放には長い処理時間が必要であ って、CPU13のDMACタイマ制御部133の処理負荷が大きくなると言う問題が明 らかとされた。

#### [ 0 1 2 3 ]

従って、ISDB-Tmmと呼ばれる次世代ワンセグ放送を受信可能な携帯電話機端末 に搭載されるアプリケーションプロセッサ等の半導体集積回路の内蔵CPUの消費電力が 増大すると言う問題が発生するものである。また、複数の割り込み要因を処理するための 内蔵CPUの制御ソフトウェアが複雑化して、ソフトウェアを格納するための内蔵不揮発 性メモリのメモリ容量も増加すると言う問題も発生するものである。

#### [0124]

本発明は、以上のような本発明に先立った本発明者等による検討の結果、なされたもの である。

#### [0125]

従って、本発明の目的とするところは、複数の割り込み要因に対する処理での重複処理 の矛盾を解消する際の負担が軽減された半導体集積回路を提供することにある。

#### [0126]

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面か ら明らかになるであろう。

【課題を解決するための手段】

## [0127]

本願において開示される発明のうちの代表的なものについて簡単に説明すれば下記のと おりである。

## [0128]

すなわち、本発明の代表的な半導体集積回路(1)は、受信インターフェース(11)と、 メモリインターフェース(17)と、データ転送ユニット(12)と、処理ユニット(13、 18)とを具備する(図15参照)。

#### [0129]

データ転送ユニット(12)が所定のパケット数の複数の受信パケットデータのバッファ (111)から外部メモリ(7)へのデータ転送を完了すると、データ転送完了割り込みが処 理ユニット(13、18)に通知される。

# [0130]

受信中断の間に、タイマ(113)によるカウント時間の間に所定のパケット数の受信パ ケットデータのデータ転送が未完了の場合には、タイマ割り込みが処理ユニット(13、 18)に通知される。

# [0131]

データ転送完了割り込みおよびタイマ割り込みに応答して処理ユニット(13、18)が 外部メモリ(7)に格納された複数の受信パケットデータの処理を開始する以前に、処理ユ ニット(13、18)はパケットカウンタ(114)から転送パケット数を取得する。

40 処理ユニット(13、18)によるパケットカウンタ(114)からの転送パケット数の取 得の後に、パケットカウンタ(114)の値はゼロにリセットされる(図14参照)。

受信再開後に、パケットカウンタ(1 1 4)はデータ転送ユニット(1 2)により外部メモ リ(7)に転送再開される再開受信パケットデータの転送再開パケット数を格納する。

#### [0134]

受信中断の前に外部メモリ(7)に格納された受信パケットデータの転送パケット数を、 タイマ割り込みの発生(18C)に応答して、処理ユニットがパケットカウンタ(114)か ら取得(18D)した後に、データ転送完了割り込みの発生(18E)が生じる。

## [0135]

タイマ割り込みの発生に応答して処理ユニットがパケットカウンタから取得した転送パ

20

10

30

ケット数に従って、受信中断の前に外部メモリ(7)に格納された受信パケットデータのタ イマ割り込みの発生(18C)に応答する処理(図18(A):18I)もしくは外部メモリ( 7)に格納された複数の受信パケットデータのデータ転送完了割り込みの発生(18E)に 応答する処理(図18(B):18G)のいずれかの処理の実行が省略されることを特徴とす る。

# 【発明の効果】

#### [ 0 1 3 6 ]

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明す れば下記の通りである。すなわち、複数の割り込み要因に対する処理での重複処理の矛盾 を解消する際の負担が軽減された半導体集積回路を提供することができる。

10

#### 【図面の簡単な説明】

#### [0137]

- 【図1】図1は、本発明に先立って本発明者等によって検討されたアプリケーションプロ セッサの構成を示す図である。

- 【図2】図2は、図1に示したアプリケーションプロセッサ1に含まれるトランスポート ストリームインターフェース(TSIF)11の構成を示す図である。

- 【図3】図3は、図1に示したアプリケーションプロセッサ1の内部でのMPEG2-ト ランスポートストリーム(MPEG2-TS)の流れを説明する図である。

- 【図4】図4は、図3に示したMPEG2-TSの流れを図1に示したアプリケーション プロセッサ1の外部デジタルテレビチューナー3、TSIF11、DMAC12、外部メ モリフの各点で観測した図である。

20

30

40

- 【図5】図5は、図1に示したアプリケーションプロセッサ1の内部のMPEG2-TS の流れの制御を説明する図である。

- 【図6】図6は、強電界の場合でのMPEG2-TSの流れの制御を図1に示したアプリ ケーションプロセッサ 1 のTSIF11、DMAC12、CPU13、外部メモリ7の各 点で詳細に観測した図である。

- 【図7】図7は、弱電界の場合でのMPEG2-TSの流れの制御を図1に示したアプリ ケーションプロセッサ 1 のTSIF11、DMAC12、CPU13、外部メモリ 7 の各 点で詳細に観測した図である。

【図8】図8は、次世代ワンセグ放送の受信に際して割り込み間隔が短くなると言う問題 を解決するため複数パケット単位の割り込み通知方式を採用して強電界の場合のたMPE G2-TSの流れの制御を図1に示したアプリケーションプロセッサ1の各部で詳細に観

測した図である。 【図9】図9は、図8に示した複数パケット単位の割り込み通知方式を採用した際に強電

ションプロセッサ1の各部で詳細に観測した図である。 【図10】図10は、複数パケット単位のDMA転送完了割り込みとタイマ割り込みを採 用した際に強電界から弱電界に変化する場合のMPEG2-TSの流れの制御を図1に示

したアプリケーションプロセッサ1の各部で詳細に観測した図である。

界から弱電界に変化する場合のMPEG2-TSの流れの制御を図1に示したアプリケー

【図11】図11は、図10の処理でタイマ割り込みよりもDMA転送完了割り込みの優 先度を高く設定した場合に、優先度の高いDMA転送完了割り込みがタイマ割り込みより も先に発生した場合の処理を説明する図である。

【 図 1 2 】 図 1 2 は 、 図 1 0 の 処理 で タイ マ 割 り 込 み よ り も D M A 転 送 完 了 割 り 込 み の 優 先度を高く設定した場合に、優先度の低いタイマ割り込みがDMA転送完了割り込みより も先に発生した場合の処理を説明する図である。

【図13】図13は、図12に示す複数の割り込み要因に対する処理での重複処理の問題 を解決するために、本発明に先立って本発明者等によって検討された処理を説明する図で

【図14】図14は、図15に示すアプリケーションプロセッサ1に含まれたTSIF1 1の構成を示す図である。

20

30

40

50

【図15】図15は、本発明の実施の形態1によるアプリケーションプロセッサの構成を示すブロック図である。

【図16】図16は、強電界の場合のMPEG2-TSの流れの制御を図14に示すTSIF11を含む図15に示すアプリケーションプロセッサ1の各部で詳細に観測した図である。

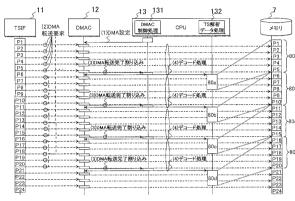

【図17】図17は、複数パケット単位のDMA転送完了割り込みとタイマ割り込みを採用した際に強電界から弱電界に変化する場合のMPEG2-TSの流れの制御を図15に示した本発明の実施の形態1によるアプリケーションプロセッサ1の各部で詳細に観測した図である。

【図18】図18は、図17の処理で後の高優先度の(3)DMAC転送完了割り込みに応答した先のデコード処理と先の低優先度の(7)タイマ割り込みに応答した後のデコード処理との逆転処理あるいは重複処理を回避する処理を説明する図である。

【発明を実施するための形態】

[0138]

1.実施の形態の概要

まず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

[0139]

[1] 本発明の代表的な実施の形態は、受信インターフェース(11)と、メモリインターフェース(17)と、データ転送ユニット(12)と、処理ユニット(13、18)とを具備する半導体集積回路(1)である。

[0140]

前記受信インターフェース(11)は、複数の受信パケットデータ(P1、P2、P3...) を逐次に蓄積可能なバッファ(111)と、計数動作を行うタイマ(113)とを含むものである。

[0141]

前記メモリインターフェース(17)は、外部メモリ(7)と接続可能とされている。

[0142]

前記データ転送ユニット(12)は、前記バッファ(111)に蓄積される前記複数の受信パケットデータを、前記メモリインターフェース(17)に接続される前記外部メモリ(7)に転送可能とされている。

[0143]

前記処理ユニット(13、18)は、前記外部メモリ(7)に転送され格納される前記複数の受信パケットデータを処理可能とされている(図15参照)。

[0144]

前記データ転送ユニット(12)が所定のパケット数の前記複数の受信パケットデータの前記パッファから前記外部メモリへのデータ転送を完了すると、前記データ転送ユニット(12)はデータ転送完了割り込みを前記処理ユニット(13、18)に通知可能とされている。

[0145]

前記データ転送ユニット(12)からの前記データ転送完了割り込みの発生に応答して、前記処理ユニット(13、18)は前記外部メモリ(7)に格納された前記複数の受信パケットデータの処理を開始可能とされたものである。

[0146]

前記受信インターフェース(11)への前記複数の受信パケットデータの受信中断の間に、前記タイマ(113)は前記計数動作を実行するものである。

[0147]

前記受信中断の間に、前記計数動作による所定のカウント時間の間に前記所定のパケット数を有した前記複数の受信パケットデータの前記データ転送が未完了の場合には、前記

タイマ(1 1 3)はタイマ割り込みを前記処理ユニット(1 3 、 1 8)に通知可能とされている。

#### [0148]

前記タイマ(113)からの前記タイマ割り込みの発生に応答して、前記処理ユニット(13、18)は前記受信中断の前に前記外部メモリ(7)に格納された受信パケットデータの処理を開始可能とされたものである(図17参照)。

#### [0149]

前記受信インターフェース(11)は、前記データ転送ユニット(12)による前記外部メモリ(7)に転送済みの受信パケットデータの転送パケット数を格納するパケットカウンタ(114)を更に含むものである。

## [0150]

前記データ転送完了割り込みの発生に応答して前記処理ユニット(13、18)が前記外部メモリ(7)に格納された前記複数の受信パケットデータの処理を開始する以前に、前記処理ユニット(13、18)は前記パケットカウンタ(114)から前記転送パケット数を取得可能とされたものである。

#### [0151]

前記タイマ割り込みの発生に応答して、前記処理ユニット(13、18)が前記受信中断の前に前記外部メモリ(7)に格納された前記受信パケットデータの処理を開始する以前に、前記処理ユニット(13、18)は前記パケットカウンタ(114)から前記転送パケット数を取得可能とされたものである。

#### [0152]

前記処理ユニット(13、18)による前記パケットカウンタ(114)からの前記転送パケット数の取得の後に、前記パケットカウンタ(114)の値はゼロにリセットされるものである(図14参照)。

## [0153]

前記受信中断の後の受信再開後に、前記パケットカウンタ(1 1 4)は前記データ転送ユニット(1 2)により前記外部メモリ(7)に転送再開される再開受信パケットデータの転送再開パケット数を格納するものである(図 1 7 参照)。

## [0154]

前記受信中断の前に前記外部メモリ(7)に格納された前記受信パケットデータの前記転送パケット数を、前記タイマ割り込みの前記発生(18C)に応答して、前記処理ユニットが前記パケットカウンタ(114)から取得(18D)した後に、前記データ転送完了割り込みの前記発生(18E)が生じるものである(図18参照)。

#### [ 0 1 5 5 ]

前記タイマ割り込みの前記発生に応答して前記処理ユニットが前記パケットカウンタから取得した前記転送パケット数に従って、前記外部メモリ(7)に格納された前記受信パケットデータの前記タイマ割り込みの前記発生(18C)に応答する前記処理(図18(A):18I)もしくは前記外部メモリ(7)に格納された前記複数の受信パケットデータの前記データ転送完了割り込みの前記発生(18E)に応答する前記処理(図18(B):18G)のいずれかの処理の実行が省略されることを特徴とするものである。

# [0156]

前記実施の形態によれば、複数の割り込み要因に対する処理での重複処理の矛盾を解消 する際の負担が軽減された半導体集積回路を提供することができる。

# [0157]

好適な実施の形態では、前記タイマ割り込みの前記発生に応答して前記処理ユニットが前記パケットカウンタから取得した前記転送パケット数が前記所定のパケット数よりも小さい場合には、前記受信中断の前に前記外部メモリ(7)に格納された前記受信パケットデータの前記タイマ割り込みの前記発生(18C)に応答する前記処理(18I)の実行が省略される一方、前記外部メモリ(7)に格納された前記複数の受信パケットデータの前記データ転送完了割り込みの前記発生(18E)に応答する前記処理(18G)が実行されるもので

10

20

30

40

ある(図18(A)参照)。

# [0158]

前記タイマ割り込みの前記発生に応答して前記処理ユニットが前記パケットカウンタから取得した前記転送パケット数が前記所定のパケット数と等しい場合には、前記受信中断の前および前記受信再開後に前記外部メモリ(7)に格納された前記受信パケットデータの前記タイマ割り込みの前記発生 $(1\ 8\ C)$ に応答する前記処理 $(1\ 8\ I)$ の実行される一方、前記外部メモリ(7)に格納された前記複数の受信パケットデータの前記データ転送完了割り込みの前記発生 $(1\ 8\ E)$ に応答する前記処理 $(1\ 8\ G)$ の実行が省略されるものである $(2\ B)$  多照 $(2\ B)$ 。

# [0159]

他の好適な実施の形態では、前記処理ユニットは中央処理ユニット(CPU)を含み、前記データ転送ユニット(12)はダイレクトメモリアクセスコントローラ(DMAC)である(図15参照)。

# [0160]

更に他の好適な実施の形態では、前記受信インターフェース(11)は、MPEGのトランスポートストリームの形態である複数の受信パケットデータを受信可能とされている(図15参照)。

## [0161]

より好適な実施の形態では、前記処理ユニットの前記中央処理ユニット(CPU)は前記MPEGのトランスポートストリームの形態で前記外部メモリ(7)に格納された前記複数の受信パケットデータをデマルチプレックスの処理よって映像および音声のエレメンタリー・ストリームに分離するものである。

## [0162]

具体的な実施の形態では、前記処理ユニットは、MPEGデコーダ(18)と、表示制御装置(14)と、音声出力制御部(19)とを更に含む。

## [0163]

前記中央処理ユニット(CPU)によって分離された前記映像および音声のエレメンタリー・ストリームは、前記MPEGデコーダ(18)によって映像再生信号と音声再生信号とに復号化される。

# [0164]

前記映像再生信号の出力同期が前記表示制御装置(14)で実行され、前記音声再生信号の出力同期が前記音声出力制御部(19)で実行されるものである。

#### [0165]

より具体的な実施の形態では、前記データ転送完了割り込みの優先度は前記タイマ割り込みの優先度よりも高く設定されたものである。

#### [0166]

〔2〕本発明の別の観点の代表的な実施の形態は、入力インターフェース(11)と、第1処理ユニット(12)と、第2処理ユニット(13、18)とを具備する半導体集積回路(1)である。

## [0167]

前記入力インターフェース(11)は、複数の入力パケットデータ(P1、P2、P3...) を逐次に蓄積可能なバッファ(111)と、計数動作を行うタイマ(113)とを含むものである。

# [0168]

前記第1処理ユニット(12)は前記バッファ(111)に蓄積される前記複数の入力パケットデータを処理可能とされ、前記第2処理ユニット(13、18)は前記第1処理ユニット(12)の処理結果を処理可能とされている(図15参照)。

#### [0169]

前記第1処理ユニット(12)が所定のパケット数の前記複数の入力パケットデータを前記バッファから読み出して、前記第1処理ユニット(12)が読み出しデータの第1処理を

10

20

30

40

完了すると、前記第1処理ユニット(12)は第1処理完了割り込みを前記第2処理ユニット(13、18)に通知可能とされている。

#### [ 0 1 7 0 ]

前記第1処理ユニット(12)からの前記第1処理完了割り込みの発生に応答して、前記第2処理ユニット(13、18)は前記第1処理ユニット(12)の前記処理結果の第2処理を開始可能とされたものである。

#### [0171]

前記入力インターフェース(11)への前記複数の入力パケットデータの入力中断の間に、前記タイマ(113)は前記計数動作を実行するものである。

#### [0172]

前記入力中断の間に、前記計数動作による所定のカウント時間の間に前記所定のパケット数を有した前記複数の入力パケットデータの前記第1処理が未完了の場合には、前記タイマ(113)はタイマ割り込みを前記第2処理ユニット(13、18)に通知可能とされている。

## [0173]

前記タイマ(1 1 3)からの前記タイマ割り込みの発生に応答して、前記第2処理ユニット(1 3 、 1 8)は前記入力中断の前に前記第1処理ユニット(1 2)によって処理された処理済みデータの前記第2処理を開始可能とされたものである(図17参照)。

## [0174]

前記入力インターフェース(11)は、前記第1処理ユニット(12)によって処理された処理済みデータの処理済みパケット数を格納するパケットカウンタ(114)を更に含むものである。

## [0175]

前記第1処理完了割り込みの前記発生に応答して前記第2処理ユニット(13、18)が前記第2処理を開始する以前に、前記第2処理ユニット(13、18)は前記パケットカウンタ(114)から前記処理済みパケット数を取得可能とされたものである。

#### [0176]

前記タイマ割り込みの前記発生に応答して、前記第2処理ユニット(13、18)が前記入力中断の前に前記第1処理ユニット(12)によって処理された前記処理済みデータの処理済みパケット数を前記パケットカウンタ(114)から取得可能とされたものである。

## [0177]

前記第2処理ユニット(13、18)による前記パケットカウンタ(114)からの前記処理済みパケット数の取得の後に、前記パケットカウンタ(114)の値はゼロにリセットされるものである(図14参照)。

# [0178]

前記入力中断の後の入力再開後に、前記パケットカウンタ(114)は入力再開される再開入カパケットデータの入力再開パケット数を格納するものである。

## [0179]

前記タイマ割り込みの前記発生(18C)に応答して、前記入力中断の前に入力された前記入力パケットデータの前記パケット数を、前記第2処理ユニットが前記パケットカウンタ(114)から取得(18D)した後に、前記第1処理完了割り込みの前記発生(18E)が生じるものである(図18参照)。

## [0180]

前記タイマ割り込みの前記発生に応答して前記第 2 処理ユニットが前記パケットカウンタから取得した前記処理済みパケット数に従って、前記第 1 処理ユニット(1 2)によって処理された前記処理済みデータの前記第 2 処理ユニット(1 3、1 8)による前記タイマ割り込みの前記発生(1 8 C)に応答する処理(図 1 8 (A): 1 8 I)もしくは前記第 1 処理ユニット(1 2)によって処理された前記処理済みデータの前記第 2 処理ユニット(1 3、1 8)による前記第 1 処理完了割り込みの前記発生(1 8 E)に応答する前記第 2 処理(図 1 8 (B): 1 8 G)のいずれかの処理の実行が省略されることを特徴とするものである。

10

20

30

40

#### [0181]

前記実施の形態によれば、複数の割り込み要因に対する処理での重複処理の矛盾を解消する際の負担が軽減された半導体集積回路を提供することができる。

## [0182]

好適な実施の形態では、前記タイマ割り込みの前記発生に応答して前記第 2 処理ユニットが前記パケットカウンタから取得した前記処理済みパケット数が前記所定のパケット数よりも小さい場合には、前記入力中断の前に前記第 1 処理ユニット(1 2)によって処理された前記処理済みデータの前記第 2 処理ユニット(1 3、1 8)による前記タイマ割り込みの前記発生(1 8 C)に応答する前記処理(1 8 I)の実行が省略される一方、前記第 1 処理ユニット(1 2)によって処理された前記処理済みデータの前記第 2 処理ユニット(1 3、1 8)による前記第 1 処理完了割り込みの前記発生(1 8 E)に応答する前記第 2 処理(1 8 G)が実行されるものである(図 1 8 (A)参照)。

#### [0183]

前記タイマ割り込みの前記発生に応答して前記第2処理ユニットが前記パケットカウンタから取得した前記処理済みパケット数が前記所定のパケット数と等しい場合には、前記入力中断の前および前記入力再開後に前記第1処理ユニット(12)によって処理された前記処理済みデータの前記第2処理ユニット(13、18)による前記タイマ割り込みの前記発生(18C)に応答する前記処理(18I)の実行される一方、前記第1処理ユニット(12)によって処理された前記処理済みデータの前記第2処理ユニット(13、18)による前記第1処理完了割り込みの前記発生(18E)に応答する前記第2処理(18G)の実行が省略されるものである(図18(B)参照)。

#### [0184]

他の好適な実施の形態では、前記第 2 処理ユニット(13、18)は中央処理ユニット(CPU)を含み、前記第 1 処理ユニット(12)は他の処理ユニット(DMAC) を含むものである(図 15 参照)。

# [0185]

より好適な実施の形態では、前記第1処理完了割り込みの優先度は前記タイマ割り込みの優先度よりも高く設定されたものである。

## [0186]

# 2.実施の形態の詳細

次に、実施の形態について更に詳述する。尚、発明を実施するための最良の形態を説明するための全図において、前記の図と同一の機能を有する部品には同一の符号を付して、その繰り返しの説明は省略する。

# [0187]

# [実施の形態1]

《アプリケーションプロセッサの構成》

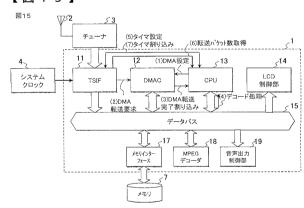

図 1 5 は、本発明の実施の形態 1 によるアプリケーションプロセッサの構成を示すブロック図である。

## [0188]

図 1 5 に示すアプリケーションプロセッサ 1 は、図 1 と同様にTSIF 1 1 、 D M A C 1 2 、 C P U 1 3 、 L C D 制御部 1 4 、データバス 1 5 、メモリインターフェース 1 7 、 M P E G デコーダ 1 8 、音声出力制御部 1 9 を含んでいる。

#### [0189]

図1と同様に図15では携帯電話端末に搭載されるデジタルテレビアンテナ2によってISDB-Tmmの次世代ワンセグ放送が受信され、外部デジタルテレビチューナー3の出力端子からアプリケーションプロセッサ1のTSIF11の入力端子にMPEG2-TSのパケットデータが供給される。外部のシステムクロック発生器4からTSIF11に、基準クロックとしてのシステムクロック信号が供給される。また更に、TSIF11に供給されたMPEG2-TSのパケットデータは、内蔵DMAC12にて実行されるDMA転送によってデータバス15とメモリインターフェース17とを介して外部のメモリ7

10

20

30

40

に転送される。外部メモリ7としては、高速・大容量の同期DRAMが使用可能である。 【 0 1 9 0 】

図 1 5 に示すアプリケーションプロセッサ 1 に含まれた各構成要素 1 1 ~ 1 5 、 1 7 ~ 1 9 は図 1 に示すアプリケーションプロセッサ 1 に含まれたそれらと同一の動作であるので、これらの説明は省略する。

# [0191]

しかし、図15に示すアプリケーションプロセッサ1では、図1に示すアプリケーションプロセッサ1に含まれたタイマ16が省略されている。その代わり、図15で省略された図1のタイマ16と同等の機能は、図15に示すアプリケーションプロセッサ1に含まれたTSIF11によって実現されるものである。

[0192]

《TSIFの構成》

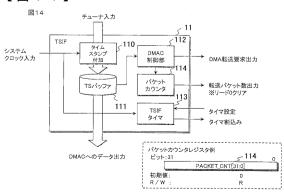

図 1 4 は、図 1 5 に示すアプリケーションプロセッサ 1 に含まれたTSIF 1 1 の構成を示す図である。

[0193]

[0194]

図14に示すTSIF11のタイムスタンプ付加部110とTSバッファ111とDMAC制御部112の構成と動作は、図2に示したTSIF11のそれらと同様であるので、これらの説明は省略する。

[ 0 1 9 5 ]

TSIFタイマ113は、図1のタイマ16の代わりに、CPU13にタイマ割込みを発生させる機能を有している。このタイマ113のリソースは、タイムスタンプを付加するために使用しているシステムクロック生成器4から供給されるシステムクロック信号を利用するものである。この例ではシステムクロックを利用しているが、別のクロック信号を利用することもできる。また更に、TSIFタイマ113外部のクロック生成器を利用することもできる。タイマ16と同様に、TSIFタイマ113はカウンタによって構成されて、TSIFタイマ113はカウンタによって信が大つで設定されることによって計数動作を実行する。この計数動作による所定のカウント時間の間にMPEG2・TSの所定数の複数パケットのDMAC12によるDMAC転送が未完了の場合には、TSIFタイマ113はCPU13のDMACタイマ制御部133に(7)タイマ割り込みを実行する。この(7)タイマ割り込みに応答して、CPU13は外部メモリ7にDMAC転送済みのパケットの早期のトランスポートストリーム(TS)解析とデータ処理による(4)デコード処理を開始するものである。

[0196]

パケットカウンタ114は、DMAC12によるDMA転送を完了した192バイトのパケットの転送数をカウントする機能を有している。図14の右下に示すように、例えばパケットカウンタ114のカウント値PACKET\_CNTは32ビットである。カウント値PACKET\_CNTの初期値はゼロであって、DMAC12による192バイトのパケットのDMA転送毎にカウントアップされる。パケットカウンタ114の読み出し動作Rによって、CPU13がカウント値PACKET\_CNTを読み出すと、カウント値PACKET CNTはゼロにリセットされる。

[0197]

《強電界の場合の制御》

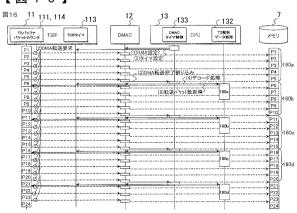

図16は、強電界の場合のMPEG2-TSの流れの制御を図14に示すTSIF11を含む図15に示すアプリケーションプロセッサ1の各部で詳細に観測した図である。

[0198]

10

20

30

40

20

30

40

50

図 1 6 では図 1 0 と異なり、 C P U 1 3 の D M A タイマ制御部 1 3 3 は、タイマ 1 6 に (5)タイマ設定を実行するのではなく、図 1 4 の T S I F 1 1 に含まれた T S I F タイマ 1 1 3 に(5)タイマ設定を実行する。

## [0199]

また、図16では、DMAC12によるDMA転送済みの転送パケット数は、図14に示したTSIF11のパケットカウンタ114に格納されることが可能である。すなわち、MPEG2-TSの192バイトの1個のパケットのDMAC12によるTSIF11のTSバッファ111から外部メモリ7へのDMA転送の実行が完了する毎に、パケットカウンタ114に格納される転送パケット数が1個のパケット分、増加される。このようにして、複数のパケットのDMA転送の間に、パケットカウンタ114に格納される転送パケット数は更新される。

#### [0200]

また、(3) DMA転送完了割り込みもしくは(7)タイマ割り込みに応答して、CPU13のTS解析データ処理部132は(6)転送パケット数取得を行って、外部メモリ7にDMAC転送済みの受信パケットデータに含まれたパケットの個数を認識する。この(6)転送パケット数取得では、CPU13のTS解析データ処理部132はTSIF11のパケットカウンタ114の更新値を読み出し、その後の(4)デコード処理にて処理されるパケットの個数が取得される。このようにして、CPU13によるTSIF11のパケットカウンタ114の更新値の読み出しが完了すると、パケットカウンタ114の値PACKET\_CNTはゼロにリセットされる。

#### [0201]

図 1 6 でも図 8 と同様に、最初に C P U 1 3 の D M A タイマ制御部 1 3 3 は、 D M A C 1 2 に(1) D M A 設定を実行する。この(1) D M A 設定では、例えば 5 パケット(1 9 2 バイト×5)の D M A 転送データサイズが指定される。すると、 D M A C 1 2 は、 T S I F 1 1 の D M A C 制御部 1 1 2 からの D M A C 転送要求を待つ状態となる。

## [0202]

次に、TSIF11のTSバッファ111へのMPEG2-TSの最初のパケットP1の受信が完了すると、TSIF11のDMAC制御部112はDMAC12に(2)DMA転送要求を出力する。TSIF11のTSバッファ111への最初のパケットP1の受信完了により出力される(2)DMA転送要求に応答して、CPU13のDMAタイマ制御部133はTSIF11に含まれたTSIFタイマ113の計数動作を開始する。更にDMAC12は上述の(2)DMA転送要求に応答してTSIF11のTSバッファ111に一時的に格納された最初のパケットP1を読み出して、外部メモリ7へのDMA転送を実行する。同様に、TSIF11のTSバッファ111へのMPEG2-TSの2番目のパケットP2、3番目のパケットP3、4番目のパケットP4、5番目のパケットP5の受信がそれぞれ完了すると、各受信完了時点でTSIF11のDMAC12は(2)各DMA て12に(2)DMA転送要求をそれぞれ出力する。更に、DMAC12は(2)各DMA転送要求に応答してTSIF11のTSバッファ111に一時的に格納された2番目のパケットP2から5番目のパケットP5までのデータを読み出し、外部メモリ7へのDMA転送を実行する。

# [0203]

このようにして、最初のパケットP1から5番目のパケットP5までのデータ160aのTSIF11から外部メモリ7へのDMA転送が完了すると、DMAC12はCPU13のDMAタイマ制御部133に(3)5パケット単位のデータ160aのDMA転送完了割り込みを通知する。するとCPU13のTS解析データ処理部132は、5パケット単位のDMA転送完了割り込みに応答して、5パケット単位のデータ160aのトランスポートストリーム解析とデータ処理とによる(4)デコード処理を実行する。尚、この(4)デコード処理の開始に先立って、CPU13のTS解析データ処理部132はTSIF11のパケットカウンタ114の読み出しによる(6)転送パケット数取得を行って、外部メモリ7にDMAC転送済みの1番目の受信パケットデータ160aに含まれたパケットP1

~ P 5 の個数を認識する。更にM P E G 2 - T S の後続の 5 パケット単位のパケット P 6 ~ P 1 0、 P 1 1 ~ P 1 5 のデータ 1 6 0 b、 1 6 0 c に関して、上述と同様な 5 パケット単位のデータの D M A 転送完了割り込みおよび 5 パケット単位のデータの T S 解析とデータ処理とによる(4)デコード処理が繰り返される。

# [0204]

#### 《弱電界の場合の制御》

図17は、複数パケット単位のDMA転送完了割り込みとタイマ割り込みを採用した際に強電界から弱電界に変化する場合のMPEG2-TSの流れの制御を図15に示した本発明の実施の形態1によるアプリケーションプロセッサ1の各部で詳細に観測した図である。

## [0205]

図 1 7 (A)は(7)タイマ割り込みと(3) D M A 転送完了割り込みの時間差が比較的大きく、タイマ割り込みによるデコード処理が滞った場合の処理を説明する図であり、図 1 7 (B)は(7)タイマ割り込みと(3) D M A 転送完了割り込みの時間差が比較的小さな場合の処理を説明する図である。

#### [0206]

(7)タイマ割り込みと(3)DMA転送完了割り込みとの時間差が比較的大きく、タイマ割り込みによるデコード処理が滞った場合の図17(A)では、特にTSIF11の直下に、TSIF11のパケットカウンタ114の値が示されている。パケットカウンタ114の値は、(2)DMA転送要求に応答するMPEG2-TSの192バイトの1個のパケットのDMAC12によるTSIF11のTSバッファ111から外部メモリ7へのDMA転送の実行が完了する毎に、1個のパケット分増加される。また、パケットカウンタ114の値は、(6)転送パケット数取得に応答して、CPU13のTS解析データ処理部132がTSIF11のパケットカウンタ114の更新値を読み出すと、ゼロにリセットされる。

# [0207]

図 1 7 (A)でも、図 9 と図 1 0 と図 1 6 と同様に最初の 5 パケット単位のパケット P 1 ~ P 5 のデータ 1 7 0 a に関して、 T S I F 1 1 への受信、 D M A C 1 2 による T S I F 1 1 から外部メモリ 7 への D M A 転送、 C P U 1 3 による T S 解析とデータ処理による(4) デコード処理が実行される。図 1 7 (A)のこの動作は、図 9 と図 1 0 と図 1 6 と全く同様であるので、詳細な説明を省略する。

# [0208]

また図17(A)でも、図9と図10と同様に、2番目の5パケット単位のデータ170 bの3個のパケットP6~P8に関して、TSIF11への受信とDMAC12によるT SIF11から外部メモリ7へのDMA転送とが実行された後、強電界から弱電界に変化 して、データ170bに含まれるパケットP9~P16のMPEG2-TSがTSIF1 1によって受信不可能の受信中断状態となる。

## [0209]

更に図17(A)でも、図9と図10と同様に、同様に弱電界から強電界へ復帰すると、 3番目の受信パケットデータ170cの2個のパケットP17、P18がTSIF11に よって受信されるようになる。

# [0210]

図10の処理では、図12の処理に示したように、弱電界による受信中断状態の間にタイマ16による低優先度の(7)タイマ割り込み12Cが弱電界から強電界への復帰の後のDMAC12による高優先度の(3)DMAC転送完了割り込み12Eよりも先に発生すると、誤動作が発生されるものであった。

#### [0211]

すなわち、図10の処理では、図12の処理に示したように、後の高優先度の(3)DMAC転送完了割り込み12Eに応答した先の(4)デコード処理12Hと先の低優先度の(7)タイマ割り込み12Cに応答した後の(4)デコード処理12Kとの重複処理12Mに

10

20

30

20

30

40

50

よって、誤動作が発生していた。尚、後の高優先度の(3) DMAC転送完了割り込み12 Eに応答する先の(4) デコード処理12 Hは、受信再開後に受信された3番目の受信パケットデータ100 cの2個のパケットP17、P18の(4) デコード処理である。また、先の低優先度の(7) タイマ割り込み12 Cに応答する後の(4) デコード処理12 Kは、弱電界による受信中断状態前に受信された2番目の受信パケットデータ100 bに含まれた3個のパケットP6~P8の(4) デコード処理12 Kである。

#### [0212]

しかし図 1 7 (A)の処理では、弱電界による受信中断状態の間にタイマ 1 1 3 による低 優先度の(7)タイマ割り込みに応答したCPU13のTS解析データ処理部132の(6) 転送パケット数取得後、何らかの要因によりデコード処理が滞った状態で、しばらくして 弱電界から強電界への復帰の後のDMAC12による高優先度の(3)DMAC転送完了割 り込みが発生している。このような場合には、先の低い優先度の(7)タイマ割り込みによ る(6)転送パケット数取得に応答する受信中断状態前の2番目の受信パケットデータ17 0 b の合計 5 7 6 バイトの 3 個のパケット P 6 ~ P 8 に関する(4) デコード処理は、高優 先度の(3)DMAC転送完了割り込みによって、実行されずに、保留される。しかし、弱 電界による受信中断状態の間に低い優先度の(7)タイマ割り込みに応答したCPU13の (6)転送パケット数取得の後、所定の経過時間内に高優先度の(3)DMAC転送完了割り 込みが発生しない場合には、保留されていた受信中断状態の前の2番目の受信パケットデ ータ170bの合計576バイトの3個のパケットP6~P8に関する(4)デコード処理 が所定の経過時間の経過後に実行されるものである。また弱電界による受信中断状態の間 に低優先度の(7)タイマ割り込みに応答したCPU13の(6)転送パケット数取得の後、 所定の経過時間内に高い優先度の(3)DMAC転送完了割り込みが発生しないことは、C PU13のDMACタイマ制御部133に配置されるタイマによって検出することが可能 である。

# [0213]

更に、強電界への復帰の後のDMAC12による高優先度の(3)DMAC転送完了割り込みに応答して、CPU13のTS解析データ処理部132はTSIF11のパケットカウンタ114から(6)転送パケット数取得を実行する。この時には、受信再開後の3番目の受信パケットデータ170cの合計384バイトの2個のパケットP17、P18に関してDMAC12によるDMAC転送が完了している。従って、後の高い優先度の(3)DMAC転送完了割り込みによる(6)転送パケット数取得に応答する受信再開後の3番目の受信パケットデータ170cの合計384バイトの2個のパケットP17、P18に関して、(4)デコード処理が実行されるものとなる。受信再開後の3番目の受信パケットデータ170cの2個のパケットP17、P18に関する(6)転送パケット数取得による(4)デコード処理の実行時には、受信中断状態の前の2番目の受信パケットデータ170bの3個のパケットP6~P8に関する(6)転送パケット数取得の情報と(4)デコード処理のための情報とが破棄される。

## [0214]

このようにして、図17(A)の処理では、図10の処理で発生していた後の高優先度の(3)DMAC転送完了割り込みに応答した先の(4)デコード処理と先の低優先度の(7)タイマ割り込みに応答した後の(4)デコード処理との逆転処理と誤動作との発生を回避することが可能となる。

## [0215]

(7)タイマ割り込みと(3)DMA転送完了割り込みとの時間差が比較的小さな場合の図17(B)でも、特にTSIF11の直下に、TSIF11のパケットカウンタ114の値が示されている。図17(B)でも、図17(A)と同様に、強電界から弱電界への変化による受信中断と弱電界から強電界への変化による受信再開とが発生している。しかし、図17(B)では、弱電界の受信中断状態によるタイマ113による低優先度の(7)タイマ割り込み発生のタイミングが、弱電界から強電界への変化による受信再開後の状態まで遅延している。従って、先の低い優先度の(7)タイマ割り込みによる(6)転送パケット数取得に

20

30

40

50

応答して、受信中断状態前に受信された2番目の受信パケット170bの3個のパケットP6~P8と受信再開の後の3番目の受信パケットデータ170cの2個のパケットP17、P18の合計5個のパケットの値がTSIF11のパケットカウンタ114の値としてCPU13のTS解析データ処理部132により読み出される。このようにして、受信中断状態前に受信された2番目の受信パケット170bの3個のパケットP6~P8と受信再開の後の3番目の受信パケットデータ170cの2個のパケットP17、P18の合計5個のパケットに関して、(4)デコード処理が実行されるものとなる。

## [0216]

このようにして、図17(B)の処理では、図10の処理で発生していた後の高優先度の(3)DMAC転送完了割り込みに応答した先の(4)デコード処理と先の低優先度の(7)タイマ割り込みに応答した後の(4)デコード処理との重複処理と誤動作との発生を回避することが可能となる。

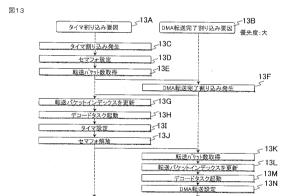

# [0217]

《重複処理を回避する処理》

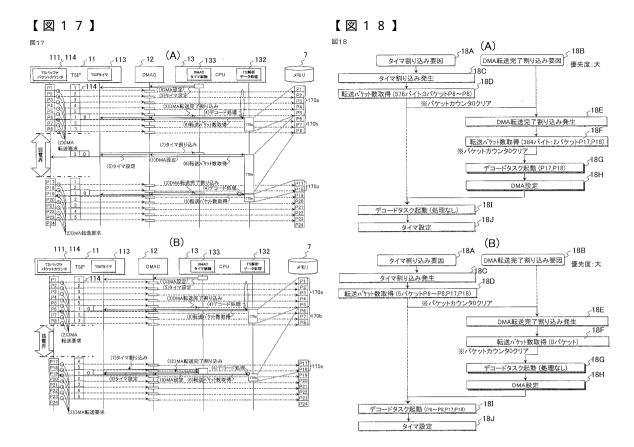

図18は、図17の処理で後の高優先度の(3)DMAC転送完了割り込みに応答した先のデコード処理と先の低優先度の(7)タイマ割り込みに応答した後のデコード処理との逆転処理あるいは重複処理を回避する処理を説明する図である。

#### [0218]

図18(A)は優先度が低いタイマ割り込み発生18Cと優先度が高いDMA転送完了割り込み発生18Eとの時間差が比較的大きく、タイマ割り込みによるデコード処理が滞った場合の処理を説明する図であり、図18(B)は優先度が低いタイマ割り込み発生18Cと優先度が高いDMA転送完了割り込み発生18Eとの時間差が比較的小さな場合の処理を説明する図である。

#### [0219]

時間差が比較的大きく、タイマ割り込みによるデコード処理が滞った場合の図 1 8 (A) でも、図12(A)と同様に複数の割り込み要因としてタイマ割り込み要因18AとDMA 転送完了割り込み要因18Bとが存在しているが、優先度が高い(3)DMA転送完了割り 込み発生18Eより先に優先度が低い(7)タイマ割り込み発生18Cが発生している。し かし、この先の低優先度の(7)タイマ割り込み発生18Cに応答した受信中断状態前の2 番目の受信パケットデータ 1 7 0 b の合計 5 7 6 バイトの 3 個のパケットP 6 ~ P 8 に関 する(6)転送パケット数取得18Dの後、タイマ割り込みによるデコード処理が滞った状 態でしばらくして後の高い優先度の(3)DMA転送完了割り込み発生18Eが発生してい る。従って、先の低優先度の(7)タイマ割り込み18Cによる(6)転送パケット数取得1 8Dに応答する受信中断状態前の2番目の受信パケットデータ170bの3個のパケット P 6 ~ P 8 に関する(4)デコード処理は、高優先度の(3) D M A C 転送完了割り込みによ って、実行されずに保留される。尚、先の低い優先度の(7)タイマ割り込み発生18Cに 応答した(6)転送パケット数取得18Dによって、TSIF11のパケットカウンタ11 4の値はゼロにリセットされる。しかし、弱電界による受信中断状態の間に低優先度の( 7)タイマ割り込み18Cに応答したCPU13の(6)転送パケット数取得18Dの後、 所定の経過時間内に高優先度の(3)DMAC転送完了割り込み18Eが発生しない場合に は、保留されていた受信中断状態の前の2番目の受信パケットデータ170bの合計57 6 バイトの3個のパケットP6~P8に関する(4)デコード処理が所定の経過時間の経過 後にステップ18Iで実行されるものである。上述したように、弱電界による受信中断状 態の間に低優先度の( 7 )タイマ割り込み18Cに応答したCPU13の( 6 )転送パケット 数取得18Dの後、所定の経過時間内に高優先度の(3)DMAC転送完了割り込み18E が発生しないことは、CPU13のDMACタイマ制御部133に配置されるタイマによ って検出することが可能である。

#### [0220]

その後、後の高い優先度の(3)DMA転送完了割り込み発生18Eに応答した(6)転送パケット数取得18Fによって、受信再開後の3番目の受信パケットデータ170cの2

個のパケット P 1 7、 P 1 8 に関する転送パケット数が取得される。その結果、その後の (4) デコード処理のステップ 1 8 G にて、後の高優先度の(3) D M A 転送完了割り込み発生 1 8 E による(6) 転送パケット数取得 1 8 F に応答する受信再開の後の 3 番目の受信パケットデータ 1 7 0 c の 2 個のパケット P 1 7、 P 1 8 に関して(4) デコード処理 1 8 G が実行されることが可能となる。尚、後の高い優先度の(3) D M A 転送完了割り込み発生 1 8 E による(6) 転送パケット数取得 1 8 F によって、 T S I F 1 1 のパケットカウンタ 1 1 4 の値はゼロにリセットされる。尚、(4) デコード処理 1 8 G の実行時には、受信中断状態の前の 2 番目の受信パケットデータ 1 7 0 b の合計 5 7 6 バイトの 3 個のパケット P 6 ~ P 8 に関する(6) 転送パケット数取得の情報と(4) デコード処理のための情報とは破棄されるものである。

[0221]

[0222]

時間差が比較的小さな場合の図18(B)でも、時間差が比較的大きな場合の図18(A)と同様に複数の割り込み要因としてタイマ割り込み要因18AとDMA転送完了割り込み発生18Eより先に優先度が低い(7)タイマ割り込み発生18Cが発生している。しかし、この先の低優先度の(7)タイマ割り込み発生18Cに応答した受信中断状態前の2番目の受信パケットデータ1706〜アットデータ170mの合計5個のパケットP6〜ア8、ア17、ア18に関する(6)転送パケット数取得18Dの直後に、後の高い優先度の(3)DMA転送完了割り込み発生18Eによって先の低優先度の(7)タイマ割り込み18Cによる(6)転送パケット数取得18Dに応答する合計5個のパケットア8〜ア8、ア17、ア18に関する(4)デコード処理は、実行されずに一時的に保留されることになる。尚、先の低優先度の(7)タイマ割り込み発生18Cに応答した(6)転送パケット数取得18Dに応答する合計5個のパケットア

[0223]

その後、処理は先の低優先度の(7)タイマ割り込み発生18Cに応答した処理から、後の高い優先度の(3)DMA転送完了割り込み発生18Eに応答した処理に移行するものである。その結果、後の高優先度の(3)DMA転送完了割り込み発生18Eに応答した(6)転送パケット数取得18Fによって、パケットカウンタ114からリセットされた値であるゼロが読み出される。従って、その後の(4)デコード処理のステップ18Gでは実質的なデコード処理は実行されない。(4)デコード処理のステップ18Gでは実質的なデコード処理は実行されないことによって、受信中断状態の前後の合計5個のパケットP6~P8、P17、P18に関する(6)転送パケット数取得18Dの情報と(4)デコード処理のための情報とは、破棄されることなく、CPU13のTS解析データ処理部132の内部に保存されている。その次のステップ18Hでは、CPU13のDMACタイマ制御部133は(1)DMA設定を実行する。その後に、処理は後の高い優先度の(3)DMA転送完了割り込み発生18Eに応答した処理から、先の低優先度の(7)タイマ割り込み発生18

[0224]

10

20

30

このようにして、優先の低優先度の(7)タイマ割り込み発生18Cに応答した(4)デコード処理のステップ18Iの処理に戻される。上述したように、先の低い優先度の(7)タイマ割り込み発生18Cに応答した(6)転送パケット数取得18Dに関する合計5個のパケットP6~P8、P17、P18の(4)デコード処理の情報は、CPU13のTS解析データ処理部132の内部に保存されている。従って、ステップ18Iの(4)デコード処理が再開されて、パケット数5個のP6~P8、P17、P18のデコード処理が実行される。またステップ18Jで、CPU13のDMACタイマ制御部133は(5)タイマ設定を実行するものである。

## [0225]

このようにして、図14から図18に示した本発明の実施の形態1によれば、図13に示したような長い処理時間の必要なセマフォ制御を採用する必要が無いので、複数の割り込み要因を処理する際の処理の負担を軽減することが可能となる。

#### [0226]

以上、本発明者によってなされた発明を種々の実施の形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

## [0227]

#### 「他の実施の形態]

例えば、本発明の実施の形態によるアプリケーションプロセッサは、地上ディジタル放送のワンセグ放送の受信に限定されるものではなく、ワンセグ放送以外のブルートース電波の受信や無線LANの電波を受信する際等にも広く適用することができる。

#### [0228]

従って、図15に示すアプリケーションプロセッサ1においては、MPEG2-TSを受信するTSIF(トランスポートストリームインターフェース)11の代わりに、種々の受信電波に基づく受信ビットストリームデータを入力してまた送信電波を生成するため送信ビットストリームを出力するデータI/Oインターフェースを使用することも可能である。

## [0229]

また、図15に示すアプリケーションプロセッサ1において、(7)タイマ割り込み、もしくは、(3)DMA転送完了割り込みに応答して実行される処理は、CPU13によるデマルチプレックス(DEMUX)処理の後のMPEGデコーダ18による映像および音声の復号による(4)デコード処理に限定されるものではない。例えば、それ以外の処理としては、CPU13または他のコプロセッサや他のアクセラレータによる種々のデータ処理が想定されるものである。

# [0230]

更に、図15に示すアプリケーションプロセッサ1において、(7)タイマ割り込み、もしくは、(3)DMA転送完了割り込みを生成する処理は、DMAC12によるDMA転送に限定されるものではない。例えば、それ以外の処理としては、CPU13または他のコプロセッサや他のアクセラレータによる長い処理時間で重い処理負担の種々のデータ処理が想定されるものである。

# 【符号の説明】

## [0231]

- 1 ... アプリケーションプロセッサ

- 2 ... デジタルテレビアンテナ

- 3 ... 外部デジタルテレビチューナー

- 4 ... システムクロック生成器

- 5 ...液晶表示装置

- 6 ... スピーカ

- 7 ... 外部メモリ

- 1 1 ... トランスポートストリームインターフェース(TSIF)

40

30

10

20

- 13...中央処理ユニット(CPU)

- 14…液晶表示制御部

- 15…データバス

- 16…タイマ

- 17...メモリインターフェース

- 18...MPEGデコーダ

- 19...音声出力制御部

- 1 1 0 ... タイムスタンプ付加部

- 1111...トランスポートストリームバッファ

- 1 1 2 ... D M A C 制御部

- 1 1 3 ... T S I F タイマ

- 114...パケットカウンタ

- 1 3 1 ... D M A C 制御処理部

- 132...TS解析データ処理部

- 133... D M A C タイマ制御部

# 【図3】

【図4】

メモリ

# 【図7】

# 【図6】

ァ (3)DMA転送完了割り込み

# 【図8】

<sub><12</sub> (A) <sub><13</sub> <sub>133</sub>

# 【図9】

図9

【図10】

P4 P5

## 【図11】

図11

# 【図12】

# 【図13】

# 【図15】

## 【図14】

【図16】

# フロントページの続き

# 審査官 稲葉 崇

(56)参考文献 特開2005-267294(JP,A)

特開平10-207822(JP,A)

国際公開第2007/094611(WO,A1)

(58)調査した分野(Int.CI., DB名)

G06F 13/20-13/378

G06F 13/38-13/42

G06F 13/00

H04N 7/10, 7/14 - 7/173

H04N 7/20-7/22

H04N 21/00-21/858

H04N 5/76

H04B 1/16