### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-109902 (P2010-109902A)

(43) 公開日 平成22年5月13日(2010.5.13)

| (51) Int.Cl. |           | F I         |              | テーマコード (参考) |

|--------------|-----------|-------------|--------------|-------------|

| HO4N 5/335   | (2006.01) | HO4N 5/335  | $\mathbf{E}$ | 4M118       |

| HO4N 9/07    | (2006.01) | HO4N 9/07   | Α            | 50024       |

| HO1L 27/146  | (2006.01) | HO1L 27/14  | Α            | 5CO65       |

| HO4N 101/00  | (2006.01) | HO4N 101:00 |              |             |

|                    |                                                          | 審査請求     | 未請求 請求項の数 22 OL (全 37 頁)                                              |  |  |  |

|--------------------|----------------------------------------------------------|----------|-----------------------------------------------------------------------|--|--|--|

| (21) 出願番号 (22) 出願日 | 特願2008-282155 (P2008-282155)<br>平成20年10月31日 (2008.10.31) | (71) 出願人 | 000005821<br>パナソニック株式会社<br>大阪府門真市大字門真1006番地<br>100109210<br>弁理士 新居 広守 |  |  |  |

|                    |                                                          | (74)代理人  |                                                                       |  |  |  |

|                    |                                                          | (72) 発明者 | 加藤 剛久<br>大阪府門真市大字門真1006番地 パナ<br>ソニック株式会社内                             |  |  |  |

|                    |                                                          | (72) 発明者 | 春日繁孝                                                                  |  |  |  |

|                    |                                                          |          | 大阪府門真市大字門真1006番地 パナ<br>ソニック株式会社内                                      |  |  |  |

|                    |                                                          | (72) 発明者 | 村田 隆彦<br>大阪府門真市大字門真1006番地 パナ<br>ソニック株式会社内                             |  |  |  |

|                    |                                                          |          | 最終頁に続く                                                                |  |  |  |

(54) 【発明の名称】固体撮像装置及びその駆動方法

# (57)【要約】

【課題】広いダイナミックレンジを有する固体撮像装置 の画素出力信号が容易に補正され、画素間の輝度ばらつ きやカラー信号の偽色の発生が抑止された固体撮像装置 及びその調整方法を提供する。

【解決手段】受光強度及び露光時間に応じた光信号電荷 を発生する受光素子を有する複数の FDA型画素 2 1 が 二次元状に配置されたカラー固体撮像装置20であって 、駆動部25は、受光素子での光信号電荷の飽和量を制 限し、受光素子に蓄積された光信号電荷の一部を残留電 荷量として読み残すようにFDA型画素21を駆動する

【選択図】図2

#### 【特許請求の範囲】

### 【請求項1】

受光強度及び露光時間に応じた光信号電荷を発生する光電変換素子を有する複数の画素部が二次元状に配置された固体撮像装置であって、

前記光電変換素子での前記光信号電荷の飽和量を制限し、前記光電変換素子に蓄積された前記光信号電荷の一部を残留電荷として読み残すように前記画素部を駆動する駆動部を備える

固体撮像装置。

### 【請求項2】

前記画素部は、

前記光電変換素子で発生した前記光信号電荷を転送する転送トランジスタを備え、前記駆動部は、

前記光信号電荷の蓄積時には前記転送トランジスタが不完全なオフ状態となるように第1のゲート電圧を設定することにより前記光信号電荷の飽和量を制限し、前記光信号電荷の読み出し時には前記転送トランジスタが不完全なオン状態となるように第2のゲート電圧を設定することにより前記残留電荷を読み残すように前記画素部を駆動する

請求項1記載の固体撮像装置。

#### 【請求項3】

前記駆動部は、

前記第1のゲート電圧として、接地電位よりも高くなるよう電圧を設定し、

前記第2のゲート電圧として、前記転送トランジスタの導通状態におけるゲート下ポテンシャルが前記光電変換素子の最高ポテンシャルよりも低くなるような電圧を設定する 請求項2記載の固体撮像装置。

#### 【請求項4】

前記画素部は、

前記光電変換素子にリセット電圧を印加するリセットトランジスタを備え、

前記駆動部は、

前記光信号電荷の蓄積時には前記リセットトランジスタが不完全なオフ状態となるように第1のゲート電圧を設定することにより前記光信号電荷の飽和量を制限し、前記光信号電荷のリセット時には前記リセットトランジスタが不完全なオン状態となるように第2のゲート電圧を設定することにより前記残留電荷を読み残すように前記画素部を駆動する請求項1記載の固体撮像装置。

#### 【請求項5】

前記駆動部は、

前記第1のゲート電圧として、接地電位よりも高くなるよう電圧を設定し、

前記第2のゲート電圧として、前記リセットトランジスタの導通状態におけるゲート下ポテンシャルが前記光電変換素子の最高ポテンシャルよりも低くなるような電圧を設定する

請求項4記載の固体撮像装置。

#### 【請求項6】

前記複数の画素部のそれぞれは、前記光信号と前記光電変換素子との間に配置されたカラーフィルタを備え、

前記駆動部は、

制限された前記飽和量と前記残留電荷量との差である信号電荷容量が同一色の画素部では同一となるよう、前記第1のゲート電圧及び前記第2のゲート電圧を設定する

請求項2~5のうちいずれか1項に記載の固体撮像装置。

#### 【請求項7】

前記画素部は、異なる露光時間ごとに前記光電変換素子で発生した複数の光信号電荷に応じた信号電圧を合成する合成部を備える

請求項6記載の固体撮像装置。

10

20

30

00

40

#### 【請求項8】

前記合成部は、前記画素部外に形成されている請求項7記載の固体撮像装置。

### 【請求項9】

前記複数の光信号電荷がそれぞれ制限された前記飽和量に達するときの入射光強度である飽和入射光強度が、同一の露光時間においては全ての前記画素部で同一となるように、前記第1のゲート電圧及び前記第2のゲート電圧を調整する調整部を備える

請求項6~8のうちいずれか1項に記載の固体撮像装置。

### 【請求項10】

前記調整部は、

前記画素部の入射光強度 - 合成信号電圧の特性を、異色のカラーフィルタを有する画素部間で調整するため、前記入射光強度の全範囲において同一の割合で前記合成信号電圧を補正するための一の補正係数を設定する設定部と、

前記画素部ごとに出力される前記合成信号電圧を、前記補正係数を用いて補正する補正部とを備える

請求項9記載の固体撮像装置。

### 【請求項11】

さらに、

前記画素部の有する前記転送トランジスタのゲート端子に接続され、前記転送トランジスタのオンオフ状態を制御する制御信号電圧を前記ゲート端子に与えるゲート制御線を複数備え、

異なるカラーフィルタを有する同行の画素部には、異なる前記ゲート制御線が接続されている

請求項6~10のうちいずれか1項に記載の固体撮像装置。

#### 【請求項12】

さらに、

前記画素部の有する前記リセットトランジスタのゲート端子に接続され、前記リセットトランジスタのオンオフ状態を制御する制御信号電圧を前記ゲート端子に与えるゲート制御線を複数備え、

異なるカラーフィルタを有する同行の画素部には、異なる前記ゲート制御線が接続されている

請求項6~10のうちいずれか1項に記載の固体撮像装置。

#### 【請求項13】

前記複数の画素部のそれぞれは、前記光信号と前記光電変換素子との間に配置されたカラーフィルタを備え、

前記駆動部は、

全画素部の有する前記光電変換素子において、制限された前記飽和量と前記残留電荷量との差である信号電荷容量が同一となるよう、全画素部に共通の前記第 1 のゲート電圧及び前記第 2 のゲート電圧を設定する

請求項2~5のうちいずれか1項に記載の固体撮像装置。

# 【請求項14】

異なる露光時間ごとに前記光電変換素子で発生した複数の光信号電荷に応じた信号電圧 を合成する合成部を備える

請求項13記載の固体撮像装置。

#### 【請求項15】

前記合成部は、前記画素部外に形成されている請求項14記載の固体撮像装置。

#### 【請求項16】

前記画素部ごとに出力される、前記合成部で合成された前記信号電圧を調整する調整部とを備え、

10

20

30

30

40

前記調整部は、

前記画素部の入射光強度・合成信号電圧の特性を、異色のカラーフィルタを有する画素部間で調整するため、前記入射光強度の所定の領域ごとに前記合成信号電圧を増幅する一以上の補正係数を設定する設定部と、

前記画素部ごとに出力される前記合成信号電圧を、前記補正係数を用いて補正する補正部とを備える

請求項13~15のうちいずれか1項に記載の固体撮像装置。

#### 【請求項17】

請求項1から16のうちいずれか1項に記載の固体撮像装置を備えたカメラ。

### 【請求項18】

異なる露光期間ごとに光信号電荷を発生する光電変換素子と前記光電変換素子で得られた前記光信号電荷を転送する転送トランジスタとを備え、前記光信号電荷に応じた信号電圧を合成することにより得られた合成信号電圧を出力する複数の画素部が二次元状に配置された固体撮像装置の駆動方法であって、

第1の露光期間において、前記光電変換素子で発生した光信号電荷の飽和量を制限するよう、前記転送トランジスタのゲート電圧を接地電位よりも高い第1のゲート電圧に設定する第1電圧設定ステップと、

前記第1電圧設定ステップの後、前記光電変換素子で蓄積された光信号電荷を一部残して読み出すよう、前記転送トランジスタのゲート電圧を前記転送トランジスタの導通状態におけるゲート下ポテンシャルが前記光電変換素子の最高ポテンシャルよりも低くなるような第2の電圧に設定する第2電圧設定ステップと、

前記第2電圧設定ステップの後、第1の露光期間と異なる時間を有する第2の露光期間において、前記光電変換素子で発生した光信号電荷の飽和量を制限するよう、前記転送トランジスタのゲート電圧を前記第1のゲート電圧に設定する第3電圧設定ステップと、

前記第3電圧設定ステップの後、前記光電変換素子で蓄積された光信号電荷を一部残して読み出すよう、前記転送トランジスタのゲート電圧を前記第2のゲート電圧に設定する第4電圧設定ステップとを含む

固体撮像装置の駆動方法。

### 【請求項19】

異なる露光期間ごとに光信号電荷を発生する光電変換素子と前記光信号電荷を出力する出力ノードにリセット電圧を印加するリセットトランジスタとを備え、前記光信号電荷に応じた信号電圧を合成することにより得られた合成信号電圧を出力する複数の画素部が二次元状に配置された固体撮像装置の駆動方法であって、

第1の露光期間において、前記光電変換素子で発生した光信号電荷の飽和量を制限するよう、前記リセットトランジスタのゲート電圧を接地電位よりも高い第1のゲート電圧に設定する第1電圧設定ステップと、

前記第1電圧設定ステップの後、前記光電変換素子で蓄積された光信号電荷を一部残してリセットするよう、前記リセットトランジスタのゲート電圧を前記リセットトランジスタの導通状態におけるゲート下ポテンシャルが前記光電変換素子の最高ポテンシャルよりも低くなるような第2の電圧に設定する第2電圧設定ステップと、

前記第2電圧設定ステップの後、第1の露光期間と異なる時間を有する第2の露光期間において、前記光電変換素子で発生した光信号電荷の飽和量を制限するよう、前記リセットトランジスタのゲート電圧を前記第1のゲート電圧に設定する第3電圧設定ステップと

前記第3電圧設定ステップの後、前記光電変換素子で蓄積された光信号電荷を一部残して読み出すよう、前記リセットトランジスタのゲート電圧を前記第2のゲート電圧に設定する第4電圧設定ステップとを含む

固体撮像装置の駆動方法。

#### 【請求項20】

前記第1のゲート電圧は、同色のカラーフィルタを有する画素部では同一の電圧値を有

10

20

30

40

前記第2のゲート電圧は、同色のカラーフィルタを有する画素部では同一の電圧値を有 する

請求項18または19に記載の固体撮像装置の駆動方法。

### 【請求項21】

前記第1のゲート電圧は、全ての画素部で同一の電圧値を有し、

前記第2のゲート電圧は、全ての画素部で同一の電圧値を有する

請求項18または19に記載の固体撮像装置の駆動方法。

#### 【請求項22】

さらに、

前記第1の露光期間及び前記第2の露光期間において前記光電変換素子で発生した光信 号電荷が飽和しないような入射光を入射させる第1入射ステップと、

前記第1入射ステップの間に、各画素部からの前記合成信号電圧を測定する第1電圧測 定ステップと、

前記第1入射ステップの間に、前記第1電圧測定ステップにて測定された前記合成信号 電圧のうち、異色のカラーフィルタを有する画素部間で前記合成信号電圧を比較してゲイ ン調整をする第1調整ステップと、

前記第1調整ステップの後、前記第1の露光期間及び前記第2の露光期間において前記 光電変換素子で発生した光信号電荷を飽和させるような入射光を入射させる第2入射ステ ップと、

前記第2入射ステップの間に、各画素部からの前記合成信号電圧を測定する第2電圧測 定ステップと、

前記第2入射ステップの間に、前記第2電圧測定ステップにて測定された前記合成信号 電圧のうち、異色のカラーフィルタを有する画素部間で前記合成信号電圧を比較してゲイ ン 調 整 し 、 前 記 光 信 号 電 荷 を 飽 和 さ せ る よ う な 入 射 光 の 強 度 が 異 色 の カ ラ ー フ ィ ル タ を 有 する画素部間で同一となるよう前記第1のゲート電圧及び前記第2のゲート電圧とを調整

請求項18記載の固体撮像装置の駆動方法。

【発明の詳細な説明】

# 【技術分野】

[00001]

本 発 明 は 、 固 体 撮 像 装 置 及 び そ の 駆 動 方 法 に 関 し 、 特 に デ ジ タ ル カ メ ラ に 用 い ら れ る 固 体撮像装置及びその駆動方法に関する。

# 【背景技術】

[0002]

従来の固体撮像装置のダイナミックレンジは、 6 0 d B から 8 0 d B 程度であり、肉眼 や 銀 塩 フ ィ ル ム に 匹 敵 す る 1 0 0 d B か ら 1 2 0 d B 程 度 、 あ る い は 車 載 カ メ ラ や 監 視 カ メラ等の用途によってはそれ以上のレベルにまで向上させることが望まれている。

### [00003]

特 許 文 献 1 で は 、 露 光 期 間 の 長 さ を 異 な ら せ て 複 数 の フ レ ー ム を 撮 像 し 、 撮 像 さ れ た 複 数のフレームを合成する技術が開示されている。1フレームで撮影可能な輝度域は、露光 期間の長さに応じて変化するが、特許文献1では、露光時間が異なることにより輝度域が 異なる複数のフレームが合成されることにより、ダイナミックレンジが拡大される。

#### [0004]

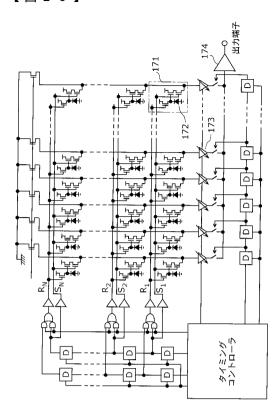

図26は特許文献1記載の固体撮像素子のブロック図である。

# [0005]

同図における固体撮像素子は、画素部171と、フォトダイオード172と、ノイズキ ャンセラ173と、アンプ174とを備える。フォトダイオード172は受光素子である

[0006]

10

20

30

図中に記載されているタイミングコントローラは、上記構成要素を制御し、動作させる画素行や画素列の選択などを実行させる。タイミングコントローラの指示により端子 R i の電圧レベルが H I G H になると、フォトダイオード 1 7 2 のカソードが高い電圧(初期値)に設定される。次に、端子 R i の電圧レベルが L O W になるとフォトダイオード 1 7 2 に入射した光によりカソード電位が低下する積分モードに移る。

### [0007]

端子Siの電圧レベルがHIGHになった行においては、フォトダイオード172のカソード電位が、ノイズキャンセラ173及びアンプ174を介して出力端子に出力される

### [0008]

そして、再び端子Riの電圧レベルがHIGHになると、フォトダイオード172のカソードが高い電圧(初期値)に設定され、新たな積分モードへと移る。

#### [0009]

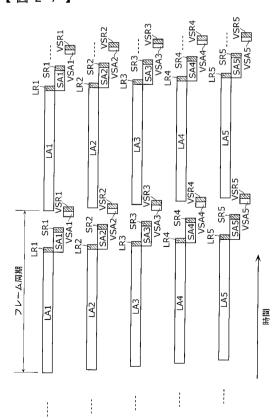

図27は、特許文献1記載の固体撮像素子における露光時間および出力のタイミングを示す図である。同図は、露光時間を、長(LAi:iは自然数)、短(SAi:iは自然数)、極短(VSAi:iは自然数)の3種に分けて、それぞれ積分モードにて得られた信号をそれぞれLRi(iは自然数)、SRi(iは自然数)、VSRi(iは自然数)にて出力するタイミングを示す。LAiは通常光、SAiは強い光、VSAiは大変強い光を受光して電圧変換する場合に対応できるため、広いダイナミックレンジをもった光応答が可能となる。

#### [0010]

しかし、上述した特許文献1の技術では、複数の信号(LAi、SAi、VSAi)を別々に記憶する必要があるため、処理時間がかかる。また、それらを記憶するための記憶部や、合成するための信号合成部を固体撮像素子の外部に設置して後処理を実行しなければならない。

### [0011]

上記問題を解決するため、固体撮像素子の外部に記憶部や信号合成部を必要とせず、複数回の露光で得られた信号を画素内で合成することによりダイナミックレンジを拡大した 固体撮像素子が、非特許文献 1 に提案されている。

# [0012]

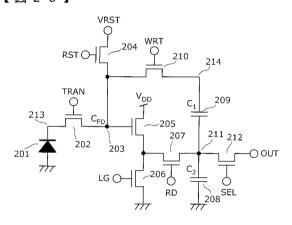

図28は、非特許文献1に記載された固体撮像素子の画素内における回路構成図である。また、図29は、非特許文献1に記載された固体撮像素子の画素回路に印加される電気信号のタイミングチャートである。この多重露光・画素内合成型の固体撮像素子は、図28に示される構成の画素回路を有する。図28に記載された画素回路は、VRST及びLG端子にDC電圧が、また、他の端子に図29に記載された電圧パルスが印加されることにより、3回の露光と2回の信号合成が行われる。

# [0013]

その動作は、リセット(図29中の期間 t 5 0 ~ t 5 1 )、第一の露光(図29中の期間 t 5 1 ~ t 5 2)、第一の露光で光電変換された第一信号のメモリ格納(図29中の期間 t 5 2 ~ t 5 3 )、第二の露光(図29中の期間 t 5 3 ~ t 5 4 )、メモリから第一信号の読み出し(図29中の期間 t 5 4 ~ t 5 5 )、第一信号と第二の露光で光電変換された第二信号との第一合成および第一合成信号のメモリ格納(図29中の期間 t 5 5 ~ t 5 6 )、第三の露光(図29中の期間 t 5 6 ~ t 5 7 )、メモリから第一合成信号の読み出し(図29中の期間 t 5 7 ~ t 5 8 )、及び第三の露光で光電変換された第三信号と第一合成信号との第二合成(図29中の期間 t 5 8 ~ t 5 9 )から成る。

# [0014]

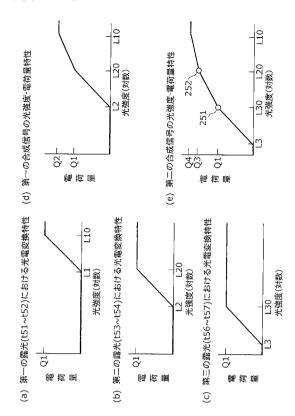

図30(a)、図30(b)及び図30(c)は、それぞれ、非特許文献1に記載された固体撮像素子の有する受光素子の第一の露光期間、第二の露光期間及び第三の露光期間における光電変換特性を表すグラフである。第一、第二及び第三の露光期間である期間 t 5 1 ~ t 5 2、期間 t 5 3 ~ t 5 4、期間 t 5 6 ~ t 5 7 は、順に長くなるように設定さ

10

20

30

40

20

30

40

50

れているので、3つの露光時間における画素に内蔵された受光素子201の光電変換特性は、それぞれ、図30(a)、図30(b)及び図30(c)のようになる。ここで、第一の露光において光電変換される照射光の最低強度L1と、第二の露光で飽和電荷量Q1に達する照射光の強度L20が等しくなるようにし、かつ第二の露光において光電変換される照射光の最低強度L2と、第三の露光で飽和電荷量Q1に達する照射光の強度L30を等しくなるようにする。

### [0015]

上述した一連の動作において、光電変換された電荷を蓄積容量 2 0 8 (  $C_2$  ) に格納し、フィードバック容量 2 0 9 (  $C_1$  ) を介して浮遊容量  $C_{FD}$  に読み出す動作が 2 度 ( 期間 t 5 4 ~ t 5 5 及び期間 t 5 7 ~ t 5 8 ) 行われる。このとき、合成容量  $C_1$  ×  $C_2$  / (  $C_1$  +  $C_2$  ) と浮遊容量  $C_{FD}$  の比に従って信号は圧縮される。

[0016]

図30(d)及び図30(e)は、それぞれ、第一の合成動作期間及び第二の合成動作期間における光電変換特性を表すグラフである。第一の合成動作(期間 t 55~ t 56)において、飽和レベルが圧縮された第一信号と第二信号が浮遊容量 C FD にて合成され、第一合成信号は図30(d)のような光強度・電荷量特性となる。同様に、第二の合成動作(期間 t 58~ t 59)において、飽和レベルが圧縮された第一合成信号と第三信号とが浮遊容量 C FD にて合成され、第二合成信号は図30(e)のような光強度・電荷量特性となる。3回の露光を合成した第二合成信号は、光強度 L 3~ L 30~ L 20~ L 20~ L 10という3つの領域で異なった感度(すなわち、図30に記載されたグラフの傾き)を示すことになる。言い換えれば、図30(e)の光強度・電荷量特性において、2つのニーポイント251(L 30,Q1)及びニーポイント252(L 20,Q3)を有する。

[0017]

上記構成および動作により、異なる露光時間における複数の光信号電荷の短時間合成が画素内で可能となるので、固体撮像素子外部に信号合成部を配置せずとも、ダイナミックレンジの拡張が実現される。

【特許文献 1 】特開 2 0 0 4 - 3 6 3 6 6 6 号公報

【非特許文献 1】ISSCC2008 (International Solid-State Circuits Conference), 2008 年, Digest of Technical Papers, p.50

【発明の開示】

【発明が解決しようとする課題】

[0018]

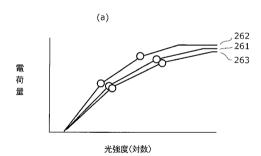

しかしながら、このような多重露光・画素内合成型の固体撮像素子の受光素子201に 3 原 色 の カ ラ ー フ ィ ル タ を 配 置 し て カ ラ ー 固 体 撮 像 素 子 を 形 成 す る と 、 各 色 で 光 電 変 換 特 性が異なるためにニーポイントとなる照射光強度が色毎にずれる。さらに、受光素子20 1の飽和電荷量Q1は画素毎にばらつくため、ニーポイントの電荷量も画素毎にずれる。 図 3 1 ( a ) は、異なる種類のカラーフィルタが配置された画素の有する従来の光強度 -電荷量特性を示すグラフである。3原色のR,G,Bに対応する光強度-電荷量特性は、 それぞれ、光電変換特性261、262及び263である。このような特性を有するR, G,B画素からの出力信号を、各色で固有の率で増幅してホワイトバランス調整を行った 場合、照射光強度領域の一部しかホワイトバランス状態にならない。図31(b)は、R , G , B 画 素 の 有 す る 従 来 の 光 強 度 - 電 荷 量 特 性 を 各 色 固 有 の 増 幅 率 に よ り ホ ワ イ ト バ ラ ンス調整を行った場合の光強度-電荷量特性を示すグラフである。同図に記載されたグラ フには、R,G,B画素からの出力信号に対して、それぞれ、ゲイン1.0、0.9及び 1 . 0 5 の調整を行った結果として得られた光電変換特性 2 7 1 、 2 7 2 及び 2 7 3 が記 載されている。このとき、照射光強度LL以下ではR,G,B出力信号強度を一致させる ことができるが、LL以上ではずれてしまう。つまり、強い光を受光した状態では、合成 画像の輝度ばらつきが発生する。さらに、色ごとの補正がとりにくいため、偽色が発生す るなど綺麗なカラー信号が得られない。

#### [0019]

上記問題に鑑み、本発明は、広いダイナミックレンジを有する固体撮像装置の画素出力信号が容易に補正され、画素間の輝度ばらつきやカラー信号の偽色の発生が抑止された固体撮像装置及びその調整方法を提供することを目的とする。

### 【課題を解決するための手段】

### [0020]

上記目的を達成するために、本発明に係る固体撮像装置は、受光強度及び露光時間に応じた光信号電荷を発生する光電変換素子を有する複数の画素部が二次元状に配置された固体撮像装置であって、前記光電変換素子での前記光信号電荷の飽和量を制限し、前記光電変換素子に蓄積された前記光信号電荷の一部を残留電荷として読み残すように前記画素部を駆動する駆動部を備えることを特徴とする。

#### [0021]

画素ごとに配置された光電変換素子は、製造時における光電変換素子への不純物注入濃度や光信号電荷を読み出すためのトランジスタのゲート絶縁膜厚などのばらつきにより、光信号電荷の飽和量にばらつきを有する。よって、各光電変換素子に固有の飽和量を最大に利用して光信号電荷の蓄積及び読み出しを実行すると、同じ入射光量の光信号が各画素に入射されても、各光電変換素子から読み出される光信号電荷量にばらつきが発生する。よって、各画素から出力される画素出力信号にばらつきが生じ、結果的に輝度信号にばらつきが生じてしまう。

# [ 0 0 2 2 ]

本発明の構成によれば、個々の光電変換素子やトランジスタによって規定される光信号電荷の飽和量が一部制限され、また電荷読み出し量の一部が残留電荷として読み残されることにより、個々の光電変換素子や読み出しトランジスタの構造ばらつきに影響されない任意の基準量に基づいた電荷読み出しが実現される。よって、画素間での光信号電荷量のばらつきを抑制することが可能となる。

### [0023]

また、前記画素部は、前記光電変換素子で発生した前記光信号電荷を転送する転送トランジスタを備え、前記駆動部は、前記光信号電荷の蓄積時には前記転送トランジスタが不完全なオフ状態となるように第1のゲート電圧を設定することにより前記光信号電荷の飽和量を制限し、前記光信号電荷の読み出し時には前記転送トランジスタが不完全なオン状態となるように第2のゲート電圧を設定することにより前記残留電荷を読み残すように前記画素部を駆動してもよい。

#### [0024]

これにより、受光素子から光信号電荷を読み出す転送トランジスタを備えた画素、いわゆるFDA(Floating Diffusion Amplifier)型画素の受光素子に蓄積される、または、受光素子から読み出される光信号電荷量は、転送トランジスタのゲート下ポテンシャルの高さで決まることになる。つまり、光電変換素子や転送トランジスタの構造ばらつきに影響されない、不完全状態におけるゲート電圧に設定することによって、画素間での光信号電荷量を均一化することが可能となる。

#### [0025]

また、前記駆動部は、前記第1のゲート電圧として、接地電位よりも高くなるよう電圧を設定し、前記第2のゲート電圧として、前記転送トランジスタの導通状態におけるゲート下ポテンシャルが前記光電変換素子の最高ポテンシャルよりも低くなるような電圧を設定することが好ましい。

#### [0026]

光信号電荷の蓄積時に、転送トランジスタのゲート電位が接地電位に設定されると、光電変換素子の飽和量は転送トランジスタの閾値電圧に影響される。また、光信号電荷の読み出し時に、転送トランジスタのゲート電位が前記光電変換素子の最高ポテンシャル以上に設定されると、光電変換素子からの電荷読み出し量は当該光電変換素子の最高ポテンシャルのレベルに影響される。上記転送トランジスタの閾値電圧及び上記光電変換素子の最

10

20

30

40

高ポテンシャルレベルは、製造時における光電変換素子への不純物注入濃度や光信号電荷を読み出すためのトランジスタのゲート絶縁膜厚に依存して変化する。本発明のようにゲート電圧が設定されることにより、光電変換素子や転送トランジスタの構造ばらつきに影響されずに画素間での光信号電荷量を均一化することが可能となる。

[0027]

また、前記画素部は、前記光電変換素子にリセット電圧を印加するリセットトランジスタを備え、前記駆動部は、前記光信号電荷の蓄積時には前記リセットトランジスタが不完全なオフ状態となるように第1のゲート電圧を設定することにより前記光信号電荷の飽和量を制限し、前記光信号電荷のリセット時には前記リセットトランジスタが不完全なオン状態となるように第2のゲート電圧を設定することにより前記残留電荷を読み残すように前記画素部を駆動してもよい。

[0028]

これにより、リセットトランジスタが接続された受光素子から光信号電荷を直接読み出す画素、いわゆるAMI(Amplified MOS Imager)型画素の受光素子に蓄積される、または、受光素子から読み出される光信号電荷量は、リセットトランジスタのゲート下ポテンシャルの高さで決まることになる。つまり、光電変換素子やリセットトランジスタの構造ばらつきに影響されない、不完全状態におけるゲート電圧に設定することによって、画素間での光信号電荷量を均一化することが可能となる。

[0029]

また、前記駆動部は、前記第1のゲート電圧として、接地電位よりも高くなるよう電圧を設定し、前記第2のゲート電圧として、前記リセットトランジスタの導通状態におけるゲート下ポテンシャルが前記光電変換素子の最高ポテンシャルよりも低くなるような電圧を設定することが好ましい。

[0030]

光信号電荷の蓄積時に、リセットトランジスタのゲート電位が接地電位に設定されると、光電変換素子の飽和量はリセットトランジスタの閾値電圧に影響される。また、光信号電荷の読み出し時に、リセットトランジスタのゲート電位が前記光電変換素子の最高ポテンシャル以上に設定されると、光電変換素子からの電荷読み出し量は当該光電変換素子の最高ポテンシャルに影響される。上記リセットトランジスタの閾値電圧及び上記光電変換素子の最高ポテンシャルレベルは、製造時における光電変換素子への不純物注入濃度や光信号電荷を読み出すためのトランジスタのゲート絶縁膜厚に依存して変化する。本発明のようにゲート電圧が設定されることにより、光電変換素子やリセットトランジスタの構造ばらつきに影響されずに画素間での光信号電荷量を均一化することが可能となる

[0031]

また、前記複数の画素部のそれぞれは、前記光信号と前記光電変換素子との間に配置されたカラーフィルタを備え、前記駆動部は、制限された前記飽和量と前記残留電荷量との差である信号電荷容量が同一色の画素部では同一となるよう、前記第1のゲート電圧及び前記第2のゲート電圧を設定してもよい。

[0032]

これにより、同一色のカラーフィルタを備える画素間での光信号電荷量のばらつきが抑制される。

[0033]

また、前記画素部は、異なる露光時間ごとに前記光電変換素子で発生した複数の光信号電荷に応じた信号電圧を合成する合成部を備えてもよい。

[0034]

これにより、異なる露光時間で発生した光信号電荷が画素部内で短時間合成されるので、画素間での光信号電荷量のばらつきが抑制された固体撮像素子のダイナミックレンジを拡張することが可能となる。

[0035]

20

10

30

40

また、前記合成部は、前記画素部外に形成されていてもよい。

### [0036]

これにより、固体撮像素子の有する画素ごとに信号合成部を必要としないので、回路素子数が削減され、素子の省面積化が実現される。

### [0037]

また、前記複数の光信号電荷がそれぞれ制限された前記飽和量に達するときの入射光強度である飽和入射光強度が、同一の露光時間においては全ての前記画素部で同一となるように、前記第1のゲート電圧及び前記第2のゲート電圧を調整する調整部を備えることが好ましい。

### [0038]

これにより、多重露光における合成信号の光強度 - 電荷量特性におけるニーポイントとなる入射光強度を、全色で共通とすることが可能となる。このような光強度 - 電荷量特性とすることで、ホワイトバランス調整を容易にすることが可能となる。すなわち、全入射光強度領域にわたって同一の増幅率でホワイトバランス調整することが可能となる。

#### [0039]

また、前記調整部は、前記画素部の入射光強度 - 合成信号電圧の特性を、異色のカラーフィルタを有する画素部間で調整するため、前記入射光強度の全範囲において同一の割合で前記合成信号電圧を補正するための一の補正係数を設定する設定部と、前記画素部ごとに出力される前記合成信号電圧を、前記補正係数を用いて補正する補正部とを備えてもよい。

#### [0040]

これにより、多重露光・画素内合成型の固体撮像素子から出力される信号のホワイトバランス回路を簡便に構成することが可能となる。

#### [0041]

また、さらに、前記画素部の有する前記転送トランジスタのゲート端子に接続され、前記転送トランジスタのオンオフ状態を制御する制御信号電圧を前記ゲート端子に与えるゲート制御線を複数備え、異なるカラーフィルタを有する同行の画素部には、異なる前記ゲート制御線が接続されていてもよい。

### [0042]

これにより、FDA型画素を有する固体撮像装置において、転送トランジスタのゲート 電圧を色毎に設定することができる。

# [ 0 0 4 3 ]

また、さらに、前記画素部の有する前記リセットトランジスタのゲート端子に接続され、前記リセットトランジスタのオンオフ状態を制御する制御信号電圧を前記ゲート端子に与えるゲート制御線を複数備え、異なるカラーフィルタを有する同行の画素部には、異なる前記ゲート制御線が接続されていてもよい。

# [0044]

これにより、AMI型画素を有する固体撮像装置において、リセットトランジスタのゲート電圧を色毎に設定することができる。

### [0045]

また、前記複数の画素部のそれぞれは、前記光信号と前記光電変換素子との間に配置されたカラーフィルタを備え、前記駆動部は、全画素部の有する前記光電変換素子において、制限された前記飽和量と前記残留電荷量との差である信号電荷容量が同一となるよう、全画素部に共通の前記第1のゲート電圧及び前記第2のゲート電圧を設定してもよい。

#### [0046]

これにより、同一露光期間における画素ごとの最大電圧(読み出し電荷容量)が等しくなり、画素間での光信号電荷量のばらつきが抑制される。

#### [0047]

また、前記画素部ごとに出力される、前記合成部で合成された前記信号電圧を調整する調整部とを備え、前記調整部は、前記画素部の入射光強度・合成信号電圧の特性を、異色

10

20

30

•

40

のカラーフィルタを有する画素部間で調整するため、前記入射光強度の所定の領域ごとに前記合成信号電圧を増幅する一以上の補正係数を設定する設定部と、前記画素部ごとに出力される前記合成信号電圧を、前記補正係数を用いて補正する補正部とを備えてもよい。

#### [0048]

これにより、広ダイナミックレンジを有し、偽色の生じないカラー画像信号を生成する ことが可能となる。

#### [0049]

また、本発明は、上記のような特徴を有する固体撮像装置として実現することができるだけでなく、このような固体撮像装置を備えるカメラとしても、上記と同様の構成と効果がある。

### [0050]

また、本発明は、このような特徴的な手段を備える固体撮像装置として実現することができるだけでなく、固体撮像装置に含まれる特徴的な手段をステップとする固体撮像装置の駆動方法として実現することができる。

### 【発明の効果】

#### [ 0 0 5 1 ]

本発明の固体撮像装置及びその調整方法によれば、画素ごとに異なる最大出力電圧(読み出し電荷容量)が均一化される。さらには、各色の画素部で実行される多重露光の入射 光強度 - 合成信号電圧が容易に補正されるので、広いダイナミックレンジが確保された状態でカラー画像信号の輝度バラツキを抑制することができる。

【発明を実施するための最良の形態】

#### [0052]

(実施の形態1)

以下、本発明の実施の形態1に係る固体撮像装置について、図面を参照しながら説明する。

# [0053]

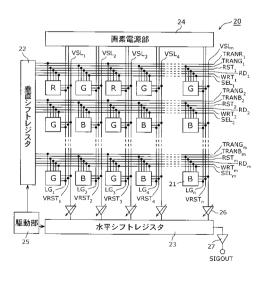

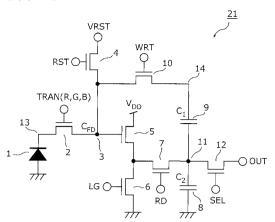

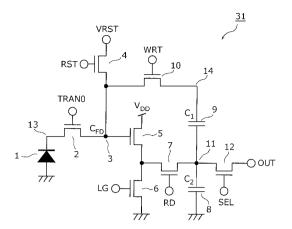

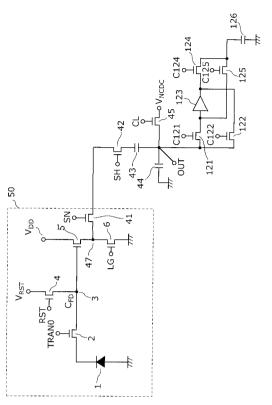

図1は、本発明の実施の形態1における固体撮像装置の有するFDA(Floating Diffusion Amplifier)型画素の回路図である。同図に記載されたFDA型画素21は、画素部であり、受光素子1と、転送トランジスタ2と、浮遊拡散(Floating Diffusion、以下FDと記す)ノード3と、リセットトランジスタ4と、出力トランジスタ5と、負荷トランジスタ6と、読み出しトランジスタ7と、蓄積容量8と、フィードバック容量9と、書き込みトランジスタ10と、蓄積ノード11と、選択トランジスタ12と、負極ノード13、電極ノード14とを備える。

#### [0054]

受光素子1は、転送トランジスタ2を介してFDノード3に接続された光電変換素子である。FDノード3には、出力トランジスタ5のゲートが接続される。出力トランジスタ5は、負荷トランジスタ6とともにソースフォロワ構成の増幅器を構成しており、その出力は読み出しトランジスタ7を介して蓄積ノード11に接続される。

# [0055]

蓄積ノード11と接地線との間には蓄積容量8が挿入され、蓄積ノード11とFDノード3の間にはフィードバック容量9および書き込みトランジスタ10が挿入されるとともに、蓄積ノード11は選択トランジスタ12を介して出力OUTに接続される。

### [0056]

さらに、FDノード3は、リセットトランジスタ4を介してリセット線VRSTが接続される。FDA型画素21を構成する転送トランジスタ2、出力トランジスタ5、負荷トランジスタ6、読み出しトランジスタ7、書き込みトランジスタ10、選択トランジスタ12、リセットトランジスタ4は、全てNチャネル型のMOSトランジスタである。なお、転送トランジスタ2、読み出しトランジスタ7、書き込みトランジスタ10、選択トランジスタ12、リセットトランジスタ4のゲート電極であるTRAN(R,G,B)、RD、WRT、SEL及びRSTには外部より制御信号が入力され、負荷トランジスタ6の

10

20

30

40

ゲート電極 L G およびリセット線 V R S T には D C 電圧 V LG および V RST が印加される。

### [0057]

F D A 型画素 2 1 を構成する受光素子 1 には 3 原色のカラーフィルタのいずれかが配置され、R , G または B の入射光強度が電気信号に変換され信号が出力される。この F D A 型画素 2 1 が二次元マトリクス状に構成され、これに周辺回路が接続されてカラー固体撮像装置が構成される。

#### [0058]

なお、読み出しトランジスタ7、蓄積容量8、フィードバック容量9、書き込みトランジスタ10、蓄積ノード11、選択トランジスタ12及び電極ノード14は、異なる露光時間ごとに受光素子1で発生した複数の光信号電荷に応じた信号電圧を合成する合成部を構成する。

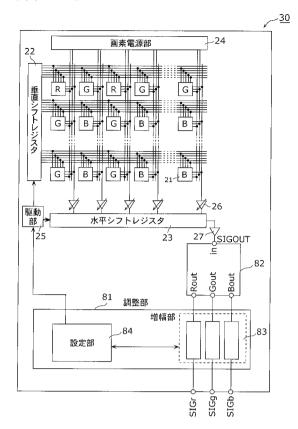

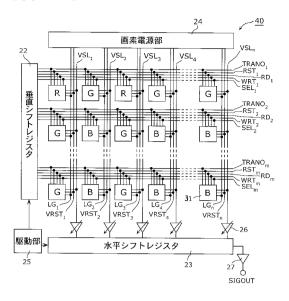

### [0059]

図 2 は、本発明の実施の形態 1 に係る m 行 n 列の画素アレイを有するカラー固体撮像装置の構成図である。同図におけるカラー固体撮像装置 2 0 は、m×n 個の F D A 型画素 2 1 と、垂直シフトレジスタ 2 2 と、水平シフトレジスタ 2 3 と、画素電源部 2 4 と、駆動部 2 5 と、カラムアンプ 2 6 と、出力アンプ 2 7 と、制御線 T R A N R y、 T R A N G y、 T R A N B y、 R S T y、 R D y、 W R T y 及び S E L y(1 y m)と、配線 L G x 及び V R S T x と、垂直信号線 V S L x(1 x n)とを備える。

### [0060]

図2では、3原色に対応してFDA型画素21をR(赤)、G(緑)、B(青)と記載している。FDA型画素21のTRAN(R,G,B)端子には、R,G,Bの色毎に異なる制御線TRANRy、TRANGy、TRANByが接続され、RST、RD、WRT、SEL端子には色の区別なく共通の制御線RSTy、RDy、WRTy、SELyが接続される。TRANRy、TRANGy、TRANBy、RSTy、RDy、WRTy、SELyがおされる。TRANRy、TRANGy、TRANBy、RSTy、RDy、WRTy、SELyは水平方向に配置された制御線群であり、垂直シフトレジスタ22から制御パルスが印加される。なお、添字yは垂直アドレスを示す。

#### [0061]

一方、LGおよびVRST端子には、垂直方向に配置された配線LG×およびVRST×が接続され、画素電源部24からDC電圧V<sub>LG</sub>およびV<sub>RST</sub>が印加される。なお、添字×は水平アドレスを示す。

### [0062]

FDA型画素21の出力端子OUTには垂直信号線VSL×が接続され、その端部にはカラムアンプ26を介して水平シフトレジスタ23が接続される。水平シフトレジスタ23は、FDA型画素21の出力端子OUTから垂直信号線VSL×を介して伝達された信号を水平方向に転送し、出力アンプ27で増幅した後にチップ出力端子SIGOUTからシリアルに出力する。なお、垂直シフトレジスタ22および水平シフトレジスタ23は、駆動部25により制御されている。

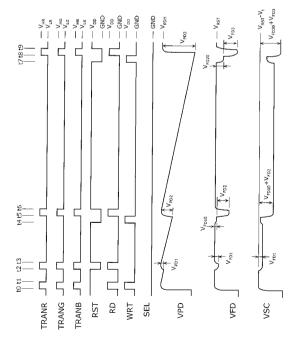

### [0063]

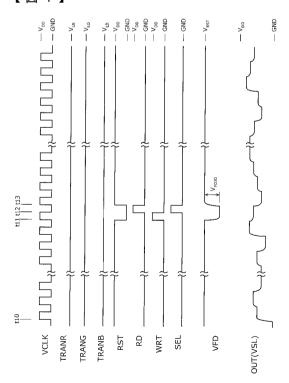

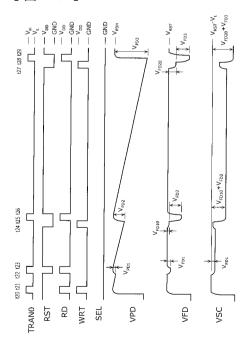

図3及び図4は、本発明の実施の形態1に係る固体撮像装置の有する制御線群に印加する制御パルスのタイミングチャートである。図3に記載されたタイミングチャートには、垂直シフトレジスタ22から制御線群TRANR、TRANG、TRANB、RST、RD、WRT及びSELに印加する制御パルス信号電圧と、受光素子1の負極ノード13の典型的なポテンシャルVPDと、FDJード3の典型的なポテンシャルVFDと、蓄積ノード11の典型的なポテンシャルVSCとの時間経過が示されている。また、図4に記載されたタイミングチャートには、駆動部25から垂直シフトレジスタ22へ印加される垂直転送クロックVCLKと、垂直シフトレジスタ22から制御線群TRANR、TRANG、TRANB、RST、RD、WRT及びSELに印加する制御パルス信号電圧と、FDJード3の典型的なポテンシャルVFDと、蓄積ノード11の典型的なポテンシャルVSCとの時間経過が示されている。

# [0064]

50

10

20

30

図3に示された期間は、3回の露光と2回の信号合成動作期間であり、図4に示された期間は、FDA型画素21から水平シフトレジスタ23への出力期間である。

#### [0065]

最初に、3回の露光期間における過剰電荷の排出を伴った電荷蓄積動作および受光素子 1へ電荷を残した読み出し動作について、図5及び図6を用いて説明する。

#### [0066]

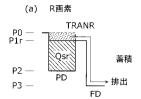

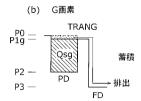

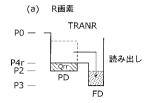

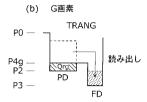

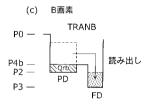

図5(a)、図5(b)及び図5(c)は、それぞれ、本発明のR画素、G画素及びB画素の有する受光素子の電荷蓄積時におけるポテンシャルを表す図である。また、図6(a)、図6(b)及び図6(c)は、それぞれ、本発明のR画素、G画素及びB画素の有する受光素子の電荷読み出し時におけるポテンシャルを表す図である。なお、図5及び図6に記載されたポテンシャル図において、縦軸方向は電子から見たエネルギー準位を基準としているので、上方にいくにつれポテンシャルが低いことを表している。

#### [0067]

図 3 に示された第一、第二及び第三の露光期間 t 1 ~ t 2 、 t 3 ~ t 4 、 t 6 ~ t 7 において、 T R A N R 、 T R A N G Q U T R A N B には、 それぞれ、 接地電位 G N D L U E 高い電位  $V_{LR}$ 、  $V_{LG}$  Q U  $U_{LB}$  が第 1 のゲート電圧として印加されており、 転送トランジスタ 2 は弱反転状態となっている。

### [0068]

このような状態における転送トランジスタ2のゲート下ポテンシャルは、図5に示されるように、R,G,B画素について、ゲート電極に接地電位を印加してオフ状態とした場合のポテンシャルP0に対して、それぞれ高い値であるP1r、P1g、P1bに設定されている。つまり、図5に示された状態では、転送トランジスタ2は不完全なオフ状態となっている。従って、露光期間中に受光素子1が蓄積可能な電荷量(図5のPDと表記した部分の斜線領域)は、R,G,B画素について、それぞれ、Qsr、Qsg、Qsbとなる。入射光強度が強く、受光素子1の蓄積可能な電荷量を超えて電荷が生成された場合、過剰な電荷は高いポテンシャル状態P3にあるFDノード3(図5のFDと表記した部分)へと排出される。露光期間中(t1~t2、t3~t4、t6~t7)、RSTには電源電圧VDDが印加されてリセットトランジスタ4はオン状態となっているので、過剰電荷は画素外のVRST線へとさらに排出される。これにより、全画素で飽和量を均一化する作用を有する。

### [0069]

しかし、一般的に、転送トランジスタ2のしきい値 $V_t$ 及び受光素子1の最高ポテンシャルP2は、製造時における受光素子1への不純物注入濃度や転送トランジスタ2のゲート絶縁膜厚などのばらつきにより、画素間でばらつくので、本動作を実行しても飽和電荷量Qs(R,G,B) を表す)にある一定のばらつき  $Qs(V_t)$  は残ることとなる。

# [0070]

$V_{t}$  ばらつきに起因した飽和電荷量ばらつき  $Q_{s}$  ( $V_{t}$ ) を抑制するため、3回の露光中に光電変換された電荷は、露光後の期間  $t_{2}$   $\sim$   $t_{3}$   $\sim$   $t_{5}$   $\sim$   $t_{6}$   $\sim$   $t_{8}$   $\sim$   $t_{9}$   $\sim$   $t_{1}$   $\sim$   $t_{2}$   $\sim$   $t_{1}$   $\sim$   $t_{1}$

10

20

30

40

#### [0071]

従って、転送トランジスタ2のゲート下ポテンシャル制御による過剰電荷を排出した蓄積で得られた飽和電荷量Qs± Qs(Vț)は、残留電荷量Qr± Qr(Vţ)を残して読み出すことにより、転送トランジスタ2のしきい値Vţ及び受光素子1の最高ポテンシャルP2のばらつきを取り除くことが可能である。

### [0072]

これにより、受光素子 1 や転送トランジスタ 2 によって規定される光信号電荷の蓄積飽和量が一部制限され、また電荷読み出し量の一部が残留電荷として読み残されることにより、各受光素子 1 や各転送トランジスタ 2 の構造ばらつきに影響されない任意の基準量に基づいた電荷読み出しが実現される。よって、画素間での光信号電荷量のばらつきを抑制することが可能となる。

#### [0073]

以下、受光素子 1 に蓄積される総電荷量から残留電荷量 Q r を引いた量を信号電荷量と呼ぶこととする。

### [0074]

このような電荷蓄積動作および読み出し動作を基本として、多重露光・信号合成動作を行う。この動作は画素アレイ全体で同時に実行され、いわゆるグローバルシャッター動作を行う。多重露光における第一、第二、第三の露光期間である t 1 ~ t 2 、 t 3 ~ t 4 、 t 6 ~ t 7 は順に長く設定されている。以下、画素内における電荷および電圧の様子を示した図 1 2 を参照しながら、図 3 のタイミングチャートを説明する。図 1 2 は、本発明の実施の形態 1 に係る固体撮像装置の画素回路における電荷及び電圧状態を表す図である。

#### [0075]

まず、期間( t 0 ~ t 1)において、垂直シフトレジスタ 2 2 は駆動部 2 5 の指示により、 T R A N R 、 T R A N G 及び T R A N B に、それぞれ、 H I G H 電位  $V_{HR}$ 、  $V_{HG}$ 及び  $V_{HB}$ (図 1 2 中では、 R , G , B 画素への印加電位をまとめて  $V_{H(R,G,B)}$  と表記)を印加する。また、 R S T 、 R D 、 W R T に電源電圧を印加して、転送トランジスタ 2 、 リセットトランジスタ 4 、 読み出しトランジスタ 7 及び書き込みトランジスタ 1 0 をオン状態にする。この動作により、 図 1 2 ( a )に示されるように、 受光素子 1 の負極ノード 1 3 のポテンシャル V P D は高レベルの  $V_{PDH}$ に、 F D ノード 3 のポテンシャル V F D は  $V_{RST}$ に、 オード 1 1 のポテンシャル V S C は  $V_{RST}$  ・  $V_{\tau}$  に リセットされる。ここで、 H I G H 電位  $V_{HR}$ 、  $V_{HG}$ 及び  $V_{HB}$ が印加された転送トランジスタのゲート下ポテンシャルは、 それぞれ、 図 6 に記載された P 4 r 、 P 4 g 、 P 4 b に相当する。また、  $V_{PDH}$  は受光素子 1 に 残留電荷 Q r が存在する状態のポテンシャル値であり、  $V_{rST}$  は画素電源部 2 4 から V R S T 線に給電される D C 電位であり、  $V_{\tau}$  は出力トランジスタ 5 のしきい値電圧である。

# [0076]

次に、期間( t 1 ~ t 2 )において、垂直シフトレジスタ22は駆動部25の指示により、 T R A N R 、 T R A N G 及び T R A N B に、それぞれ、 L O W 電位  $V_{LR}$ 、  $V_{LG}$ 及び  $V_{LB}$ (図12中では、 R , G , B 画素への印加電位をまとめて  $V_{L(R,G,B)}$  と表記)を印加して転送トランジスタ2を弱反転状態にする。また、 R D および W R T に接地電位を印加し、読み出しトランジスタ7及び書き込みトランジスタ10をオフ状態にする。この状態で、第一の露光(期間 t 1 ~ t 2 )を行い、受光素子1に第一の信号電荷 Q s i g 1 を蓄積する。電荷蓄積の結果、図12(b)に示されるように、受光素子1の負極ノード13のポテンシャル V P D は  $V_{PDH}$  から  $V_{PD1}$  だけ低下する。ここで、 L O W 電位  $V_{LR}$ 、  $V_{LG}$  及び  $V_{LB}$  が印加された転送トランジスタのゲート下ポテンシャルは、それぞれ、図5に記載された P 1 r 、 P 1 g 、 P 1 g に相当する。

### [0077]

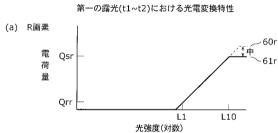

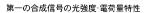

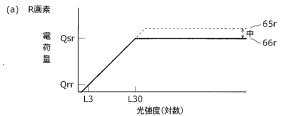

図7(a)、図7(b)及び図7(c)は、それぞれ、本発明の実施の形態1に係る固体撮像素子の有するR画素、G画素及びB画素の第一の露光期間における光電変換特性を表すグラフである。TRANR、TRANG、TRANBに接地電位を印加した場合には

10

20

30

40

20

30

40

50

、第一の露光時間においてR,G,B画素の受光素子1が示す光電変換特性は、それぞれ、図7(a)の光電変換特性60r、図7(b)の光電変換特性60g及び図7(c)の光電変換特性60bのようになる。しかし、第一の露光期間中に転送トランジスタ2を弱反転状態にしているため、蓄積電荷量は、それぞれ、図7(a)の光電変換特性61r、図7(b)の光電変換特性61g及び図7(c)の光電変換特性61bのように電荷量Qsr、Qsb、Qsgで飽和する。ここで、後述する調整部により、R,G,B画素間において飽和電荷量に達する照射光強度が等しくL10となるようにVLR、VLG、VLBを調整する。

# [0078]

次に、期間(t2~t3)において、垂直シフトレジスタ22は駆動部25の指示により、RSTに接地電位を印加してリセットトランジスタ4をオフにした状態で、TRANR、TRANG、TRANBにHIGH電位  $V_{HR}$ 、 $V_{HG}$ 、 $V_{HB}$ を印加し、転送トランジスタ2をオンにする。この動作により、R,G,B画素の受光素子1にそれぞれQrr、Qrg、Qrbだけの電荷を残して、受光素子1からFDノード3へと第一の信号電荷Qsig1を読み出す。このとき、図12(c)に示されるように、FDノード3のポテンシャルVFDは $V_{RST}$ - $V_{FD1}$ へと低下し、受光素子1の負極ノード13のポテンシャルVPDは $V_{PDH}$ - $V_{PD1}$ から $V_{PDH}$ へ復帰する。同時に、ソースフォロワは $V_{FD1}$ のポテンシャルVBDは $V_{RST}$ - $V_{FD1}$ - $V_{1}$ を出力する。このとき、RDには電源電位が印加されて読み出しトランジスタ7はオンとなっているので、蓄積ノード11のポテンシャルVSCは $V_{RST}$ - $V_{FD1}$ - $V_{1}$ となる。すなわち、蓄積ノード11には第一の信号電荷Qsig1に対応した第一の蓄積電荷Qsig10( $=V_{FD1}\times C_{2}$ 、ただし $C_{2}$ は蓄積容量8の容量値)が格納される。

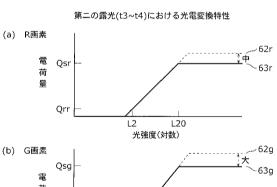

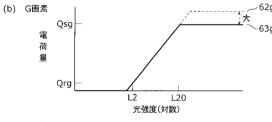

# [0079]

次に、期間( t 3 ~ t 4 )において、垂直シフトレジスタ 2 2 は駆動部 2 5 の指示により、 T R A N R 、 T R A N G 、 T R A N B に L O W 電位  $V_{LR}$ 、  $V_{LG}$ 、  $V_{LB}$ を印加して転送トランジスタ 2 を弱反転状態にする。また、 R D に接地電位を印加して読み出しトランジスタ 7 をオフ状態に、 R S T に電源電圧を印加してリセットトランジスタ 4 をオン状態にする。この状態で第二の露光(期間 t 3 ~ t 4 )を行い、 受光素子 1 に第二の信号電荷 Q s i g 2 を蓄積する。電荷蓄積の結果、 受光素子 1 の負極ノード 1 3 のポテンシャル V P D は  $V_{PDH}$  から  $V_{PD2}$  だけ低下する。

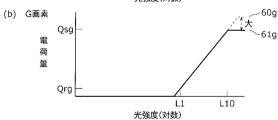

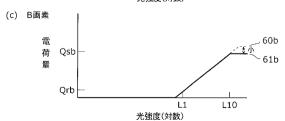

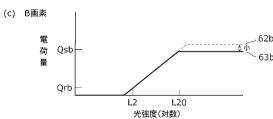

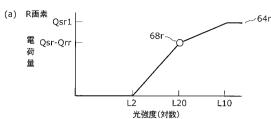

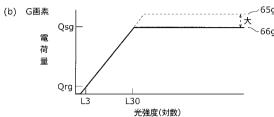

#### [0800]

図8(a)、図8(b)及び図8(c)は、それぞれ、本発明の実施の形態1に係る固体撮像装置の有するR画素、G画素及びB画素の第二の露光期間における光電変換特性を表すグラフである。TRANR、TRANG、TRANBに接地電位を印加した場合には、第二の露光時間においてR,G,B画素の受光素子1が示す光電変換特性は、それぞれ、図8(a)の62g及び図8(c)の62bのようになる。し、第二の露光期間中に転送トランジスタ2を弱反転状態にしているため、蓄積電荷量は、それぞれ、図8(a)の63r、図8(b)の63g及び図8(c)の63bのように電荷量Qsr、Qsb、Qsgで飽和する。ここで、後述する調整部により、R,G,B回素間において飽和電荷量に達する照射光強度が等しくL20となるようにVLR、VLBを調整する。さらに、第一の露光条件下で受光素子1が残留電荷量Qrr、Qrg、Qrbだけの電荷を生成する照射光強度L1とL20が一致するように調整することが、後述するR,G,Bのニーポイントがより一致するので望ましい。

# [0081]

次に、期間(t4~t5)において、垂直シフトレジスタ22は駆動部25の指示により、RSTに接地電位を印加してリセットトランジスタ4をオフに、WRTに電源電圧を印加して書き込みトランジスタ10をオンにする。このとき、図12(d)に示されるように、フィードバック容量9を介して、FDノード3と蓄積ノード11は結合し、第一の蓄積電荷の一部 ・QSig10がFDノード3へと移動する。蓄積容量8、フィードバック容量9、FDノード3が有する浮遊容量の容量値をそれぞれC2、C1、CFDとしたと

20

30

40

50

き、移動する電荷の割合 は合成容量  $C_1 \times C_2 / (C_1 + C_2)$  と浮遊容量  $C_{FD}$ の比で決まる。これらの容量値を適当に選ぶことにより、 は任意に設定できる。 FD ノード 3 へ電荷が移動した結果、そのポテンシャル VFD は  $V_{RST} - V_{FD10}$ へと低下する。

#### [0082]

次に、期間(t5~t6)において、垂直シフトレジスタ22は駆動部25の指示により、WRTに接地電位を印加して書き込みトランジスタ10をオフにし、TRANR、TRANG、TRANBに、それぞれ、HIGH電位V<sub>HR</sub>、V<sub>HG</sub>、V<sub>HB</sub>を印加して転送トランジスタ2をオンにする。この動作により、R,G,B画素の受光素子1に、それぞれ、Qrr、Qrg、Qrbだけの電荷を残して、受光素子1からFDノード3へと第二の信号電荷Qsig2が読み出される。このとき、図12(e)に示されるように、FDノード3には先に読み出された第一の蓄積電荷の一部・Qsig10がすでにあり、FDノード3にてこれらの電荷は合成される。

#### [0083]

### [0084]

次に、期間 t 6 ~ t 7 において、垂直シフトレジスタ 2 2 は駆動部 2 5 の指示により、 T R A N R 、 T R A N G 、 T R A N B に L O W電位  $V_{LR}$ 、  $V_{LG}$ 、  $V_{LB}$ を印加して転送トランジスタ 2 を弱反転状態にする。また、 R D に接地電位を印加して読み出しトランジスタ 7 をオフ状態にし、 R S T に電源電圧を印加してリセットトランジスタ 4 をオン状態にする。この状態で、第三の露光( t 6 ~ t 7 )を行い、 受光素子 1 に第三の信号電荷 Q s i g 3 を蓄積する。電荷蓄積の結果、 受光素子 1 の負極 J ード 1 3 のポテンシャル V P D は  $V_{PDH}$  から  $V_{PD3}$  だけ低下する。

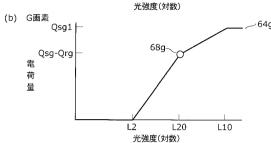

### [0085]

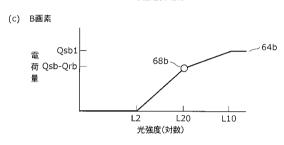

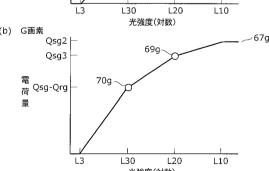

図10(a)、図10(b)及び図10(c)は、それぞれ、本発明の実施の形態1に係る固体撮像装置の有するR画素、G画素及びB画素の第三の露光期間における光電変換特性を表すグラフである。TRANR、TRANG、TRANBに接地電位を印加した場合には、第三の露光時間においてR,G,B画素の受光素子1が示す光電変換特性は、それぞれ、図10(a)の65g及び図10(c)の65bのようになる。しかし、第三の露光期間中に転送トランジスタ2を弱反転状態にしているため、蓄積電荷量は、それぞれ、図10(a)の66F、図10(b)の66g及び図10(c)の66bのように電荷量Qsr、Qsb、Qsgで飽和する。ここで、後述するおにより、R,G,B画素間において飽和電荷量に達する照射光強度が等しくL30と部ようにVLR、VLG、VLBを調整する。さらに、第二の露光条件下で受光素子1が残留電荷Qrr、Qrg、Qrbだけの電荷を生成する照射光強度L2とL30が一致するように調整することが、後述するR,G,Bのニーポイントがより一致するので望ましい。

### [0086]

次に、期間(t7~t8)において、垂直シフトレジスタ22は駆動部25の指示によ

20

30

40

50

り、RSTに接地電位を印加してリセットトランジスタ 4 をオフに、WRTに電源電圧を印加して書き込みトランジスタ 1 0 をオンにする。このとき、図 1 2 ( f ) に示されるように、フィードバック容量 9 を介して、FDノード 3 と蓄積ノード 1 1 は結合し、第二の蓄積電荷の一部 ・QSig20がFDノード 3 へと移動する。移動する電荷の割合 は、 $C_1$ 、 $C_2$ 、 $C_{FD}$ の比により任意である。FDノード 3 へ電荷が移動した結果、そのポテンシャル VFDは  $V_{RST}$  -  $V_{FD20}$ へと低下する。

[0087]

次に、期間(t8~t9)において、垂直シフトレジスタ22は駆動部25の指示により、WRTに接地電位を印加して書き込みトランジスタ10をオフにし、TRANR、TRANG、TRANBにHIGH電位V<sub>HR</sub>、V<sub>HG</sub>、V<sub>HB</sub>を印加して転送トランジスタ2をオンにする。この動作により、R,G,B画素の受光素子1にそれぞれQrr、Qrg、Qrbだけの電荷を残して、受光素子1からFDノード3へと第三の信号電荷Qsig3を読み出す。このとき、図12(g)に示されるように、FDノード3には先に読み出された第一の合成電荷の一部である ・Qsig20がすでに存在し、FDノード3にてこれらの電荷は合成される。

[0088]

図 1 1 ( a )、図 1 1 ( b )及び図 1 1 ( c )は、それぞれ、本発明の実施の形態 1 に 係る固体撮像素子の有するR画素、G画素及びB画素の第二合成信号の光電変換特性を表 すグラフである。第二の合成電荷量はQsig3+ ・Qsig20となるので、R画素 、G画素及びB画素の光強度-電荷量特性は、それぞれ、図11(a)、図11(b)及 び図11(c)に示されるような形状となる。これらの図より、R,G,B画素の特性6 7 r 、 6 7 g 、 6 7 b は、それぞれ、 2 つの照射光強度 L 2 0 および L 3 0 でニーポイン ト 6 9 r 、 6 9 g 、 6 9 b 及び 7 0 r 、 7 0 g 、 7 0 b を有する。感度は、照射光強度が L10~L20の範囲では ・ 倍だけ低下し、L20~L30の範囲では 倍だけ低下 する。ここで、R,G,Bの特性を比較すると、ニーポイントの照射光強度は一致してお り、ニーポイントを境界とする3つの照射光強度領域(L10以下、L10~L20、L 2 0 ~ L 3 0 ) における R , G , B の感度(傾き)の比は同じである。このとき、図 1 2 (g)に示されるように、第三の信号電荷によるポテンシャルVFDの低下はV<sub>೯D3</sub>であ り、 受 光 素 子 1 の 負 極 ノ ー ド 1 3 の ポ テ ン シ ャ ル V P D は V <sub>PDH</sub> ・ V <sub>PD3</sub> か ら V <sub>PDH</sub> へ 復 帰 する。同時に、ソースフォロワはVFDよりもV,だけ低い電位V<sub>RST</sub> - V<sub>FD20</sub> - V<sub>FD3</sub> -V,を出力する。このとき、RDには電源電位が印加されて読み出しトランジスタ7はオ ンとなっているので、蓄積ノード11のポテンシャルVSCはV<sub>RST</sub> - V<sub>FD20</sub> - V<sub>FD3</sub> - V ,となる。すなわち、蓄積ノード11には第二の合成電荷に対応した第三の蓄積電荷Qs ig30(=( $V_{FD20} + V_{FD3}$ )× $C_2$ )が格納される。

[0089]

以上の動作により、本発明の実施の形態 1 に係る固体撮像装置は、多重露光における合成信号の光強度 - 電荷量特性におけるニーポイントとなる入射光強度を、全色で共通とすることが可能となる。このような光強度 - 電荷量特性とすることで、ホワイトバランス調整を容易にすることが可能となる。すなわち、全入射光強度領域にわたって同一の補正係数でホワイトバランス調整することが可能となる。

[0090]

固体撮像素子内での多重露光・信号合成動作は、以上の動作により完了する。次に、図4に記載されたタイミングチャートに従って、FDA型画素21から水平シフトレジスタ23への出力動作を説明する。

[0091]

出力動作は時刻 t 1 0 から開始され、駆動部 2 5 から垂直シフトレジスタ 2 2 へ印加される垂直転送クロック V C L K に同期して行毎に順次行われる。

[0092]

所定の行においてVCLKがHIGH期間(t11~t12)に、垂直シフトレジスタ 22は駆動部25の指示により、RSTに接地電位を印加してリセットトランジスタ4を オフに、WRTに電源電圧を印加して書き込みトランジスタ10をオンにする。このとき、図12(h)に示されるように、フィードバック容量9を介して、FDノード3と蓄積ノード11は結合し、第三の蓄積電荷の一部 ・Qsig30がFDノード3へと移動する。移動する電荷の割合 は、 $C_1$ 、 $C_2$ 、 $C_FD$ の比により任意である。FDノード3へ電荷が移動した結果、そのポテンシャルVFDは $V_{RST}$ - $V_{FD30}$ へと低下する。

### [0093]

次に、所定の行においてVCLKがロー期間(t12~t13)に、垂直シフトレジスタ22は駆動部25の指示により、WRTに接地電位を印加して書き込みトランジスタ10をオフにし、RDおよびSELに電源電圧を印加して読み出しトランジスタ7および選択トランジスタ12をオンにする。この動作により、図12(i)に示されるように、ソースフォロワから出力端子OUTを通して垂直信号線VSLへ、V<sub>RST</sub>-V<sub>FD30</sub> V、なる信号線圧が出力される。垂直信号線VSLへと出力された信号はカラムアンプ26で増幅された後、水平シフトレジスタ23から列順次に出力アンプ27を通してチップ出力端子SIGOUTへと出力される。

#### [0094]

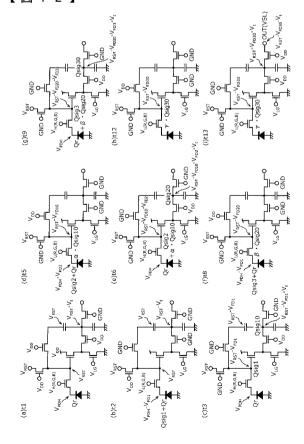

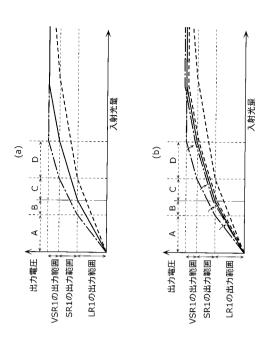

図13は、本発明の実施の形態1に係る、調整部を備えたカラー固体撮像装置の構成図である。同図に記載されたカラー固体撮像装置30は、図2に記載されたカラー固体撮像装置20に対し、調整部81と、マルチプレクサ82とが付加されている。また調整部81は、プログラマブル増幅器である増幅部83と、設定部84とを備える。

### [0095]

カラー固体撮像装置30のSIGOUTにはマルチプレクサ82が接続され、シリアル出力されたR,G,B信号をそれぞれRout、Gout、Bout端子に振り分けて出力する。これら3つの出力端子には、補正部である増幅部83が接続されている。この増幅部83により、R,G,B信号を任意の割合(ゲイン)で増幅することで色調整を行う

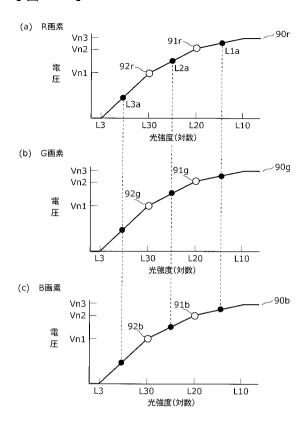

# [0096]

図14(a)、図14(b)及び図14(c)は、それぞれ、ゲイン調整されたR,G,B信号の光電変換特性を表すグラフである。例えば、図14に示されるように、R,G,Bの入射光強度・合成信号電圧特性である光電変換特性90r、90g及び90bの形状を一致させて出力端子SIGr、SIGg、SIGbに出力することができる。すなわち、ニーポイント91r、91g、91bおよび92r、92g、92bの照射光強度と電圧値を、それぞれ、(L30,Vn1)および(L20,Vn2)と一致させる。

#### [0097]

上記一致は、図11に記載された、ニーポイントにおける入射光強度の一致した入射光強度・合成信号電圧特性を有するR,G,B信号がSIGOUTから出力されることにより、全入射光強度領域にわたって同一の補正係数を用いて実現される。

#### [0098]

これにより、3つの光強度範囲L3~L30、L30~L20~L10における感度を一致させ、飽和電圧値をVn3で一致させることが可能である。ゲインは被写体の色温度によって変更するパラメータであり、本実施の形態によれば広い照射光強度範囲(L3~L10)にわたって破綻することなく色調整が可能である。

#### [0099]

また、設定部 8 4 は、 F D A 型画素 2 1 の有する転送トランジスタ 2 のゲートに印加する H I G H 電位  $V_{HR}$ 、  $V_{HG}$ 、  $V_{HB}$ 及び L O W 電位  $V_{LR}$ 、  $V_{LG}$ 、  $V_{LB}$ を調整し、調整された H I G H 電位及び L O W 電位情報を駆動部 2 5 に与える。以下、設定部 8 4 における、転送トランジスタ 2 のゲート電圧調整方法について説明する。

#### [0100]

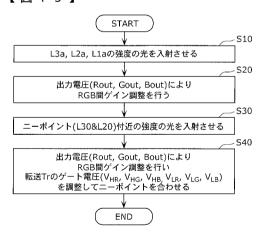

図 1 5 は、本発明の実施の形態 1 に係る固体撮像装置の有する転送トランジスタのゲート電圧を調整する動作フローチャートである。

# [0101]

50

10

20

30

20

30

40

50

まず、設定部84は、各露光期間において出力電圧が飽和しない入射光を与えながら(S10)、駆動部25に対し、出力電圧Rout、Gout及びBoutを測定させる。この間、増幅部83に対し、R,G,B間のゲイン調整、つまりホワイトバランス調整を行わせる(S20)。ここで、出力電圧が飽和しない入射光強度とは、具体的には、図14に記載されたL1a、L2a及びL3aである。

[0102]

次に、設定部84は、R,G,Bの入射光強度-合成信号電圧特性におけるニーポイント付近での入射光を与えながら(S30)、駆動部25に対し、出力電圧Rout,Gout及びBoutを測定させる。この間、プログラマブル増幅器である増幅部83に対しニーポイント付近でのR,G,B間のゲイン調整を行わせる。同時に、駆動部25に対し、HIGH電位V<sub>HR</sub>、V<sub>HB</sub>及びLOW電位V<sub>LR</sub>、V<sub>LG</sub>、V<sub>LB</sub>値を指示し、それによる出力電圧Rout,Gout及びBoutの変化をみて上記ニーポイントを調整する(S40)。ここで、入射光強度-合成信号電圧特性におけるニーポイントとは、具体的には、図14に記載された91r、91g、91b、92r、92g及び92bである。

[0103]

以上の動作により、多重露光における合成信号の光強度 - 合成信号電圧特性におけるニーポイントとなる入射光強度を、全色で共通とすることが可能となる。このような光強度 - 電荷量特性とすることで、ホワイトバランス調整を容易にすることが可能となる。すなわち、全入射光強度領域にわたって同一の補正係数でホワイトバランス調整することが可能となる。

[0104]

なお、上記転送トランジスタ2のゲート電圧の調整は、本固体撮像装置を含む製品の出荷時に調整されていてもよい。さらに、上記製品出荷後、定期的に調整されてもよい。

[ 0 1 0 5 ]

また、設定部84は、駆動部25に含まれていてもよい。

[0106]

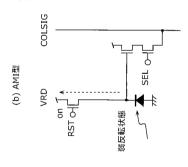

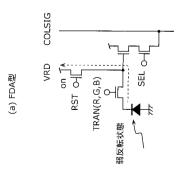

また、本実施の形態では、画素部はFDA型回路構成をとったが、AMI型回路構成をとってもよい。

[0107]

図16(a)は、FDA型回路で構成された画素部の回路構成図を、また、図16(b)は、AMI型回路で構成された画素部の回路構成図である。図16(a)に示されたFDA型回路は、すでに本実施の形態で説明したように、受光素子から光信号電荷を読み出す転送トランジスタを備えたものである。この画素の光信号電荷の飽和量は転送トランジスタのゲート端子(TRAN)のゲート下ポテンシャルの高さによって決定される。よって、蓄積できる光信号電荷量を上記ゲート下ポテンシャルの開閉幅を制御することにより、OFF状態におけるゲート電圧と導通状態におけるゲート電圧を同色のカラーフィルタを有する画素部ごとに設定することによって、飽和を均一化できる。

[0108]

一方、図16(b)に示されたAMI型回路は、上記転送トランジスタなるものはなく、受光素子で発生した光信号電荷を出力する出力ノードにリセット電圧を印加するリセットトランジスタが配置されている。この画素の光信号電荷の飽和量はリセットトランジスタが配置されている。この画素の光信号電荷の飽和量はリセットトランジスタのゲート下ポテンシャルの高さによって決定される。一般の「ロセットトランジスタにおいても、画素ごとにリセットトランジスタのが「ロートではいる」となるようにの「ロートではいる」とにより飽和量を制御する。となるように「ロートではいる」とによりによりでで変換された光信号電荷の一下ポテンシャルが受光素子ポテンシャルよりも高くなるようにゲート電圧を印加する。これにより、いわゆるAMI型画を光素子においても、蓄積できる光信号電荷量はリセットトランジスタのゲート下ポテンジスタのゲート下ポテンジスタのゲート下ポテンジスタのゲート下ポテンジスタのゲート下ポテンジスタのゲート下ポテンジスタのゲート下ポテンジスタのゲート下ポテンジスタのゲート下ポテ

20

30

40

50

ンシャルの開閉幅で決まることになり、 OFF 状態におけるゲート電圧と導通状態におけるゲート電圧を同色のカラーフィルタを有する画素部ごとに設定することによって、飽和を均一化できる。

### [0109]

(実施の形態2)

以下、本発明の実施の形態 2 に係る固体撮像装置について、図面を参照しながら説明する。

# [0110]

図17は、本発明の実施の形態2における固体撮像装置の有するFDA型画素の回路図である。同図に記載されたFDA型画素31は、画素部であり、受光素子1と、転送トランジスタ2と、FDノード3と、リセットトランジスタ4と、出力トランジスタ5と、負荷トランジスタ6と、読み出しトランジスタ7と、蓄積容量8と、フィードバック容量9と、書き込みトランジスタ10と、蓄積ノード11と、選択トランジスタ12と、負極ノード13、電極ノード14とを備える。図17に記載されたFDA型画素31は、図1に記載されたFDA型画素31は、図1に記載されたFDA型画素31と比較して回路構成は同じであるが、転送トランジスタ2のゲート端子に印加されるゲート電圧が、全画素にわたって共通している点が実施の形態1と異なる。

### [0111]

以下、実施の形態1と同じ点は説明を省略し、異なる点のみ説明する。

#### [0112]

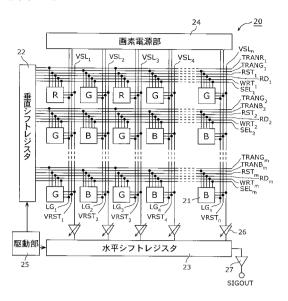

図18は、本発明の実施の形態2に係るm行n列の画素アレイを有するカラー固体撮像装置の構成図である。同図におけるカラー固体撮像装置40は、m×n個のFDA型画素31と、垂直シフトレジスタ22と、水平シフトレジスタ23と、画素電源部24と、駆動部25と、カラムアンプ26と、出力アンプ27と、制御線TRAN0y、RSTy、RDy、WRTy及びSELy(1 y m)と、配線LGx及びVRSTxと、垂直信号線VSLx(1 x n)とを備える。

# [ 0 1 1 3 ]

図18では、3原色に対応してFDA型画素31をR(赤)、G(緑)、B(青)と記載している。FDA型画素31のTRAN0端子には、R,G,B画素に共通して制御線TRAN0yが接続され、RST、RD、WRT、SEL端子には色の区別なく共通の制御線RSTy、RDy、WRTy、SELyが接続される。TRAN0y、RSTy、RDy、WRTy、SELyは水平方向に配置された制御線群であり、垂直シフトレジスタ22から制御パルスが印加される。

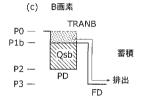

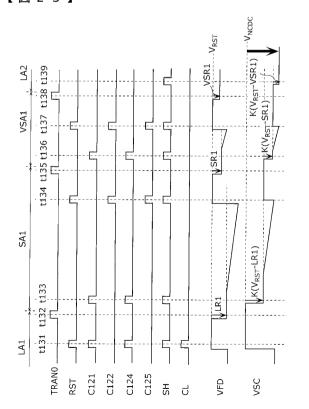

### [0114]

図19は、本発明の実施の形態2に係る固体撮像装置の有する制御線群に印加する制御パルスのタイミングチャートである。図19に記載されたタイミングチャートには、垂直シフトレジスタ22から制御線群TRANO、RST、RD、WRT及びSELに印加する制御パルス信号電圧と、受光素子1の負極ノード13の典型的なポテンシャルVPDと、FDノード3の典型的なポテンシャルVFDと、蓄積ノード11の典型的なポテンシャルVSCとの時間経過が示されている。図19に記載されたタイミングチャートは、実施の形態1に係る図3に記載されたタイミングチャートと比較して、色毎の区別なく、共通した制御パルスが、転送トランジスタ2のゲートに印加されている点のみが異なる。以下、実施の形態1と異なる点のみ説明する。

# [0115]

まず、期間(t20~t21)において、垂直シフトレジスタ22は駆動部25の指示により、TRAN0にHIGH電位V<sub>H</sub>を印加する。また、RST、RD、WRTに電源電圧を印加して、転送トランジスタ2、リセットトランジスタ4、読み出しトランジスタ7及び書き込みトランジスタ10をオン状態にする。このHIGH電位V<sub>H</sub>は、転送トランジスタのゲート下ポテンシャルが受光素子1の最高ポテンシャルレベルよりも低くなるような値に設定されている。つまり、転送トランジスタ2は不完全なオン状態となってい

る。

# [0116]

次に、期間( t 2 1 ~ t 2 2 )において、垂直シフトレジスタ 2 2 は駆動部 2 5 の指示により、 T R A N 0 に L O W電位  $V_L$ を印加して転送トランジスタ 2 を弱反転状態にする。また、 R D および W R T に接地電位を印加し、読み出しトランジスタ 7 及び書き込みトランジスタ 1 0 をオフ状態にする。この L O W電位  $V_L$ は、接地電位 G N D よりも高い電位に設定されている。つまり、転送トランジスタ 2 は弱反転状態であり不完全がオフ状態となっている。

### [0117]

次に、期間( t 2 2 ~ t 2 3 ) において、垂直シフトレジスタ 2 2 は駆動部 2 5 の指示により、 R S T に接地電位を印加してリセットトランジスタ 4 をオフにした状態で、 T R A N 0 に H I G H 電位  $V_H$ を印加し、転送トランジスタ 2 をオンにする。

#### [0118]

次に、期間(t23~t24)において、垂直シフトレジスタ22は駆動部25の指示により、TRAN0にLOW電位VLを印加して転送トランジスタ2を弱反転状態にする。また、RDに接地電位を印加して読み出しトランジスタ7をオフ状態に、RSTに電源電圧を印加してリセットトランジスタ4をオン状態にする。

### [0119]

次に、期間(t24~t25)において、垂直シフトレジスタ22は駆動部25の指示により、RSTに接地電位を印加してリセットトランジスタ4をオフに、WRTに電源電圧を印加して書き込みトランジスタ10をオンにする。

#### [ 0 1 2 0 ]

次に、期間( t 2 5 ~ t 2 6 ) において、垂直シフトレジスタ 2 2 は駆動部 2 5 の指示により、WRTに接地電位を印加して書き込みトランジスタ 1 0 をオフにし、TRAN 0 にHIGH電位  $V_H$ を印加して転送トランジスタ 2 をオンにする。

### [0121]

次に、期間(t26~t27)において、垂直シフトレジスタ22は駆動部25の指示により、TRAN0にLOW電位V」を印加して転送トランジスタ2を弱反転状態にする。また、RDに接地電位を印加して読み出しトランジスタ7をオフ状態にし、RSTに電源電圧を印加してリセットトランジスタ4をオン状態にする。

#### [0122]

次に、期間(t27~t28)において、垂直シフトレジスタ22は駆動部25の指示により、RSTに接地電位を印加してリセットトランジスタ4をオフに、WRTに電源電圧を印加して書き込みトランジスタ10をオンにする。

# [0123]

次に、期間( t 2 8 ~ t 2 9 ) において、垂直シフトレジスタ 2 2 は駆動部 2 5 の指示により、WRTに接地電位を印加して書き込みトランジスタ 1 0 をオフにし、TRAN 0 にHIGH電位  $V_H$ を印加して転送トランジスタ 2 をオンにする。

# [0124]

固体撮像装置内での多重露光・信号合成動作は、以上の動作により完了する。

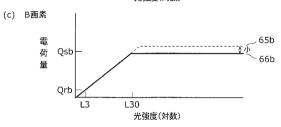

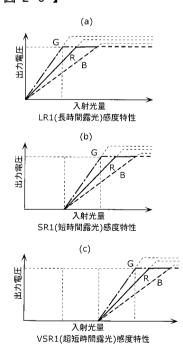

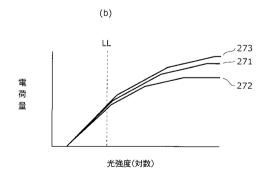

図20(a)、図20(b)及び図20(c)は、それぞれ、本発明の実施の形態2に係る固体撮像装置の有する画素部の長時間露光、短時間露光及び超短時間露光における光電変換特性を表すグラフである。横軸は、入射光量が対数表示されており、縦軸は各露光期間において転送トランジスタ2から転送された光信号電荷に対応する出力電圧である。図19に記載されたタイミングチャートと比較すると、期間(t21~t22)における光電変換特性は、図20(c)に記載された光電変換特性に対応する。また、期間(t23~t24)における光電変換特性は、図20(b)に記載された光電変換特性に対応する。また、期間(t26~t27)における光電変換特性は、図20(a)に記載された光電変換特性に対応する。

# [0125]

10

20

30

転送トランジスタ2のゲート電圧が完全オフ状態及び完全オン状態で電荷蓄積及び電荷 読み出しがなされた場合には、少なくともR画素、G画素及びB画素の光電変換特性にお ける飽和出力電圧は一致しない。これに対し、全画素の転送トランジスタ2のゲート電圧 が図19に記載されたTRAN0の制御信号のように、不完全オフ状態及び不完全オン状 態に設定された場合には、図20に示されたように、R画素、G画素及びB画素の飽和出 力電圧が一致していることが解る。これらを単純に合成すると、図21(a)の光電変換 特性のように、当該特性にあらわれるニーポイントも同じ出力電圧で出現する。

### [0126]

#### [ 0 1 2 7 ]

(実施の形態3)

以下、本発明の実施の形態3に係る固体撮像装置について図面を参照しながら詳細に説明する。

[0128]

図22は、本発明の実施の形態3に係る固体撮像装置の回路構成図である。

[0129]

同図における固体撮像装置は、FDA型画素50内に、受光素子1と、転送トランジスタ2と、FDJード3と、リセットトランジスタ4と、出力トランジスタ5と、負荷トランジスタ6と、画素行選択トランジスタ41と、ソースフォロワ出力点47とを備え、列信号線毎に、読み出しトランジスタ42と、容量43、44及び126と、スイッチングトランジスタ45、121、122、124及び125と、バッファ回路123とを備える。

[0130]

図22に記載された回路構成は、実施の形態2の図17に記載された回路構成と比較して、受光素子1で発生した光信号電荷を合成する合成部が、FDA型画素内になく、列信号線毎に設けられている点が異なる。以下、実施の形態2と同じ点は説明を省略し、異なる点のみ説明する。

[0131]

転送トランジスタ 2 は、実施の形態 1 及び 2 で説明したように、電荷蓄積時には弱反転状態となるように O F F 状態におけるゲート電圧が印加される。また、電荷読み出し時には導通状態におけるゲート下ポテンシャルが受光素子ポテンシャルよりも高くなるようにゲート電圧が印加される。これにより、全画素で飽和電荷量を均一化する動作を行う。

[0132]

リセットトランジスタ 4 は、リセット部を構成し、 F D ノード 3 の電圧をリセットする機能を有する。

[0133]

10

20

30

20

30

40

50

読み出しトランジスタ42、スイッチングトランジスタ45、容量43及び44は、差分回路部を構成し、FDノード3の信号電圧とリセット電圧との差分電圧と、電圧設定部により設定された基準電圧とを合成する機能を有する。なお、基準電圧の初期値はV<sub>NCDC</sub>である。

[0134]

スイッチングトランジスタ121、124、バッファ回路123、及び容量126は、記憶部を構成し、差分回路部で合成された電圧を記憶する機能を有する。

[0135]

スイッチングトランジスタ122、125、及びバッファ回路123は、電圧設定部を構成し、記憶部で保持された電圧を基準電圧として差分回路部に設定する機能を有する。 【0136】

出力トランジスタ5及び負荷トランジスタ6は、回路部を構成し、FDノード3の電圧を読み出す機能を有する。

[0137]

本実施の形態においては、差分回路部、記憶部及び電圧設定部が機能分担して1つの合成部を構成しており、光信号電荷に応じた電圧を合成する機能を有する。なお、この合成部は、画素ごとには配置されておらず、列信号線毎に設けられている。

[0138]

本回路構成の機能について、各回路素子の駆動動作を例示して説明する。

[0139]

図23は、本発明の実施の形態3における固体撮像装置の動作タイミングチャートである。図23に記載されたタイミングチャートには、垂直シフトレジスタ22から制御線群TRAN0、RST、C121、C122、C124、C125、SH及びCLに印加する制御パルス信号電圧と、FDノード3の典型的なポテンシャルVFDと、出力OUTの典型的なポテンシャルVSCとの時間経過が示されている。また、実施の形態1及び2では、露光期間を、超短時間露光、短時間露光、長時間露光の順で多重露光動作を実施したが、本実施の形態では、露光期間を、長時間露光、短時間露光、超短時間露光の順で重露光動作を実施している。

[0140]

最初に、時刻 t 1 3 1 では、駆動部 2 5 は、R S T、C 1 2 1、C 1 2 4、S H、及び C L の電圧レベルを H I G H にし、リセットトランジスタ 4、スイッチングトランジスタ 4 5、1 2 1 及び 1 2 4、読み出しトランジスタ 4 2 を導通させる。電圧 V<sub>RST</sub>が F D ノード 3 に与えられ、電圧 V<sub>NCDC</sub>が出力 O U T に与えられる。また、 V<sub>NCDC</sub>は、スイッチングトランジスタ 1 2 1 及び 1 2 4、及びバッファ回路 1 2 3 を介して容量 1 2 6 に保存される。

[0141]

次に、時刻 t 1 3 2 では、駆動部 2 5 は、T R A N 0 の電圧レベルをH I G H にし、転送トランジスタ 2 を介して期間 L A 1 において受光素子 1 に発生した電荷が F D ノード 3 に転送される。発生した電荷は負の特性のため F D ノード 3 は V <sub>RST</sub> より電位が下がる。この電圧降下分を"L R 1"とすると F D ノード 3 の電圧は(V <sub>RST</sub> - L R 1)である。

[0142]

次に、時刻 t 1 3 3  $\overline{c}$  は、駆動部 2 5 は、 C 1 2 1、 C 1 2 4、 S H の電圧レベルを H I G H にし、スイッチングトランジスタ 1 2 1、 1 2 4、 及び読み出しトランジスタ 4 2 を導通させる。この時、出力 O U T において、  $V_{NCDC}$  からの電圧変化は  $\{k \times (-LR1)\}$  であり、これが期間 L A 1 に受光素子 1 が受光した信号出力である。ここで、 k は、  $Y_{NCDC}$  -  $\{k \times (V_{RST} - LR1)\}$  ] が容量 1 2 6 に保持される。

[0143]

次に、時刻 t 1 3 4 では、駆動部 2 5 は、R S T 、 C 1 2 2 、 C 1 2 5 、 S H の電圧レベルを H I G H に し、リセットトランジスタ 4 、スイッチングトランジスタ 1 2 2 及び 1

25、及び読み出しトランジスタ42を導通させる。FDノード3では、再び、リセット電圧であるV<sub>RST</sub>に設定される。しかし、出力OUTは容量126で保持されていた電圧値[V<sub>NCDC</sub>・{k×(V<sub>RST</sub>-LR1)}]が設定される。即ち、初期(時刻t131)では、出力OUTはV<sub>NCDC</sub>が設定されたが、時刻t134では期間LA1の信号出力を含んだ電圧値が設定されることで各期間の信号出力の加算が実現されている。

### [0144]

上述した時刻 t 1 3 2 から時刻 1 3 4 までの動作と同様に、時刻 1 3 5 から時刻 t 1 3 7 までの動作が実行される。その後、時刻 t 1 3 8 において T R A N 0 の電圧レベルを H I G H とし転送トランジスタ 2 が導通すれば、 F D ノード 3 には、連続して期間 V S A 1 において受光素子 1 で発生した電荷が転送される。

[0145]

最後に、時点 t 1 3 9 では、 S H の電圧レベルを H I G H とし、読み出しトランジスタ4 2 を導通させる。これにより、出力 O U T には V <sub>NCDC</sub>に対して期間 L A 1 、 S A 1 、 V S A 1 の合成信号の変化分が出力される。

[0146]

なお、本実施の形態 3 における固体撮像素子の回路構成では、期間 L A 1 、 S A 1 、 V S A 1 で発生したそれぞれの信号電圧を合成するため合成部の核となる差分回路部が、画素毎に設けられていない。

[0147]

本実施例では、差分回路部、記憶部、及び電圧設定部が、画素毎ではなく列信号線毎に設けられているので、回路素子数が削減され、素子の省面積化が実現される。

[0148]

ここで、列信号線毎に電荷合成部が設けられた場合の出力電圧の読み出し動作について、説明する。

[0149]

例えば、所望のダイナミックレンジを得る場合のケースとして、期間LA1、SA1、VSA1をそれぞれ30msec、300μsec、3μsecとする。この条件に対し、列信号線が1行を読み取るのに与えられる時間Hは、60μsecである。ここで、期間LA1として最長露光時間である30msecが先頭で実行されることにより、期間LA1による露光動作は、他の複数の画素行の出力動作中になされることが可能となり、上記読み取り時間Hには影響しない。また、最短露光時間である3μsecについては、上記読み取り時間Hに対し、無視できる値であるため、上記読み取り時間Hには影響しない

[0150]

しかし、露光時間300μsecである期間SA1に関しては、期間LA1の最後に期間VSA1に相当する信号電圧が差分回路部に読み込まれて以来、差分回路部はにについまっては、その間に画素行の選択が保持されず、60μsecで読み出し行が変更されてしまでは、その間に画素行の選択が保持されず、60μsecで読み出し行が変更されてしまいて、容量126が1素子ではなく、5素子が並列接続され、各々のちつのおけったのないで、容量126が1素子ではなく、5素子ではかられ、各のののカーをであるののカーをでである。そして、がが立め、ののカーをでである。その方ののカーをであるののカーをである。その方ののカーをである。その前にして3行目のは、1行目の画素が記憶され、同様にして3行目、4行目、5行目が記憶されるので、1行目の画素が読み込まれて以来合計300μsecが経過し、1行目の画素の信号電圧が合成され読み出されるので、その直後に1つ目のキャパシタに6行目の画素の信号電圧の読み込みが開始される。

[0151]

このようにして、スムーズなローリングシャッタ動作が実現される。

[0152]

10

20

30

40

20

30

40

50

以上のように、本実施の形態3における固体撮像装置によれば、受光素子で発生した光信号電荷を蓄積するFDノードと、FDノードの電圧をリセットするリセット部と、FDノードの信号電圧とリセット電圧との差分電圧を加算する差分回路部と、差分回路部の電圧を記憶する記憶部と、当該記憶部の電圧を差分回路部に設定する電圧設定部とを素子内に備えることにより、例えば、複数回の露光時間により発生したそれぞれの光信号電荷に対応した電圧を素子内で短時間に加算することができるため、外部回路を必要とせずにダイナミックレンジの拡張が達成される。

# [0153]

また、本実施の形態の固体撮像装置は、素子外部に記憶部、画像合成部を必要としないため、ダイナミックレンジの仕様および設計変更が生じた場合においても、外部システムに大きな影響を及ぼすことなく、固体撮像素子であるチップのみが設計変更されることで対応できるという大きな効果を奏する。

#### [0154]

固体撮像素子内で実行された多重露光・信号合成動作は、以上の動作により完了する。そして、得られた各画素の合成信号は、実施の形態2と同様にして、図21(b)に記載された光電変換特性のゲイン調整によりホワイトバランスを容易に実行することができる

### [0155]

この結果、強い光を受光した状態でも合成画像に輝度ばらつきが見えなくなり、カラー 化信号処理のためにホワイトバランスを取る場合、色ごとの補正も容易になるので、偽色 が抑止された綺麗なカラー信号を得ることができる。

#### [0.156]

なお、本発明に係る固体撮像装置は、上記実施の形態に限定されるものではない。実施の形態 1~3における任意の構成要素を組み合わせて実現される別の実施形態や、実施の形態 1~3に対して本発明の主旨を逸脱しない範囲で当業者が思いつく各種変形を施して得られる変形例や、本発明に係る固体撮像装置を内蔵した各種機器も本発明に含まれる。

# [0157]

例えば、実施の形態1及び2に係る固体撮像装置の画素内の回路においても、実施の形態3と同様に、光信号電荷に対応した信号電圧の合成機能を画素外である列信号線毎に設けてもよい。例えば、図1に記載された画素内の回路において、読み出しトランジスタ7、蓄積容量8、フィードバック容量9、書き込みトランジスタ10、蓄積ノード11、選択トランジスタ12及び電極ノード14を画素外の列信号線毎に配置することが可能である。この場合には、実施の形態3と同様に、光信号電荷に対応した信号電圧を合成する合成部が、画素毎ではなく列信号線毎に設けられているので、回路素子数が削減され、素子の省面積化が実現される。

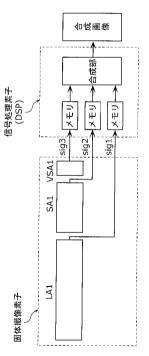

### [0158]

また、さらに、上述した合成部を、画素内または列信号線毎に配置された回路構成として実現するのではなく、素子外部の信号処理素子で生成されてもよい。図24は、合成部を素子内に有しない場合の本発明の固体撮像装置の機能構成図である。固体撮像素子で得られたLA1(長時間露光)の信号sig1、SA1(短時間露光)の信号sig2、及びVSA1(極短時間露光)の信号sig3は素子外部の信号処理素子DSPで合成され、合成画像である多重露光信号を出力する。この構成においても、信号処理素子DSPで合成された合成画像である多重露光信号を、実施の形態1~3で述べた色間でのゲイン調整を用いて簡便に行うことが可能である。

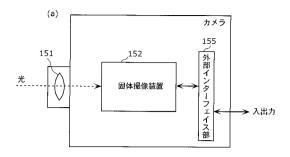

# [0159]

また、例えば、図25(a)に示されるように、本発明に係る固体撮像装置152が内蔵されたカメラも本発明に含まれる。同図に記載されたカメラは、レンズ151と、固体撮像装置152と、外部インターフェイス部155とを備える。レンズ151を通過した光は、固体撮像装置152に入射する。固体撮像装置152からの出力信号は、外部インターフェイス部155を介して外部に出力される。ここで、固体撮像装置152は、画素

ごとに異なる最大出力電圧(読み出し電荷容量)が均一化され、各色の画素部で実行される多重露光の入射光強度 - 合成信号電圧が簡便に補正されるので、輝度バラツキが抑制され広いダイナミックレンジを有する輝度信号を有する。このようなカメラは、強い光が入射したときであっても、あるいは微弱な光が入射されても、鮮明な画像を撮影することができる利点を有し、例えば、図25(b)に示されるデジタルスチルカメラや図25(c)に示されるビデオカメラとして実現される。

【産業上の利用可能性】

[0160]

本発明は、特に固体撮像素子を内蔵するデジタルスチルカメラやビデオカメラに有用であり、特に広いダイナミックレンジのカラー画像が必要な固体撮像装置に用いるのに最適である。

10

【図面の簡単な説明】

[0161]

【図1】本発明の実施の形態1における固体撮像素子の有するFDA型画素の回路図である。

【図2】本発明の実施の形態1に係るm行n列の画素アレイを有するカラー固体撮像装置の構成図である。

【図3】本発明の実施の形態1に係る固体撮像装置の有する制御線群に印加する制御パルスのタイミングチャートである。

【図4】本発明の実施の形態1に係る固体撮像装置の有する制御線群に印加する制御パルスのタイミングチャートである。

20

【図5】(a)は、本発明のR画素の有する受光素子の電荷蓄積時におけるポテンシャルを表す図である。(b)は、本発明のG画素の有する受光素子の電荷蓄積時におけるポテンシャルを表す図である。(c)は、本発明のB画素の有する受光素子の電荷蓄積時におけるポテンシャルを表す図である。

【図6】(a)は、本発明のR画素の有する受光素子の電荷読み出し時におけるポテンシャルを表す図である。(b)は、本発明のG画素の有する受光素子の電荷読み出し時におけるポテンシャルを表す図である。(c)は、本発明のB画素の有する受光素子の電荷読み出し時におけるポテンシャルを表す図である。

30

【図7】(a)は、本発明の実施の形態1に係る固体撮像装置の有するR画素の第一の露光期間における光電変換特性を表すグラフである。(b)は、本発明の実施の形態1に係る固体撮像装置の有するG画素の第一の露光期間における光電変換特性を表すグラフである。(c)は、本発明の実施の形態1に係る固体撮像装置の有するB画素の第一の露光期間における光電変換特性を表すグラフである。

【図8】(a)は、本発明の実施の形態1に係る固体撮像装置の有するR画素の第二の露光期間における光電変換特性を表すグラフである。(b)は、本発明の実施の形態1に係る固体撮像装置の有するG画素の第二の露光期間における光電変換特性を表すグラフである。(c)は、本発明の実施の形態1に係る固体撮像装置の有するB画素の第二の露光期間における光電変換特性を表すグラフである。

40

【図9】(a)は、本発明の実施の形態1に係る固体撮像装置の有するR画素の第一合成信号の光電変換特性を表すグラフである。(b)は、本発明の実施の形態1に係る固体撮像装置の有するG画素の第一合成信号の光電変換特性を表すグラフである。(c)は、本発明の実施の形態1に係る固体撮像装置の有するB画素の第一合成信号の光電変換特性を表すグラフである。

【図10】(a)は、本発明の実施の形態1に係る固体撮像装置の有するR画素の第三の露光期間における光電変換特性を表すグラフである。(b)は、本発明の実施の形態1に係る固体撮像装置の有するG画素の第三の露光期間における光電変換特性を表すグラフである。(c)は、本発明の実施の形態1に係る固体撮像装置の有するB画素の第三の露光期間における光電変換特性を表すグラフである。

【図11】(a)は、本発明の実施の形態1に係る固体撮像装置の有するR画素の第二合

成信号の光電変換特性を表すグラフである。(b)は、本発明の実施の形態 1 に係る固体撮像装置の有する G 画素の第二合成信号の光電変換特性を表すグラフである。(c)は、本発明の実施の形態 1 に係る固体撮像装置の有する B 画素の第二合成信号の光電変換特性を表すグラフである。

【図12】(a)~(i)は、本発明の実施の形態1に係る固体撮像装置の画素回路における電荷及び電圧状態を表す図である。

【図13】本発明の実施の形態1に係る、調整部を備えた固体撮像装置の構成図である。

【図14】(a)は、ゲイン調整されたR信号の光電変換特性を表すグラフである。(b)は、ゲイン調整されたG信号の光電変換特性を表すグラフである。(c)は、ゲイン調整されたB信号の光電変換特性を表すグラフである。

【図15】本発明の実施の形態1に係る固体撮像装置の有する転送トランジスタのゲート電圧を調整する動作フローチャートである。

【図16】(a)は、FDA型回路で構成された画素部の回路構成図である。(b)は、AMI型回路で構成された画素部の回路構成図である。

【 図 1 7 】本発明の実施の形態 2 における固体撮像装置の有する F D A 型画素の回路図で ある。

【図18】本発明の実施の形態2に係るm行n列の画素アレイを有するカラー固体撮像装置の構成図である。

【図19】本発明の実施の形態2に係る固体撮像装置の有する制御線群に印加する制御パルスのタイミングチャートである。

【図20】(a)は、本発明の実施の形態2に係る固体撮像装置の有する画素部の長時間露光における光電変換特性を表すグラフである。(b)は、本発明の実施の形態2に係る固体撮像装置の有する画素部の短時間露光における光電変換特性を表すグラフである。(c)は、本発明の実施の形態2に係る固体撮像装置の有する画素部の超短時間露光における光電変換特性を表すグラフである。

【図21】(a)は、本発明の実施の形態2に係る固体撮像装置の有する画素の合成信号の光電変換特性を表すグラフである。(b)は、ゲイン調整前後での光電変換特性を表すグラフである。

【図22】本発明の実施の形態3に係る固体撮像装置の回路構成図である。

【図23】本発明の実施の形態3における固体撮像装置の動作タイミングチャートである

【図24】合成部を素子内に有しない場合の本発明の固体撮像装置の機能構成図である。

【図25】(a)は、本発明の固体撮像装置が内蔵されたカメラの機能構成図である。(b)は、本発明の固体撮像装置が内蔵されたデジタルスチルカメラの外観図である。(c)は、本発明の固体撮像装置が内蔵されたビデオカメラの外観図である。

【図26】特許文献1記載の固体撮像素子のブロック図である。

【図27】特許文献1記載の固体撮像素子における露光時間および出力のタイミングを示す図である。

【図28】非特許文献1に記載された固体撮像素子の画素内における回路構成図である。

【図 2 9 】非特許文献 1 に記載された固体撮像素子の画素回路に印加される電気信号のタイミングチャートである。

【図30】(a)は、非特許文献1に記載された固体撮像素子の有する受光素子の第一の露光期間における光電変換特性を表すグラフである。(b)は、非特許文献1に記載された固体撮像素子の有する受光素子の第二の露光期間における光電変換特性を表すグラフである。(c)は、非特許文献1に記載された固体撮像素子の有する受光素子の第三の露光期間における光電変換特性を表すグラフである。(d)は、非特許文献1に記載された固体撮像素子の有する受光素子の第一の合成動作期間における光電変換特性を表すグラフである。(e)は、非特許文献1に記載された固体撮像素子の有する受光素子の第二の合成動作期間における光電変換特性を表すグラフである。

【図31】(a)は、異なる種類のカラーフィルタが配置された画素の有する従来の光強

10

20

30

40

度・電荷量特性を示すグラフである。(b)は、R,G,B画素の有する従来の光強度・ 電荷量特性を各色固有の増幅率によりホワイトバランス調整を行った場合の光強度・電荷 量特性を示すグラフである。

### 【符号の説明】

1 7 4

アンプ

```

[0162]

1, 201

受光素子

2, 202

転送トランジスタ

3 、 2 0 3

FDノード

4, 204

リセットトランジスタ

10

5 \ 2 0 5

出力トランジスタ

6, 206

負荷トランジスタ

7, 207

読み出しトランジスタ

8, 208

蓄積容量

9,209

フィードバック容量

10,210

書き込みトランジスタ

1 1 、 2 1 1

蓄積ノード

1 2 、 2 1 2

選択トランジスタ

13,213

負極ノード

14,214

電極 ノード

20

2 0 、 3 0 、 4 0 カラー固体撮像装置

2 1 、 3 1 、 5 0

FDA型画素

垂直シフトレジスタ

2 2

2 3

水平シフトレジスタ

2 4

画素電源部

2 5

駆動部

2 6

カラムアンプ

出カアンプ

2 7

4 1

画素行選択トランジスタ

4 2

読み出しトランジスタ

30

43、44、126 容量

4 5 、 1 2 1 、 1 2 2 、 1 2 4 、 1 2 5 スイッチングトランジスタ

47 ソースフォロワ出力点

60r, 60g, 60b, 61r, 61g, 61b, 62r, 62g, 62b, 63r

、 63g、 63b、 64r、 64g、 64b、 65r、 65g、 65b、 66r、 66g

、66b、67r、67g、67b、90r、90g、90b、261、262、263

、 2 7 1 、 2 7 2 、 2 7 3 光電変換特性

68r、68g、68b、69r、69g、69b、70r、70g、70b、91r

、91g、91b、92r、92g、92b、251、252 ニーポイント

8 1

調整部

40

8 2

マルチプレクサ

8 3

増幅部

設定部

8 4

バッファ回路

1 2 3

1 5 1

レンズ

1 5 2

固体撮像装置

1 5 5

外部インターフェイス部

1 7 1

画素部

1 7 2

フォトダイオード

1 7 3

ノイズキャンセラ

50

```

【図1】

【図2】

【図3】

【図4】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

# 【図9】

# 【図10】

第三の露光(t6~t7)における光電変換特性

# 【図11】

# 【図12】

# 【図13】

# 【図14】

【図15】

# 【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

# 【図25】

【図26】

【図27】

# 【図28】

【図29】

【図30】

【図31】

# フロントページの続き

# (72)発明者 山田 隆善

大阪府門真市大字門真1006番地 パナソニック株式会社内

F ターム(参考) 4M118 AA02 AB01 BA14 CA02 DD05 DD12 FA06 FA33

5C024 AX01 BX01 CX11 CX47 CX54 EX52 GX06 GY38 GY39 GZ02

5C065 AA01 AA03 BB13 DD10 DD15 EE03 GG10 GG15