# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51)Int. CI. <sup>6</sup><br>HO1L 21/3205 | (45) 공고일자<br>(11) 등록번호                            | 1998년 12월01일<br>특0152370      |

|-------------------------------------------|---------------------------------------------------|-------------------------------|

| ·                                         | (24) 등록일자                                         | 1998년06월26일                   |

| (21) 출원번호<br><u>(</u> 22) 출원일자            | 특 1995-003627 (65) 공개번호<br>1995년02월24일 (43) 공개일자  | 특 1995-025957<br>1995년09월 18일 |

| (30) 우선권주장                                | 94-026672 1994년02월24일 일본(JP)                      |                               |

| (73) 특허권자                                 | 닛본덴기 가부시끼가이샤 - 가네꼬 히사시<br>일본국 도꾜도 미나도꾸 시바 5쪼메 7-1 |                               |

| (72) 발명자                                  | 미까기 가오루                                           |                               |

| (74) 대리인                                  | 일본국 도꾜도 미나도꾸 시바 5쪼메 7-1 닛본덴기<br>구영창, 주성민          | 가무시끼가이샤 내                     |

| 실사과 : 귀이히                                 |                                                   |                               |

#### <u>심사관: 권인희</u>

#### (54) 적층 구조의 배선을 갖고 있는 반도체 디바이스 및 그 제조 방법

#### 요약

금속 배선은 Ti막, TiN막, Cu-Ti 화합물막, 및 Cu 및 다른 금속 성분을 소량 포함하는 Cu 합금막을 포함하는 적층 구조를 갖고 있고, 이 막들은 반도체 기판 상에 위치된  $SiO_2$  상에 연속적으로 형성된다. W막은 적층 구조의 표면을 피복한다. Cu-Ti 화합물막은 순차 열 처리에 이어 Ti 및 Cu 합금 타겟을 스퍼터링하거나, 순차 열 처리에 이어 Cu-Ti 합금 타겟 스퍼터링으로 형성된다. Cu-Ti 화합물막은 Cu 합금막과 TiN 막과의 밀착성을 증가시키고, W 막은 산화 및 부식으로부터 금속 배선을 보호한다.

#### 叫丑도

#### 명세서

[발명의 명칭]

적층 구조의 배선을 갖고 있는 반도체 디바이스 및 그 제조 방법

[도면의 간단한 설명]

제1a-1c도는 제1 종래 배선 구조의 연속적인 제조 단계를 도시하는 단면도.

제2a-2b도는 제2 종래 배선 구조의 연속적인 제조 단계를 도시하는 단면도.

제3a-3c도는 제3 종래 배선 구조의 연속적인 제조 단계를 도시하는 단면도.

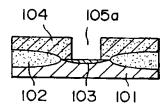

제4a-4d도는 비평면 구조로 된 제4 종래 배선 구조의 연속적인 제조 단계를 도시하는 단면도.

제5a-5d도는 평면 구조로 된 제5 종래 배선 구조의 연속적인 제조 단계를 도시하는 단면도.

제6a-6b도는 제6 종래 배선 구조의 연속적인 제조 단계를 도시하는 단면도.

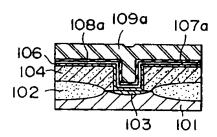

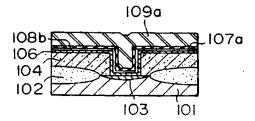

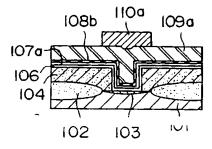

제7a-7f도는 본 발명의 제1 실시예에 따른 반도체 디바이스의 배선 구조의 연속 제조 단계의 단면도. 제8a-8e도는 본 발명의 제2 실시예에 따른 반도체 디바이스의 배선 구조의 연속 제조 단계의 단면도.

\* 도면의 주요부분에 대한 부호의 설명

101 : Si 기판102 : 필드 산화막103 : 확산 영역104 : 산화막

105a : 비아 홀 106 : 제1 Ti막

107a : TiN 막 108 : 제2 Ti막

109a : Cu 합금막 109b : Cu막

110a : Si₃N₄ 마스크 패턴

[발명의 상세한 설명]

본 발명은 적층 구조의 배선을 갖고 있는 반도체 디바이스 및 그 제조 방법에 관한 것으로, 특히 반도체 디바이스의 배선 패턴의 새로운 적층 구조에 관한 것이다.

소정의 반도체 디바이스는 구리(Cu)의 메인 컨덕터를 포함하는 적층 구조로 구성된 배선 패턴을 갖고 있다

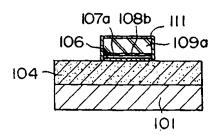

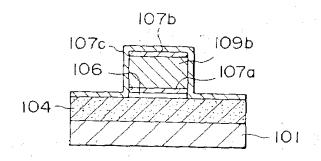

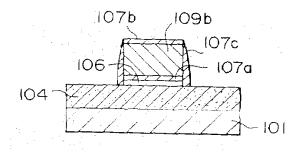

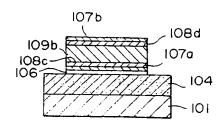

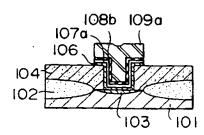

제1a-1c도는 특허 출원 번호 JP-A-88-156341에 기재된 반도체 디바이스의 제1 종래 배선 패턴의 연속적인 제조 단계를 도시하는 단면도이다. 먼저, 실리콘(Si) 기판(101) 위에 있는 실리콘 산화막(SiO $_2$ : 104) 상에는 반도체 기판(101)의 확산 영역 내에 옴 접촉을 형성하기 위한 50 nm 두께의 제1 티탄(Ti)막, Cu원자의 확산에 대해 배리어층으로 이루어지는 100 nm 두께의 제1 산화 티탄(TiN), 주 도전층으로 이루어지는 700 nm의 두께의 Cu막 및 Cu 확산에 대해 배리어층으로 이루어지는 200 nm의 두께의 제2 TiN막이 연속적으로 형성된다. 다음에, 제2 TiN막은 에칭되어 공지된 기술로 막 패턴(107b)를 형성한다. 그 다음, Cu막은 제2 TiN 패턴(107b)를 마스크로서 사용하는 이온 밀링 기술로 에칭하여 Cu 패턴(109b)를 형성한다. Cu 패턴(109b) 아래에 있는 제1 TiN막 및 제1 Ti막은 10 : 1 의 유량으로 헥사플루오르화황(SF $_6$ ) 및 산소  $(O_2)$  가스로 구성된 혼합 가스를 이용하는 반응성 이온 에칭(RIE) 기술로 에칭하여 TiN 및 Ti 패턴(107a 및 106)를 형성한다. 따라서, 제1a도에 도시된 구조가 얻어진다.

제1b도는 배선 패턴의 상부 표면, 배선 패턴의 측벽 및  $SiO_2$ 막(104)의 표면상에 바이어스 스퍼터링법으로 300 nm 두께의 TiN막(107c)를 형성한 후에 순차 단계의 배선 구조를 도시한다. 제1c도는 이방성 RIE에 따른 단계의 배선 패턴을 도시한 것으로,  $SiO_2$ (104) alc 배선 패턴의 상부 표면 상에 위치된 TiN막(107c)을 에치 오프(etch off)시켜 배선 패턴의 측벽에만 TiN(107c)를 남긴다. 결과적으로, 배선 패턴의 거의모든 표면이 배선의 TiN막(107b) 및 TiN막(107b)에 의해 피복 보호되어 낮은 배선 저항 및 장기 신뢰성을 갖고 있는 구조가 얻어진다. 선택적으로, TiN W, TiN Mo, TiN Cr막 등은 상술한 바와 같이 TiN막 대신에 TiN인 TiN인

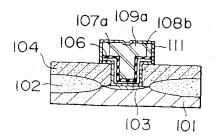

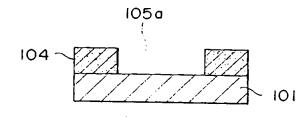

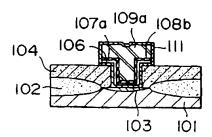

제2a도 및 제2b도는 특허 출원 번호 JP-B-74-3237에 기재된 제2 종래 배선 패턴의 연속적인 제조 단계를 도시하는 단면도이다. 제2a도에 도시하는 바와 같이, SiO<sub>2</sub> 막은 Si 기판(101) 상에 형성되고 패턴되어, 공지된 기술을 사용하여 콘택트 홀(105a: 제1 레벨 배선의 비아 홀, 이하 비아 홀이라 함)을 갖고 있는 막패턴(104)을 형성한다. 계속해서, TiN막(107a)는 반응성 스퍼터링법으로 SiO<sub>2</sub>막(104)의 표면 상 및 비아홀(105a)의 내측 상에 형성되고, 제2b도에 도시된 바와 같이 주 도전층으로 이루어지는 얇은 Ti막(108a) 및 금(Au)막(109c)를 순차 형성하기 위한 단계가 이어진다. 제2 Ti막(108a)는 주도전층으로 이루어지는 Au막(109c)와 Au 확산을 방해하는 배리어층으로 이루어지는 TiN막(107a)와의 밀착성을 증가시키기 위해 제공된다.

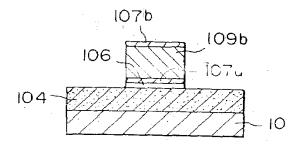

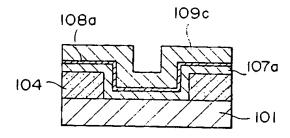

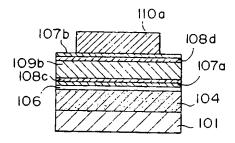

제3a-3c도는 Extended Abstracts of 183rd Electrochemical Society Meeting, 1993년 5월 93-1권 468 페이지의 케이. 오노(K. Ohno) 등에 의해 기록된 제3 종래 배선 패턴의 연속적인 제조 단계를 도시하는 단면도이다. 먼저, 약 500 nm 두께의 SiO₂막(104)가 Si 기판(101) 상에 형성된다. 그 다음, 30 nm두께의 제1 Ti막(106) 및 100 nm 두께의 제1 TiN막(17a)는 각각 스퍼터링 및 반응성 스퍼터링법으로 연속적으로 형성된다.

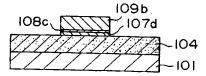

다음에, 30 nm 두께의 제1 텅스턴(W)막(108c) 및 500 nm 두께의 Cu막(109b)는 스퍼터링법으로 연속적으로 형성된다. 그 다음, 30 nm 두께의 제2 W막(108d) 및 50 nm 두께의 제2 TiN막(107b)는 스퍼터링법으로 Cu 막(109b) 상에 연속적으로 형성되어, 제3a도에 도시된 디바이스 구조로 된다.

상술한 단계 중에, 제1 Ti막(106)을 형성하는 단계는 SiO₂막(104)와 제1 TiN막(107a)와의 밀착성을 증가시키기 위한 것 뿐만 아니라 Si 기판(101) 내에 형성된 확산 영역과 제1 TiN막(107a)와의 콘택트 저항을 감소시키기 위해 행해진다. 여기에서, 제1 및 제2 TiN막(107a 및 107b)는 Cu막(109b) 내에서 Cu의 확산, 산화 및 부식을 방지하기 위해 제공된다. 또한, 이들TiN막은 일렉트로미그레이션(electromigration) 및 스트레스미그레이션(stressmigration)에 대한 내성을 향상시키는 기능을 갖고 있으므로, 배선의 장기 신뢰성을 얻을 수 있다.

한편, W막(108c 및 108d)는 Cu막(109b)와 TiN막(107a 및 107b)와의 밀착성을 증가시키기 위해 제공된다. W막(108c 및 108b)가 Cu막(109b)와 TiN막(107a 및 107b) 사이에 존재함에도 불구하고, 염소(CI) 원자를 포함하는 래디컬은 염소 원자를 포함하는 가스를 사용하여 고온에서 행해진 Cu막(109b)를 패터닝하는 단계 동안, Cu막(109b)와 TiN막(107a 및 107b) 사이에 계면을 침식시켜, TiN막(107a 및 107b)의 사이드 에칭 또는 필링 오프 중 하나가 발생한다.

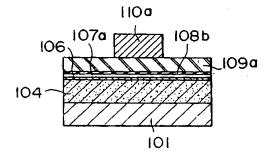

계속해서, 약 400-500 nm 두께의 실리콘 질화막( $Si_3N_4$ )막은 플라즈마 증가형화학 기상증착법(PE-CVD)에 의해 TiN막(107b) 상에 형성된다. 그 다음,  $Si_3N_4$  막은 금속막을 에칭하는데 사용되는  $Si_3N_4$  마스크 패턴(110a)를 형성하기 위해 공지된 포토리소그래픽 및 드라이 에칭을 사용하여 패턴화되어, 제3b도에 도시된 디바이스 구조로 된다.

더우기, 실리콘 테트라클로라이드(SiCl₄), Cl₂, 질소(N₂) 및 암모니아(NH ₃)로 구성된 가스를 사용하는 RIE 단께는 280 ℃의 기판 온도에서 TiN막(107b), W막(108d), Cu막(109b), W막(108c), TiN막(107a) 및 Ti 막(106)을 포함하는 적층을 에칭하도록 행해서, 제3c도에 도시된 바와 같은 배선 패턴을 얻는다. RIE단계

시, Si<sub>3</sub>N<sub>4</sub>막과 거의 동일한 구조를 갖고 있는 가장 얇은 막은 부산물로서 배선(도면에 도시하지 않음)의 측벽 상에 피착되어 Cu 패턴(109b)의 측벽 보호막으로서 작용한다.

산화 및 부식으로부터 Cu 표면을 보호하는 보호막을 갖고 있는 제4 종래 배선 패턴은 11th Symposium on VLSI Technology, the Digest of Technical Papers, 1991년 5월, 39 페이지에 제이. 조(J. Cho) 등에 의해 보고되어 있다. 제이. 조는 보호막으로 덮혀져 있는 Cu 배선의 2 구조 , 즉 비평면 구조 및 평면구조를 설명하고 있다. 제4a-4d도는 비평면 구조의 배선 패턴의 연속적인 제조 단계의 단면도를 도시하고, 제5a-5d도는 제5 종래 구조로서 평면 구조의 배선 패턴을 유사하게 도시하고 있다.

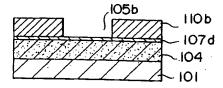

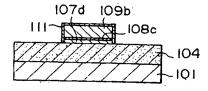

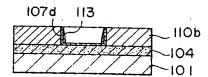

제1 SiO<sub>2</sub>막(104) 및 TiW막(107d)는 먼저 제4a도에 도시된 바와 같이 Si 기판(101) 상에 연속적으로 형성된다. 그 다음, 제2 SiO<sub>2</sub>막은 저온에서 TiW막(107d) 상에 성장되는데, 이 제2 SiO<sub>2</sub>막은 공지된 기술로 패턴화되어, 배선을 일시적으로 끼워넣는 트렌치(105b)를 갖고 있는 SiO<sub>2</sub> 마스크 패턴(110b)를 형성한다.

계속해서, 얇은 W막(108c)는 공지된 기술인 선택 W-CVD법에 의해 SiO $_2$  트렌치(105b)의 저부로 이루어지는 TiW막(107d) 상에 선택적으로 성장된다. 그 후, Cu막(109b)는 비선택 Cu-CVD 또는 선택 Cu-CVD법으로 Cu 막의 화학적-기계적 폴리싱(CMP: Chemical-Mechanical Polishing)을 사용하여 W막(108c) 상에 선택적으로 형성되어 제4b도에 도시된 구조로 된다.

Cu막(109b)를 마스크로서 사용하여 SiO<sub>2</sub> 마스크 패턴(110b) 및 TiW막(107b)의 순차 에치 백은 제4c도에 도 시된 바와 같이, TiW막(107d), W막(108c) 및 Cu막(109b)를 포함하는 적층 구조의 배선을 제공한다. 계속 해서, W막(111)은 선택 W-CVD법을 사용하여 적층 구조를 피복하도록 형성하여, 제4d도에 도시된 바와 같 이 Cu막(109b)를 산화 및 부식으로부터 보호한다.

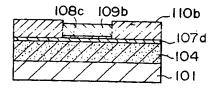

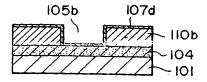

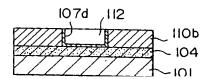

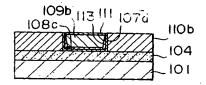

한편, 제5a-5d도에 도시된 평면 구조를 형성하는 상술한 방법은 Si 기판(101) 상에 제1 Si0₂막(104)를 형성하는 프로세스 단계를 유사하게 개시한다. 제2 Si0₂막은 공지된 기술을 사용하여 형성하고 패턴화하여, 배선을 영구적으로 끼우기 위해 트렌치(105b)를 갖고 있는 Si0₂ 마스크 패턴(110b)를 형성한다. 이 경우그 다음, TiW막(107d)는 전체 표면을 거의 덮도록 스퍼터 증착하여, 제5a도에 도시된 구조를 얻는다.

포토레지스트막은 스핀 코팅으로 전체 표면을 피복하도록 형성된다. 그 다음, 포토레지스트막(112) 및 TiW막(107d)가 제5b도에 도시된 바와 같이  $SiO_2$  트렌치(105b)내에만 남는 조건으로 포토레지스트막 및 TiW 막을 에치 백한다. 그 다음, 포토레지스트막(112)는 제거되고,  $Si_3N_4$ 막은 거의 전체 표면 상에 성장된 다음, 제5c 도에 도시된 바와 같이  $SiO_2$  트렌치(105b)의 내부 측벽에만 남겨  $Si_3N_4$  측벽 스페이서(113)을 얻는 조건으로 이방성 에치 백한다. 제5d도는 Tiw막(107d) 상에 형성된 W막(108c), Cu막(109b) 및 W막(108d)를 포함하는 최종 배선 구조를 도시하고 있다.

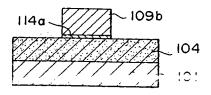

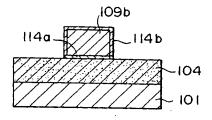

제6a-6b도는 질화니오브(niobium nitride : NbN) 보호막이 Cu 배선의 표면을 보호하기 위해 셀프 얼라이 닝 방식으로 형성되는 제6 종래 배선 구조의 연속적인 제조 단계를 도시하는 단면도이다. 이 구조39th Spring Meeting of the Japan Society of Applied Physics and Related Societies, 1992년 강연 번호 30p-ZH-9, 2권, 707 페이지에 에이취. 이토(H. Itoh) 등에 의해 발표되었다.

Si 기판(101) 상에 SiO₂막(104)로부터 시작하는 단계는 제6a도에 도시된 바와 같이 스퍼터 증착 및 패터닝법을 사용하여 Nb막(114a) 및 Cu막(109b)를 형성한다. 다음에, 열 처리는 N₂ 분위기에서 30분 및 1 시간동안 약 750 ℃에서 처리되어, 제6a도에 도시된 바와 같이 Cu막(109b)를 통해 Nb 원자를 Cu막(109b)의 표면에 확산하고, NbN 보호막(114b)를 형성한다. Nb 원자는 열 처리후, 3 at % 정도로 Cu막(109b)에 남는다. 그러나, Cu막(109b)의 저항은 낮게 유지되는데, 예를 들어 1.89 -cm이다. X선 회절(XRD) 분석으로 Nb막(114a)상에 형성된 Cu막의 결정은 (111) 방향이 가장 강한 것을 알 수 있는데, 이것은 일렉트로- 및스트레스 미그레이션에 대해 형성된 배선 패턴의 내성이 높다는 것을 의미한다.

상술한 5 종류의 종래의 기술은 후술하는 결점을 제외하여 상대적으로 우수한 성능을 나타낸다.

본 발명의 목적은 제조시 금속 배선막의 필링 오프에 대해 기계적, 열적 및 화학적 내성 및 저항을 갖고 있는 우수한 성능의 배선 구조를 갖고 있는 반도체 디바이스 및 배선 구조를 형성하는 방법을 제공하기 위한 것이다.

본 발명에 따른 반도체 디바이슨는 반도체 기판: 기판 위에 있는 절연막: 및 Ti막, TiN막, Ti-Cu 화합물 막 및 Cu와 Cu외의 미량의 적어도 하나의 금속 성분을 포함하는 Cu 합금막을 포함하는 적층 구조의 금속 배선을 포함하고, 이들 막들은 적어도 적층막 상에 연속적으로 형성되는 것을 특징으로 한다.

우수한 성능을 갖고 있는 옴 접촉은 금속 배선이 적층막 내에 형성된 비아홀을 통해 반도체 기판의 주표 면에 접촉하는 위치에서 얻어진다. 금속 배선은 금속 배선의 거의 전체 표면을 피복하는 W막을 추가적으 로 포함해도 좋다.

또한, 적어도 하나의 금속 성분은 추가 성분으로서 지르코늄(Zr,), 은(Ag), 납(Sn) 및 안티몬(Sb)로 구성되는 그룹에서 선택되어도 좋다. 적어도 하나의 금속 성분의 함유량은 모든 추가 금속 성분의 0.01과 0.5 wt % 사이에 존재해도 좋다.

다른 양호한 실시예는 Cu-Ti 화합물막이 원자 비율의 조성을 Cu : Ti = 5 : 1에서 Cu : Ti = 1 : 2까지의 범위에서 갖는다.

또 본 발명의 반도체 디바이스 제조 방법은 반도체 기판 위에 있는 절연막을 형성하는 단계; 절연막 상에 Ti막을 형성하는 단계; Ti막 상에 TiN막을 형성하는 단계; Cu-Ti 화합물막, 및 Cu 및 미량의 적어도 하나의 금속 성분을 포함하는 Cu 합금막을 형성하는 단계, 배선 패턴을 형성하기 위해 Cu 합금막, Cu-Ti 화합물막, TiN막 및 Ti막을 패터닝하는 단계를 포함하고, Cu-Ti 화합물막 및 Cu 합금막은 TiN막 상에 연속적으로 적층된다.

Cu-Ti 화합물층 및 Cu 합금층을 연속적으로 형성하는 단계에 있어서, 양 층들은 스퍼터 증착법으로 적절한 조성을 갖고 있는 각각의 타겟으로부터 독립적으로 형성될 수 있다. 선택적으로, 양 층들은 제2 Ti층 및 Cu 합금층이 TiN막 상에 먼저 연속적으로 형성되는 방식으로 형성될 수 있고, 그 다음 연속적인 열 처리로 Cu 및 Ti를 포함하는 금속간 화합물층으로 변환된다. 본 발명에 따른 반도체 디바이스 또는 본 발명에 따른 방법이 저 저항 Cu 합금층, 우수한 옴 접촉 저항을 제공하는 Ti막, Cu 확산에 대해 우수한 배리어층으로서 작용하는 TiN막 및 자체와 TiN막간 뿐만 아니라 자체와 Cu 합금막간의 우수한 내성을 제공하는 Cu-Ti 화합물층을 포함하는 적층 구조의 배선을 갖고 있기 때문에, 본 발명은 우수한 기계적, 열적 및 화학적 내성 뿐만 아니라 우수한 전기 전도도 및 옴 접촉을 갖고 있는 금속 배선을 제공하므로, 반도체 디바이스의 제조 단계동안 적층 구조에는 필링 오프가 발생하지 않는다.

이하, 도면을 참조하여 상세히 설명하겠다.

본 발명의 양호한 실시예를 설명하기 전에, 종래 방법에 포함된 문제점 및 단점을 본 발명의 이해를 높이 기 위해 설명하겠다.

제1a-1c도에 도시된 제1 종래 배선 구조는 Cu막(106) 및 측벽 스페이서(107c)로서 작용하는 TiN막을 패터 닝하는 이온 밀링 단계를 포함하고 있기 때문에, 최소 공간을 갖는 배선 패턴에 적용하기 어렵다. 더욱이, Cu막(106)과 TiN막(107a, 107b 및 107c)와의 밀착성이 불충분하기 때문에, 디바이스 성능에서 양호한 제조 보유나 장기 신뢰성을 얻기 어렵다. TiN막 대신에 배리어 금속층으로서 W막이 사용된 경우, W막은 최소 패턴을 형성하기 어려워 적용이 곤란하다.

제2a-2b도에 도시된 제2 종래 배선 구조에 있어서, Ti막(108a) 및 AU막(109c)를 형성한 후 처리되는 열처리 단계는 Au막(109c) 내로 Ti 원자가 확산될 수 있어, Ti 원자가 Au내로 고용체로 될 수 있기 때문에, Ti막(108a)와 Au막(109c) 사이의 계면의 Ti 농도가 감소된다. 계면의 Ti 농도의 감소는 초기에 밀착성을 향상시키기 위해 얇은 두께의 Ti막(108a)만 사용되기 때문, TiN막(107a)와 Au막(109c)과의 밀착성이 즉시낮아진다. 특히, 다중 레벨 배선 구조의 제조 프로세스는 많은 열 처리 단계를 포함하므로, 계면의 Ti 농도가 최대로 낮아질 수 있어 가장 불량한 밀착성이 생긴다.

한편, 본래 두꺼운 Ti막(108a)가 계면의 Ti 농도를 증가시키도록 사용될 경우, Au막(109c)의 Ti 농도는 높아질 수 있어 Au막(109c)의 저항이 높아진다. 이들 상황은 열 처리가 Cu막내로 Ti 원자의 확산을 일으 킬 수 있기 때문에, Cu막으로 대체될지라도 유사하게 되어 불량한 밀착성이 생긴다.

제3a-3c도에 도시된 제3 종래 배선 구조는 6개의 층을 포함하는 적층 구조를 사용하고, 복잡한 프로세스로 인해 제조 비용이 상승하고 칩 생산율을 낮아진다.

또,  $Si_3N_4$ 와 유사한 구성을 갖고 있고, Cu 배선(109b)의 측벽을 보호하는 부산물로 구성된 얇은 보호막을 열악한 화학적 열적 안정성을 갖고 있으므로, 장기 신뢰성을 보장받을 수 없다. 이러한 배선은 Cu막에서 보호막에 야기된 부식 및 산화로 인해 우수한 열적 내성과 장기간 신뢰성을 갖지 못한다.

제4a-4d도에 도시된 제4 종래 배선 구조의 비평면 구조는 배선의 리셉터클로서 트렌치(105b)의 패터닝 단계시 SiO<sub>2</sub> 트렌치(105b)의 저부 상에 TiW막(107d)를 갖고 있다. SiO<sub>2</sub>막(110b)이 TiW막(107d)로부터 선택적으로 에치 백되는 프로세스 조건은 TiW막이 에치 스토퍼로서 거의 작용하지 못하기 때문에 특히 아래층이 단차가 생기거나 솔더가 생길 때를 규정하기가 어렵다. 더우기, SiO<sub>2</sub>막(110b) 및 TiW막(107d)가 Cu막(109b)를 마스크로하여 RIE버을 상요하여 패턴화되는 경우에, Cu막(109b)의 표면은 부식되어 전기 특성이 열화되고 반응 가스의 플라즈마에 노출된다. CMP 및 이온 밀링법은 Cu막(109b)에서 에치 선택 및 화학적 내성의 관점에서 상술한 에칭 단계에 적용하기 어렵다.

제5a-5d도에 도시된 제5 종래 배선 구조의 평면 구조는 SiO<sub>2</sub> 트렌치(105b) 내에 남겨진 포토레지스트막을 사용하여 TiW막(107d)를 에칭백하는 단계를 포함한다. 그러나, 일반적으로 포토레지스트막은 아래층에 형성된 단차 또는 솔더가 높은 측 상에는 너무 얇은 반면에, 단차가 높은 경우 단차가 낮은 측 상에는 너무 두껍다. 따라서, TiW막(107d)가 트렌치(105b)의 내측에만 남는 적절한 에치 백 조건을 세우기 어렵다.

더우기, 모든 Cu막(109b) 및 Cu막(109b)을 아래 위로 덥고 있는 W막(108c 및 111) 각각은 선택 CVD법을 사용하지 않고는 성장될 수 없다. 선택 CVD법을 사용하여 3개의 층 구조를 형성하는 단계는 우수한 선택 성을 보장하는 조건을 발견하기가 매우 어렵기 때문에 쉽지도 실용적이지도 않다.

제6a-6b도에 도시된 제6 종래 배선 구조에 있어서, NbN막(114b)를 형성하는 열 처리는 750 ℃ 정도의 높은 고온에서 처리되므로, 확산된 영역의 표면에 접촉하는 접촉 전극은 금속 확산 및 규화물화 반응으로인해 확산된 도펀트 원자를 흡수하고, 심지어는 PN 접합을 파괴하여, NbN막을 사용하는 Cu 표면의 보호가우수한 신뢰성을 제공하더라도 반도체 디바이스 특성을 열화시킨다. 결과적으로, 우수한 특성을 갖는 반도체 디바이스, 특히 최소 설계를 또는 얇은 접합을 갖는 디바이스를 얻기 어렵다는 다른 문제점이 발생한다.

이제, 본 발명의 양호한 실시예에 대해 도면을 참조하여 설명한다. 본 발명의 제1 실시예에 따른 반도체 디바이스는 연속적인 제조 단계를 도시하는 제7a-7f도에 도시된 배선 패턴을 갖고 있다. 먼저, 공지된 LOCOS 및 이온 주입법으로 Si 기판(101)의 주표면 상에 필드 산화막(102) 및 확산 영역(103)을 형성한다. 그 다음, 약 1000 nm 두께의 산화막(104)는 열 CVD법으로 필드 산화막(102) 및 확산 영역(104)을 덮도록 형성된다. 산화막(104)는 순수 SiO2막이 아니라, 포스포 실리케이트 글라스(phospho-silicate glass: PSG) 또는 보로 포스포 실리케이트 글라스(boro-phospho-silicate glass: BPSG)와 같은 붕소 또는 인 원자를 포함하는 도프된 산화막일 수 있다. RIE법으로 SiO2막(104) 내에 비아 홀(105a)를 형성하는 다음 단계는 제7a도에 도시된 구조를 제공한다.

그 다음, 30 nm 두께의 제1 Ti막(106), 100 nm 두께의 TiN막(107a), 5 - 10 nm 두께의 제2 Ti막(108a) 및 400 nm 두께의 Cu 합금막(109a)로 이루어지는 도전막은 DC 마그네트론 스퍼터링 및 DC 마그네트론 반응이온 스퍼터링법으로 연속적으로 형성되어 제7b도에 도시된 구조를 제공한다. Cu합금막(109a)는 Zr, Ag,

Sn 및 Sb로 구성되는 그룹에서 선택되는데, 추가 금속 성분의 함유량은 0.01과 0.1 wt% 사이다.

제1 Ti막(106)은 Si0₂막(104)과 TiN막(107a)와의 밀착성을 증가시킬 뿐만 아니라 최종 배선과 확산 영역 (103)와의 접촉 저항을 감소시키기 위해 제공된다. TiN막(107a)는 밑에 있는 확산 영역(103) 내로 금속막 안으로 확산하는 금속 원자를 차단하고, 최종 배선 구조의 일렉트로 미그레이션 내성 및 스트레스 미그레이션 내성을 향상시키기 위해 제공된다. Cu 내로 Zr, Ag, Sn 및 Sb와 같은 금속 성분의 추가는 Cu층의기계적 강도, 열적 안정성 및 산화 내성을 향상시킨다.

예를 들어, 순수한 금속 Cu막이 인장 강도가 20-25 kgf/㎜인 반면에, 0.01 wt %의 비율로 Cu막 내로 Zr을 추가시키면 35-45 kgf/㎜로 인장 강도가 증가한다. 한편, 순수한 Cu막의 재결정 온도가 150℃인 반면에, 0.01 wt %의 Zr을 포함하는 Cu 합금막은 재결정 온도가 450 ℃로 온도 안정성이 향상되었다.

일반적으로, 산화 지르코늄(ZrO<sub>2</sub>)를 형성하는 자유 에너지는 각각 산화 동 및 아산화동(CuO 및 Cu<sub>2</sub>O)의 자유도보다 더 낮은데, 이것은 Zr이 Cu보다 더 산화가 쉽게 된다는 것을 의미한다. 따라서, Cu의 산화 내성은 Zr 원자의 추가에 의해 향상되는데, 그 이유는 Zr 원자가 Cu 합금 내에서 Cu 원자 대신에 산화되기 때문이다. 또한, 기계적 강도 및 열적 내성의 향상은 ZrO<sub>2</sub>으로부터 발생된다. 즉, ZrO<sub>2</sub>가 Cu막 내에 존재하는 경우, ZrO<sub>2</sub>는 Cu 결정 내의 전위 루프를 트랩하여, Cu 원자의 미그레이션 및 Cu 원자의 확산을 억제하여 Cu막의 기계적강도 및 열적 내성을 향상시킨다. 이들 향상과 함께, 또한, Zr이 Cu막의 전기 전도도를 낮추더라도 일렉트로 미그레이션 및 스트레스 미그레이션 내성은 향상된다. 예를 들어, Cu막 내로 Zr을 0.1 wt % 추가시키면 전기 전도도는 3-6 % 감소된다.

또한, 기계적 강도 및 열적 내성은 금속 Ag가 0.01-0.1 wt % 함유량으로 Cu막 내로 삽입되는 경우와 유사하게 향상된다. 예를 들면, 0.05 wt %의 Ag를 포함하는 Cu 합금막의 인장 강도는 45 kgf/mm 이상이고, 재결정 온도가 320 ℃로 상승한다. 전기 전도도의 감소는 Zr의 경우보다 더 작은데, 예를 들어 Ag가 산화내성의 적절한 향상만을 제공하더라도 0.1 wt %의 Ag의 경우에 기껏해야 1-3 %만 감소된다.

0.01 wt %의 Sn 또는 Sb가 추가될 때, Cu의 재결정 온도는 50-150 ℃로 상승하고, 이들의 기계적 특징은 현저하게 향상된다. 그러나, 이들 추가는 산화 내성의 적절한 향상만을 나타내고, Cu막의 전도도를 2-4 % 정도 저하시킨다.

상술한 바와 같이, 미량의 Zr, Ag, Sn 및/또는 Sb 원자의 추가는 Cu막의 전기 특성을 감소시키지 않고 Cu 막의 기계적, 열적 및 화학적 특성을 향상시킬 수 있다.

계속해서, 금속 열 어닐링(RTA)는 램프 어닐링 장치를 사용하여 10-30 초 동안 600℃와 700℃ 사이로 상승하는 온도로 N₂ 분위기에서 처리되어, 제7c도에 도시된 구조를 제공한다. 열 처리는 TiN막(107a)에 남아 있는 반응하지 않은 N₂와 반응시킬 뿐만 아니라 확산 영역(103)에 접촉된 제1 Ti막(106)을 Ti 실리사이트(TiSi₂)층을 형성하도록 Si 와 반응시킴으로써, TiN막(107a)가 인정된다. 또한, 열 처리는 제2 Ti막(108a)를 Cu 합금막(109a)와 반응시켜, 금속간 화합물을 포함하는 20 - 40 nm 두께의 Cu- Ti 화합물층(108b)를 형성한다. Ti막의 규화물화는 금속막[제1 Ti막(101)]과 반도체 금속[확산 영역(103)] 사이의 쇼트키 접합의 배리어 높이를 낮추어, TiN막(107a)의 안정성으로 인해 접촉 저항이 감소하고 Cu 확산에 대한 TiN막(107a)의 배리어 능력이 증가된다.

Cu 합금막(109a)와 TiN막(107a) 사이에 형성된 Cu-Ti 화합물증(108b) 내에 포함된 7 종류의 금속간 화합물을 미확인 물질을 포함한다. 화합물 종류는 Cu<sub>4</sub>Ti(미확인), Cu<sub>7</sub>Ti<sub>2</sub>(미확인),Cu<sub>3</sub>Ti(미확인),Cu<sub>2</sub>Ti, Cu<sub>3</sub>Ti <sub>2</sub> 및 CuTi<sub>2</sub>를 포함한다.

Cu-Ti 화합물층(108b)의 화합물 종류, 결정 구조 및 막 두께는 제2 Ti막(108a)의 막 두께 및 RTA 단계의 조건에 따라 변한다. 그러나, Cu 함유량이 많이 포함된 Cu-Ti 화합물층은 계면에 형성되는데, 그 이유는 기본적으로 600℃의 Cu 상에서의 Ti 원자의 고용해(solid solubility)가 온도의 Ti 상에서의 Cu 원자보다도 고용도가 높기 때문이다. 이 경우, Zr, Ag, Sn 또는 Sb 원자의 추가는 이들 양이 최소이기 때문에 Cu-Ti 금속간 화합물 형성의 반응에는 영향을 미치지 않는다. Cu-Ti 화합물층(108b)는 우수한 열적 안정성으로 인해 Cu 확산에 대해 배리어 층으로서 작용할 뿐만 아니라, TiN 및 Cu막의 각각에 대해 우수한 밀착성으로 인한 TiN막(107a)와 Cu 합금막(109a)와의 밀착 촉진층으로서 작용한다. TiN막(107a)와 Cu 합금막(109a) 사이에 형성된 Cu-Ti 화합물층(108b)는 Cu 합금막의 드라이 에칭동안 Cu 합금막(109a)로부터 TiN막(107a)이 사이드 에칭 및 TiN막(107a)의 필링 오프를 방지할 수 있다.

제7d도는 적층 도전막을 패터닝하기 위해 Si₃N₄ 마스크 패턴을 형성한 후의 배선 구조를 도시한 것이다. 먼저, 300-500 nm 두께의 Si₃N₄막은 기판 온도가 300-350 ℃이고, 반응 압력이 0.2-0.5 Torr이며, SiH₄ 유량이 150-300 sccm이고, NH₃ 유량이 400-800 sccm이며, RF 전원이 0.5-1.5 kW인 조건 하에서 사일렌(SiH₄) 및 NH₃을 포함하는 소스 가스의 PE-CVD 반응으로 Cu 합금막(109a) 상에 성장된다. 그 다음, 공지된 포토리소그래픽 및 드라이 에칭법을 사용하여 Si₃N₄막은 패턴화되어 마스크 패턴(110a)를 형성한다. Si₃N₄ 마스크 패턴(110a)의 두께는 고려되는 Si₃N₄ 마스크 패턴에 적층 도전막의 에치 선택과 함께 결정된다.

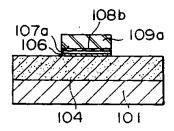

제7e도는 Cu 합금막(109a), Cu-Ti 화합물층(108b), Tin막(107a) 및 제1 Ti막(106)을 포함하는 도전형 적층의 에치 백 후의 배선 구조를 도시한 것이다. 에치 백은 기판 온도가 약 280 ℃이고, 대기 압력이 약 2 Pa이며, SiCl₄유량이 약 20 sccm이고, Cl₂ 유량이 약 20 sccm이며, NH₃의 유량이 10-30 sccm이고, N₂ 유량이 약 80 sccm이며, RF 전원이 300 W인 조건하에서 반응 가스로서 SiCl₄ + Cl₂ + NH₃ 및 희석 가스로서 N₂를 사용하여 RIE법으로 처리된다. 그 다음, Cu 합금막(109a)의 상부 상에 남아 있는 Si₃N₄ 마스크 패턴 (110a)는 SiO₂(104)에 대한 Si₃N ₄막의 높은 에치 선택에서 RIE법을 사용하여 제거된다.

상술한 도전 적층의 에칭 단계 상에, TiN막(107a)의 사이드 에치 및 Cu 합금막(109a)와 TiN막(107a) 사이

의 계면에서의 필링 오프는 Cu 합금막(109a)와 Cu-Ti 화합물층(108b) 및 Cu-Ti 화합물층(108b)와 TiN막(107a)와의 큰 밀착성으로 인해 발생하지 않는다. 그러므로, 밀착을 향상시키기 위해 종래의 기술에서 필요한 W막과 같은 개재층을 형성할 필요가 있고, 최소 배선 패턴을 얻기 위한 배선 구조 및 이것을 형성하는 프로세스를 단순화한다.

제7f도는 약 20 nm 두께의 W막(111)을 갖고 있는 적층 배선을 피복함으로써 안정된 최종 배선 구조를 도시하고 있다. 안정화는 잔여 가스로서 수소( $H_2$ )가스를 이용하여 선택 W-CVD법으로 처리된다. W막(111)을 배선 패턴 상에 선택적으로 또한 높은 균일성으로 형성하기 위해서는 2개의 전 처리가 필요하다. 하나는 Si 웨이퍼를 0.5-3 vol %의 희석(dil.) 플루오르화 수소산(HF) 내로 넣은 것이다. 다른 하나는 5-30 vol %의 dil. 황산( $H_2SO_4$ ), 질산( $HNO_3$ ), 왕수 또는  $HNO_3$ 와 인산(H  $_3PO_4$ )의 혼합 산과 같이 Cu막을 에칭할 수 있는 용액 내로 딥핑하는 것이다. HF 처리는 이온 손상된  $SiO_2$ 막(104)의 표면 상 및 적층 배선의 측벽상에 부산물로서 피착된  $Si_3N_4$ 와 거의 동일한 화학 조성을 갖고 있는 막을 제거 하는 것으로, W-CVD 단계에서 선택성을 향상시킨다. Cu 에칭 용액에 의해 처리는 마스크로서  $Si_3N_4$  패턴(110a)를 얻기 위해 RIE시, Cu 합금막 표면(109a) 상에 발생된 손상된 층을 제거하기 위한 처리이다. 이 처리는 선택 W-CVD시, 균일 핵 발생 및 필름 성장을 제공한다.

선택 W-CVD법용으로 설정된 성장 조건은 기판 온도가 350  $^{\circ}$ 오와 400  $^{\circ}$ C 사이이고, 반응 압력이 20-80 mTorr이며, 텅스텐 헥사플루오르(WF $_{6}$ )의 유량이 0.5-1 sccm이고, H $_{2}$  유량이 200과 400 sccm 사이이다. 텅스텐 성장률이 면적내에 산화 표면에 대한 금속 배선 표면의 노출 비율에 따라 변할지라도, 상술한 조건을 예를 들면 5 -7 nm/min정도로 W 성장률이 비교적 낮기 때문에, W막의 두께를 잘 제어할 수 있다.

상술한 바와 같은 배선 구조는 Cu 합금막(109a)와 TiN막(107a)와의 밀착성 및 배리어 기능을 향상시키기위해 Cu-Ti 화합물층(108n)를 갖고 있다. 게다가, 순수한 Cu막보다 높은 기계적 강도 및 열적 내성을 갖고 있는 Cu 합금막(109a)은 우수한 기계적 및 열적 특성을 제공한다. 더우기, Cu를 산화 및 부식으로부터 보호하는 W막(111)은 배선의 장기 신뢰성을 제공하고, 배선 구조 및 이것의 제조 단계는 종래 기술과비교하여 복잡하지 않다.

본 발명에 따른 반도체 디바이스 및 이것을 형성하는 방법은 MOS, 바이폴라 등의 디바이스, 또는 메모리, 로직 등의 회로의 종류에 관계없이, 광범위한 반도체 디바이스에 적용가능하다.

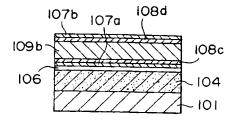

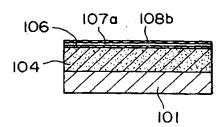

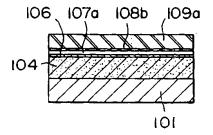

이제, 본 발명의 제2 실시예는 제8a-8e도를 참조하여 설명하겠다. 500-1000 nm 두께의 SiO₂(104)는 열적 CVD 또는 PE-CVD로 Si 기판(101) 상에 형성된 다음, 30 nm 두께의 제1 Ti막(106) 및 100 nm 두께의 TiN(107a)는 SiO₂막(104)상에 연속적으로 형성된다. 다음에, 약 10 nm 두께의 Cu-Ti 합금막은 타겟으로서 Cu-Ti 합금을 사용하여 DC 마그네트론 스퍼터링법에 의해 형성되고, 열 처리는 제8a도에 도시된 바와 같이 Cu-ti 합금막을 Cu-Ti 금속간 화합물막(108b)으로 변환하기 위해 400-600 ℃의 비산화성 분위기에서 행해진다. 최종 Cu 조성이 타겟 조성 뿐만 아니라 열 처리의 조건에 따라 기본적으로 변하더라도, Cu-Ti 화합물막(108b)의 Cu 함유량은 높다. Cu-Ti 비율이 2:1과 3:2 사이에 Cu-Ti 합금 타겟으로 조성을 선택하는 것이 양호하다.

제1 Ti막(106)은 Si0₂막(104)와 TiN막(107a)와의 밀착성을 향상시키기 위해 제공된다. TiN막(107a)는 일렉트로 미그레이션 또는 스트레스 미그레이션 면역과 같은 최종 배선의 장기간 신뢰성을 보장하기 위해 제공된다.

다음에, 0.01-0.1 wt %함유량으로 Zr, Ag, Sn 및 Sb을 구성하는 그룹에서 선택되 적어도 하나의 금속을 포함하는 400 nm 두께의 Cu 합금막(109a)는 제8b도에 도시된 바와 같이 DC 마그네트론 스퍼터링법으로 형성된다. Cu 막 내로 Zr, Ag, Sn 및/또는 Sb의 추가는 Cu막의 기계적 강도, 열적 안정성 및 산화 내성을향상시키는 것으로, 추가 성분의 기능은 제1 실시예의 경우와 유사하다.

Cu-Ti 금속간 화합물층(108b) 내의 Cu 함유량이 상술한 바와 같이 높기 때문에, Cu-Ti 화합물층(108b)는 높은 열적 내성 및 900 ℃의 융점을 갖는다. 따라서, Cu-Ti 화합물층(108b)는 Cu 합금막(109a)와 TiN막 (107a)와의 밀착층으로서 뿐만 아니라 이들 두 막 사이의 Cu확산에 대한 배리어층으로서 작용한다. 따라 서, 높은 열적 내성 및 우수한 밀착성은 고수된다. 결과적으로, TiN막의 사이 드 에치 및 필링 오프는 제2 실시예에서도 피해진다.

제8c도는 Si₃N₄ 마스트 페턴(110a)를 형성한 후의 배선 구조를 도시하고 있다. 먼저, 300 -500 nm 두께의 Si₃N₄막은 기판 온도가 300 ℃와 350 ℃사이이고, 반응 압력이 0.2-0.4 Torr이며, SiH₄ 유량이 150과 300 sccm 사이이고, Nh₃ 유량이 400과 800 sccm 사이이며, RF 전원이 0.5-1.5 kW인 조건에서 소스 가스로서 SiH₄와 Nh₃을 사용하여 PE-CVD법으로 Cu 합금막(109a) 상에 형성된다. 계속해서, SiH₄막은 패턴화되어 마스크 패턴(110a)를 형성한다. Si₃N₄ 마스크 패턴(110a) 두께는 고려되는 Si₃N₄막에 대한 적층 도전층의 에치 선택으로 결정된다.

다음에, Cu 합금막(109a), Cu—Ti 화합물층(108b), TiN막(107a) 및 Ti막(106)을 포함하는 적층은 기판 온도가 약 280 ℃이고, 반응 압력이 2 Pa이며, SiCl₄ 유량이 약 20 sccm이고, Cl₂ 유량이 약 20 sccm이며, NH₃의 유량을 10과 30 sccm 사이이고, N₂ 유량이 약 80 sccm 이며, RF 전원이 300 W인 조건하에서 반응 가스로서 SiCl₄, Cl₂ 및 NH₃ 및 희석 가스로서 N₂를 사용하는 RIE법으로 배선 구조를 형성하기 위해 패턴화된다. 그 다음, Cu 합금막(109a) 상에 남아 있는 Si₃N₄ 마스크 패턴(110a)는 SiO₂막(104)에 대한 Si₃N₄ 마스크 패턴(110a)의 선택이 SiO₂막(104)의 거의 제로 에치를 얻기에 충분할 정도로 큰 조건하에서 RIE법을 사용하여 제거됨으로써, 제8d도에 도시된 바와 같이 중간 구조를 얻는다.

우수한 밀착성은 Cu-Ti 화합물막(108b)와 TiN막(107a) 사이 뿐만 아니라 Cu 합금막(109a)와 Cu-Ti 화합물막(108b) 사이에서 보장된다. 따라서, TiN막(107a)의 사이드 에칭 및 Cu 합금막(109a)로부터의 필링 오프

는 Cu 합금막(109a)용의 RIE 단계동안 발생하지 않는다. 결과적으로, Cu막과 TiN막과의 밀착을 향상시키기 위해 W막과 같은 추가층을 제공할 필요가 없어. 배선 구조 및 이것의 제조 단계를 단순화할 수 있다.

계속해서, 약 20 nm 두께의 W막(111)은 제8e도에 도시된 바와 같이 배선 표면을 야금학적으로 안정화하기 하기 위해 여분의 H₂를 이용하여 선택 W-CVD법으로 배선의 표면에만 형성한다. 이것은 높은 선택성 및 높은 균일성을 갖고 있는 W막(111)을 형성하기 앞서 2가지 전처리를 필요로 한다. 전 처리의 목적 및 절차는 제1 실시예와 유사하다.

선택 W-CVD법은 기판 온도가 350-400 ℃이고, 반응 압력이 20-80 mTorr이며, WF<sub>6</sub> 유량이 0.5와 1 sccm 사이이고, H₂ 유량이 200-400 sccm 사이인 조건하에서 처리된다. 따라서, 형성된 W막은 SiO₂막(104)의 표면적에 대한 배선 표면의 노출 비율에 따라 5-7 nm/min 정도의 비교적 작은 성장율을 나타낸다. 작은 성장률은 W막(111)의 두께를 제어하기에 적절하다.

제2 실시예에 따라 형성된 배선 구조는 Cu-Ti 금속간 화합물층을 제공하여, Cu 합금막과 TiN막 사이의 밀착성을 향상시킬 수 있다. 게다가, 순수한 Cu막 보다 높은 기계적 강도 및 열적 내성을 갖고 있는 Cu 합금막은 배선의 기계적 및 열적 강도를 향상시킨다. 더우기, 배선 표면은 산화 및 부식으로부터 선택 W-CVD막을 보호한다. 결과적으로, 배선의 장기 신뢰성은 본 발명에 의해 얻어진다.

제2 실시예에 있어서, Cu-Ti 화합물층은 Cu-Ti 합금을 스퍼터 증착 및 어닐링으로 형성된다. 그러나, Cu-Ti 화합물층은 Cu-Ti 화합물 타겟을 스퍼터링으로 형성될 수 있다.

본 발명은 양호한 실시예에 대해 상세히 설명되었지만, 본 분야에 숙련된 기술자들이라면 본 발명의 범위를 벗어나지 않고서 양호한 실시예를 여러 가지로 변형 및 변경시킬 수 있다.

#### (57) 청구의 범위

#### 청구항 1

반도체 기판; 상기 기판윈 절연막; 및 Ti막, TiN막, Ti-Cu 화합물막 및 Cu 및 Cu외에 미량의 적어도 하나의 금속 성분을 포함하는 Cu 합금막을 포하하고, 상기 막들은 적어도 상기 절연막 상에 연속적으로 형성되는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 2

제1항에 있어서, 상기 금속 배선은 상기 절연막을 관통하는 비아 플러그를 갖고 있고, 상기 비아 플러그는 상기 반도체 기판과 옴 접촉을 형성하는 것을 특징으로 하는 반도체 디바이스.

#### 청구한 3

제1항에 있어서, 상기 배선은 상기 적층 구조를 피복하는 W막을 더 포함하는 것을 특징으로 하는 반도체디바이스.

#### 청구항 4

제1항에 있어서, 상기 적어도 하나의 금속 성분은 Zr, Ag, Sn 및 Sb를 구성하는 그룹에서 선택되는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 5

제1항에 있어서, 상기 미량은 0.01과 0.5 wt % 사이인 것을 특징으로 하는 반도체 디바이스.

#### 청구항 6

제1항에 있어서, 상기 Cu-Ti 화합물막은 원자 비율이 Cu:Ti = 5:1과 Cu-Ti = 1:2 범위 사이의 Cu 및 Ti를 포함하는 것을 특징으로 하는 반도체 디바이스.

#### 청구항 7

반도체 기판 위에 있는 절연막을 형성하는 단계; 상기 절연막 상에 Ti막을 형성하는 단게; 상기 Ti막 상에 TiN막을 형성하는 단계; 상기 Cu-Ti 화합물막, 및 Cu와 미량의 적어도 하나의 금속 성분을 포함하는 Cu 합금막을 형성하는 단계를 포함하되, 상기 Cu-Ti 화합물막 및 Cu 합금막은 상기 TiN막 상에 연속적으로 적층되고; 배선 패턴을 형성하기 위해 상기 Cu 합금막, 상기 Cu-Ti 화합물막, 상기 TiN막 상기 Ti막을 패터닝하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 형성 방법.

#### 청구항 8

제7항에 있어서, W막을 갖고 있는 상기 배선 패턴을 피복하는 단계를 더 포함하는 것을 특징으로 하는 반도체 디바이스 형성 방법.

#### 청구항 9

제7항에 있어서, 상기 Cu-Ti 화합물막 및 상기 Cu 합금막을 형성하는 상기 단계는 상기 TiN막 상에 Ti층 및 Cu 합금층을 연속적으로 피착하는 단계 및 상기 Cu-Ti 금속간 화합물막을 형성하기 위해 상기 Ti층 및 상기 Cu 합금층을 열처리하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 형성 방법.

#### 청구항 10

제7항에 있어서, 상기 Cu-Ti 화합물막 및 상기 Cu 합금막을 형성하는 상기 단계는 Cu-Ti 합금막 및 Cu 합금막을 연속적으로 피착하고, 상기 Cu-Ti 화합물막을 형성하기 위해 상기 Cu-Ti합금막을 열 처리함으로써

행해지는 것을 특징으로 하는 반도체 디바이스 형성 방법.

#### 청구항 11

제7항에 있어서, 상기 Ti-Cu 화합물막 및 상기 Cu 합금막을 형성하는 상기 단계는 Cu-Ti 화합물 타겟 및 Cu 합금 타겟을 연속적으로 스퍼터링함으로써 행해지는 것을 특징으로 하는 반도체 디바이스 형성 방법.

#### 도면

#### 도면1a

#### 도면1b

#### 도면1c

#### 도면2a

## 도면2b

## 도면3a

## 도면3b

## 도면3c

도면4a

#### 도면4b

## 도면4c

## 도면4d

## 도면5a

#### 도면5b

#### 도면5c

## *도면5d*

## 도면6a

## *도면6*b

## 도면7a

*도면7*b

## 도면7c

## 도면7d

## *도면7e*

## 도면7f

## 도면8a

## 도면8b

## 도면8c

## 도면8d

도면8e