(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4669679号 (P4669679)

(45) 発行日 平成23年4月13日(2011.4.13)

(24) 登録日 平成23年1月21日(2011.1.21)

(51) Int.Cl. F L

**HO1L 21/318 (2006.01)** HO1L 21/318 B **HO1L 29/78 (2006.01)** HO1L 29/78 3O1G

請求項の数 9 (全 17 頁)

(21) 出願番号 特願2004-221490 (P2004-221490)

(22) 出願日 平成16年7月29日 (2004. 7. 29) (65) 公開番号 特開2006-41337 (P2006-41337A)

(43) 公開日 平成18年2月9日 (2006.2.9) 審査請求日 平成19年2月9日 (2007.2.9) ||(73)特許権者 000219967

東京エレクトロン株式会社 東京都港区赤坂五丁目3番1号

||(74)代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 星 岳志

茨城県つくば市小野川16番地1 株式会

社半導体先端テクノロジーズ内

|(72)発明者 斎藤 豪|

茨城県つくば市小野川16番地1 株式会

社半導体先端テクノロジーズ内

(72) 発明者 加藤 寿

東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内

最終頁に続く

(54) 【発明の名称】 窒化珪素膜の製造方法及び半導体装置の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

基体の表面に窒化珪素膜を形成する窒化珪素膜の製造方法であって、

珪素と塩素とを含む第1のガスを前記基体の表面に供給し、前記第1のガスに含まれる前記珪素と前記塩素とを含む第1の被膜を前記基体上に形成する第1の工程と、

窒素を含む第2のガスを前記第1の被膜の表面に供給し、前記第1の被膜に含まれる前記珪素と前記塩素と、前記第2のガスに含まれる前記窒素と、を含む第2の被膜を前記基体上に形成する第2の工程と、

活性化した水素を含む第3のガスを前記第2の被膜の表面に供給し、前記第2の被膜から前記塩素を取り除き、第3の被膜を形成する第3の工程と、

をこの順に繰り返すことを特徴とする窒化珪素膜の製造方法。

## 【請求項2】

前記水素は、原子状及びラジカルの少なくともいずれかに活性化してなることを特徴と する請求項1記載の窒化珪素膜の製造方法。

### 【請求項3】

前記窒素は、活性化してなることを特徴とする請求項1<u>または2に</u>記載の窒化珪素膜の 製造方法。

### 【請求項4】

前記活性化は、プラズマにより生じてなることを特徴とする請求項<u>1~3</u>のいずれか1つに記載の窒化珪素膜の製造方法。

#### 【請求項5】

前記活性化は、触媒及び紫外線の少なくともいずれかにより生じてなることを特徴とする請求項1~3のいずれか1つに記載の窒化珪素膜の製造方法。

#### 【請求項6】

前記第1の工程と前記第2の工程との間に、前記基体の表面から前記第1のガスを除去する工程を実施し、

前記第2の工程と前記第3の工程との間に、前記基体の表面から前記第2のガスを除去する工程を実施することを特徴とする請求項1~<u>5</u>のいずれか1つに記載の窒化珪素膜の製造方法。

## 【請求項7】

シリコン基板と、前記シリコン基板の上に設けられた窒化珪素膜と、を有する半導体装 置の製造方法であって、

前記室化珪素膜を請求項1~<u>6</u>のいずれか1つに記載の室化珪素膜の製造方法により製造することを特徴とする半導体装置の製造方法。

## 【請求項8】

半導体層と、前記半導体層の主面上に選択的に設けられたゲート絶縁膜と、前記ゲート 絶縁膜の上に設けられたゲート電極と、を有する基体を形成する工程と、

前記基体の上に、請求項1~<u>6</u>のいずれか1つに記載の窒化珪素膜の製造方法により窒化珪素膜を製造する工程と、

前記半導体層の前記主面に対して略垂直方向に前記室化珪素膜をエッチングすることにより、前記半導体層及び前記ゲート電極の上の前記室化珪素膜を除去し、前記ゲート絶縁膜及びゲート電極の側面に前記室化珪素膜からなる側壁を残留させる工程と、

を備えたことを特徴とする半導体装置の製造方法。

#### 【請求項9】

半導体層の上に、請求項1~<u>6</u>のいずれか1つに記載の窒化珪素膜の製造方法により窒化珪素膜を製造する工程と、

前記室化珪素膜の上に層間絶縁層を形成する工程と、

前記層間絶縁層の上に開口を有する層を形成する工程と、

前記室化珪素膜に対するエッチング速度よりも前記層間絶縁層に対するエッチング速度のほうが大なる条件で、前記開口を介して前記層間絶縁層をエッチングする工程と、

を備えたことを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は、窒化珪素膜の製造方法及び半導体装置の製造方法に関し、特に、LP-CVD(Low Pressure-Chemical Vapor Deposition)法による窒化珪素膜の製造方法及びこの方法を備えた半導体装置の製造方法に関する。

#### 【背景技術】

#### [00002]

半導体装置のゲート電極のサイドウォールやライナー膜などを形成する目的で、LP-CVD法により窒化珪素膜が成膜される。ところが、この場合に、原料としてSiH $_2$  С  $1_2$  , SiС $1_4$  , Si $_2$  С  $1_6$ 等のシリコン原料とNH $_3$  とを用いると、シリコン原料に含まれる塩素およびNH $_3$  に含まれる水素が、成膜された膜中に不純物として残留する。この現象は、低温、例えば600 以下での成膜では特に顕著となり、窒化膜の密度の低下やウェットエッチ耐性の低下などの問題が起こる。

## [0003]

これに対して、Si/N比を一定に維持しつつ不純物含有量を少なくすること等を目的として、 $Si_2Cl_6$ およびNH $_3$ を用いた原子層蒸着 (atomic layer deposition: ALD)による窒化珪素膜形成手法が提案されている。

#### [0004]

50

10

20

30

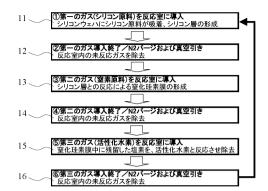

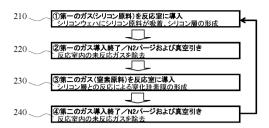

図 1 5 は、本発明者が本発明に至る過程で検討した窒化珪素膜の形成手法を表すフローチャートである。

すなわち、この方法の場合、第1の工程110として、反応室内のシリコンウェーハ上に、SiH,Cl,,Si,Cl,等の塩素を含むシリコン原料のガスを導入する。

次に、第2の工程120として、窒素ガスを導入し反応室内の未反応ガスを置換する。

次に、第3の工程130として、活性化した窒素原料のガスを反応室内に導入する。

次に、第4の工程140として、窒素ガスを導入し反応室内の未反応ガスを置換する。

## [0005]

この手法により、通常の L P C V D による室化珪素膜と比較して塩素不純物量の少ない膜を形成することが可能である(例えば、特許文献 1 参照)。

【特許文献1】特開2002-343793号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

しかし、半導体装置のゲート電極のサイドウォールやライナー膜として窒化膜を使用する場合、低サーマルバジェット実現のためには、成膜温度が500 以下、例えば成膜温度450 で、膜質が良好でありかつ被覆率の高い窒化膜の成膜方法が必要である。これに対して、これまでの成膜方法によると、成膜温度の低下とともに膜中の不純物量が増加してしまい、ウェットエッチ耐性などの点で膜質が劣化する問題がある。

[0007]

例えば、ダマシンゲートプロセスによりメタルゲート電極を有する半導体装置を作成する場合、ライナー膜を窒化珪素膜により形成した後、HF溶液による洗浄工程が必要となる。従来技術にて成膜温度 5 0 0 以下にて成膜した窒化膜では、HF溶液によるエッチング量が大きいため、目的とする構造の形成が難しい。

[00008]

本発明は、かかる課題の認識に基づいてなされたものであり、その目的は、窒化珪素膜の塩素不純物量の低減を実現し、ウェットエッチ耐性の高い窒化珪素膜の形成を可能とした窒化珪素膜の製造方法及びこの製造方法を備えた半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

[0009]

上記目的を達成するために、本発明の一態様によれば、基体の表面に窒化珪素膜を形成する窒化珪素膜の製造方法であって、珪素と塩素とを含む第1のガスを前記基体の表面に供給し、前記第1のガスに含まれる前記珪素と前記塩素とを含む第1の被膜を前記基体上に形成する第1の工程と、窒素を含む第2のガスを前記第1の被膜の表面に供給し、前記第2のガスに含まれる前記窒素と、を含む第2の被膜を前記基体上に形成する第2の工程と、活性化した水素を含む第3のガスを前記第2の被膜の表面に供給し、前記第2の被膜から前記塩素を取り除き、第3の被膜を形成する第3の工程と、をこの順に繰り返すことを特徴とする窒化珪素膜の製造方法が提供される。

[0010]

ここで、前記水素は、活性化してなることを特徴とする。

また、前記水素は、原子状及びラジカルの少なくともいずれかに活性化してなることを 特徴とする。

また、前記窒素は、活性化してなることを特徴とする。

またここで、前記活性化は、プラズマにより生じてなることを特徴とする。

または、前記活性化は、触媒及び紫外線の少なくともいずれかにより生じてなることを 特徴とする。

[0011]

また、前記第1の工程と前記第2の工程との間に、前記基体の表面から前記第1のガス

10

20

30

40

を除去する工程を実施し、

前記第2の工程と前記第3の工程との間に、前記基体の表面から前記第2のガスを除去する工程を実施することを特徴とする。

### [0012]

一方、本発明の他の一態様によれば、シリコン基板と、前記シリコン基板の上に設けられた窒化珪素膜と、を有する半導体装置の製造方法であって、

前記室化珪素膜を上記のいずれかの窒化珪素膜の製造方法により製造することを特徴とする半導体装置の製造方法が提供される

または、本発明のさらに他の一態様によれば、半導体層と、前記半導体層の主面上に選択的に設けられたゲート絶縁膜と、前記ゲート絶縁膜の上に設けられたゲート電極と、を有する基体を形成する工程と、

前記基体の上に、上記のいずれかの窒化珪素膜の製造方法により窒化珪素膜を製造する 工程と、

前記半導体層の前記主面に対して略垂直方向に前記室化珪素膜をエッチングすることにより、前記半導体層及び前記ゲート電極の上の前記室化珪素膜を除去し、前記ゲート絶縁膜及びゲート電極の側面に前記室化珪素膜からなる側壁を残留させる工程と、

を備えたことを特徴とする半導体装置の製造方法が提供される。

### [0013]

また、本発明のさらに他の一態様によれば、半導体層の上に、上記のいずれかの窒化珪素膜の製造方法により窒化珪素膜を製造する工程と、

前記室化珪素膜の上に層間絶縁層を形成する工程と、

前記層間絶縁層の上に開口を有する層を形成する工程と、

前記室化珪素膜に対するエッチング速度よりも前記層間絶縁層に対するエッチング速度のほうが大なる条件で、前記開口を介して前記層間絶縁層をエッチングする工程と、

を備えたことを特徴とする半導体装置の製造方法が提供される。

### 【発明の効果】

### [0014]

本発明によれば、窒化珪素膜の塩素不純物量の低減を実現し、ウェットエッチ耐性を向上できる。すなわち、本発明によれば、サーマルバジェットが低く、Si/N比が一定で、不純物量の少ない窒化珪素膜が得られ、従来技術よりも更に塩素不純物量を減少させることにより、ウェットエッチ耐性などの膜質を向上できる。

## [0015]

例えば、ダマシンゲートプロセスによりメタルゲート電極を有する半導体装置を作成する場合、ライナー膜を窒化膜にて形成した後、HF溶液による洗浄工程が必要となる。従来技術にて成膜温度500 以下にて成膜した窒化膜ではHF溶液によるエッチング量が大きいため、目的とする構造の形成が難しい。これに対して、本発明によればHF溶液によるエッチング量の小さい良質な窒化膜を形成することが可能なため、製造プロセス上の問題を回避し、かつ電気的特性を向上させることができる。

すなわち、本発明によれば、窒化珪素膜の塩素不純物量の低減を実現し、ウェットエッチ耐性を向上することが可能となり、産業上のメリットは多大である。

【発明を実施するための最良の形態】

#### [0016]

以下、図面を参照しつつ本発明の実施の形態について説明する。

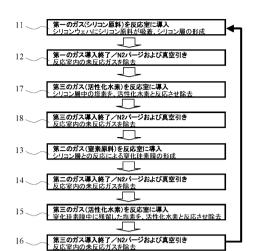

図1は、本発明の実施の形態にかかる窒化珪素膜の製造方法を表すフローチャートである。すなわち、本具体例は、LPCVD法により窒化珪素膜を成膜する方法を例示する。

## [0017]

まず、第1の工程11として、反応室内に配置されたシリコンウェーハなどの基体上に、珪素と塩素とを含む原料ガスを導入する。このような原料ガスとしては、例えば、SiH $_2$  С  $1_2$  , S  $i_2$  C  $1_6$  等を挙げることができる。以降、これらの原料ガスを「第1のガス」とする。

10

20

30

40

#### [0018]

次に、第2の工程12として、窒素ガスを導入し反応室内の未反応ガスを置換する。 次に、第3の工程13として、窒素を含む原料ガスを反応室内に導入する。以後、窒素 を含む原料ガスを「第2のガス」とする。

次に、第4の工程14として、窒素ガスを導入し反応室内の未反応ガスを置換する。 次に、第5の工程15として、活性化した水素を含む原料ガスを反応室内に導入する。 以後、活性化した水素を含む原料ガスを「第3のガス」とする。

最後に、第6の工程16として、窒素ガスを導入し反応室内の未反応ガスを置換する。

### [0019]

以上説明した第1~第6の工程を一周期とし、この周期を所望の膜厚に達するまで繰り返すことによって、塩素濃度の低い窒化珪素膜を形成する。一周期は、例えば約30秒間程度とすることができる。

#### [0020]

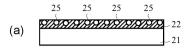

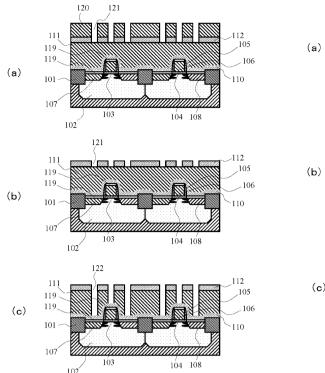

図 2 は、本発明の実施の形態にかかる半導体装置の製造方法を説明する工程断面図である。

図 2 ( a )は、図 1 に関して前述した第 1 の工程 1 1 におけるシリコンウェーハの断面構造を例示する模式図である。すなわち、第 1 のガス(SiH $_2$  С 1  $_2$  、Si $_2$  С 1  $_6$  等の塩素を含むシリコン原料のガス)を反応室に導入することによって、シリコンウェーハ 2 1 上に、シリコンと塩素 2 5 とを含む層 2 2 が形成される。

## [0021]

図2(b)は、図1に関して前述した第3の工程13におけるシリコンウェーハの断面構造を例示する模式図である。すなわち、第2のガス(窒素を含む原料ガス)を反応室に導入することによりシリコンと窒素とが結合し、塩素25を含む窒化珪素薄膜23が形成される。なおここで、シリコンと窒素との結合を促進するために、窒素をラジカルあるいは原子状などの活性化した状態にして供給してもよい。

### [0022]

図2(c)は、図1に関して前述した第5の工程15におけるシリコンウェーハの断面構造を例示する模式図である。第3のガス(活性化した水素を含む原料ガス)を反応室内に導入することにより、塩素25の含有量が低減された窒化珪素薄膜23が形成される。すなわち、活性化した水素原料のガスを導入することにより、活性化した水素26と残留した塩素25とが反応化合物を形成し、膜から取り除かれる。その結果、窒化珪素薄膜23内の含有塩素量が低減される。

## [0023]

なお、図2には、説明の便宜上、平坦なシリコンウェーハ21の上に窒化珪素膜を形成する場合を例示したが、シリコンウェーハ21の表面にはトランジスタなどの構造が形成されていてもよく、またシリコンウェーハの代わりにSOI(semiconductor on insulator)基板などの各種の基板を用いることができる。

### [0024]

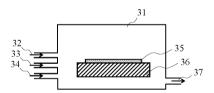

図3は、本発明の実施の形態にかかる窒化珪素膜の製造方法に用いることができる反応室を例示する模式図である。すなわち、同図は、LPCVD装置の反応室を例示する。

反応室 3 1 内において、ウェーハステージ 3 6 上にシリコンウェーハ 3 5 が載置可能とされている。反応室 3 1 の側壁には、第 1 のガス(S i H  $_2$  C 1  $_2$  , S i  $_2$  C 1  $_6$  などのシリコンと塩素とを含む原料ガス)を導入するためのインジェクター 3 2 と、第 2 のガス(N H  $_3$  などの窒素を含む原料ガス)を導入するためのインジェクター 3 3 と、第 3 のガス(活性化した水素原料のガス)を導入するためのインジェクター 3 4 と、真空ポンプに接続されている排気口 3 7 とが設けられている。

### [0025]

活性化した水素は、例えば、リモートプラズマ発生装置としてRFジェネレータにて13.56MHz(メガヘルツ)の高周波を800W(ワット)印加することにより生成できる。または、水素を触媒に接触させたり、紫外線を照射することによっても活性化でき

10

20

30

40

る。触媒としては、例えば、タングステン、白金、パラジウム、モリブデン、タンタル、チタン、チタン酸化物、バナジウム、シリコン、アルミナ、炭化珪素、金属蒸着セラミックスなどを挙げることができる。また、光触媒の原理を利用して水素を活性化させてもよい。

紫外線により水素を活性化させる場合、紫外線の波長は概ね400ナノメータ以下とすると効率的である。

このようにして水素を活性化した後、反応室31に導入する。

## [0026]

また、窒素を含む第 2 のガスとしては、例えば、N H  $_3$  を用いることができる。また、第 2 のガスとして、活性化した窒素を含むガスを導入してもよい。この場合もプラズマを利用して窒素を活性化できる。

成膜条件としては、例えば温度 4 5 0 、圧力 1 3 0 P a (パスカル)、 S i  $_2$  C l  $_6$  流量 1 0 c c 、 N H  $_3$  流量 1 0 0 0 c c 、 H  $_2$  流量 1 0 0 0 c c にて実施することができる。

## [0027]

活性化した水素原料のガスとしては、水素ラジカルや原子状水素などを含むガスを挙げることができる。例えば、プラズマや触媒あるいは紫外線照射などより水素分子を分解させると、不対電子を持つ水素原子が得られる。この水素原子は反応性が高く、活性である

## [0028]

また、窒素を含む第2のガスとしては、 $NH_3$ 以外にも、アミン系のガスなどを用いることができ、例えばヒドラジンを用いることができる。

### [0029]

本実施形態によれば、上記した工程を経ることにより、塩素含有量の低い窒化珪素膜を低温で成膜できる。低温で成膜させることにより、製造工程途中の半導体装置に余分な熱を加えることなく、窒化膜の膜質を改善し、半導体装置の信頼性を向上する効果が得られる。

## [0030]

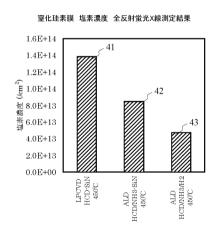

図4は、窒化珪素膜中の塩素濃度を全反射蛍光X線法により測定した結果を表すグラフ図である。

すなわち、 $Si_2Cl_6$ および $NH_3$ の2種類のガスを同時に導入して成膜した第1の比較例の窒化珪素膜41と、第1のガス: $Si_2Cl_6$ 、第2のガス:活性化した $NH_3$ を交互に導入し、これを繰り返すことにより成膜した第2の比較例の窒化珪素膜42と、本発明による第1のガス: $Si_2Cl_6$ 、第2のガス:活性化した $NH_3$ に続いて、第3のガス:活性化した水素を導入し、これを繰り返すことにより成膜した窒化珪素膜43の3種の膜について比較した。

## [0031]

## [0032]

図 5 は、HF溶液に対するエッチング量の評価を行った結果を示すグラフ図である。DHF(希フッ酸)0.5%溶液に対するウェットエッチレート(対  $SiO_2$ 比)は、通常のLPCVDにて成膜した第 1 比較例の窒化珪素膜 4 1 で 1 9.7、第 2 比較例の窒化珪素膜 4 2 で 8.5 であったのに対し、本発明の方法で成膜した窒化珪素膜 4 3 では 4.7 であった。すなわち、第 1 比較例の窒化珪素膜 4 1 と比較して約 4.2 倍、第 2 比較例の窒化珪素膜 4 2 と比較して約 1.8 倍、ウェットエッチ耐性を向上させることが可能とな

20

10

30

40

った。

### [0033]

次に、本発明の窒化珪素膜の製造方法を備えた半導体装置の製造方法について説明する

## [0034]

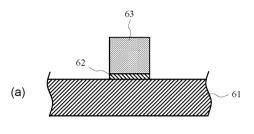

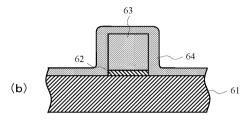

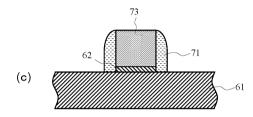

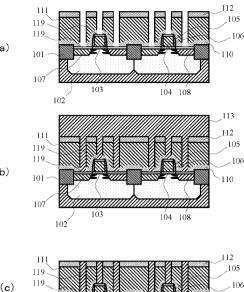

図6は、本発明の実施の形態にかかる半導体装置の製造方法を例示する工程断面図である。すなわち、本具体例は、ゲート側壁の形成工程を表す。

まず、図6(a)に表したように、シリコン基板61の上に、ゲート絶縁膜62を介してゲート電極63を形成する。

次に、図6(b)に表したように、これらの上に、窒化珪素膜64を形成する。この時に図1乃至図3に関して前述したような本発明の方法により形成する。

#### [0035]

次に、図6(c)に表したように、窒化珪素膜64をドライエッチングによって加工してサイドウォール71を形成する。すなわち、RIE(reactive ion etching)などの異方性の高いエッチング方法によりシリコン基板61の主面に対して略垂直方向からエッチングすると、ゲート絶縁膜62及びゲート電極73の側面のみに窒化珪素膜が残り、サイドウォール71として形成される。このサイドウォール71は、本発明の実施の形態にかかる製造方法によって成膜されているので、膜中の塩素濃度は低減されている。

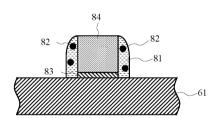

#### [0036]

図 7 は、前述した比較例 1 あるいは比較例 2 の窒化珪素膜を設けた半導体装置の断面構造を例示する模式図である。すなわち、シリコン基板 6 1 の上に、ゲート絶縁膜 8 3 を介してゲート電極 8 4 が設けられていて、ゲート電極 8 4 の側面をサイドウォール 8 1 が覆っている。このサイドウォール 8 1 は、比較例の方法により  $Si_2Cl_6$ と $NH_3$ を用いて成膜したので、膜中の塩素 8 2 の濃度が高い。

#### [0037]

本発明におけるサイドウォール 7 1 と比較して、比較例のサイドウォール 8 1 は、膜中の塩素 8 2 の濃度が高く、例えば、ゲート絶縁膜 8 3 やゲート電極 8 4 に対して塩素が拡散することにより、半導体装置の信頼性を低下させる懸念がある。これに対して、本発明におけるサイドウォール 7 1 では、残留する塩素の含有量を低減していることにより、例えばゲート絶縁膜 7 2 やゲート電極 7 3 に対する不純物拡散量を抑制することができるため、半導体装置の信頼性を向上する効果が得られる。

## [0038]

本発明は、半導体装置のサイドウォールのみならず、その他、例えば、窒化珪素膜からなるゲート絶縁膜やライナー膜(エッチングストッパ膜)の形成に用いても、含有塩素濃度を低減させた良質の膜を低温で形成できる点で有利な効果が得られる。

#### [0039]

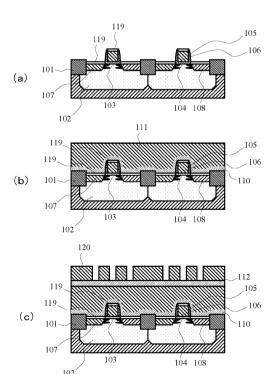

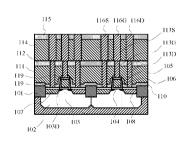

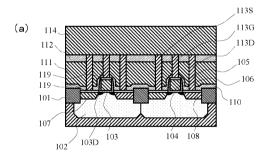

図8は、本発明により製造される半導体装置の要部断面構造を例示する模式図である。 すなわち、同図は、半導体集積回路を構成するMOSFET (Metal Oxide Semiconduc tor Field Effect Transister)の要部断面構造を表す。

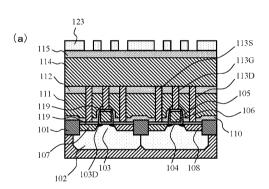

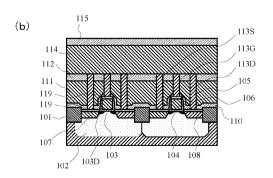

### [0040]

シリコン基板の表面部分が素子分離領域101により絶縁分離され、これら分離されたウエル102のそれぞれにMOSFETが形成されている。それぞれのMOSFETは、ソース領域107、ドレイン領域108と、これらの間に設けられたチャネル103と、を有する。チャネル103の上には、ゲート絶縁膜104を介してゲート電極106が設けられている。ソース・ドレイン領域107、108とチャネル103との間には、いわゆる「ショートチャネル効果」などを防ぐ目的で、LDD(lightly doped drain)領域103Dが設けられている。そして、これらLDD領域103Dの上には、ゲート電極106に隣接してゲート側壁105が設けられている。ゲート側壁105は、LDD領域103Dをセルフアライン(自己整合)的に形成するために設けられている。

## [0041]

50

20

10

30

10

20

30

40

50

また、ソース・ドレイン領域107、108とゲート電極106の上には、電極とのコンタクトを改善するためにシリサイド層119が設けられている。これら構造体の上は、第1の層間絶縁膜110と第2の層間絶縁膜111と第3の層間絶縁膜112により覆われ、これらを貫通するコンタクトホールを介して、ソースコンタクト113S、ゲートコンタクト113G、ドレインコンタクト113Dが形成されている。ここで、第1の層間絶縁膜110と第3の層間絶縁膜112は、例えば、窒化珪素により形成され、第2の層間絶縁膜111は、例えば、酸化シリコンにより形成することができる。

## [0042]

さらに、この上に、第4の層間絶縁膜114と第5の層間絶縁膜115が形成されている。そして、これらを貫通するトレンチにソース配線1165、ゲート配線116G、ドレイン配線116Dがそれぞれ埋め込み形成されている。ここで、第4の層間絶縁膜1140酸化シリコンにより形成され、第5の層間絶縁膜115は、窒化珪素により形成することができる。

## [0043]

以上説明したような半導体装置を製造するに際し、本発明によれば、ゲート側壁105のみならず、ゲート絶縁膜104、第1の層間絶縁膜110、第3の層間絶縁膜112、第5の層間絶縁膜115などを構成する窒化珪素膜を、図1乃至図3に関して前述した本発明により形成できる。

#### [0044]

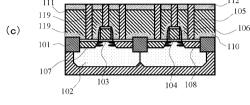

図 9 乃至図 1 3 は、本発明の実施の形態にかかる半導体装置の製造方法を表す工程断面図である。

まず、図9(a)に表したように、MOSトランジスタの要部を形成する。すなわち、Si基板上に素子分離領域101、ウェル102、チャネル103、ゲート絶縁膜104、ゲート電極106、LDD注入サイドウォール(ゲート側壁)105を順次形成し、ソース領域107、ドレイン領域108の形成を行う。さらに、ニッケル(Ni)のスパッタ、RTP(rapid thermalprocessing)を順次行い、ニッケルシリサイドからなるシリサイド層119を形成する。

ここで、ゲート絶縁膜104を形成する工程において、図1及び図2に関して前述した方法により窒化珪素膜を形成することができる。また、この時、ゲート絶縁膜104は、単一の窒化珪素膜には限定されず、例えば、酸化珪素やhigh-k(高誘電率)材料からなる膜と、窒化珪素膜と、の積層構造とすることができる。この場合には、窒化珪素膜について図1及び図2に関して前述した方法を実施することができる。

また、ゲート側壁105を形成する工程についても、図6に関して前述したように、本発明の窒化珪素膜の製造方法を用いることができる。

### [0045]

次に、図9(b)に表したように、第1の層間絶縁膜110及び第2の層間絶縁膜111を形成する。ここで、第1の層間絶縁膜110として、図1乃至図3に関して前述したように本発明の製造方法により厚みが50nm程度の窒化珪素膜を形成する。この時、ニッケルシリサイドからなる下地のシリサイド層119のコンタクト抵抗の上昇を防ぐためには、窒化珪素膜の成膜時の温度を500以下に抑えることが望ましい。これに対して、本発明によれば、例えば450程度の低温でも膜質が良好で、且つ、塩素の含有量の少ない窒化珪素膜を形成できる。

## [0046]

このように第1の層間絶縁膜110として室化珪素膜を形成した後に、第2の層間絶縁膜111として、TEOS(tetra ethoxy silane)ガスを用い、プラズマCVDにより 6 0 0 において厚みが600nmのシリコン酸化膜を形成する。

また、第2の層間絶縁膜111の材料として、さらに誘電率の低い材料を用いることができる。そのような材料としては、メチル基を有するシリコン酸化物や、水素基を有するシリコン酸化物、有機ポリマーなど用いることができる。さらに具体的には、例えば、多孔質のメチルシルセスキオキサン (methyl silsequioxane: MSQ) などの各種のシルセ

スキオキサン化合物、ポリイミド、炭化フッ素(fluorocarbon)、パリレン(parylene)、ベンゾシクロブテンなどを挙げることができる。また、その形成方法としては、例えば、溶液をスピンコートし熱処理して薄膜を形成するスピン・オン・グラス(spin on glass:SOG)法を用いることができる。

## [0047]

このように第2の層間絶縁膜111を形成した後に、図9(c)に表したように、この上に第3の層間絶縁膜112として、窒化珪素膜を形成する。この時にも、本発明の製造方法により、例えば成膜温度を450 にして厚み120nm程度の窒化珪素膜を形成することができる。成膜温度を低く抑えることにより、シリサイド層119を構成するニッケルシリサイドの変質を防ぐことができる。

その後、レジストを塗布してパターニングすることにより、レジストパターン120を 形成する。レジストパターン120は、例えば、ArF露光機を用いて120nm径に露 光することにより形成する。

## [0048]

次に、図10(a)に表したように、レジストパターン120をマスクとして第3の層間絶縁膜112のエッチングを行う。エッチング方法としては、例えば、ICP(induct ion coupled prasma)型反応性イオンエッチング装置を用いることができる。第3の層間絶縁膜112のエッチングに際しては、例えば、CH<sub>2</sub>F<sub>2</sub>:50sccm О<sub>2</sub>:50sccm の混合ガスを用いて6.7パスカル(Pa)にてエッチングすることにより、層間絶縁膜112に開口部121を形成することができる。

#### [0049]

次に、図10(b)に表したように、酸素プラズマによるアッシングを実施してレジストマスク120を除去する。

#### [0050]

## [0051]

この時に、シリコン窒化膜からなる第3の層間絶縁膜112をエッチングマスクして用いることにより、安定したエッチングができる。すなわち、第2の層間絶縁膜111を構成するシリコン酸化膜と、第3の層間絶縁膜112を構成するシリコン窒化膜とでは、エッチング速度を異ならせることにより、大きなエッチング選択比を得ることが容易である。従って、第3の層間絶縁膜112により確実にマスクされた状態を維持しつつ、第2の層間絶縁膜111をエッチングできる。つまり、マスクの劣化によるエッチング開口サイズの変動などの問題を解消して、所望の開口を安定的に形成することができる。

### [0052]

一方、第1の層間絶縁膜110は、第3の層間絶縁膜112と同一のシリコン窒化膜により形成されているので、エッチングストッパとして確実に作用する。つまり、オーバーエッチングやアンダーエッチングなどによる問題を解消することもできる。

#### [0053]

次に、図11(a)に表したように、第1の層間絶縁膜110に接続孔を形成する。第1の層間絶縁膜110と第3の層間絶縁膜112を同質の材料により形成した場合には、このエッチング工程において、第3の層間絶縁膜112もエッチングされる。そこで、第3の層間絶縁膜112を第1の層間絶縁膜112もエッチングされる。そこで、第3の層間絶縁膜112を第1の層間絶縁膜110よりも厚く形成しておくことが必要である。エッチング条件としては、反応性イオンエッチング法により、CH $_2$  F $_2$  :50sccm О $_2$  :50sccm およびAr:200sccmの混合ガスを用いて6.7パスカルにてエッチング行うことができる。

## [0054]

30

40

20

10

次に、図11(b)に表したように、コンタクト金属113を堆積する。

そして、化学機械研磨法(chemical mechanical polishing: CMP)により研磨して表面を平坦化させて、図11(c)に表したようにコンタクト金属を埋め込んだ構造を形成できる。なお、この際にも、第3の層間絶縁膜112を設けることにより、CMPによる研磨に対して、第2の層間絶縁膜111を保護することができる。つまり、多孔質の酸化シリコンなどの比較的柔らかい材料により形成された第2の層間絶縁膜111の上に、窒化珪素などの比較的堅い材料からなる第3の層間絶縁膜112を設けることによりCMPの研磨の際に、第2の層間絶縁膜111が研磨されて膜厚が薄くなることを防ぐことができる。その結果として、配線間容量の増大や電流リークなどの問題を抑制できる。

#### [0055]

次に、図12(a)に表したように、第4の層間絶縁膜114として、例えば、MSQなどの原料を用いて多孔質の酸化シリコンなどを堆積する。そして、さらに、図12(b)に表したように、第5の層間絶縁膜115として、例えば窒化珪素膜を堆積する。この時も、図1乃至図3に関して前述したように本発明の製造方法を用いることができる。

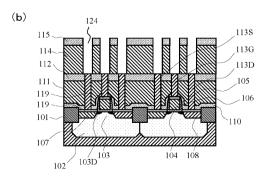

### [0056]

次に、図13(a)に表したように、レジストパターン123を形成する。

そして、図13(b)に表したように、第5の層間絶縁膜115と第4の層間絶縁膜114をそれぞれエッチングすることにより、トレンチ124を形成する。第5の層間絶縁膜115のエッチングに際しては、例えば、 $CH_2F_2:50sccm$  の混合ガスを用いて6.7パスカル(Pa)にてエッチングすることにより、層間絶縁膜115に開口部を形成することができる。第4の層間絶縁膜114にトレンチを形成する際には、 $C_4F_6:50sccm$ 、CO:50sccm、 $O_2:50sccm$ がる。この際には、 $C_4F_6:50sccm$ 、CO:50sccm0、CO:50sccm0、CO:50sccm0、CO:50sccm0、CO:50sccm0、CO:50sccm0、CO:50sccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CO:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0、CC:50scccm0 CC:50scccm0 CC:5

## [0057]

この後、配線用の金属を堆積し、CMPによって研磨して平滑化することにより、図8に表したように、トレンチにソース配線116S、ゲート配線116G、ドレイン配線116Dがそれぞれ埋め込まれた層間配線構造を形成できる。

## [0058]

以上説明したように、本実施形態によれば、エッチングストッパやハードマスクなどとして作用する層間絶縁膜110、112、115などを構成する窒化珪素膜を低温で形成することができ、シリサイド層119の変質を防ぐことができる。しかも、これら層間絶縁膜を構成する窒化珪素膜は、残留塩素の濃度が低く、半導体装置の信頼性の点でも優れる。

### [0059]

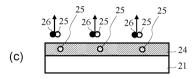

図14は、本発明の窒化珪素膜の製造方法の変型例を表すフローチャートである。

すなわち、本変型例の場合、工程11において第1のガスを導入し、工程12において 窒素ガスによるパージを実施した後に、工程17において第3のガスとして活性化水素を 導入する。すると、基板上に形成されたシリコン層に含有される塩素が活性化水素と反応 しシリコン層から取り除かれる。

## [0060]

しかる後に、工程18において窒素ガスによりパージし、その後、工程13において第 2逃すとしてアンモニアなどの窒素を含む原料ガスを導入する。この後は、図1に表した 工程と同様に実施する。

本変型例によれば、第1のガスを導入してシリコン層を形成した後に、第3のガスとし

10

20

30

50

て活性化水素を導入(工程17)してシリコン層に含有される塩素を引き抜く。またさら に、第2のガスを導入して窒化珪素膜を形成した後に、活性化水素を導入(工程15)し て窒化珪素層に含有される塩素を引き抜く。このように、シリコン層の状態と、窒化珪素 層の状態のそれぞれにおいて活性化水素により残留塩素を引き抜くことにより、膜中の塩 素の濃度をさらに低くすることができる。

#### [0061]

以上、具体例を参照しつつ本発明の実施の形態について説明した。

## [0062]

しかし、本発明は、これらの具体例に限定されるものではない。例えば、本発明の製造 方法を使用して製造した半導体装置を構成する要素について当業者が設計変更を加えたも のであっても、本発明の要旨を備えたものであれば、本発明の範囲に包含される。

10

【図面の簡単な説明】

#### [0063]

【図1】本発明の実施の形態にかかるLPCVD法による低温室化成膜のフローチャート である。

【図2】本発明の実施の形態にかかるLPCVD法による低温窒化成膜の、シリコンウェ 一八の工程断面構造を例示する模式図である。

【図3】本発明の実施の形態にかかるLPCVD法による低温窒化成膜を行う際に使用す る反応室を例示する模式図である。

【図4】窒化珪素膜中の塩素濃度の、全反射蛍光 X線測定結果を示すグラフ図である。

【図5】HF溶液に対するエッチング量の評価を行った結果を示すグラフ図である。

【図6】本発明の実施の形態にかかる半導体装置の製造方法を例示する模式図である。

【図7】比較例の製造方法によって作成した半導体装置の断面構造を例示する模式図であ

【図8】本発明により製造される半導体装置の要部断面構造を例示する模式図である。

【図9】本発明の実施の形態にかかる半導体装置の製造方法を表す工程断面図である。

【図10】本発明の実施の形態にかかる半導体装置の製造方法を表す工程断面図である。

【図11】本発明の実施の形態にかかる半導体装置の製造方法を表す工程断面図である。

【図12】本発明の実施の形態にかかる半導体装置の製造方法を表す工程断面図である。

【図13】本発明の実施の形態にかかる半導体装置の製造方法を表す工程断面図である。

【図14】本発明の窒化珪素膜の製造方法の変型例を表すフローチャートである。

【図15】本発明者が本発明に至る過程で検討した窒化珪素膜の形成手法を示すフローチ ャートである。

## 【符号の説明】

### [0064]

11 第1の工程

12 第2の工程

13 第3の工程

14 第4の丁程 15 第5の工程

16 第6の工程

2 1 シリコンウェーハ

22 シリコンと塩素とを含む層

2 3 窒化珪素薄膜

2 5 塩素

2 6 水素

3 1 反応室

32 第1のガスを供給するインジェクター

3 3 第 2 のガスを供給するインジェクター

3 4 第 3 のガスを供給するインジェクター

20

30

40

- 35 シリコンウェーハ

- 36 ウェーハステージ

- 3 7 排気口

- 41 通常のLPCVDによって形成した窒化珪素膜

- 42 従来技術によって形成した窒化珪素膜

- 43 本発明の製造方法によって形成した窒化珪素膜

- 6 1 シリコン基板

- 6 2 ゲート絶縁膜

- 6 3 ゲート電極

- 6 4 窒化珪素膜

- 7 1 サイドウォール

- 7 2 ゲート絶縁膜

- 7 3 ゲート電極

- 8 1 サイドウォール

- 8 2 塩素

- 8 3 ゲート絶縁膜

- 8 4 ゲート電極

- 101 素子分離領域

- 102 ウェル

- 103 チャネル

- 104 ゲート絶縁膜

- 105 ゲート側壁

- 106 ゲート電極

- 107 ソース領域

- 108 ドレイン領域

- 1 1 0 ~ 1 1 2 層間絶縁膜

- 113D ドレインコンタクト

- 113G ゲートコンタクト

- 1135 ソースコンタクト

- 1 1 4 、 1 1 5 層間絶縁膜

- 1 1 6 D ドレイン配線

- 116G ゲート配線

- 1165 ソース配線

- 119 シリサイド層

- 120 レジストパターン

- 120 レジストマスク

- 1 2 1 開口部

- 1 2 2 接続孔

- 123 レジストパターン

- 124 トレンチ

- 2 1 0 第 1 の 工程

- 220 第2の工程

- 230 第3の工程

- 2 4 0 第 4 の 工程

10

20

30

【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

# 【図14】

# 【図15】

## フロントページの続き

# (72)発明者 織戸 康一

東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内

# 審査官 宮本 靖史

# (56)参考文献 国際公開第03/025243(WO,A1)

特開2003-249657(JP,A) 特開平01-179710(JP,A)

特開2003-218106(JP,A)

特開2002-343793(JP,A)

# (58)調査した分野(Int.CI., DB名)

H 0 1 L 2 1 / 3 1 8 H 0 1 L 2 9 / 7 8