## (12) UK Patent Application (19) GB (11) 2 077 010 A

- (21) Application No 8116575

- (22) Date of filing 29 May 1981

- (30) Priority data

- (31) 55/072715 55/170942 56/039593

- (32) 2 Jun 1980 5 Dec 1980 20 Mar 1981

- (33) Japan (JP)

- (43) Application published 9 Dec 1981

- (51) INT CL3 G06F 9/26

- (52) Domestic classification G4A 12R 15A1 16D 17B 17P PM

- (56) Documents cited GB 1541756 GB 1528332 GB 1478489 GB 1457878 GB 1192368

- (58) Field of search G4A

- (71) Applicant

Hitachi Ltd

5–1 Marunouchi

1-chome

Chiyoda-ku

Tokyo

Japan

- (72) Inventors Koyo Katsura Hideo Maejima

- (74) Agents

Langner Parry

52–54 High Holborn

London WC1V 6RR

## (54) A microprogram control method and apparatus therefor

(57) A microprogram control system is disclosed which increases a processing speed of a microprogram, reduces a capacity of a microprogram memory and facilitates error checking.

A decoder to decode a content of an instruction register is omitted to attain the high speed and an instruction decoding function is integrated in the microprogram memory to attain a general purpose control system.

Short word memory device (132) is used to reduce the memory capacity of the microprogram memory. A check function of readout error is also provided.

A microinstruction is read out of a corresponding address in a microprogram memory 15 in accordance with an instruction read out of a main memory or an externally supplied instruction and is decoded 17 to provide an operation control signal. The address designated in the microprogram memory is based on a signal from a register 11 storing the instruction and on a signal from a page register 61 which designates a page of the microprogram memory to provide a decoding function.

GBZU//UIU A

FIG. IA

FIG. 3 PRIOR ART FROM MAIN MEMORY INSTRUCTION BIT PATTERN REGISTER 31 **GENERATOR** 3a ADDRESS SELECTION 13~ CIRCUIT MICROPROGRAM ADDRESS REGISTER 14 3b MICROPROGRAM 15-**MEMORY** 3c MICROINSTRUCTION 16 REGISTER 3d-MICROINSTRUCTION 17-DECODER CONTROL SIGNALS

FIG. 5 PRIOR ART

FIG. 6

F16.7

6/12

FIG. 10A

FIG. IOB

FIG. IOC

FIG. IIB

FIG.14

FIG. 15

FIG. 17

FIG. 18

FIG. 19

r.

FIG. 20

FIG. 21

## **SPECIFICATION**

## Microprogram control method and apparatus therefor

|    | inition program contact and a second |    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | The present invention relates to a microprogram control method and an apparatus therefor having a microprogram memory with an instruction decoding function, in which, more particularly, the microprogram memory is arranged to store short word length microinstructions and to detect abnormal microprogram sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5. |

| 10 | In the microprogram control system, all of the control items are stored in the microprogram memory. Accordingly, the contents of the memory may be updated to allow a different execution other than the old one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 |

| 15 | On the other hand, in order to execute a different instruction set, contents of an instruction decoder must also be modified. However, since the instruction decoder is usually constructed to comply with a particular instruction set, a sufficiently large scale of decoder circuit must be prepared or troublesome modification of circuit configuration is required in order to execute the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 |

| 15 | completely different instruction set.  The present invention permits the flexibility to the different instruction set without loosing generality so that the microprogram control system can be used for general purpose while a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 20 | memory capacity for storing the microprograms can be reduced and also it has a function to detect abnormal microprogram sequence.  In an instruction fetch microproutine, an instruction word is read out of a main memory and an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

| 25 | instruction decoder decodes it to generate an initial address of a microroutine corresponding to that instruction. The generated initial address is stored in a microprogram address register through address selection means, and a microinstruction word specified by the register is read out of a microprogram memory. An operation field (code) of the read-out microinstruction is stored in a microinstruction register and an address field (code) of the microinstruction is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 |

| 30 | returned to the address selection means. The operation field (code) of the microinstruction is decoded by a microinstruction decoder, which generates various control signals. On the other hand, the content of the address field of the microinstruction returned to the address selection means is transferred to a microprogram address register to sequentially read out and executes the microinstructions. The above is an example of a prior art system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 |

| 35 | In the system, a time period from the decode of the instruction to the generation of the initial address is mainly determined by an access time of the memory although it may vary depending on the configuration and the scale of the instruction decoder. In this system, therefore, the configuration of the instruction decoder governs the operation speed of the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35 |

|    | Another known system is a mapping system. It is in many cases used in a computer of a simple instruction set. In this system, a fixed bit pattern generating means is provided and an output signal from the bit pattern generating means and a content of an instruction register which stores a word read out of a main memory are combined to generate an initial address of a microroutine. This system may be called a simplified system in that it does not use an instruction decoder. While this system needs shorter time than the previously mentioned system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40 |

|    | to establish the output of the microprogram address register, it is not a general purpose system because it cannot be used in a complex instruction set having two or more instruction codes because a branch-to address to the instruction code is fixed in this system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 45 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45 |

| 50 | A method for reading a microprogram is disclosed in U.S. Patent 4,008,462 entitled "Plural Control Memory System with Multiple Microinstruction Readout". It discloses a control system which permits the readout of the microinstruction at the same speed as that of the microinstruction readout in a prior art system, even with a low performance control memory. However, this method is applicable only to a system having a control memory bank which reads out a plurality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50 |

| 55 | of microinstruction by a single address designation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55 |

| 60 | flexible generality.  It is another object of the present invention to provide a microprogram control system having an improved microprogram memory efficiency in which microprograms having high frequency of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 |

| 65 | use are described in short length words.  It is a further object of the present invention to provide a microprogram control system including means for rapidly detecting an abnormal microprogram control sequence which is caused by an error in decoding an address in a microprogram memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| - | 5  | In order to attain the above objects, it is a main feature of the present invention to divide the microprogram memory into plural-word pages and provide a page allocation register controlled by the microprogram and an address-in-page allocation register which can directly read in the content of the instruction register so that any desired page can be used as an instruction decode area.                                                                           | 5               |

|---|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|   | •  | It is another feature of the present invention to construct the microprogram memory by a first microprogram memory for storing long word microinstructions capable of general representation and a second microprogram memory for storing short word microinstructions which have high frequency of use and represent limited processes. When a short word microinstruction is read                                                                                            |                 |

| 1 | 0  | out, it is restored to an original long word microinstruction by a pit pattern generating circuit.  It is a further feature of the present invention to contain in each microinstruction a phase information on a reference clock having a period which is a multiple of the microinstruction execution clock period and, when a microinstruction is read out, to detect any abnormal                                                                                          | <sub>2</sub> 10 |

| 1 | 5  | microinstruction control sequence by checking if the phase information has a predetermined relationship with the phase of the reference clock.  The objects, features and advantages of the present invention will be understood from the following description of embodiments of the present invention in conjunction with the accompa-                                                                                                                                       | 15              |

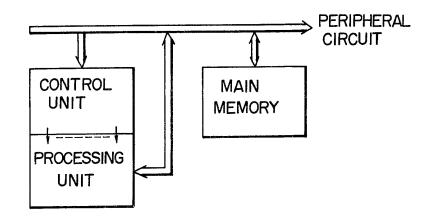

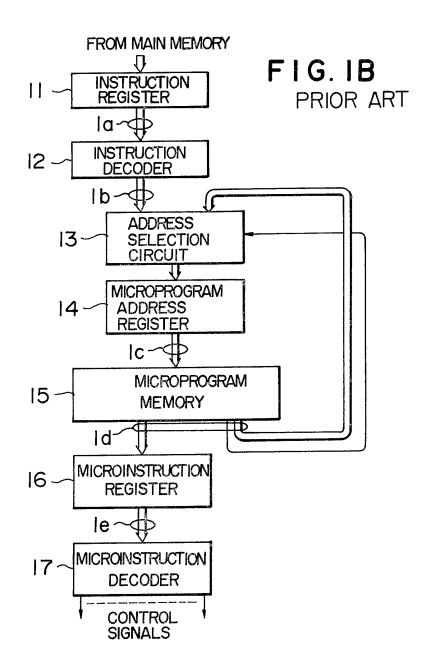

| 2 | 0  | nying drawings in which,  Figure 1A shows a general arrangement of a system using a microprogram control unit of the present invention,  Figure 1B shows a block diagram of a prior art microprogram control unit,                                                                                                                                                                                                                                                             | 20              |

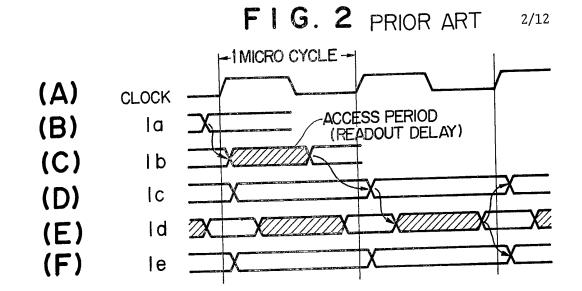

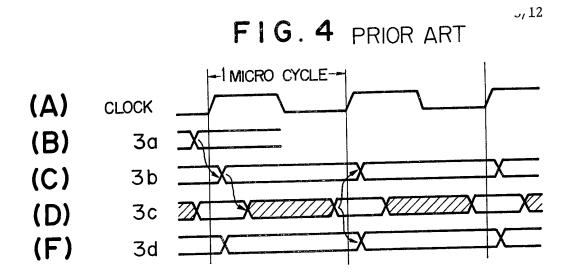

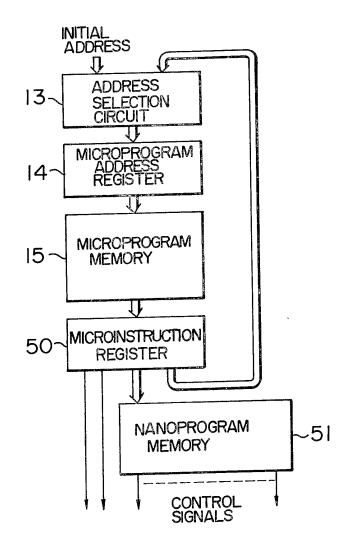

| 2 | 5  | Figure 2 shows a timing chart therefor, Figures 3 and 4 shows a block diagram and a timing chart, respectively, of a prior art system called a mapping system, Figure 5 shows a block diagram of a prior art nanoprogram system,                                                                                                                                                                                                                                               | 25              |

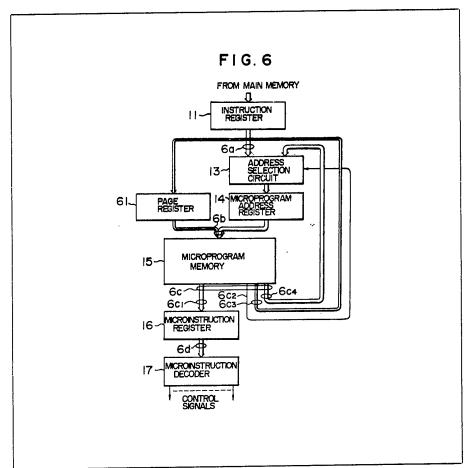

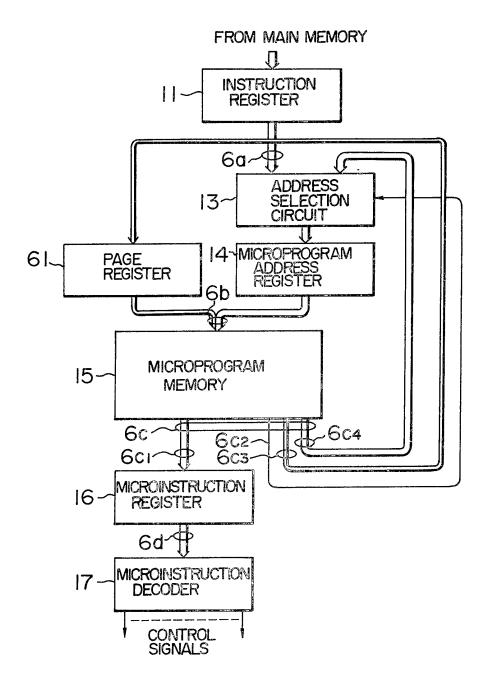

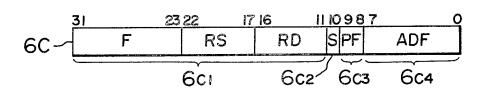

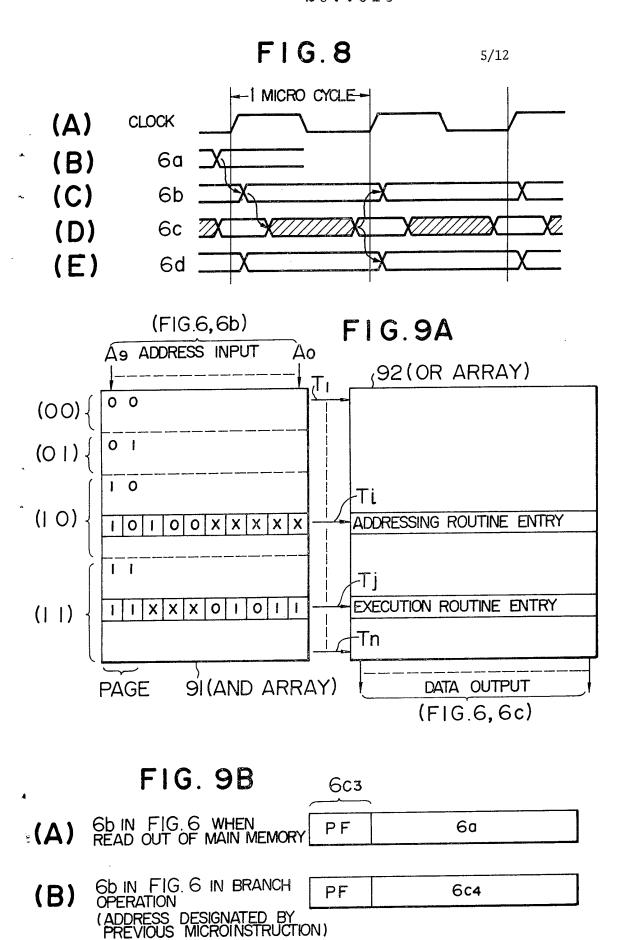

|   |    | Figure 6 shows a block diagram of a microprogram control system having a page register, for explaining the present invention,  Figure 7 shows an example of a microinstruction format,  Figure 8 shows an example of an operation time chart of Fig. 6,                                                                                                                                                                                                                        |                 |

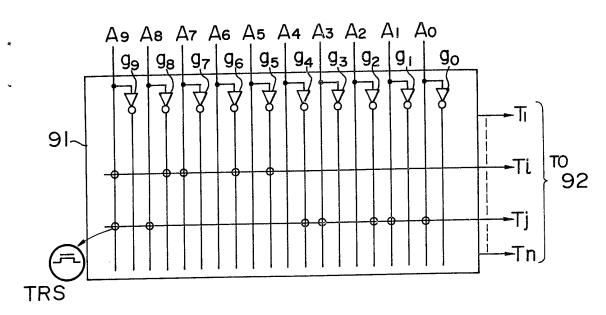

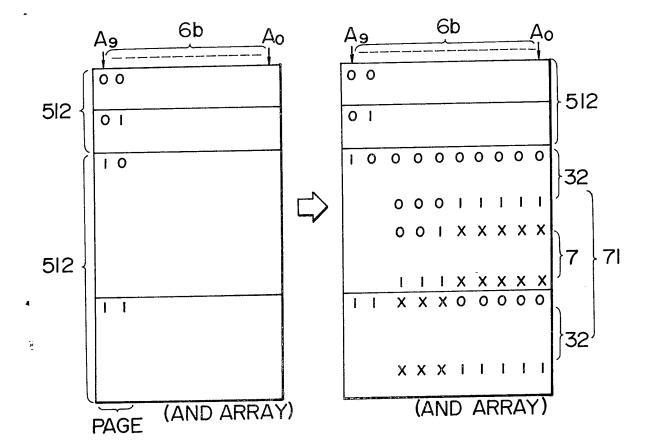

| 3 | 0  | Figure 9A shows a configuration of a microprogram memory in connection with pages, Figure 9B shows an example of a format of a signal 6b in Fig. 6, Figure 10A shows a configuration of an AND array 91 in Fig. 9A, Figure 10B illustrates comparison of capacity of the AND array 91 in Fig. 9A in which a                                                                                                                                                                    | 30              |

| 3 | 5  | decoder is not disposed as opposed to in Fig. 1 but integrated in the memory,                                                                                                                                                                                                                                                                                                                                                                                                  | • 35            |

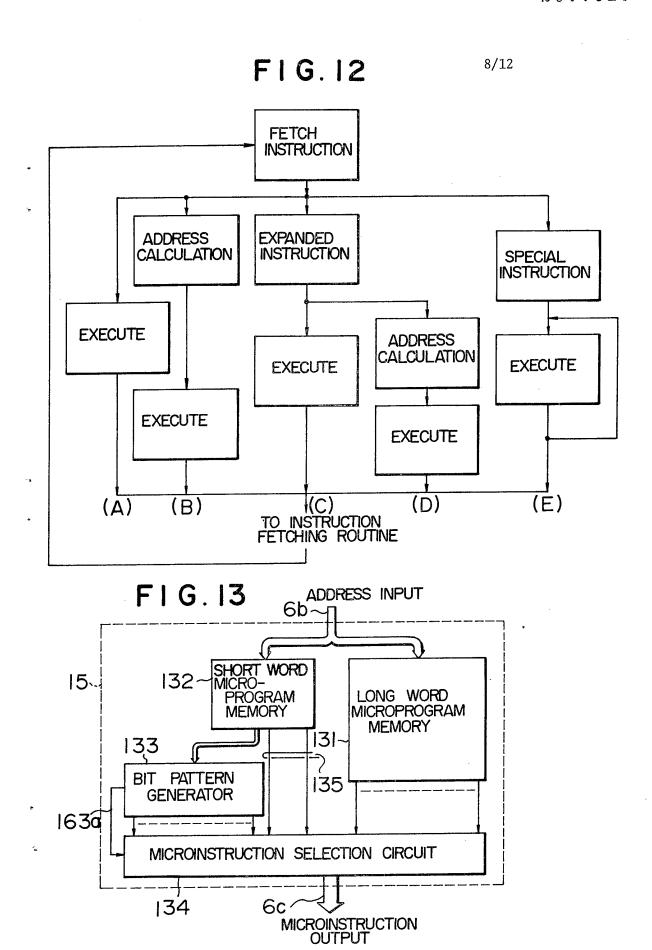

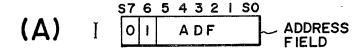

| 4 | 0  | register, Figure 12 shows a process flow chart by the instruction formats shown in Fig. 11A, Figure 13 shows a block diagram in which a short word memory system is introduced to save a memory capacity,                                                                                                                                                                                                                                                                      | 40              |

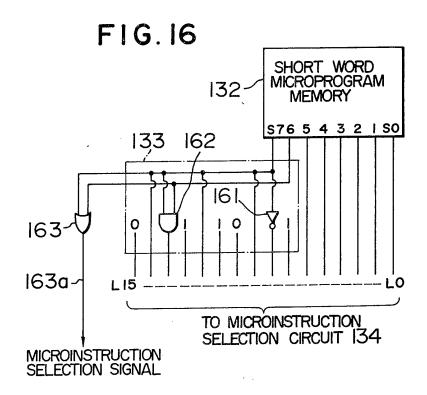

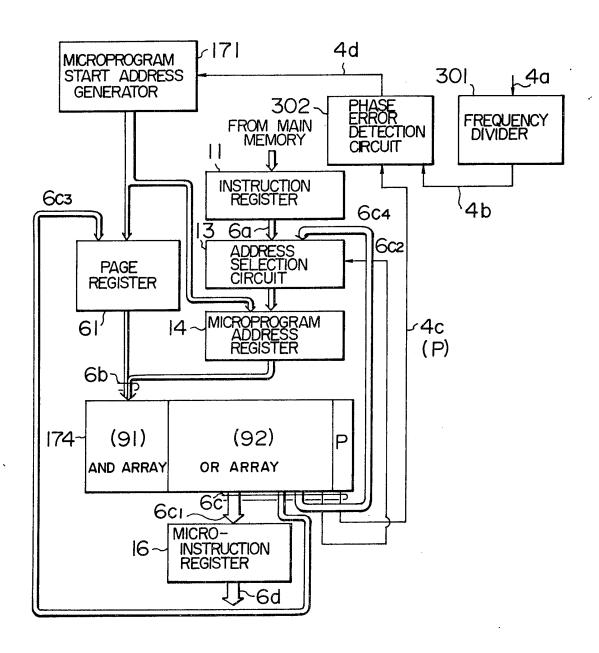

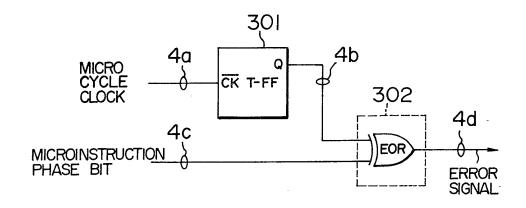

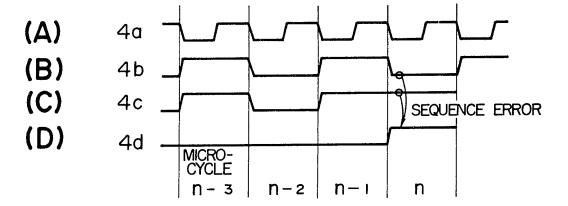

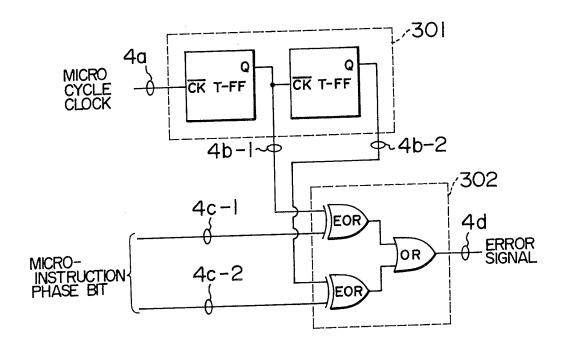

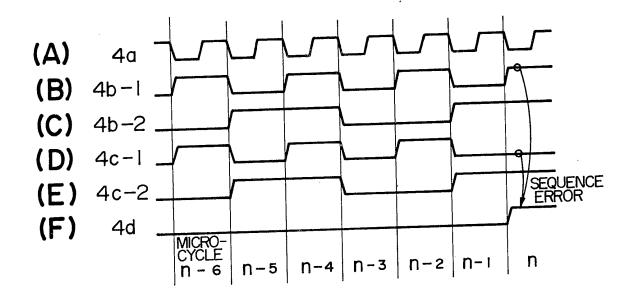

| 4 | -5 | Figure 14 illustrates short word microinstructions, Figure 15 illustrates long word microinstructions to compare with Fig. 14, Figure 16 shows a bit pattern generating circuit in Fig. 13, Figure 17 shows a block diagram of a microprogram control system having a fault detection                                                                                                                                                                                          | 45              |

|   |    | circuit,  Figure 18 shows a specific embodiment of the fault detection circuit,  Figure 19 shows a timing chart therefor,                                                                                                                                                                                                                                                                                                                                                      | F0              |

| 5 | 0  | Figure 20 shows a modification of Fig. 18 and Figure 21 shows a timing chart therefor. In order to facilitate the understanding of the present invention, a technical background is first explained.                                                                                                                                                                                                                                                                           | 50              |

| 5 | 5  | microprogram control unit which corresponds to the control unit of the processor shown in Fig. 1A. An output of a microinstruction decoder or a control signal controls a processing unit (Fig. 1A).                                                                                                                                                                                                                                                                           | 55              |

| 6 | 0  | The microprogram control system shown in Fig. 1B comprises an instruction register 11, an instruction decoder 12, an address selection circuit 13, a microprogram address register 14, a microprogram memory 15, a microinstruction register 16 and a microinstruction decoder 17. In an instruction fetch microroutine, an instruction word is read out of the main memory and stored into the instruction register 11. The instruction decoder 12 decodes the content of the | 60              |

| 6 | 5  | instruction register 11 to generate an initial address of a microroutine corresponding to the instruction code. The initial address generated by the instruction decoder 12 is loaded to the                                                                                                                                                                                                                                                                                   | 65              |

|    | microprogram address register 14 through the address selection circuit 13 and a microinstruction word corresponding to the address is read out of the microprogram memory 15. An operation field (code) of the read-out microinstruction is loaded to the microinstruction register                                                                                                                                                                                                               |    |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | 16 while an address field (code) of the microinstruction is returned to the address selection circuit 13. The content of the microinstruction decoder 16 is decoded by the microinstruction decoder 17, which generates various control signals. On the other hand, the content of the address field returned to the address selection circuit 13 is transferred to the microprogram address register 14 so that the microinstructions are sequentially read out and executed. Fig. 2             | 5  |

| 10 | shows a timing chart thereof, in which an output 1a of the instruction register 11, an output 1b of the instruction decoder 12, an output 1c of the microprogram address register 14, an output 1d of the microprogram memory 15 and an output 1e of the microinstruction register 16 are shown together with a basic clock. Hatched areas in Fig. 2 show periods in which signals are                                                                                                            | 10 |

| 15 | not established due to delay times in the circuit a time period from the establishment of the output 1a of the instruction register 11 to the establishment of the output 1b of the instruction decoder 12, or in other words a time period from the decode of the instruction to the generation of the initial address is essentially comparable to an access time of the memory although it may vary depending on the configuration and the scale of the instruction decoder. Fig. 2 shows that | 15 |

| 20 | one microinstruction cycle as called "micro cycle" is necessary as waiting time before starting the readout of the microprogram memory. As discussed hereinabove in connection with the prior art, this system has problems in the processing speed and the generality.  Fig. 3 shows an example of the mapping system and Fig. 4 shows a timing chart therefor. It                                                                                                                               | 20 |

| 25 | is used in a computer of a simple instruction set. A combination of an output of a fixed bit pattern generating circuit 31 and the content of the instruction register 11 is used as an initial address of the microroutine. It does not use an instruction decoder and hence it is a simple system.                                                                                                                                                                                              | 25 |

|    | Fig. 4 shows a relation of an output 3a of the instruction register 11, an output 3b of the microprogram address register 14, an output 3c of the microprogram memory 15 and an output 3d of the microinstruction register 16. The advantages and the disadvantages of this system have been discussed hereinabove.                                                                                                                                                                               |    |

| 30 | The microprogram memory 15 contains many microinstructions which are identical to each other in their processing contents except branch-to address information fields and certain control bits of the microinstructions. In the construction shown in Fig. 1B, however, even when the contents of the microinstructions are substantially identical, the microinstructions are separately                                                                                                         | 30 |

| 35 | stored if the branch-to address information fields or certain control bits are different. As a result, the microprogram memory 15 contains a plurality of microinstructions which are identical in major portions of their bit patterns. Consequently, the efficiency of the microprogram memory is poor and the memory capacity increases. An improvement over the above system is known as a                                                                                                    | 35 |

| 40 | nanoprogram system which is shown in Fig. 5. In this system, the microinstruction includes a branch-to address information field, a control bit field and a nanoprogram address field. In response to a nanoprogram address field of a microinstruction read out to the microinstruction register 50, a nanoprogram memory 51 is activated to read out a corresponding nanoinstruction to generate various control signals. With this construction, the member of words of the long               | 40 |

| 45 | word nanoprograms is reduced by eliminating overlaps and the length of words of the microprograms including a number of words is shortened in order to improve the overall efficiency of the memory. However, in this nanoprogram system, a hardware construction is complex and the efficiency is poor unless the word length of the nanoinstruction is very long. As a result, a capacity of the nanoprogram 51 increases. In addition, since the readout time of the                           | 45 |

| 50 | nanoprogram is additionally required, the processing time from the activation of the microprogram memory to the generation of the control signals increases. Another problem arises in improving the reliability of the microprogram control system.  It is a common method of detecting an error in the microprogram memory to add one parity bit to the microinstruction and check if a total number of "1" bits in the microinstruction is                                                     | 50 |

| 55 | even or odd.  The method of adding the parity bit such that the total number of "1" bits is equal to an even number is called an even parity method, and the method of adding the parity bit such that the total number is equal to an odd number is called an odd parity method.  The error detection system by the addition of the parity bit is effective to the detection of an                                                                                                               | 55 |

| 60 | error in reading out the microinstruction but it cannot detect an error in the microprogram address information or an error in decoding an address of the microprogram memory.  A watch dog timer system is known as a fault detection system by an overrun of software or bardware.                                                                                                                                                                                                              | 60 |

|    | A conventional watch dog timer normally counts up clock signals and is reset by a software instruction. When the timer count exceeds a preset count before it is reset, a system restart                                                                                                                                                                                                                                                                                                          |    |

| 65 | signal is produced.  The location of insertion of the watch dog timer and the preset count of the timer are selected                                                                                                                                                                                                                                                                                                                                                                              | 65 |

5

15

20

25

30

· 35

65

such that the timer is always reset before the timer count reaches the preset count in a normal operation condition and if the watch dog timer is not reset because of the program overrun or the like, the timer count exceeds the preset count to produce the restart signal and interrupt the abnormal process.

The watch dog timer system is used to prevent the overrun at a software level so that the preset count of the timer usually has a relatively large count. Accordingly, this system is effective to the detection of an abnormal sequence in the software level but it is not practical to the detection of an abnormal sequence in the microinstruction level which needs a rapid response.

Bearing the basic technical description explained above in minds, preferred embodiments of the present invention is now explained.

An embodiment of the present invention is shown in Fig. 6 in which the like elements to those in Figs. 1 and 3 are designated by like reference numerals. A page register 61 relates to

the present invention. The content of the instruction register is loaded to the address register 14 through the address selection circuit 13. The content of the page register 61 is controlled by a microprogram. A combination 6b of the content of the page register 61 and the content of the address register 14 is used to designate an address of the microprogram memory 15 to readout a microinstruction word from the microprogram memory 15. The read-out microinstruction includes an operation field 6c1 which is loaded to the microinstruction register 16, an address selection bit 6c2 which controls the address selection circuit 13, a page field 6c3 which is returned to the page register 61 and an address field 6c4 which is returned to the address selection circuit 13. The content of the microinstruction register 16 is decoded by the microinstruction decoder 17 which produces various control signals. The address field 6c4 of the microinstruction returned to the address selection circuit 13 is loaded to the microprogram address register 14, and the content of the page register 61 and the content of the microprogram address register 14 are combined and based on the combination 6b a microin-

struction is read out of the microprogram memory 15. In this manner a series of microinstructions are sequentially executed. Address space of the microprogram memory 15 is classified into page areas each including a plurality of words having a common page field. A certain page area of the memory is allocated to leading areas of microroutines which branch depending on the content of the instruction register 11 so that any desired branch can be permitted. In addition, by controlling the content of the page register 61, a plurality of branches can be permitted to a given instruction code (two branches in the example of Fig. 9) so that the system can be adapted to a complex instruction set. The adaption to a different instruction set is permitted by merely altering the content of the microprogram memory 15 and hence the system has a sufficient generality.

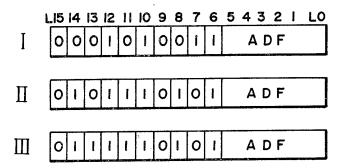

Fig. 7 shows a format of the microinstruction. It comprises a function field F (nine bits) for specifying a type of operation, a source register field RS (six bits) for designating a readout register, a destination register field RD (six bits) for designating a write register, an address selection bit field S (one bit) for controlling the address selection 13, a page field PF (two bits) for designating a next branch-to page and an address field ADF (eight bits) for designating a next branch-to address.

Fig. 8 shows a timing chart for the system of Fig. 6, in which (B) represents the output 6a of the instruction register 11, (C) represents the output 6b of the page register 61 and the address register 14, (D) represents the output 6c of the microprogram memory 15 and (E) represents the 45 output 6d of the microinstruction register 16, and (A) represents the basic clock. The hatched areas represent the access periods like in Fig. 2.

In the system of Fig. 6, no instruction decoder is disposed downstream the instruction register 11. Since the content of the register 11 is directly loaded to the address register 14, the time required to generate the initial address of the microroutine can be shortened as is seen from Fig. 50 8.

The process procedure in the system of Fig. 6 is now explained. In the instruction set used in the illustrated example, the instruction code is represented by eight bits of which three high order bits define an addressing mode and five low order bits define a content to be executed.

The instructions are classified into the following two major categories depending on their process procedures. 55

(A) Instructions whose operands to be executed are in the register or instructions which do not need operands, such as an accumulator operation instruction or a return instruction from a subroutine. Those instructions which have "000" in the three high order bit positions are

60 categorized hereto. They are branched to process routines corresponding to the instruction codes after the completion of the instruction fetch routine.

(B) Instructions whose operands are in the memory, such as a load instruction from the memory to the accumulator, an operation instruction between the accumulator and the memory and a jump instruction. This type of instructions have 001~111 in the three high order bit

65 positions with the three high order bits defining an operand address calculation mode and the

GB 2 077 010A 5

65

five low order bits defining a content to be executed. The addressing mode includes a direct addressing mode, an indirect addressing mode and a relative addressing mode. In this type of instructions, they branch to the address calculation routines after the completion of the instruction fetch routine and branch to the execution routines corresponding to the instructions 5 after the completion of the address calculation. In order to execute the instruction, the instruction register 11, the address register 14 and the page register 61 in Fig. 6 have eight bits, eight bits and two bits, respectively, and the following functions are allocated to the pages of the address of the microprogram memory 15. (1) Pages (00) and (01) 10 They are used as working areas. Second and subsequent words of the instruction fetch routines and the process routines are stored therein. It is allotted to a first decoding area of the instruction code. First words of the routines of the type (A) instructions and first words of the address calculation routines of the type (B) 15 15 instructions are stored therein. Page (11) It is a second decoding area of the type (B) instruction. First words of the execution routines are stored therein. In the instruction fetch microroutine, an instruction word is read out of the main memory and loaded in the instruction register 11. When the instruction fetch routine is 20 20 completed, (10) is loaded to the page register 61 and the content of the instruction register 11 is loaded to the address register 14 and the process branches to the address corresponding to the instruction code on the page (10). In th type (A) instruction, the microroutines starting from the address corresponding to the page (10) are execution routines corresponding to the instructions. After the completion of the execution processes, the process returns to the 25 instruction fetch routine. In the type (B) instruction, the address calculation routine starts from 25 the address corresponding to the page (10). When the address field calculation routine is completed, (11) is loaded to the page register 61 and the content of the instruction register 11 is loaded to the address register 14 and the process branches to the address corresponding to the page (11). The routines having the first words on the page (11) are the execution routines 30 for the instructions. When the execution routine is completed, the process returns to the 30 instruction fetch routine. Since the address calculation and execution processes for the type (B) instruction are common to a plurality of instruction codes, the microinstructions of a plurality of addresses are identical when the process branches to the page (10) and the page (11). In the present system, one word of the memory is allotted to the plurality of address to substantially 35 save the memory capacity. Fig. 9A illustrates the above and it shows an arrangement of the 35 memory. The symbols X indicate non-decoded areas. The memory comprises an AND array 91 which decodes an address input to produce a signal designating a word in the memory and an OR array 92 for producing a content of the word of the memory designated by the output of the AND array 91. The output of the OR array 92 corresponds to the signal 6c in Fig. 6. The input 40 address signals A<sub>0</sub>~A<sub>9</sub> to the AND array 91 correspond to the signal 6b in Fig. 6. As shown in 40 Fig. 9b, they are read out of the main memory (A) or designated by the previous microinstruction (branch) (B), Fig. 10A shows a detailed circuit configuration of the AND array 91 of Fig. 9. Symbols  $g_0 \sim g_9$  indicate gate circuits. In order to decode address information, transistors TRS are connected to positive logic sides of bits "1" of the address input, and to negative logic 45 sides of bits "O" of the address input, respectively. Each of the transistors TRS produces an 45 output "1" in response to an input "1" applied thereto, and a group of transistors TRS disposed for decoding each one of the address inputs are connected to an AND gate thereby to produce an output "1" when all of the transistors of the group receive an input "1". For example, in Fig. 10A, the output Ti goes "1" when the positive logic sides of inputs A<sub>9</sub> and A<sub>7</sub> 50 are all "1" and the negative logic sides of inputs  $A_8$ ,  $A_6$  and  $A_5$  are all "1". In an AND array of 50 a conventional memory, the address input is completely decoded to allocate one word of the memory to each address. In the present system, it is effective in some cases to partially decode the address by the AND array 91. More particularly, the X-mark areas in Fig. 9A can be realized in the circuit of Fig. 10A by omitting the transistors TRS either on the positive logic side or on 55 the negative logic side. As a result, the increase of the capacity of the microprogram memory 15 55 due to the need of the identical microinstruction at different addresses is avoided. As shown in Figs. 10B and 10C, 512 transistors required for the pages (10) and (11) are reduced to 71 transistors. In the type (B) instruction, when the process branches to the addressing routine on the page 60 (10), the five low order bits of the address are not decoded so that only one word of the 60 memory is allotted to a plurality of addresses having different low order bits. The AND array 91 may be constructed to decode the two high order bits or the page designating field of the address on the page (11) and the five low order bits. This system is particularly effective when

the microprogram memory is a read-only memory because the content of the address decoder

65 and the content of the memory can be simultaneously designed.

5

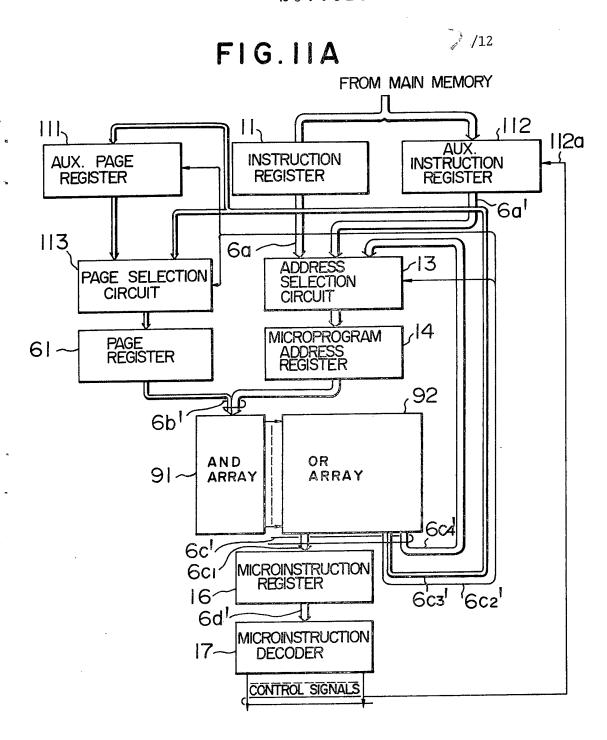

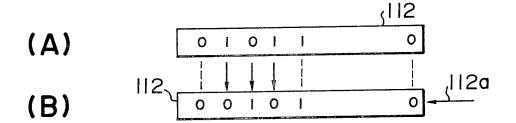

| 5  | Fig. 11A shows another embodiment of the present invention. It differs from the embodiment of Fig. 6 in that an auxiliary page register 111, an auxiliary instruction register 112 and a page selection circuit 113 are added in order to efficiently process more complicated instruction set. The elements and their functions are described below.  (1) Auxiliary page register 111  It is a four-bit register and retains data to be located to the page register 61. Any desired content can be preset by the microprogram.  (2) Instruction register 11                                                                             | 5  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10 | It is an eight-bit register and retains an instruction word read out of the main memory.  (3) Auxiliary instruction register 112  It is an eight-bit register and has a similar function to that of the instruction register 11. By the provision of two instruction registers, the system is adaptable to a fairly complicated                                                                                                                                                                                                                                                                                                           | 10 |

| 15 | instruction set. The register has an additional function of setting and resetting any bit by a microinstruction 112a (see Fig. 11B). This will be explained hereinlater.  (4) Page selection circuit 113  It selects the data to be loaded to the page register 61 from the content of the auxiliary page register 111 and the page field of the microinstruction read from the memory. It is activated by a selection signal from the microinstruction.                                                                                                                                                                                  | 15 |

| 20 | <ul> <li>(5) Address selection circuit 13 It selects the data to be loaded to the address register 14 from (i) the output of the instruction register 11, (ii) the output of the auxiliary instruction register 112 and (iii) the address field of the microinstruction. It is activated by a control signal from the microinstruction. </li> <li>(6) Page register 61</li> </ul>                                                                                                                                                                                                                                                         | 20 |

| 25 | It is a four-bit register and retains four higher order bits of the 12-bit address of the microprogram memory 15.  (7) Microprogram address register 14  It is an eight-bit register and retains light lower order bits of the memory address.                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

| 30 | (8) AND array 91 It is a 12 bits × (number of memory words) array. It decodes an address to designate one word of the memory. The address spaces are sorted by areas (pages) having common four high order bits of the addresses. The address is decoded as partially as possible in order to reduce the number of memory words.  (9) OR array 92                                                                                                                                                                                                                                                                                         | 30 |

| 35 | It is a read-only memory having a capacity of (number of memory words) × 32 bits for storing microprograms.  (10) Microinstruction register 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35 |

| 40 | It retains an operation field of a microinstruction read out of the microprogram memory 15.  (11) Microinstruction decoder 17  It decodes the content of the microinstruction register 16 and produces control signals to processing circuits and gate circuits.  The instruction set under consideration is now explained. The instructions are classified into the five categories listed in Table 1 depending on their types of process. Fig. 12 shows a process flow for those five types of instructions. In order to execute those instructions, the address spaces of the microprogram memory 15 are allotted as shown in Table 2. | 40 |

|          | TABLE 1                     | PROCESSES OF INSTRUCTIONS                                                                                                                                                                                           |

|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Type of<br>Instruc-<br>tion | Process                                                                                                                                                                                                             |

|          | (A)                         | Branches directly to an execution routine corresponding to an instruction code.                                                                                                                                     |

| 10<br>15 | (B)                         | Branches to corresponding execution routine after operand address calculation. A next sequential word to the instruction code specifies one of a plurality of addressing modes.                                     |

| 20       | (C)                         | If the instruction code of the first word has a particular value, a next sequential second word to the first word defines a new instruction. Branches to an execution routine corresponding to the new instruction. |

| 25       | (D)                         | Similar to (C) but needs operand address calculation. The addressing mode is identical to that of (B)                                                                                                               |

| 30       | (E)                         | Bits of a next sequential second word to the instruction code are permission flags to the corresponding process.                                                                                                    |

| 35       | TABLE 2                     | ADDRESS PAGE ALLOCATION                                                                                                                                                                                             |

| 00       | Page                        | Allocation of Functions of Areas                                                                                                                                                                                    |

| 40       | 0000<br>0001                | Work area                                                                                                                                                                                                           |

| 70       | 0010                        | First decode area of instuction code                                                                                                                                                                                |

| 45       | 0011                        | Decode area for branching to an execution routine after address calculation for type (B) instruction.                                                                                                               |

|          |                             | Second decode area of instruction code for type (C) and (D) instructions.                                                                                                                                           |

| 50       | 0101                        | Decode area for branching to an execution routine after address calculation for type (D) instruction.                                                                                                               |

| 55       | 0110                        | Decode area for execution routine of type (E) instruction.                                                                                                                                                          |

|          | 0111                        | Decode area for address calculation.                                                                                                                                                                                |

| 60       | 1000<br>∫<br>1111           | Undefined spare areas. Not used in the present instruction set                                                                                                                                                      |

| 5  | loaded to the instruction register 11. Upon the completion of the instruction fetch routine, "0010" is loaded to the page register 61 and the content of the instruction register 11 is loaded to the address register 14, and the process branches to an address on the page (0010). In the type (A) instruction, the page (0010) is the leading area of the execution routine and the microinstruction corresponding to the first word of the execution routine is stored in the address corresponding to the instruction word in the page (0010). The second and subsequent words of the routines are stored in the working area. In the type (B) instruction, the address is calculated | 5  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10 | prior to the execution routine. The address calculation routine is common to the type (B) and (D) instructions but the branch-to addresses after the address calculation are different. In order to efficiently process the above, the auxiliary page register 111 is used. The process of the address calculation differs depending on the content of the next sequential word to the instruction code,                                                                                                                                                                                                                                                                                    | 10 |

| 15 | but the content of the instruction register 11 should be maintained because it includes information on the branch to the next sequential execution routine. Accordingly, the auxiliary instruction register 112 is used for the address calculation. In the execution of the type (B) instruction on the page (0010), the next sequential word to the instruction code is read out of the main memory and loaded to the auxiliary instruction register 112, and the branch-to page (0011) after the address calculation is loaded to the auxiliary page register 111. Then, the content of the auxiliary instruction register 112 is loaded to the address register 14 and the              | 15 |

| 20 | process branches to the address calculation routine corresponding to the addressing mode on the page (0111). Upon the completion of the address calculation routine, the content of the auxiliary page register 111 is loaded to the page register 61 and the content of the instruction register 11 is loaded to the address register 14. Thus, the process branches to the execution                                                                                                                                                                                                                                                                                                      | 20 |