# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 112929512 B (45) 授权公告日 2024.04.05

(21)申请号 201911374373.4

(22)申请日 2019.12.27

(65) 同一申请的已公布的文献号 申请公布号 CN 112929512 A

(43)申请公布日 2021.06.08

(30) 优先权数据 108144548 2019.12.05 TW

(73) **专利权人** 新唐科技股份有限公司 **地址** 中国台湾新竹科学工业园区

(72) 发明人 郝禹廸 沈子岚

(74) 专利代理机构 北京三友知识产权代理有限 公司 11127

专利代理师 周晓飞 许曼

(51) Int.CI.

**HO4N** 5/14 (2006.01)

(56) 对比文件

CN 102595193 A,2012.07.18

JP S63201783 A,1988.08.19

US 2009213261 A1,2009.08.27

US 2012075680 A1,2012.03.29

审查员 陈志清

权利要求书2页 说明书7页 附图5页

#### (54) 发明名称

控制电路及其控制方法

#### (57) 摘要

本发明提供了一种控制电路及其控制方法,该控制电路耦接于一图像获取装置与一显示装置之间。图像获取装置根据一工作频率输出多个图像数据。控制电路包括一第一传输接口、一存储电路、一处理电路以及一第二传输接口。第一传输接口耦接图像获取装置,用以接收图像数据。存储电路耦接第一传输接口,用以接收并存储图像数据。处理电路获取存储电路所存储的图像数据,用以产生多个显示数据,并根据存储电路所存储的数据的数量,产生工作频率。第二传输接口耦接处理电路,用以输出显示数据于显示装置。

- 1.一种控制电路,其特征在于,耦接于一图像获取装置与一显示装置之间,该图像获取装置根据一工作频率输出多个图像数据,该控制电路包括:

- 一第一传输接口, 耦接该图像获取装置, 用以接收所述多个图像数据;

- 一存储电路,耦接该第一传输接口,用以接收并存储所述多个图像数据;

- 一处理电路,获取该存储电路所存储的所述多个图像数据,用以产生多个显示数据,并根据该存储电路所存储的数据的数量,产生该工作频率;以及

- 一第二传输接口, 耦接该处理电路, 用以输出所述多个显示数据于该显示装置:

其中当该存储电路所储存的数据的数量大于一第一临界值时,该处理电路降低该工作频率,用以放慢该图像获取装置输出该图像数据的速度,当该存储电路所储存的数据的数量小于一第二临界值时,该处理电路增加该工作频率,用以加快该图像获取装置输出该图像数据的速度,该第一临界值大于该第二临界值。

- 2.如权利要求1所述的控制电路,其特征在于,该图像获取装置转换该工作频率,用以产生一像素频率,并提供该像素频率于该处理电路,该处理电路根据该像素频率接收所述多个图像数据,并将所述多个图像数据写入该存储电路。

- 3. 如权利要求2所述的控制电路,其特征在于,当该处理电路降低该工作频率时,该图像获取装置降低该像素频率,当该处理电路增加该工作频率时,该图像获取装置增加该像素频率。

- 4.如权利要求1所述的控制电路,其特征在于,当该存储电路所存储的数据的数量大于一第三临界值或是小于一第四临界值时,该处理电路暂停获取该存储电路所存储的所述多个图像数据,该第三临界值大于该第一临界值,该第四临界值小于该第二临界值。

- 5.如权利要求4所述的控制电路,其特征在于,当该存储电路所存储的数据的数量大于该第三临界值或是小于该第四临界值时,该处理电路通过该第二传输接口,输出一预设数据于该显示装置。

- 6. 如权利要求1所述的控制电路,其特征在于,更包括:

- 一计数电路,具有一计数值,其中该处理电路根据该存储电路所存储的数据的数量调整该计数值,并根据该计数值调整该工作频率。

- 7.一种控制方法,其特征在于,适用于一控制电路,并包括

接收多个图像数据,其中所述多个图像数据是由一图像获取装置所提供:

存储所述多个图像数据于一存储电路中;

获取该存储电路所存储的所述多个图像数据,用以产生多个显示数据;

输出所述多个显示数据于一显示装置;以及

根据该存储电路所存储的数据的数量,调整该图像获取装置的一工作频率;

其中当该存储电路所储存的数据的数量大于一第一临界值时,该处理电路降低该工作频率,用以放慢该图像获取装置输出该图像数据的速度,当该存储电路所储存的数据的数量小于一第二临界值时,该处理电路增加该工作频率,用以加快该图像获取装置输出该图像数据的速度,该第一临界值大于该第二临界值。

8. 如权利要求7所述的控制方法,其特征在于,更包括:

接收一像素频率:以及

根据该像素频率接收所述多个图像数据;

其中当该工作频率被降低时,该像素频率为一第三数值,当该工作频率被增加时,该像素频率为一第四数值,该第三数值小于该第四数值。

# 控制电路及其控制方法

### 技术领域

[0001] 本发明是有关于一种控制电路,特别是有关于一种耦接于一图像获取装置与一显示装置之间的控制电路。

## 背景技术

[0002] 在目前的图像处理过程中,通常利用微处理器单元(MPU)。然而,现今微控制器单元(MCU)效能越来越强大,渐渐可进行图像处理。不过,微控制器单元的内部存储空间有限,无法存储大量的图像数据。

## 发明内容

[0003] 本发明提供一种控制电路,耦接于一图像获取装置与一显示装置之间。图像获取装置根据一工作频率输出多个图像数据。控制电路包括一第一传输接口、一存储电路、一处理电路以及一第二传输接口。第一传输接口耦接图像获取装置,用以接收图像数据。存储电路耦接第一传输接口,用以接收并存储图像数据。处理电路获取存储电路所存储的图像数据,用以产生多个显示数据,并根据存储电路所存储的数据的数量,产生工作频率。第二传输接口耦接处理电路,用以输出显示数据于显示装置。

[0004] 本发明另提供一种控制方法,适用于一控制电路,并包括接收多个图像数据,其中所述多个图像数据是由一图像获取装置所提供;存储所述多个图像数据于一存储电路中;获取该存储电路所存储的所述多个图像数据,用以产生多个显示数据;输出所述多个显示数据于一显示装置;以及根据该存储电路所存储的数据的数量,调整该图像获取装置的一工作频率。

[0005] 本发明的控制方法可经由本发明的控制电路来实作,其为可执行特定功能的硬件或固件,亦可以通过程序代码方式收录于一纪录媒体中,并结合特定硬件来实作。当程序代码被电子装置、处理器、电脑或机器载入且执行时,电子装置、处理器、电脑或机器变成用以实行本发明的控制电路或操作系统。

#### 附图说明

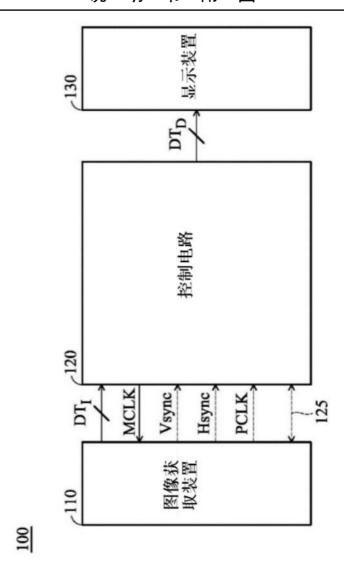

[0006] 图1为本发明的操作系统的示意图。

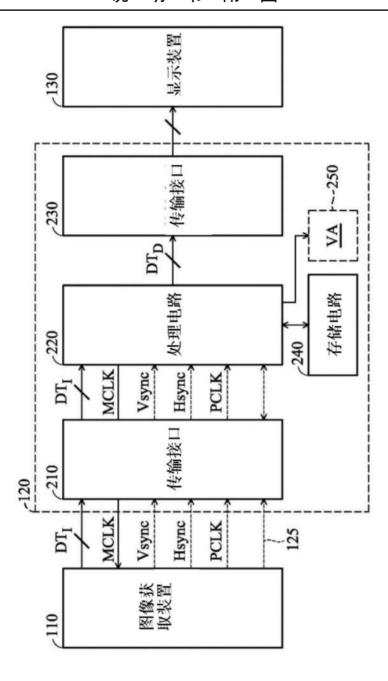

[0007] 图2为本发明的控制电路的一可能示意图。

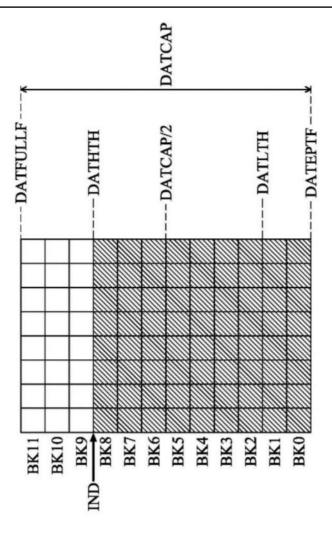

[0008] 图3为存储电路的示意图。

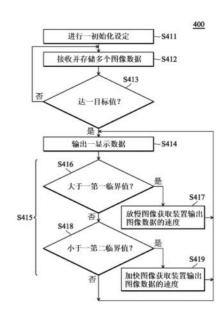

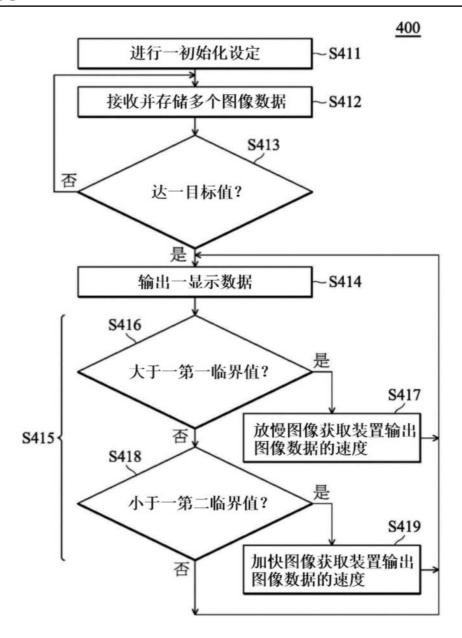

[0009] 图4为本发明的控制方法的一可能流程示意图。

[0010] 图5为本发明的控制方法的另一可能流程示意图。

[0011] 附图标记:

[0012] 100:操作系统; 110:图像获取装置;

[0013] 120:控制电路; 130:显示装置;

[0014] 125:集成电路汇流排; 210、230:传输接口;

[0015] 220:处理电路; 240:存储电路;

[0016] 250:计数电路; 400、500:控制方法;

[0017] MCLK:工作频率; VA:计数值;

[0018] DTI:图像数据; PCLK:像素频率;

[0019] DTD:显示数据; Hsync:水平同步信号;

[0020] Vsync:垂直同步信号; BK0~BK11:区块;

[0021] IND:指标; DATCAP/2:目标值;

[0022] DATHTH、DATLTH:临界值;

[0023] DATCAP:记忆空间

[0024] DATFULLF、DATEPTF:边界值;

[0025] S411~S419、S511~S521:步骤。

## 具体实施方式

[0026] 为让本发明的目的、特征和优点能更明显易懂,下文特举出实施例,并配合所附图式,做详细的说明。本发明说明书提供不同的实施例来说明本发明不同实施方式的技术特征。其中,实施例中的各元件的配置是为说明之用,并非用以限制本发明。另外,实施例中图式标号的部分重复,是为了简化说明,并非意指不同实施例之间的关联性。

[0027] 图1为本发明的操作系统的示意图。如图所示,操作系统100包括一图像获取装置110、一控制电路120以及一显示装置130。图像获取装置110根据一工作频率MCLK,传感外界的光线,并根据传感结果,产生图像数据DT<sub>I</sub>。在一可能实施例中,图像获取装置110转换工作频率MCLK,用以产生一像素频率PCLK,并根据像素频率PCLK输出图像数据DT<sub>I</sub>。在本实施例中,图像获取装置110是以一串列方式(serial communication)输出图像数据DT<sub>I</sub>,但并非用以限制本发明。在其它实施例中,图像获取装置110是以一并列方式(parallel communication)输出图像数据DT<sub>I</sub>。另外,本发明并不限定图像获取装置110的电路架构。在一可能实施例中,图像获取装置110包括一感光耦合元件(Charge Coupled Device;CCD)或是一互补型金属氧化物半导体(Complementary Metal-Oxide Semiconductor;CMOS)传感元件。

[0028] 控制电路120耦接于图像获取装置110与显示装置130之间,接收并存储图像数据  $DT_{I}$ 。在本实施例中,当控制电路120存储的图像数据 $DT_{I}$ 的数量达一目标值时,控制电路120根据本身存储的图像数据 $DT_{I}$ 产生显示数据 $DT_{D}$ 于显示装置130。在一可能实施例中,控制电路120直接将图像数据 $DT_{I}$ 作为显示数据 $DT_{D}$ 输出于显示装置130。在此例中,每当控制电路120输出一显示数据 $DT_{D}$ 时,控制电路120删除相对应的图像数据 $DT_{I}$ 。为方便说明,以下内容是假设控制电路120直接将图像数据 $DT_{I}$ 作为显示数据 $DT_{D}$ ,但并非用以限制本发明。在其它实施例中,控制电路120处理(如转换)图像数据 $DT_{I}$ ,用以产生显示数据 $DT_{D}$ 。

[0029] 在控制电路120输出显示数据DT<sub>D</sub>的同时,控制电路120仍持续接收并存储图像数据DT<sub>I</sub>。当控制电路120存储的图像数据DT<sub>I</sub>的数量大于一第一临界值时,控制电路120降低工作频率MCLK,用以放慢图像获取装置110输出图像数据DT<sub>I</sub>的速度。然而,当控制电路120存储的图像数据DT<sub>I</sub>的数量小于一第二临界值时,控制电路120提高工作频率MCLK,用以加快图像获取装置110输出图像数据DT<sub>I</sub>的速度。在本实施例中,控制电路120利用串列方式输出

显示数据 $DT_D$ ,但并非用以限制本发明。在其它实施例中,控制电路120利用并列方式输出显示数据 $DT_D$ 。本发明并不限定控制电路120的架构。在一可能实施例中,控制电路120是为一微控制单元 (MCU)。

[0030] 在其它实施例中,控制电路120根据像素频率PCLK接收图像数据DT<sub>I</sub>。本发明并不限定工作频率MCLK与像素频率PCLK之间的关系。在一可能实施例中,当控制电路120降低工作频率MCLK时,像素频率PCLK也随之下降。因此,控制电路120接收图像数据DT<sub>I</sub>的速度变慢。在此例中,当控制电路120增加工作频率MCLK时,像素频率PCLK也随之上升。因此,控制电路120接收图像数据DT<sub>I</sub>的速度变快。

[0031] 本发明并不限定控制电路120如何判断本身所存储的图像数据DT<sub>I</sub>的数量是否达一目标值。在一可能实施例中,每当图像获取装置110输出一图像数据DT<sub>I</sub>后,图像获取装置110致能一水平同步信号Hsync。因此,控制电路120只要根据水平同步信号Hsync被致能的次数,便可得知图像数据DT<sub>I</sub>的数量是否达一目标值。在另一可能实施例中,控制电路120是根据内部被图像数据DT<sub>I</sub>填满的记忆区块的数量,得知图像数据DT<sub>I</sub>的数量是否达一目标值。[0032] 本发明并不限定图像数据DT<sub>I</sub>的格式。在一可能实施例中,每一图像数据DT<sub>I</sub>是一列图像数据。在此例中,当控制电路120根据一图像数据DT<sub>I</sub>输出一显示数据DT<sub>D</sub>时,显示装置130的一列像素根据显示数据DT<sub>D</sub>而呈现画面。本发明并不限定控制电路120接收图像数据DT<sub>I</sub>的速度以及输出显示数据DT<sub>D</sub>的速度。控制电路120接收图像数据DT<sub>I</sub>的速度可能相同或不同于输出显示数据DT<sub>D</sub>的速度。

[0033] 在一可能实施例中,每当控制电路120接收一图像数据DT<sub>I</sub>时,控制电路120增加一计数值。每当控制电路120输出一显示数据DT<sub>D</sub>时,控制电路120减少该计数值。在此例中,计数值表示控制电路120所存储的图像数据DT<sub>I</sub>的数量。在其它实施例中,控制电路120每隔一固定时间,读取计数值,并根据计数值调整工作频率MCLK。

[0034] 当计数值大于一高临界值(或称第一临界值)时,表示控制电路120所存储的图像数据DT<sub>I</sub>的数量偏多。因此,控制电路120降低工作频率MCLK,用以减慢图像获取装置110输出图像数据DT<sub>I</sub>的速度。然而,当计数值小于一低临界值(或称第二临界值)时,表示控制电路120所存储的图像数据DT<sub>I</sub>的数量偏少。因此,控制电路120增加工作频率MCLK,用以加快图像获取装置110输出图像数据DT<sub>I</sub>的速度。

[0035] 在其它实施例中,每当图像获取装置110所输出的图像数据DT<sub>I</sub>的数量达一预设值时,图像获取装置110致能一垂直同步信号Vsync。举例而言,当图像获取装置110输出240笔图像数据DT<sub>I</sub>后,图像获取装置110便致能垂直同步信号Vsync。在此例中,每当图像获取装置110输出一笔图像数据DT<sub>I</sub>时,图像获取装置110致能水平同步信号Vsync。

[0036] 在一些实施例中,控制电路120通过一集成电路汇流排 (Inter-Integrated Circuit;  $I^2C$ ) 125与图像获取装置110沟通。在此例中,控制电路120可能根据本身事先存储的设定值,并通过集成电路汇流排125设定图像获取装置110输出彩色或黑色的图像数据,或是设定图像获取装置110每秒输出画面的张数,如60张、30张或1张画面。在一可能实施例中,每1张画面是由多个笔(如240笔)图像数据DT<sub>I</sub>所构成。在一些实施例中,控制电路120通过集成电路汇流排125设定图像数据DT<sub>I</sub>的解析度。举例而言,控制电路120可能要求图像获取装置110输出解析度为320X240或640X480的图像数据,以符合显示装置130的解析度。

[0037] 显示装置130根据显示数据DTn呈现画面。在一可能实施例中,显示装置130具有一

i80接口(未显示)或是一串行外设接口(serial peripheral interface),用以接收显示数据DT<sub>D</sub>。本发明并不限定显示装置130的种类。在一可能实施例中,显示装置130是为一非自发光显示器(non-self-luminous display),如液晶显示器(LCD display)。在其它实施例中,显示装置130是为一自发光显示器(self-luminous display),如有机发光二极管显示器(Organic Light Emitting Diode Display;OLED display)。

[0038] 图2为本发明的控制电路的一可能示意图。如图所示,控制电路120包括传输接口210、230、一处理电路220以及一存储电路240。传输接口210耦接图像获取装置110,用以传送图像数据DT<sub>I</sub>、工作频率MCLK、垂直同步信号Vsync、水平同步信号Hsync及像素频率PCLK。另外,传输接口210具有集成电路汇流排125。

[0039] 处理电路220通过传输接口210接收图像数据 $DT_I$ ,并将图像数据 $DT_I$ 写入存储电路240。在本实施例中,当存储电路240所存储的图像数据 $DT_I$ 的数量达一目标值时,处理电路220开始依序读取并输出存储电路240所存储的图像数据。

[0040] 传输接口230传送显示数据DT<sub>D</sub>于显示装置130。在本实施例中,传输接口230是以串列方式接收显示数据DT<sub>D</sub>,并以串列方式输出显示数据DT<sub>D</sub>于显示装置130,但并非用以限制本发明。在其它实施例中,传输接口230可能以并列方式接收处理电路220所产生显示数据DT<sub>D</sub>。

[0041] 存储电路240耦接处理电路220,用以存储图像数据DT<sub>I</sub>。在本实施例中,存储电路240通过处理电路220,间接地接收图像数据DT<sub>I</sub>,但并非用以限制本发明。在其它实施例中,存储电路240直接耦接传输接口210,用以直接接收图像数据DT<sub>I</sub>。本发明并不限定存储电路240的种类。在一可能实施例中,存储电路240是为一静态随机存取存储器(SRAM)。

[0042] 图3是为存储电路240的示意图。如图所示,存储电路240具有区块BK0~BK11,用以存储多个图像数据DT<sub>I</sub>。在其它实施例中,存储电路240具有其它的区块,用以存储其它信息。本实施例中,区块BK0~BK11的每一者用以存储一笔图像数据。在此例中,区块BK0~BK11的每一者所存储的图像数据是为显示装置130的一列像素所需的数据。在其它实施例中,每一区块所存储的图像数据可供多个列像素使用,或是多个区块所存储的图像数据可供单一列像素使用。

[0043] 在本实施例中,假设存储电路240存储九笔图像数据DT<sub>I</sub>,并且每一笔图像数据DT<sub>I</sub>可填满一区块。因此,区块BK0~BK8为填满状态,而区块BK9~BK11为未填满状态。由于区块BK0~BK8为填满状态,故指标IND指向区块BK8。在此例中,当指标IND指向区块BK5时,表示图像数据DT<sub>I</sub>的数量已达目标值DATCAP/2。因此,处理电路220开始读取并输出存储电路240所存储的图像数据DT<sub>I</sub>。

[0044] 举例而言,处理电路220可能先读取区块BK0所存储的图像数据,并将区块BK0所存储的图像数据作为第一笔显示数据DT<sub>D</sub>输出于显示装置130。显示装置130里的第一列像素根据第一笔的显示数据DT<sub>D</sub>呈现画面。此时,指标值IND可能往下移动。然而,由于处理电路220持续写入图像数据DT<sub>T</sub>至存储电路240,故指标值IND可能逐渐往上移动至区块BK8。

[0045] 当指标值IND指向区块BK8时,表示存储电路240所存储的图像数据DT<sub>I</sub>的数量已达高临界值DATHTH。因此,处理电路220降低工作频率MCLK,用以命令图像获取装置110减慢输出图像数据DT<sub>I</sub>的速度。然而,当指标值IND指向区块BK1时,表示存储电路240所存储的图像数据DT<sub>I</sub>的数量已低于低临界值DATLTH。因此,处理电路220提高工作频率MCLK,用以命令图

像获取装置110增加输出图像数据DT<sub>I</sub>的速度。当指标IND位于高临界值DATHTH与低临界值DATLTH之间时,处理电路220不调整工作频率MCLK。在一可能实施例中,目标值DATCAP/2是为存储电路240用以存储列图像数据的记忆空间DATCAP的一半。

[0046] 由于处理电路220在存储电路240的图像数据的数量达一目标值后,便开始读取存储电路240所存储的图像数据,用以提供显示数据DT<sub>D</sub>于显示装置130,故存储电路240的记忆空间不需太大。再者,由于处理电路220动态地调整工作频率MCLK,故可适当地控制存储电路240所存储的列图像数据的数量,而不会遗失图像数据DT<sub>T</sub>。

[0047] 在一些实施例中,当处理电路220检测到一异常情况发生时,处理电路220执行一特定动作。举例而言,当指标IND大于一边界值DATFULLF(如称第三临界值),表示图像获取装置110输出图像数据DT<sub>I</sub>的速度太快,存储电路240来不及存储图像数据DT<sub>I</sub>。因此,处理电路220可能在输出BK0~BK11所存储的列图像数据后,暂停提供显示数据DT<sub>D</sub>于显示装置130,直到垂直同步信号Vsync被致能。在此例中,由于处理电路220暂停刷新显示装置130的画面,故显示装置130的某些列像素可能呈现上一画面。然而,在垂直同步信号Vsync被致能后,处理电路220开始输出显示数据DT<sub>D</sub>于显示装置130,因此,使用者不易观察到显示装置130呈现不正确的画面。在其它实施例中,当存储电路240来不及存储图像数据DT<sub>I</sub>时,处理电路220可能输出特定显示数据于显示装置130,用以让显示装置130的某些列像素呈现黑画面。

[0048] 同样地,当指标IND低于另一边界值DATEPTF (如称第四临界值),表示图像获取装置110输出图像数据DT<sub>I</sub>的速度太慢,存储电路240未存储完整的图像数据DT<sub>I</sub>。因此,处理电路220无法提供正确的显示数据DT<sub>D</sub>于显示装置130。此时,处理电路220可能暂停获取区块BK0~BK11,并暂停刷新显示装置130的画面。在此例中,显示装置130可能呈现上一画面。在其它实施例中,处理电路220可能提供一预设图像于呈显示装置130,用以让显示装置130暂时呈现黑画面。此时,处理电路220可能增加工作频率MCLK,用以加快图像获取装置110输出图像数据DT<sub>I</sub>的速度。由于图像数据DT<sub>I</sub>的数量很快达目标值DATCAP/2,故处理电路220可立即产生显示数据DT<sub>D</sub>于显示置130。由于视觉暂留的影响,并且处理电路220即时提供显示数据DT<sub>D</sub>,故使用者不易观察到显示装置130呈现不正确的画面。

[0049] 请参考图2,控制电路120包括一计数电路250。计数电路250具有一计数值VA。计数值VA相当于图3的指标IND。在此例中,处理电路220根据存储电路240所存储的图像数据DT<sub>I</sub>的数量,调整计数值VA,并根据计数值VA调整工作频率MCLK。在另一可能实施例中,计数值VA与水平同步信号Hsync被致能的次数有关。此例中,每当图像获取装置110致能水平同步信号Hsync时,处理电路220增加计数值VA。每当处理电路220产生一显示数据DT<sub>D</sub>时,处理电路220减少计数值VA。

[0050] 本发明并不限定处理电路220何时调整工作频率MCLK。在一可能实施例中,每当水平同步信号Hsync被致能时,处理电路220便根据计数值VA调整工作频率MCLK。在其它实施例中,当水平同步信号Hsync被致能的次数达一预设值时,处理电路220便读取计数值VA。

[0051] 图4为本发明的控制方法的一可能流程示意图。本发明的控制方法400适用于一控制电路(如图2的控制电路200),用以调整一图像获取装置输出图像数据的速度。在此例中,控制电路不需设置大容量的存储器存储图像数据。因此,可增加控制电路的可使用空间,并减少元件成本,因容量愈大,存储器愈贵。

[0052] 首先,进行一初始化设定(步骤S411)。在一可能实施例中,步骤S411是初始化控制电路内部的多个旗标。所述多个旗标用以提供不同的预设值,如图3的DATFULLF、DATHTH、DATCAP/2、DATLTH及DATEPTF。另外,控制电路可能根据所述多个旗标,设定外部的图像获取装置。在一可能实施例中,所述多个旗标的数量可能事先烧录在控制电路中,故可省略步骤S411。

[0053] 接收并存储多个图像数据(步骤S412)。在一可能实施例中,所述多个图像数据是由一图像获取装置(如图1所示的110)所提供。图像获取装置可能包括CCD或是CMOS传感元件。在一些实施例中,每一笔图像数据是为一列图像数据,用以供显示装置的一列像素使用。在一可能实施例中,步骤S412是将所述多个图像数据存储于一存储电路中。该存储电路可能是为一挥发性存储器。

[0054] 判断被存储的图像数据的数量是否达一目标值(步骤S413)。在一可能实施例中,该目标值是为步骤S411所初始化的一旗标的数值,如图3的目标值DATCAP/2。本发明并不限定步骤S413如何判断被存储的图像数据的数量是否达一目标值。在一可能实施例中,每当图像获取装置致能一水平同步信号时,一计数值逐渐增加。因此,藉由该计数值,便可得知所存储的图像数据的数量是否达一目标值。在其它实施例中,步骤S413是根据被图像数据填满的记忆区块的数量,判断被存储的图像数据的数量是否达一目标值。

[0055] 当被存储的图像数据的数量未达目标值时,回到步骤S412,继续接收并存储图像数据。当存储的图像数据的数量达目标值时,输出一显示数据于一显示装置(步骤S414)。在一可能实施例中,步骤S414是将存储电路所存储的图像数据作为显示数据输出于显示装置。在此例中,每当步骤S414输出一显示数据后,上述计数值会被减少。不过,同时只要有一图像数据被存储,上述计数值会被增加。

[0056] 根据所存储的图像数据的数量,调整图像获取装置输出图像数据的速度(步骤 S415)。在一可能实施例中,当图像获取装置致能一水平同步信号时,才会触发步骤S415。举例而言,在步骤S414后,如果水平同步信号未被触发,则不进行步骤S415。在其它实施例中,当水平同步信号被致能的次数达一预设值时,才会进行步骤S415。

[0057] 在本实施例中,步骤S415包括步骤S416~S419。首先,判断所存储的图像数据的数量是否大于一第一临界值(步骤S416)。如果所存储的图像数据的数量大于第一临界值时,放慢图像获取装置输出图像数据的速度(步骤S417)。在一可能实施例中,步骤S417是降低图像获取装置的工作频率。在此例中,图像获取装置根据减少的工作频率,减少一像素频率。然而,回到步骤S414,继续读取并转换所存储的图像数据。

[0058] 如果所存储的图像数据的数量未大于第一临界值时,判断所存储的图像数据的数量是否小于一第二临界值(步骤S418)。在本实施例中,第二临界值小于第一临界值。当所存储的图像数据的数量小于第二临界值时,加快图像获取装置输出图像数据的速度(步骤S419)。在一可能实施例中,步骤S419是加快图像获取装置的工作频率。在此例中,图像获取装置可能根据加快的工作频率,增加像素频率。然而,回到步骤S414,继续读取并转换所存储的图像数据。

[0059] 在本实施例中,在开始接收图像数据(步骤S412)后,持续接收图像数据。因此,存储电路所存储的图像数据的数量可维持在一预设范围内。

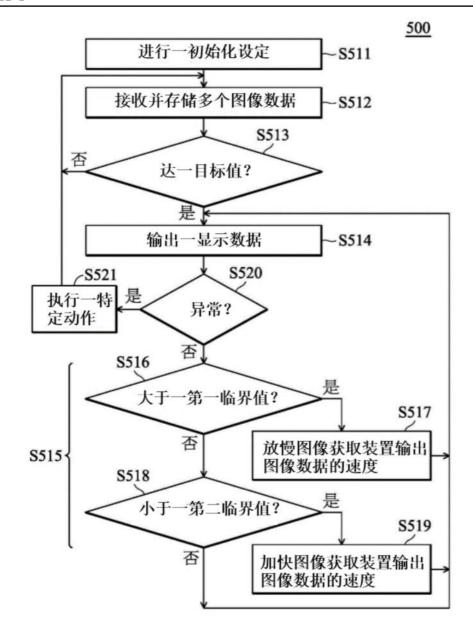

[0060] 图5为本发明的控制方法的另一流程示意图。图5相似于图4,不同之处在于,图5的

控制方法500多了步骤S520及521。由于步骤S511~S519相似于步骤S411~S419,故不再赘述。在本实施例中。步骤S520是判断一异常情况是否发生。当异常情况发生时,执行一特定动作(步骤S521),然后回到步骤S512,继续接收并存储图像数据。当异常情况未发生时,执行步骤S515。

[0061] 在一可能实施例中,异常情况是为,存储电路所存储的数据的数量大于一第三临界值或是小于一第四临界值,其中第三临界值大于第一临界值,第四临界值小于第二临界值。举例而言,当存储电路所存储的图像数据的数量大于第三临界值时,表示图像获取装置输出图像数据的速度太快了,存储电路来不及存储图像数据。在其它实施例中,当存储电路所存储的图像数据的数量小于第四临界值时,表示图像获取装置输出图像数据的速度太慢了,存储电路里的图像数据不足以驱动显示装置。

[0062] 当上述异常情况发生时,执行一特定动作,如输出一预设数据于显示装置。在此例中,显示装置的像素可能呈现黑画面(对应于预设数据)。由于视觉暂留的图像,使用者不会察觉到黑画面。在其它实施例中,特定动作可能暂停刷新显示装置,也就是不输出任何信号于显示装置。因此,显示装置呈现先前的画面。由于本发明的控制电路将适当地调整(加快或放慢)图像获取装置输出图像数据的速度,故可即时刷新显示装置,以避免数据过载(overrun)或是欠载(underrun)。

[0063] 本发明的控制方法,或特定型态或其部份,可以以程序代码的型态存在。程序代码可存储于实体媒体,如软盘、光碟片、硬盘、或是任何其他机器可读取(如电脑可读取)存储媒体,亦或不限于外在形式的电脑程式产品,其中,当程序代码被机器,如电脑载入且执行时,此机器变成用以参与本发明的控制电路。程序代码也可通过一些传送媒体,如电线或电缆、光纤、或是任何传输型态进行传送,其中,当程序代码被机器,如电脑接收、载入且执行时,此机器变成用以参与本发明的控制路。当在一般用途处理单元实作时,程序代码结合处理单元提供一操作类似于应用特定逻辑电路的独特装置。

[0064] 除非另作定义,在此所有词汇(包含技术与科学词汇)均属本发明所属技术领域中技术人员的一般理解。此外,除非明白表示,词汇于一般字典中的定义应解释为与其相关技术领域的文章中意义一致,而不应解释为理想状态或过分正式的语态。

[0065] 虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰。举例来,本发明实施例所述的系统、装置或是方法可以硬件、软件或硬件以及软件的组合的实体实施例加以实现。因此本发明的保护范围当视权利要求范围所界定者为准。

图1

图2

图3

图4

图5