### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5589329号 (P5589329)

(45) 発行日 平成26年9月17日(2014.9.17)

(24) 登録日 平成26年8月8日(2014.8.8)

| (51) Int.Cl. | FI                           |                          |

|--------------|------------------------------|--------------------------|

| HO1L 29/812  | ? <b>(2006.01)</b> HO1L      | 29/80 H                  |

| HO1L 29/778  | <b>3 (2006.01)</b> HO1L      | 29/91 H                  |

| HO1L 21/33   | <b>3 (2006.01)</b> HO1L      | 29/78 3 O 1 B            |

| HO1L 29/868  | 3 (2006.01)                  |                          |

| HO1L 29/86   | l (2006.01)                  |                          |

|              |                              | 請求項の数 13 (全 19 頁) 最終頁に続く |

| (21) 出願番号    | 特願2009-219254 (P2009-219254) | (73) 特許権者 000241463      |

| (22) 出願日     | 平成21年9月24日 (2009.9.24)       | 豊田合成株式会社                 |

| (65) 公開番号    | 特開2011-71206 (P2011-71206A)  | 愛知県清須市春日長畑1番地            |

||(74)代理人 100087723

弁理士 藤谷 修

(72) 発明者 岡 徹

愛知県西春日井郡春日町大字落合字長畑1

番地 豊田合成株式会社内

審査官 早川 朋一

最終頁に続く

(54) 【発明の名称】 1 1 1 族窒化物半導体からなる半導体装置、電力変換装置

平成23年4月7日 (2011.4.7) 平成24年2月21日 (2012.2.21)

# (57)【特許請求の範囲】

### 【請求項1】

(43) 公開日

審査請求日

| | | 族窒化物半導体からなる第1キャリア走行層と、

前記第1キャリア走行層の一部領域上に位置し、選択的に再成長されたIII 族窒化物半導体からなる第2キャリア走行層と、

前記第2キャリア走行層上に接して位置し、<u>前記第2キャリア走行層に続けて</u>選択的に再成長された、前記第2キャリア走行層よりもバンドギャップの大きなIII 族窒化物半導体からなるキャリア供給層とを、

#### を備え、

前記キャリア供給層上に、前記キャリア供給層よりもバンドギャップが小さく、<u>前記キャリア供給層に続けて</u>選択的に再成長されたIII 族窒化物半導体からなる<u>キャリア走行層としての第1層と</u>、その層よりもバンドギャップが大きく、<u>前記第1層に続けて</u>選択的に再成長されたIII 族窒化物半導体からなる<u>キャリア供給層としての第2層</u>との対が、さらに1対ないし複数対形成されており、

前記第2キャリア走行層と前記キャリア供給層とのヘテロ接合界面であって前記第2キャリア走行層側、および前記第1層と前記第2層とのヘテロ接合界面であって前記第1層側に2次元電子ガスが形成されており、

前記第2キャリア走行層、前記キャリア供給層、および前記第1層と前記第2層との対は、前記第1キャリア走行層上であって、互いに離間する2つの領域に形成されており、

2つの領域の一方の領域の最上層の前記第2層上に設けられ、前記第1層、および前記

### 第2キャリア走行層と電気的に接続した第1電極と、

2 つの領域の他方の領域の最上層の前記第 2 層上に設けられ、前記第 1 層、および前記 第 2 キャリア走行層と電気的に接続した第 2 電極と、

前記2つの領域に挟まれた領域の前記第1キャリア走行層上と、前記2つの領域における第2キャリア走行層、キャリア供給層、および前記第1層と前記第2層との対の離間して向かい合う側の側端面と、に形成された絶縁膜と、

前記絶縁膜上に形成された制御電極と、

を備えていることを特徴とする半導体装置。

ことを特徴とする請求項1に記載の半導体装置。

#### 【請求項2】

前記絶縁膜は、その一部または全部が複数の層からなることを特徴とする<u>請求項1</u>に記載の半導体装置。

#### 【請求項3】

前記絶縁膜は、AlNからなる単層、または、その一部または全部がSiO $_2$  / ZrO $_2$  、SiO $_2$  / Al $_2$  O $_3$  、SiO $_2$  / HfO $_2$  、Al $_2$  O $_3$  / ZrO $_2$  、SiN/SiO $_2$  / ZrO $_2$  、SiO $_2$  / Al $_2$  O $_3$  / HfO $_2$  からなる複層である、

# 【請求項4】

前記絶縁膜は、<u>最上層の前記第2層上</u>にも形成されており、前記制御電極は、前記絶縁膜を介して<u>最上層の前記第2層上</u>に延伸していることを特徴とする<u>請求項1ないし請求項</u>3のいずれか1項に記載の半導体装置。

#### 【請求項5】

前記第1キャリア走行層上に位置する前記絶縁膜と、<u>最上層の前記第2層上</u>に位置する前記絶縁膜とは、膜質が異なることを特徴とする<u>請求項1ないし請求項4</u>のいずれか1項に記載の半導体装置。

### 【請求項6】

前記絶縁膜の厚さは、前記第2キャリア走行層の厚さよりも薄いことを特徴とする<u>請求</u>項1ないし請求項5のいずれか1項に記載の半導体装置。

#### 【請求項7】

前記第1電極と前記第2電極は、<u>前記第1層、および</u>前記第2キャリア走行層にオーミック接触していることを特徴とする<u>請求項1ないし請求項6</u>のいずれか1項に記載の半導体装置。

# 【請求項8】

前記第1電極と前記第2電極のどちらか一方と、前記制御電極とが電気的に接続されていることを特徴とする請求項1ないし請求項7のいずれか1項に記載の半導体装置。

### 【請求項9】

前記第2キャリア走行層から離れた領域でのキャリアの走行を抑止するキャリア走行抑止層をさらに有し、前記キャリア走行抑止層上に前記第1キャリア走行層が位置する、ことを特徴とする請求項1ないし請求項8のいずれか1項に記載の半導体装置。

#### 【請求項10】

前記キャリア走行抑止層は、前記第1キャリア走行層とは異なる伝導型のIII 族窒化物 40 半導体からなることを特徴とする請求項9に記載の半導体装置。

#### 【請求項11】

前記キャリア走行抑止層は、前記第1キャリア走行層よりもバンドギャップが大きいII I族窒化物半導体からなることを特徴とする<u>請求項9または請求項10</u>に記載の半導体装置

# 【請求項12】

前記キャリア走行抑止層は、前記キャリア走行抑止層よりもバンドギャップが大きいII I族窒化物半導体からなる層上に位置する、ことを特徴とする<u>請求項9または請求項10</u> に記載の半導体装置。

# 【請求項13】

30

10

20

請求項1ないし請求項12のいずれか1項に記載の半導体装置を少なくとも1つ以上用いて構成された電力変換装置。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、III 族窒化物半導体からなる半導体装置に関するものであり、特に、オン抵抗が低減されたHFET(高電子移動度トランジスタ)やダイオードなどの半導体装置に関する。また、それらのIII 族窒化物半導体からなる半導体装置を用いた電力変換装置に関する。

# 【背景技術】

[0002]

III 族窒化物半導体は発光素子の材料として広く用いられているが、電子移動度が高く Siの約10倍の破壊電界強度を有することからパワーデバイスの材料としても期待されている。そのようなパワーデバイスとして、ヘテロ接合界面に生じる2次元電子ガス(2DEG)をチャネルとして動作するHFET(高電子移動度トランジスタ)が開発されているが、GaAs系のHFETなどの従来と同様な構造でGaN系HFETを作製すると、ゲート電極に電圧を印加しない状態でオンになる特性(ノーマリオン特性)となる。しかし、ノーマリオン特性では安全性に問題があるため、ゲート電極に電圧を印加しない状態でソース・ドレイン間に電流が流れないノーマリオフを実現するためのさまざまな構造が提案されている。

#### [0003]

そのようなノーマリオフの実現が可能な構造として、たとえば特許文献1では、MIS構造のHFETにおいて、ゲート直下にキャリア供給層を形成しない構造のHFETが示されている。この構造によれば、ゲート直下の領域に2DEGが形成されないためノーマリオフ特性となる。この構造を実現するために、特許文献1では、キャリア供給層の一部をドライエッチングして除去し、キャリア走行層表面を露出させる方法が示されている。

#### [0004]

また、特許文献 2 には、キャリア走行層上に第 1 キャリア供給層を形成し、第 1 キャリア供給層上の所定の領域にマスクを形成し、マスクを形成していない第 1 キャリア供給層上に選択的に第 2 キャリア供給層を再成長させることで、 2 つの互いに離間した第 2 キャリア供給層を形成し、一方の第 2 キャリア供給層上にソース電極、他方の第 2 キャリア供給層上にドレイン電極、マスク上にゲート電極を形成する H F E T の製造方法が示されている。

【先行技術文献】

# 【特許文献】

[0005]

【特許文献1】特開2008-147593

【特許文献2】特開2009-99691

#### 【発明の概要】

【発明が解決しようとする課題】

## [0006]

しかし、特許文献 1 に示された構造を、特許文献 2 のような選択的に再成長させる方法を適用して作製しようとすると、キャリア走行層上にキャリア供給層を再成長させる際に、キャリア走行層とキャリア供給層との界面に不純物等が取り込まれてしまったり、平坦性が劣化するなどの問題が生じていた。その結果、キャリア走行層とキャリア供給層とのヘテロ接合界面に生じる 2 D E G の移動度を低下させ、オン抵抗が増加するという問題があった。

#### [0007]

そこで本発明の目的は、オン抵抗が低減されたIII 族窒化物半導体からなる半導体装置、およびその製造方法を提供することである。また、その半導体装置を用いた電力変換装

10

20

30

- -

40

置を提供することである。

【課題を解決するための手段】

#### [0008]

第1の発明は、III族窒化物半導体からなる第1キャリア走行層と、第1キャリア走行 層の一部領域上に位置し、選択的に再成長されたII族窒化物半導体からなる第2キャリ ア走行層と、第2キャリア走行層上に接して位置し、第2キャリア走行層に続けて選択的 に再成長された、第2キャリア走行層よりもバンドギャップの大きなIII族窒化物半導体 からなるキャリア供給層とを、を備え、キャリア供給層上に、キャリア供給層よりもバン ドギャップが小さく、キャリア供給層に続けて選択的に再成長されたIII族窒化物半導体 からなるキャリア走行層としての第1層と、その層よりもバンドギャップが大きく、第1 層に続けて選択的に再成長されたIII 族窒化物半導体からなるキャリア供給層としての第 2層との対が、さらに1対ないし複数対形成されており、第2キャリア走行層とキャリア 供給層とのヘテロ接合界面であって第2キャリア走行層側、および第1層と第2層とのヘ テロ接合界面であって第1層側に2次元電子ガスが形成されており、第2キャリア走行層 キャリア供給層、および第1層と第2層との対は、第1キャリア走行層上であって、互 いに離間する2つの領域に形成されており、2つの領域の一方の領域の最上層の第2層上 に設けられ、第1層、および第2キャリア走行層と電気的に接続した第1電極と、2つの 領域の他方の領域の最上層の第2層上に設けられ、第1層、および第2キャリア走行層と 電気的に接続した第2電極と、2つの領域に挟まれた領域の第1キャリア走行層上と、2 つの領域における第2キャリア走行層、キャリア供給層、および第1層と第2層との対の 離間して向かい合う側の側端面と、に形成された絶縁膜と、絶縁膜上に形成された制御電 極と、を備えていることを特徴とする半導体装置である。

<u>絶</u>縁膜は、AlNからなる単層、または、その一部または全部がSiO $_2$  / ZrO $_2$  、 SiO $_2$  / Al $_2$  O $_3$  、 SiO $_2$  / HfO $_2$  、Al $_2$  O $_3$  / ZrO $_2$  、 SiN / SiO $_2$  / ZrO $_2$  、 SiO $_2$  / Al $_2$  O $_3$  / HfO $_2$  からなる複層として<u>も良い。</u>

### [0009]

ここで本発明においてIII 族窒化物半導体とは、一般式  $Al_x$   $Ga_y$   $In_z$  N (x + y + z = 1、0 x、y、z 1) で表される半導体であり、Al、Ga、In o 一部を他の第 1 3 族元素(第 3 B 族元素)である B や Tl で置換したもの、N o 一部を他の第 1 5 族元素(第 5 B 族元素)である P、As、Sb、Bi で置換したものをも含むものとする。より一般的には、Ga を少なくとも含む Ga N、In Ga N、Al Ga N、Al Ga In N を示す。n 型不純物としては Si、p 型不純物としては Mg が通常用いられる。

#### [0010]

第1キャリア走行層、第2キャリア走行層、キャリア供給層は、いずれも単層であってもよいし、複数の層であってもよい。また、第1キャリア走行層と第2キャリア走行層は、通常は同一組成のIII 族窒化物半導体(たとえばGaN)からなるが、必ずしも同一組成である必要はない。

### [0011]

第2キャリア走行層は、ノンドープのGaNとすることが望ましい。2DEGの移動度を低下させないためである。第2キャリア走行層を複層とする場合には、その複数の層のうち、少なくともキャリア供給層と接合する層をノンドープのGaNとすることが望ましい。

### [0012]

キャリア供給層は、第2キャリア走行層よりもバンドギャップが大きい任意の組成のII I 族窒化物半導体であってよい。キャリア供給層は、ノンドープであってもよいし、 n 型不純物がドープされていてもよい。キャリア供給層上にキャップ層を有していてもよい。

### [0013]

また、キャリア供給層上に、さらにIII 族窒化物半導体からなる単層や複層が設けられて<u>いる。</u>たとえば、キャリア供給層よりもバンドギャップが小さな層と、その層よりもバンドギャップが大きな層との対を、1回または複数回繰り返して積層された構造である。

10

20

30

40

複数回繰り返して積層させる場合、各対における各バンドギャップが小さな層は、それぞれ組成が異なっていてもよいし、各バンドギャップが大きな層は、それぞれ組成が異なっていてもよい。

#### [0014]

また、本発明は、第2キャリア走行層とキャリア供給層とのヘテロ接合界面近傍であって第2キャリア走行層側に2DEGを形成し、これをチャネルとして動作する半導体装置に適用することができる。たとえばHFETやHBT(ヘテロ接合界面バイポーラトランジスタ)のほか、ダイオードなどに適用することができる。

[0015]

[0016]

10

第1電極、第2電極は、直接<u>、最上層のキャリア供給層としての第2層</u>上に接して設けられていてもよいし、<u>その第2層</u>上にキャップ層などのIII 族窒化物半導体層を介して設けられていてもよい。

[0017]

<u>上記発明において、</u>絶縁膜は、その一部または全部が複数の層からなる<u>膜としても良い</u>

[0018]

上記発明において、絶縁膜は、キャリア供給層上にも形成されており、制御電極は、絶縁膜を介してキャリア供給層上に延伸して形成されていても良い。

[0019]

20

上記発明において、第1キャリア走行層上に位置する絶縁膜と、<u>最上層の</u>キャリア供給層としての第2層上に位置する絶縁膜とは、膜質が異なっていても良い。

[0020]

ここで膜質が異なるとは、材料が異なる場合、材料が同じでも組成比が異なっている場合、結晶性や結晶構造が異なっている場合など、絶縁膜の物性が異なっていることをいう

[0021]

上記発明において、絶縁膜の厚さは、第2キャリア走行層の厚さよりも薄い<u>ことが望ま</u> しい。

[0022]

30

上記発明において、第1電極および第2電極は、第2キャリア走行層にオーミック接触 していることを特徴とする半導体装置である。

[0023]

上記発明において、第1電極と第2電極のどちらか一方と制御電極とが電気的に接続されて<u>いても良い。</u>

[0024]

上記発明において、第 2 キャリア走行層から離れた領域でのキャリアの走行を抑止する キャリア走行抑止層をさらに有し、キャリア走行抑止層上に第 1 キャリア走行層が位置す るようにしても良い。

[0025]

40

上記発明において、キャリア走行抑止層は、第1キャリア走行層とは異なる伝導型のII K 変化物半導体としても良い。

[0026]

上記発明において、キャリア走行抑止層は、第1キャリア走行層よりもバンドギャップが大きいIII 族窒化物半導体としても良い。

[0027]

上記発明において、キャリア走行抑止層は、キャリア走行抑止層よりもバンドギャップが大きいIII 族窒化物半導体からなる層上に位置するようにしても良い。

[0028]

上記発明において、キャリア供給層は、複数の層からなるものでも良い。

[0029]

[0030]

上記発明において、第 2 キャリア走行層およびキャリア供給層の側端面は、第 1 キャリア走行層から離れるにしたがって第 2 キャリア走行層およびキャリア供給層の素子面に平行な断面積が減少するような傾斜を有していても良い。

[0031]

他の発明は、上記発明の半導体装置を少なくとも1つ以上用いて構成された電力変換装置とすることができる。

[0032]

【発明の効果】

[0033]

本発明は、第2キャリア走行層とキャリア供給層とのヘテロ接合界面近傍であって第2 キャリア走行層側、および前記第1層と前記第2層とのヘテロ接合界面であって前記第1 層側に2DEGを形成し、これをチャネルとして動作する半導体装置である。第2キャリ ア走行層は、第1キャリア走行層上に続けて選択的に再成長された層であり、さらに、第 1層および第2層から成る1対ないし複数対の層は、第2キャリア走行層上に続けて選択 的に再成長された層であるから、第1キャリア走行層と第2キャリア走行層とのヘテロ接 合界面においては再成長に伴った不純物が混入しているが、第2キャリア走行層中、およ び第1層中の不純物は第1キャリア走行層から離れるにしたがって減少している。そのた め、第2キャリア走行層とキャリア供給層とのヘテロ接合界面、および第1層と第2層と のヘテロ接合界面においては、選択的な再成長に伴う不純物はほとんど見られない。また 、キャリア供給層は、第2キャリア走行層を再成長させたのちに、第2キャリア走行層に 連続して再成長させた層であるから、第2キャリア走行層とキャリア供給層とのヘテロ接 合界面の平坦性は、直接第1キャリア走行層上にキャリア供給層を再成長させた場合の第 1キャリア走行層とキャリア供給層とのヘテロ接合界面よりも高くなっている。したがっ て、本発明の半導体装置によれば、再成長による平坦性の劣化や混入する不純物によって 2DEGの移動度を低下させてしまうことがなく、オン抵抗の低減を図ることができる。

<u>また、</u>複数の2DEG層を形成することができるので、さらに低いオン抵抗で動作可能な半導体装置を実現することができる。

[0034]

ま<u>た、本</u>発明は第1、第2電極間の導通を制御電極によって制御する半導体装置、たとえばHFETに適用することができ、オン抵抗の低い半導体装置を実現することができる

[0035]

また<u>、制</u>御電極を絶縁膜を介してキャリア供給層上にも形成<u>しているので、</u>第2キャリア走行層およびキャリア供給層の側端面と絶縁膜との界面に、より多くの電子を蓄積することができ、制御電極の下方に位置する2DEGの濃度をより高くすることができる。その結果、オン抵抗をさらに低減することができる。

[0036]

また<u>、絶</u>縁膜の一部または全部を複数の層で構成してもよく、ま<u>た、</u>第1キャリア走行 40層上に位置する絶縁膜と<u>最上層の</u>キャリア供給層<u>としての第2層</u>上に位置する絶縁膜とで膜質が異なるようにしてもよい。

[0037]

また<u>、第</u>2キャリア走行層およびキャリア供給層の側端面と絶縁膜との界面に、より多くの電子を蓄積することができ、オン抵抗をさらに低減することができる。

[0038]

また<u>、第1電極と前記第2電極を、第1層、および第2キャリア走行層にオーミック接</u>触させることで、半導体装置のオン抵抗をさらに低減することができる。

[0039]

また、第1電極と第2電極のどちらか一方と制御電極とを短絡させた構成のダイオード

10

20

30

にも適用することができ、オン電圧が低く、耐圧の高いダイオードを実現することができる。

### [0040]

また<u>、キャリア走行抑止層を設けることで、第2キャリア走行層とキャリア供給層との</u>ヘテロ接合界面から離れた領域を電流が流れることを抑制することができ、オフ動作時のリーク電流を低減することができる。

- [0041]

- [0042]

- [0043]

- [0044]

また<u>、本</u>発明の半導体装置を用いて電力変換装置を構成することで、低損失で高効率な電力変換装置を実現することができる。

- [0045]

- 【図面の簡単な説明】

- [0046]

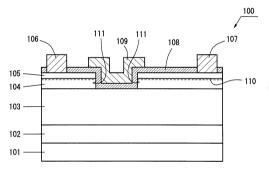

- 【図1】実施例1のHFET100の構成を示した図。

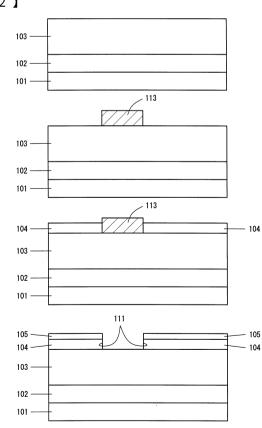

- 【図2】実施例1のHFET100の製造工程を示した図。

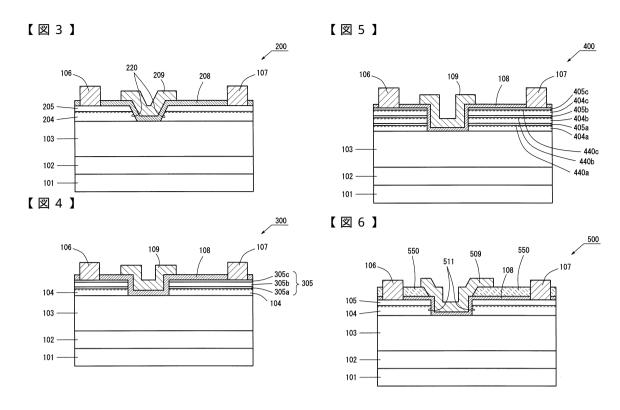

- 【図3】実施例2のHFET200の構成を示した図。

- 【図4】実施例3のHFET300の構成を示した図。

- 【図5】実施例4のHFET400の構成を示した図。

- 【図6】実施例5のHFET500の構成を示した図。

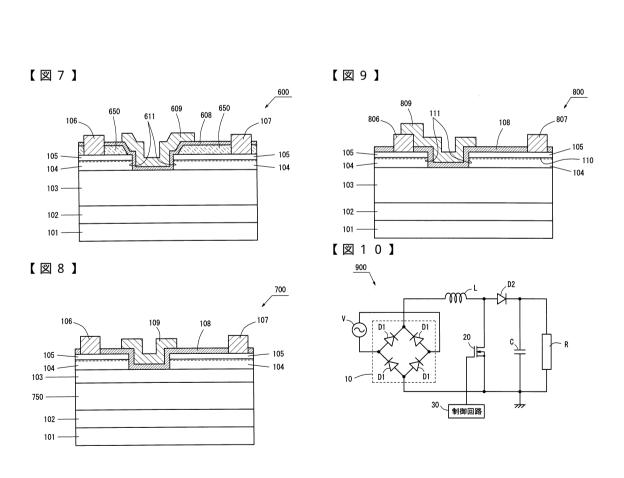

- 【図7】実施例6のHFET600の構成を示した図。

- 【図8】実施例7のHFET700の構成を示した図。

- 【図9】実施例8のダイオード800の構成を示した図。

- 【図10】実施例9の力率改善回路900の構成を示した図。

- 【発明を実施するための形態】

- [0047]

以下、本発明の具体的な実施例について図を参照に説明するが、本発明は実施例に限定されるものではない。

【実施例1】

[0048]

図1は、実施例1のHFET100の構成を示した図である。

[0049]

H F E T 1 0 0 は、S i からなる基板 1 0 1 と、基板 1 0 1 上に A 1 N からなるバッファ層 1 0 2 を介して位置するノンドープの G a N からなる第 1 キャリア走行層 1 0 3 を有している。

[0050]

また、第1キャリア走行層103上の互いに離間した2つの領域上に、2つに分離して形成されたノンドープのGaNからなる第2キャリア走行層104と、2つの分離した第2キャリア走行層104上にそれぞれ位置するA $1_{0.25}$ Ga $_{0.75}$ Nからなるキャリア供給層105を有していて、第2キャリア走行層104とキャリア供給層105はヘテロ接合している。第2キャリア走行層104とキャリア供給層105は、選択的に再成長させて形成した層である。

[0051]

また、2つの分離したキャリア供給層105のうち、一方のキャリア供給層105上に形成されたソース電極106と、他方のキャリア供給層105上に形成されたドレイン電極107と、を有している。ソース電極106およびドレイン電極107はTi/Al(キャリア供給層側からTi、Alの順)からなる。

[0052]

また、2つの第2キャリア走行層104およびキャリア供給層105の領域に挟まれ第

10

20

30

40

20

30

40

50

2 キャリア走行層 1 0 4 の形成されていない第 1 キャリア走行層 1 0 3 上、 2 つの第 2 キャリア走行層 1 0 4 およびキャリア供給層 1 0 5 の領域が離間して向かい合う側の第 2 キャリア走行層 1 0 4 およびキャリア供給層 1 0 5 の 2 つの側端面 1 1 1、キャリア供給層 1 0 5 上に S i O 2 からなる絶縁膜 1 0 8 を有している。

### [0053]

また、この絶縁膜108を介して、第2キャリア走行層104の形成されていない第1キャリア走行層103上、および2つの側端面111に形成されたゲート電極109を有している。ゲート電極109は、Ni/Au(絶縁膜108側からNi、Auの順)からなる。このゲート電極109は、側端面111近傍のキャリア供給層105上にも、絶縁膜108を介して延伸していて、ソース電極106側とドレイン電極107側それぞれに0.5μm延伸している。このように延伸させることで、ゲート電極109に正の電圧を印加した際に、側端面111近傍により多くの電子を蓄積することができ、その延伸されたゲート電極109の下部にあたる領域の2DEGの濃度をより高めることができる。そのため、オン抵抗をより低減することができる。

#### [0054]

第 1 キャリア走行層 1 0 3 の厚さは 2  $\mu$  m、第 2 キャリア走行層 1 0 4 の厚さは 1 0 0 n m、キャリア供給層 1 0 5 の厚さは 2 5 n mである。また、絶縁膜 1 0 8 の厚さは 4 0 n mである。また、ソース電極 1 0 6 とゲート電極 1 0 9 との間隔は 1 . 5  $\mu$  m、ゲート電極 1 0 9 とドレイン電極 1 0 7 との距離は 6 . 5  $\mu$  mであり、ゲート電極 1 0 9 はソース電極 1 0 6 よりに位置した非対称な構成となっている。このようにゲート電極 1 0 9 をドレイン電極 1 0 7 よりもソース電極 1 0 6 に近い位置とすることで、耐圧性の向上を図っている。

### [0055]

基板101には、Si以外に、サファイア、SiC、ZnO、スピネル、GaNなどの従来よりIII 族窒化物半導体の成長基板として知られる任意の材料の基板を用いてもよい

#### [0056]

バッファ層102には、A1Nのほか、GaNを用いてもよく、A1N/GaNなどの複数の層であってもよい。また、第1キャリア走行層103は、任意の組成比のIII 族窒化物半導体でよいが、結晶性等の点からGaNが望ましい。また、第1キャリア走行層103はn型不純物などがドープされていてもよく、複数の層で構成されていてもよい。また、バッファ層102を形成せず、直接基板101上に第1キャリア走行層103が形成されていてもよい。

## [0057]

第2キャリア走行層104はGaN、キャリア供給層105はA1GaNであるが、キャリア供給層105のバンドギャップが第2キャリア走行層104よりも大きくなるようにIII 族窒化物半導体の組成比が選択されていれば、第2キャリア走行層104およびキャリア供給層105は任意のIII 族窒化物半導体でよい。たとえば、第2キャリア走行層104としてInGaNを用い、キャリア供給層105としてGaNないしA1GaNを用いてもよい。また、キャリア供給層105は、Siなどの不純物がドープされたn型としてもよい。また、キャリア供給層105上にキャップ層を設けた構造としてもよい。また、第2キャリア走行層104は、第1キャリア走行層103と同一組成であってもよいし、異なる組成比のIII 族窒化物半導体材料であってもよい。

# [0058]

第2キャリア走行層104とキャリア供給層105とのヘテロ接合により、第2キャリア走行層104とキャリア供給層105とのヘテロ接合界面110近傍であって第2キャリア走行層104側には、2DEGが形成される(図1の点線で示した部分)。第2キャリア走行層104とキャリア供給層105は、ゲート電極109によって互いに離間された2つの領域に形成されているため、2DEGもまた、キャリア供給層105上にソース電極106が形成されている側(ソース・ゲート側)と、キャリア供給層105上にドレ

イン電極 1 0 7 が形成されている側(ゲート・ドレイン側)の 2 つの領域に分離して形成される。

### [0059]

ソース電極106およびドレイン電極107は、トンネル効果によってキャリア供給層105を介して第2キャリア走行層104にオーミックコンタクトをとる。ソース電極106およびドレイン電極107の材料として、Ti/A1以外にも、Ti/Auなどを用いることができる。なお、ショットキーコンタクトをとる材料であってもよいが、オン抵抗の低減を図るためには望ましくない。また、良好なオーミックコンタクトを得るために、ソース電極106およびドレイン電極107直下のキャリア供給層105、第2キャリア走行層104の領域に、高濃度にSiをドープしたり、ソース電極106およびドレイン電極107直下のキャリア供給層105の厚さを薄くしてもよい。

#### [0060]

絶縁膜 1 0 8 は、ゲート絶縁膜と保護膜とを兼ねたものである。また、絶縁膜 1 0 8 は、  $SiO_2$  以外に  $SiN_x$  、  $Al_2$   $O_3$  、  $HfO_2$  、  $ZrO_2$  、 AlN などを用いることができる。なお、絶縁膜 1 0 8 は単層であるが、絶縁膜 1 0 8 の全部または一部を複数の層で構成してもよい。たとえば、 2 層とする場合は、  $SiO_2$  /  $ZrO_2$  (第 1 キャリア走行層 1 0 3 側から  $SiO_2$  、  $ZrO_2$  の順に積層されていることを意味する。この段落において以下同じ)、  $SiO_2$  /  $Al_2$   $O_3$  、  $SiO_2$  /  $HfO_2$  、 SiN /  $SiO_2$  、  $Al_2$   $O_3$  /  $ZrO_2$  、  $ZrO_2$  、  $ZrO_3$  /  $ZrO_3$

#### [0061]

ゲート電極 1 0 9 は、N i / A u の他にも、T i / A l 、W やポリシリコンなどを用いてもよい。

#### [0062]

このHFET100は、ゲート電極109にバイアス電圧が印加されていない状態では、2DEGがソース・ゲート側と、ゲート・ドレイン側に分離され、電気的に接続されていない。したがって、ソース・ドレイン間に電流は流れず、オフ状態となっている。つまり、HFET100はノーマリオフ特性を有している。一方、ゲート電極109に閾値電圧以上のバイアス電圧が印加されると、絶縁膜108を介してゲート電極109と接している領域、すなわち、第2キャリア走行層104の形成されていない第1キャリア走行層103表面近傍、第2キャリア走行層104およびキャリア供給層105の向かい合う側端面111近傍に電子が蓄積され、この蓄積された電子を介してソース・ゲート側の2DEGとゲート・ドレイン側の2DEGが電気的に接続される。その結果、ソース・ドレイン間に電流が流れ、オン状態となる。

### [0063]

また、このHFET100では、第2キャリア走行層104は、第1キャリア走行層103上に選択的に再成長された層であるから、第1キャリア走行層103と第2キャリア走行層104との界面に再成長に伴う不純物が混入しているが、第2キャリア走行層104中の再成長に伴う不純物は、第1キャリア走行層103から離れるにしたがって減少のでいる。そのため、第2キャリア走行層104とキャリア供給層105とのヘテロ接合界面110においては、選択的な再成長に伴う不純物はほとんど見られない。また、キャリア供給層105は、第2キャリア走行層104を再成長させたのちに、第2キャリア共行層104に連続して選択的に再成長させた層であるから、第2キャリア走行層104に連続して選択的に再成長させた層であるから、第2キャリア走行層104とキャリア供給層105を再成長させた場合の第1キャリア走行層103上にキャリア供給層105を再成長させた場合の第1キャリア走行層103上にキャリア供給層105とのヘテロ接合界面110近傍であって第2キャリア居行層104とキャリア供給層105とのへテロ接合界面よりも高くなっている。そのため、第2キャリア居行層104とキャリア供給層105とのへテロ接合界面よりも高くなっている。そのため、第2キャリア産行層104側に形成される2DEGの移動度を低下させてしまうことがない。したがって、実施例1のHFET100は、ノーマリオフでありながら、オン抵抗の低い構造となっている。

10

20

30

40

20

30

40

50

#### [0064]

なお、第2キャリア走行層104とキャリア供給層105とのヘテロ接合界面における、再成長に伴って混入した不純物を十分に低減し、平坦性を高めるためには、第2キャリア走行層104の厚さを50nm以上とすることが望ましい。

### [0065]

また、HFET100では、第1キャリア走行層103上に形成された絶縁膜108の上端が、第2キャリア走行層104とキャリア供給層105とのヘテロ接合界面110よりも低い位置(第1キャリア走行層103により近い位置)となるように、絶縁膜108の厚さを第2キャリア走行層104の厚さよりも薄くしている。これにより、ゲート電極109に正の電圧を印加した際に、2つの側端面111近傍に、より多くの電子を蓄積することができる。その結果、オン抵抗がさらに低減された構造となっている。

[0066]

次に、HFET100の製造方法について図2を参照に説明する。

## [0067]

まず、Siからなる基板101上に、A1Nからなるバッファ層102をMOCVD法によって形成する。そして、バッファ層102上にノンドープGaNからなる第1キャリア走行層103をMOCVD法によって形成する(図2(a))。キャリアガスには水素と窒素、窒素源にはアンモニア、Ga源にはTMG(トリメチルガリウム)、A1源にはTMA(トリメチルアルミニウム)、を用いる。

# [0068]

次に、第1キャリア走行層103上の所定の領域に、CVD法によって $SiO_2$ からなるマスク113を形成し、マスク113を挟んで2つの離間した領域にはマスク113を形成せず第1キャリア走行層103表面を露出させる(図2(b))。マスク113は、III族窒化物半導体の成長を阻害する材料であれば何でもよく、 $SiO_2$ のほか、 $Si_3N_4$ 、 $Al_2O_3$ 、 $HfO_2$ 、 $ZrO_2$ などの絶縁膜などを用いることができる。

# [0069]

次に、第1キャリア走行層103上に、MOCVD法によってノンドープGaNからなる第2キャリア走行層104を再成長させる。ここで、マスク113上は結晶成長が阻害されてGaNが成長しないため、マスク113の形成されていない2つの離間した領域上にのみ、第2キャリア走行層104が選択的に再成長する(図2(c))。この再成長時において、第1キャリア走行層103と第2キャリア走行層104との界面の平坦性は悪化し、不純物が混入してしまう。しかし、第2キャリア走行層104が成長するにしたがって、第2キャリア走行層104表面の平坦性は回復していき、再成長に伴う不純物の混入も減少していく。

# [0070]

第 2 キャリア走行層 1 0 4 を所定の厚さまで成長させた後、続けて  $A 1_{0.25}$   $G a_{0.75}$  N からなるキャリア供給層 1 0 5 を M O C V D 法によって成長させる。ここにおいても、マスク 1 1 3 上は結晶成長が阻害されるため、 2 つの第 2 キャリア走行層 1 0 4 上にのみ、キャリア供給層 1 0 5 が選択的に成長する。キャリア供給層 1 0 5 の形成時において、第 2 キャリア走行層 1 0 4 の平坦性は回復し、不純物の混入が減少しているため、第 2 キャリア走行層 1 0 4 とキャリア供給層 1 0 5 とのヘテロ接合界面の平坦性は高く、またその界面近傍における再成長に伴う不純物はほとんど見られない。マスク 1 1 3 は、キャリア供給層 1 0 5 を所定の厚さまで成長させたのちに除去する(図 2 ( d ) )。

# [0071]

次に、第 2 キャリア走行層 1 0 4 が形成されていない第 1 キャリア走行層 1 0 3 上、 2 つの領域の第 2 キャリア走行層 1 0 4 およびキャリア供給層 1 0 5 が離間して向かい合う側の第 2 キャリア走行層 1 0 4 およびキャリア供給層 1 0 5 の 2 つの側端面 1 1 1、キャリア供給層 1 0 5 上に、  $SiO_2$  からなる絶縁膜 1 0 8 を形成する。絶縁膜 1 0 8 は、ゲート絶縁膜とキャリア供給層 1 0 5 の保護膜とを兼ねるものであり、これにより製造工程数の削減を図っている。また絶縁膜 1 0 8 は、 CVD法、スパッタ、 ALD法などによっ

て形成する。次に、ソース電極106、ドレイン電極107を形成する領域の絶縁膜108を除去してキャリア供給層105を露出させ、その露出したキャリア供給層105上に蒸着とリフトオフによってソース電極106、ドレイン電極107を形成する。また、第2キャリア走行層104が形成されていない第1キャリア走行層103上、2つの側端面111、その側端面111近傍のキャリア供給層105上に、蒸着とリフトオフによってゲート電極109を形成する。以上によって図1に示すHFET100が製造される。

#### [0072]

このHFET100の製造方法によれば、第2キャリア走行層104とキャリア供給層105とのヘテロ接合界面の平坦性が高く、その界面近傍における再成長に伴う不純物はほとんど見られないため、ノーマリオフ特性を有しつつオン抵抗を低くすることができる

10

#### [0073]

なお、上記HFET100の製造方法において、選択成長に用いたマスク113は、キャリア供給層105の形成後に除去しているが、除去せずにゲート絶縁膜として利用して もよい。

#### 【実施例2】

### [0074]

図3は、実施例2のHFET200の構成を示した図である。HFET200は、実施例1のHFET100における第2キャリア走行層104、キャリア供給層105、絶縁膜108、ゲート電極109を、それぞれ第2キャリア走行層204、キャリア供給層205、絶縁膜208、ゲート電極209に替えたものであり、他の構成はHFET100と同様である。第2キャリア走行層204およびキャリア供給層205の領域が離間して向かい合う側の第2キャリア走行層204およびキャリア供給層205の領域が離間して向かい合う側の第2キャリア走行層204およびキャリア供給層205の2つの側端面220が傾斜してい外の点は同様であり、第2キャリア走行層204およびキャリア供給層105とは異なっている。それ以外の点は同様であり、第2キャリア走行層204およびキャリア供給層103から離れるにしたがって、第2キャリア走行層104、キャリア供給層103から離れるにしたがって、第2キャリア走行層204およびキャリア供給層205の素子面に平行(基板101の主面に平行)な断面積が減少するような傾斜を有している。絶縁膜208、ゲート電極109と同様である。

20

30

# [0075]

このような傾斜した側端面 2 2 0 は、第 2 キャリア走行層 2 0 4、キャリア供給層 2 0 5 を再成長させる際に、特定の成長条件とすることで可能である。そのような特定の成長条件では、素子面であるIII 族窒化物半導体の c 面に対して傾斜したファセット面(たとえば、(1 0 - 1 1)面など)を保持した状態で、第 2 キャリア走行層 2 0 4、キャリア供給層 2 0 5 を c 面に垂直な方向へ結晶成長させることができ、この時傾斜したファセット面が側端面 2 2 0 となる。

40

### [0076]

このように、第2キャリア走行層204およびキャリア供給層205の側端面220を傾斜させることで、ゲート電極209と絶縁膜208を介して接する第1キャリア走行層103表面近傍、および側端面220近傍における電界の集中が緩和される。そのため、HFET200は、HFET100に比べて耐圧性がより向上した構造となっている。

#### 【実施例3】

# [0077]

図4は、実施例3のHFET300の構成を示した図である。HFET300は、実施例1のHFET100におけるキャリア供給層105を、以下に説明するキャリア供給層305に替えたものであり、他の構成はHFET100と同様である。キャリア供給層305は、第2キャリア走行層104側から、ノンドープのGaNからなる第1キャリア供

20

30

40

50

給層305a、ノンドープのA1GaNからなる第2キャリア供給層305b、ノンドープのA1Nからなる第3キャリア供給層305cの順に積層された3層構造である。このキャリア供給層305もまた、キャリア供給層105と同様に、第2キャリア走行層104上に選択的に再成長された層である。

### [0078]

このHFET300もまた、第2キャリア走行層104と、3層からなるキャリア供給層305が、第1キャリア走行層103上に選択的に再成長された層であるため、2DEGの移動度の低下が抑制されており、オン抵抗が低減された構造となっている。

#### [0079]

なお、キャリア供給層305は、他の複層構造であってもよい。たとえばGaN/A1GaN(第1キャリア走行層103側からGaN、A1GaNの順の積層構造であることを意味する。以下、この段落において同じ)、InGaN/A1GaN/A1GaN/A1GaN/A1RaN/A1RaN/A1RaN/A1RaN/A1RaN/A1RaN/A1RaN/A1RaN

#### 【実施例4】

#### [0800]

図5は、実施例4のHFET400の構成を示した図である。HFET400は、実施例1のHFET100における第2キャリア走行層104およびキャリア供給層105に替えて、第2キャリア走行層404とキャリア供給層405の対を3対形成したものであり、第1キャリア走行層103側から順に、第2キャリア走行層404a、キャリア供給層405b、第2キャリア走行層404c、キャリア供給層405b、第2キャリア走行層404c、キャリア供給層405cの順に積層された構造である。他の構成についてはHFET100と同様である。この3対の第2キャリア走行層404およびキャリア供給層105と同様に、いずれも第1キャリア走行層104およびキャリア供給層105と同様に、いずれも第1キャリア走行層103上に選択的に再成長された層である。

### [0081]

第2キャリア走行層404aとキャリア供給層405aとのヘテロ接合界面440aであって第2キャリア走行層404a側、第2キャリア走行層404b側、第2キャリア走行層404b側、第2キャリア走行層404cとキャリア供給層405cとのヘテロ接合界面440cであって第2キャリア走行層404c側、にそれぞれ2DEGが形成される。また、第2キャリア走行層404とキャリア供給層405は、第1キャリア走行層103上に選択的に再成長された層であるから、これらのヘテロ接合界面440a、b、cは平坦性が高く、ヘテロ接合界面440a、b、c近傍の領域は再成長に伴って混入した不純物がほとんど見られない。したがって、これらのヘテロ接合界面440a、b、c近傍に形成される2DEGは、移動度の低下が抑制されており、オン抵抗が低減されている。

# [0082]

以上のように、実施例4のHFET400では、移動度の低下が抑制された2DEGの層が3つ形成されているため、さらにオン抵抗が低減された構造となっている。

### [0083]

なお、上記実施例 4 では、第 2 キャリア走行層 4 0 4 a、 b、 c はいずれも同一組成とし、キャリア供給層 4 0 5 a、 b、 c のいずれも同一組成としたが、第 2 キャリア走行層 4 0 4 a とキャリア供給層 4 0 5 a、第 2 キャリア走行層 4 0 4 b とキャリア供給層 4 0 5 b、第 2 キャリア走行層 4 0 4 c とキャリア供給層 4 0 5 c がそれぞれへテロ接合となり、その界面近傍に 2 D E G が形成されるのであれば、第 2 キャリア走行層 4 0 4 a、 b、 c をそれぞれ異なる組成としてもよく、キャリア供給層 4 0 5 a、 b、 c をそれぞれ異なる組成としてもよい。

## 【実施例5】

# [0084]

図6は、実施例5のHFET500の構成を示した図である。HFET500は、実施

20

30

40

50

例 1 の H F E T 1 0 0 において以下のように変更したものであり、他の構成については H F E T 1 0 0 と同様である。 H F E T 5 0 0 は、絶縁膜 1 0 8 上であって、ソース電極 1 0 6 およびドレイン電極 1 0 7 の形成領域以外のキャリア供給層 1 0 5 の上部にあたる領域に、  $SiO_2$  からなる絶縁膜 1 0 8 よりも比誘電率の高い  $ZrO_2$  からなる絶縁膜 5 5 0 が形成されている。ゲート電極 5 0 9 は、絶縁膜 1 0 8 を介して、第 2 キャリア走行層 1 0 4 の形成されていない第 1 キャリア走行層 1 0 3 上、 2 つの第 2 キャリア走行層 1 0 4 およびキャリア供給層 1 0 5 の領域が離間して向かい合う側の第 2 キャリア走行層 1 0 4 およびキャリア供給層 1 0 5 の 2 つの側端面 5 1 1 に形成されており、さらにソース電極 1 0 6 側の側端面 5 1 1 からソース電極 1 0 6 側の側端面 5 1 1 からドレイン電極 1 0 7 側の側端面 5 1 1 からドレイン電極 1 0 7 側の側端面 5 1 1 からドレイン電極 1 0 7 側に向かって 1 . 5  $\mu$ m延伸して絶縁膜 5 5 0 上に形成されている。

[0085]

このHFET500の構造によると、ドレイン電極107側の第2キャリア走行層104、キャリア供給層105の側端面511からドレイン電極107側へ延伸したゲート電極509と、絶縁膜108との間に、絶縁膜108よりも比誘電率の高い絶縁膜550が設けられているため、オフ動作時において、ドレイン電極107側の側端面511近傍でキャリア供給層105上の絶縁膜108内部の電界強度が緩和される。したがって、HFET500は耐圧性がさらに向上した構造となっている。

【実施例6】

[0086]

図 7 は、実施例 6 の H F E T 6 0 0 の構成を示した図である。 H F E T 6 0 0 は、実施例 1 の H F E T 1 0 0 において以下のように変更したものであり、他の構成については H F E T 1 0 0 と同様である。 H F E T 6 0 0 は、ソース電極 1 0 6 およびドレイン電極 1 0 7 の形成領域以外のキャリア供給層 1 0 5 上に、SiNからなる絶縁膜 6 5 0 が形成されている。SiO₂からなる絶縁膜 6 0 8 は、第 1 キャリア走行層 1 0 3 上、2つの第 2 キャリア走行層 1 0 4 およびキャリア供給層 1 0 5 の領域が離間して向かい合う側のキャリア走行層 1 0 4 およびキャリア供給層 1 0 5 の 2 つの側端面 6 1 1 、絶縁膜 6 5 0 上に連続して膜状に形成されている。ゲート電極 6 0 9 は、絶縁膜 6 0 8 を介して、第 1 キャリア走行層 1 0 3 上、側端面 6 1 1 に形成されており、さらにソース電極 1 0 6 側の側端面 6 1 1 からソース電極 1 0 6 側に向かって 0 . 5  $\mu$  m延伸して絶縁膜 6 0 8 上に形成されており、ドレイン電極 1 0 7 側の側端面 6 1 1 からドレイン電極 1 0 7 側の側端面 6 1 1 からドレイン電極 1 0 7 側の側端面 6 1 1 からドレイン電極 1 0 7 側に向かって 1 . 5  $\mu$  m延伸して絶縁膜 6 0 8 上に形成されている。

[0087]

このHFET600では、オン動作時において電界強度が高くなる側端面611、および第2キャリア走行層104が形成されていない第1キャリア走行層103上には、耐圧性の高いSi〇 $_2$  からなる絶縁膜608が設けられている。また、オフ動作時において電界強度が高くなるゲート電極609のドレイン側端部の直下にも、耐圧性の高いSiО $_2$  からなる絶縁膜608が設けられている。また、オフ動作時において電界強度が高くなるゲート電極609のドレイン側端部の直下であってキャリア供給層105上には、絶縁膜650が設けられている。絶縁膜650はSiNからなるため、絶縁膜650としてSiO $_2$  を用いた場合よりも、キャリア供給層105と絶縁膜650との界面に発生する界面準位密度を低減することができ、電流コラプス(高電圧動作時にドレイン電流が大きく減少する現象)などの特性劣化を抑制することができる。

[0088]

このように、HFET600では、耐圧性が要求される領域と界面準位密度の低減が要求される領域とで異なる材料の絶縁膜を用いる構造としたので、耐圧性の向上と、界面準位の高さに起因した特性劣化の防止の両立が可能な構造となっている。

【実施例7】

[0089]

図8は、実施例7のHFET700の構成を示した図である。HFET700は、実施

20

30

40

50

例 1 の H F E T 1 0 0 において、バッファ層 1 0 2 と第 1 キャリア走行層 1 0 3 との間に キャリア走行抑止層 7 5 0 を設けたものである。キャリア走行抑止層 7 5 0 は、 M g を 1  $\times$  1 0  $^{19}$  c m  $^{-3}$  ドープした、厚さ 1 0 0 n m の p - G a N からなり、正孔濃度は 1  $\times$  1 0  $^{17}$  c m  $^{-3}$  である。

# [0090]

このキャリア走行抑止層 7 5 0 は、電子の流れに対して高抵抗となることから、オフ動作時においてソース・ドレイン間に高いバイアス電圧を印加した際に、第 2 キャリア走行層 1 0 4 とキャリア供給層 1 0 5 とのヘテロ接合界面から離れた領域を介して電流が流れる経路を遮断することができる。そのため、HFET 7 0 0 は、オフ動作時のソース・ドレイン間のリーク電流が低減されていて、さらにHFET 1 0 0 と同様にノーマリオフでオン抵抗が低減されている。

#### [0091]

ここで、キャリア走行抑止層750を設ける場合、キャリア走行抑止層750とキャリア供給層105との距離をある程度以上に大きくする必要があり、具体的には第1キャリア走行層103、第2キャリア走行層104、およびキャリア供給層105の合計の厚さを100mm以上とすることが望ましい。これは、キャリア走行抑止層750とキャリア供給層105との距離が近いと、第1キャリア走行層103、第2キャリア走行層104、およびキャリア供給層105を形成する際に、キャリア走行抑止層750にドープされたMgがキャリア供給層105にまで拡散してしまい、2DEGの濃度や移動度を低下させてしまうことがあるからである。また、キャリア走行抑止層750がp型である影響で2DEGの濃度を低下させてしまうからである。

#### [0092]

なお、実施例7ではキャリア走行抑止層750としてp-GaNを用いたが、電子が第2キャリア走行層104から離れた領域を走行することを抑止することができる材料であればよい。たとえば、キャリア走行抑止層750は第1キャリア走行層103の伝導型とは異なる伝導型であればよい。第1キャリア走行層103はノンドープGaNであり、低濃度のn型であるから、キャリア走行抑止層750としてp-GaNだけでなくi-GaNを用いることもできる。

### [0093]

また、ノンドープGaNである第1キャリア走行層103よりもバンドギャップが広いA1GaNをキャリア走行抑止層750に用いることができる。キャリア走行抑止層750としてA1GaNを用いると、第1キャリア走行層103とキャリア走行抑止層750とのヘテロ接合界面に負の分極電荷が発生し、この電荷およびヘテロ接合界面におけるバンドの不連続が電子に対して障壁となる。その結果、オフ動作時においてソース・ドレイン間に高いバイアス電圧を印加した際に、第2キャリア走行層104とキャリア供給層105とのヘテロ接合界面から離れた領域を介して電流が流れる経路を遮断することができ、ソース・ドレイン間のリーク電流を低減することができる。このとき、キャリア走行抑止層750が薄すぎると、電子はトンネル効果によりキャリア走行抑止層750を透過し、バッファ層102を介して電流がリークしてしまう。そのため、キャリア走行抑止層750は100mm以上とすることが望ましい。

# [0094]

また、バッファ層102よりもバンドギャップが狭いInGaNをキャリア走行抑止層750に用いることができる。キャリア走行抑止層750としてInGaNを用いると、バッファ層102とキャリア走行抑止層750とのヘテロ接合界面に負の分極電荷が発生し、この電荷およびヘテロ接合界面におけるバンドの不連続が電子に対して障壁となる。その結果、オフ動作時においてソース・ドレイン間に高いバイアス電圧を印加した際に、第2キャリア走行層104とキャリア供給層105との界面から離れた領域を介して電流が流れる経路を遮断することができ、ソース・ドレイン間のリーク電流を低減することができる。ここで、キャリア走行抑止層750はノンドープGaNである第1キャリア走行層103よりもバンドギャップが狭いため、キャリア走行抑止層750を介してリーク電

20

30

40

50

流が流れる。そのため、キャリア走行抑止層 750 の厚さを 200 n m以下とすることでキャリア走行抑止層 750 を介したリーク電流を減少させることが望ましい。また、キャリア走行抑止層 750 を p - I n G a N または i - I n G a N とすることがさらに望ましい。

# 【実施例8】

## [0095]

図9は、実施例8のダイオード800の構成を示した図である。ダイオード800は、実施例1のHFET100におけるソース電極106およびドレイン電極107を、それぞれアノード電極806、カソード電極807に替え、ゲート電極109をゲート電極809に替えたものであり、ゲート電極809は、HFET100におけるゲート電極109をアノード電極806の方向へさらに延伸させてアノード電極806を覆うようにして接合させたものである。また、アノード電極806、カソード電極807は、実施例1のHFET100におけるソース電極106およびドレイン電極107と同一の構成であり、Ti/Alからなる。また、ゲート電極809はNi/Auからなる。

#### [0096]

アノード電極806とカソード電極807は、トンネル効果によってキャリア供給層105を介して第2キャリア走行層104にオーミック接触している。また、ゲート電極809は、印加するバイアス電圧によって、ゲート電極809と絶縁膜108を介して接する第1キャリア走行層103表面近傍、2つの第2キャリア走行層104およびキャリア供給層105の領域が離間して向かい合う側の第2キャリア走行層104およびキャリア供給層105の側端面111近傍の電子濃度を制御する制御電極として作用する。

#### [0097]

また、このダイオード 8 0 0 では、実施例 1 の H F E T 1 0 0 と同様に、第 2 キャリア走行層 1 0 4 とキャリア供給層 1 0 5 とのヘテロ接合界面 1 1 0 近傍であって第 2 キャリア走行層 1 0 4 似に 2 D E G が形成される。第 2 キャリア走行層 1 0 4 とキャリア供給層 1 0 5 は、ゲート電極 8 0 9 を挟んで 2 つの領域に離間しているため、 2 D E G も、アノード・ゲート間の 2 D E G と、ゲート・カソード間の 2 D E G に分離して形成されている。

#### [0098]

次に、ダイオード800の動作について説明する。ダイオード800のアノード電極806とカソード電極807の間に順方向バイアス電圧を印加した場合、アノード電極806と電気的に接続されているゲート電極809に、絶縁膜108を介して接する第1キャリア走行層103表面近傍、および側端面111近傍に、電子が蓄積される。この電子によって、アノード・ゲート間に形成されている2DEGとゲート・カソード間に形成されている2DEGとが接続され、アノード電極806とカソード電極807との間に電流が流れる。一方、アノード電極806とカソード電極807の間に逆方向バイアス電圧を印加した場合、アノード電極806と電気的に接続されているゲート電極809近傍の電子、およびゲート・カソード間の2DEGは空乏化されるため、電流は遮断される。

### [0099]

このように、実施例8のダイオード800では、ゲート電極809によって絶縁膜を介して電子濃度が制御されることにより、整流動作が得られている。

# [0100]

また、実施例8のダイオード800では、実施例1のHFET100の説明でも述べたように、第2キャリア走行層104とキャリア供給層105とのヘテロ接合界面110の平坦性が高く、そのヘテロ接合界面110近傍における再成長に伴って混入した不純物がほとんどないため、2DEGの移動度が高い。また、アノード電極806は、第2キャリア走行層104とオーミック接触しているため、順方向バイアス電圧時の立ち上がり電圧が0に近い。したがって、ダイオード800は、オン抵抗、オン電圧の低い構造となっている。

# [0101]

さらにダイオード800では、ゲート電極809を設け、アノード電極806と電気的

20

30

40

50

に接続した構成としていることから、逆方向バイアス電圧の印加時に最も電界強度が高くなるのはゲート電極809のカソード電極807側端部である。その端部には絶縁膜108が形成されており、その絶縁膜108を介して、ゲート電極809は第2キャリア走行層104およびキャリア供給層105に接している。そのため、電界強度の高いゲート電極809端部における逆方向リーク電流を大幅に低減することができる。したがって、ダイオード800は、オフ動作時の耐圧が高い構造となっている。

#### [0102]

なお、実施例8のダイオード800は、実施例1のHFET100においてソース電極106をアノード電極806とし、ゲート電極109をアノード電極806側に延伸することでアノード電極806とゲート電極109とを接合した構造であるが、実施例1のソース電極106をアノード電極806とゲート電極109とを電気的に接続する構造であれば他の構造であってよい。たとえば、アノード電極をゲート電極109側に延伸させてアノード電極とゲート電極109とを接合する構造であってもよい。また、配線電極などによってアノード電極とゲート電極109とを間接的に接続する構造であってもよい。また、アノード電極とゲート電極109とを同一材料として共通化し、複合アノード電極構造としてもよい。

### [0103]

また、実施例8のダイオード800は、実施例1のHFET100においてソース電極106をアノード電極としてアノード電極とゲート電極を電気的に接続した構造であるが、実施例2~7のHFET200~700におけるドレイン電極107をアノード電極として、そのアノード電極とゲート電極を電気的に接続した構造としても、ダイオード800と同様の効果のダイオードを実現することができる。

#### 【実施例9】

#### [0104]

図10は、実施例9の力率改善回路900の構成を示した回路図である。力率改善回路900は、交流電源Vと、交流電源Vの交流電圧を整流する4つのダイオードD1からなるダイオードブリッジ10とを有している。また、ドレイン側をインダクタLを介してダイオードブリッジ10の直流側の正極出力端に、ソース側をダイオードブリッジ10の直流側の負極出力端に接続するHFET20のゲートに接続する制御回路30と、をさらに有している。また、HFET20のソース・ドレイン間には、ダイオードD2とキャパシタCとを直列に接続した回路が接続されていて、キャパシタCと並列に負荷Rが接続されている。力率改善回路900は、出力電圧やダイオードブリッジ10に流れる電流などに基づいて制御回路30がHFET20のオンオフを制御することで、交流電源Vの力率を改善する回路である。

# [0105]

上記構成の力率改善回路900において、ダイオードD1、D2は、実施例8のダイオード800を使用し、HFET20には、実施例1のHFET100を使用している。そのため、力率改善回路900では、回路内部での損失が軽減されており、高効率で低損失な動作が可能となっている。

### [0106]

なお、実施例では本発明の半導体装置をHFETまたはダイオードに適用した例を示したが、本発明は、キャリア走行層とキャリア供給層との界面に生じる2DEGをチャネルとして動作する他の半導体装置に対しても適用可能である。たとえばヘテロ接合バイポーラトランジスタ(HBT)などにも適用可能である。

#### [0107]

また、実施例1~7のHFETにフィールドプレート構造を導入し、さらなる耐圧性の向上を図るようにしてもよい。

## 【産業上の利用可能性】

#### [0108]

本発明の半導体装置はオン抵抗が低いので、電力変換装置に本発明の半導体装置を利用

# することで、高効率な電力変換装置を実現することができる。

### 【符号の説明】

# [0109]

101:基板

1 0 2 : バッファ層

1 0 3 : 第 1 キャリア走行層

104、204、404:第2キャリア走行層

105、205、305、405:キャリア供給層

106:ソース電極

107:ドレイン電極

108、208、550、650: 絶縁膜

109、209、509、609、809:ゲート電極

750:キャリア走行抑止層

8 0 6 : アノード電極 8 0 7 : カソード電極

# 【図1】

# 【図2】

(a)

(b)

(c)

(b)

# フロントページの続き

# (51) Int.CI. F I

H 0 1 L 29/78 (2006.01) H 0 1 L 21/336 (2006.01)

# (56)参考文献 特開2007-035905(JP,A)

特開2009-200096(JP,A) 特開2009-099691(JP,A) 特開2009-016655(JP,A)

特開2008-147593(JP,A)

特開2011-009493(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/336-21/338

H01L 27/095-27/098

H01L 29/775-29/778

H01L 29/78

H01L 29/80-29/812

H01L 29/861-29/885