#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2015-43438 (P2015-43438A)

(43) 公開日 平成27年3月5日(2015.3.5)

| (51) Int.Cl. |                       | FI      |         |           | テーマコー    | ド(参考)  |

|--------------|-----------------------|---------|---------|-----------|----------|--------|

| HO1L 23/     | (15 <b>(200</b> 6.01) | HO1L    | 23/14   | C         |          |        |

| HO1L 23/     | (12 (2006.01)         | HO1L    | 23/12   | N         |          |        |

| HO5K 3/      | (46 (2006.01)         | H05K    | 3/46    | N         |          |        |

| HO1L 21/     | 768 (2006.01)         | H05K    | 3/46    | T         |          |        |

|              |                       | H05K    | 3/46    | В         |          |        |

|              |                       | 審査請求 未請 | 事求 請求項の | O数 12 O L | (全 28 頁) | 最終頁に続く |

(21) 出願番号 特願2014-192658 (P2014-192658)

(22) 出願日 平成26年9月22日 (2014.9.22)

(62) 分割の表示 特願2012-542016 (P2012-542016)

の分割

原出願日 平成22年11月1日 (2010.11.1)

(31) 優先権主張番号 12/653,722

(32) 優先日 平成21年12月17日 (2009.12.17)

(33) 優先権主張国 米国 (US)

(71) 出願人 593096712

インテル コーポレイション アメリカ合衆国 95054 カリフォル ニア州 サンタ クララ ミッション カ

レッジ ブールバード 2200

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(74)代理人 100091214

弁理士 大貫 進介

(72) 発明者 マー,チーン

アメリカ合衆国 95070 カリフォル ニア州 サラトガ スカリー アヴェニュ

- 12540

最終頁に続く

(54) 【発明の名称】多層ガラスコアを含む集積回路デバイス用基板、及びその製造方法

### (57)【要約】

【課題】 集積回路(IC)デバイス用の基板の実施形態が開示される。

【解決手段】 基板は、ともに接合された2つ以上の別々のガラス層を有するコアを含む。隣接し合うガラス層の間に、これらの層をともに結合する別個の接合層が配設され得る。基板はまた、多層ガラスコアの両面に、あるいは場合により該コアの片面のみに、ビルドアップ構造を含み得る。基板の両面に導電端子が形成され得る。基板の一方の面の端子にICダイが結合され得る。反対側の面の端子は、例えば回路基板などの次階層の部品と結合され得る。1つ以上の導電体が多層ガラスコアを貫いて延在し、これら導電体のうちの1つ以上が、コア上に配置されたビルドアップ構造と電気的に結合され得る。その他の実施形態も開示される。

【選択図】 図1B

#### 【特許請求の範囲】

#### 【請求項1】

ともに接合された複数のガラス層を含む板を設ける工程であり、前記板は第 1 表面及び その反対側の第 2 表面を有する、工程と、

前 記 複 数 の ガ ラ ス 層 の う ち の 第 1 の ガ ラ ス 層 内 に 第 1 の ビ ア を 形 成 す る 工 程 と 、

前記第1のビアの壁に保護層を配設する工程と、

前記第1のガラス層に隣接する第2のガラス層内に第2のビアを形成する工程であり、前記第1のビアと前記第2のビアとが概して整列され、前記第1及び第2のビアが、前記第1表面から前記第2表面まで延在する孔の少なくとも一部を形成する、工程と、

を有する方法。

#### 【請求項2】

前記保護層を除去する工程、を更に有する請求項1に記載の方法。

#### 【請求項3】

前記孔の壁にシード層を堆積する工程と、

前記シード層上に金属をめっきして、前記孔内に導電体を設ける工程と、

を更に有する請求項1に記載の方法。

#### 【請求項4】

前記板の前記第1表面に少なくとも1つの誘電体層及び少なくとも1つの金属層を配設し、前記第1表面における前記少なくとも1つの金属層を前記導電体と電気的に結合する工程と、

前記板の前記第2表面に少なくとも1つの誘電体層及び少なくとも1つの金属層を配設し、前記第2表面における前記少なくとも1つの金属層を前記導電体と電気的に結合する工程と、

を更に有する請求項3に記載の方法。

#### 【請求項5】

前記板の前記第1表面に配設される前記少なくとも1つの金属層は、前記第1表面に直に接触して配設され、且つ前記板の前記第2表面に配設される前記少なくとも1つの金属層は、前記第2表面に直に接触して配設される、請求項4に記載の方法。

#### 【請求項6】

前記第1のガラス層は接合層によって前記第2のガラス層と結合され、当該方法は更に、前記接合層内に、前記孔の一部を形成するビアを形成する工程を有する、請求項1に記載の方法。

#### 【請求項7】

第1のガラス層内に複数のビアを形成する工程と、

第2のガラス層を前記第1のガラス層に接合して、第1の二層構造を形成する工程と、前記第2のガラス層内に複数のビアを形成する工程であり、前記第1のガラス層の前記ビアと前記第2のガラス層の前記ビアとがほぼ整列されて、前記二層構造を貫通する複数の孔を形成する、工程と、

必要に応じて、前記第1の二層構造を第2の二層構造と接合する工程であり、前記第1の二層構造の前記複数の孔が前記第2の二層構造の複数の孔と整列される、工程と、 を有する方法。

#### 【請求項8】

前記第1の二層構造が基板コアを提供し、あるいは前記第2の二層構造と接合された前記第1の二層構造が基板コアを提供する、請求項7に記載の方法。

#### 【請求項9】

前記第1のガラス層と前記第2のガラス層との間に接合層を配設する工程を更に有し、該接合層は、前記第1及び第2のガラス層の各々と結合される、請求項7に記載の方法。

#### 【請求項10】

前記接合層内に複数のビアを形成する工程を更に有し、前記接合層の前記ビアは、前記第1のガラス層の前記ビア及び前記第2のガラス層の前記ビアとほぼ整列される、請求項

10

20

30

40

9に記載の方法。

#### 【請求項11】

前記第1の二層構造と前記第2の二層構造との間に接合層を配設する工程を更に有し、該接合層は、前記第1及び第2の二層構造の各々と結合される、請求項7に記載の方法。

### 【請求項12】

前記接合層内に複数のビアを形成する工程を更に有し、前記接合層の前記ビアは、前記第1の二層構造の前記孔及び前記第2の二層構造の前記孔とほぼ整列される、請求項11 に記載の方法。

【発明の詳細な説明】

#### 【技術分野】

[0001]

開示の実施形態は、概して、集積回路デバイス用基板に関し、より具体的には、多層ガラスコアを有する基板に関する。

### 【背景技術】

# [0002]

集積回路(IC)ダイは、該ダイを支持するため、また、例えばマザーボード、メインボード又はその他の回路基板などの次階層の部品と該ダイとの間の電気接続を形成する助けとなるよう、パッケージ内に配置され得る。パッケージは典型的に、ダイが機械的且つ電気的に結合される基板を含む。例えば、ICダイは、フリップチップ構成にて、インターコネクト(相互接続)のアレイによって基板に結合され、インターコネクトの周り及びダイと基板との間にアンダーフィルの層が配設され得る。各インターコネクトは、基板上の対をなす端子(例えば、パッド、ピラー、スタッドバンプなど)に(例えばリフローはんだによって)電気的に結合されるダイ上の端子(例えば、ボンドパッド、銅ピラー又はスタッドバンプなど)を有し得る。代替的に、更なる例として、ICダイは、ダイ取付け接着剤の層によって基板に貼り付けられ、ダイと基板との間に複数のワイヤボンドが形成されてもよい。

#### [0003]

ICダイは基板の一方の面に配置され、基板の反対側の面には多数の導電端子が形成される。基板の反対側の端子は、次階層の部品(例えば、回路基板)との電気接続を形成するために使用され、これらの電気接続は、ダイに電力を送り届けるとともにダイに対して入力/出力(I/O)信号を伝送するために使用されることができる。基板の反対側の導電端子はピン、パッド、ランド、カラム、バンプなどのアレイを有することができ、これらの端子は、回路基板又はその他の次階層部品上の対応する端子のアレイに電気的に結合され得る。パッケージ基板の反対側の端子は、例えばソケット(及び保持機構)を用いて、あるいははんだリフロープロセスによって、次階層の基板に結合され得る。

【発明の概要】

【発明が解決しようとする課題】

#### [0004]

多層ガラスコアを有する基板の実施形態が開示される。

【課題を解決するための手段】

### [0005]

一態様において、基板は、複数の別々のガラス層を含むコアを含む。コアは第1表面及びその反対側の第2表面を有する。基板はまた、前記コアを貫通して前記第1表面から前記第2表面まで延在する複数の導電体を含む。基板はまた、前記コアの前記第1表面に配置された少なくとも1つの誘電体層及び少なくとも1つの金属層を含み、前記第1表面における該少なくとも1つの金属層は前記導電体のうちの少なくとも1つの誘電体層及び少なくとも1つの金属層を含み、前記第2表面に配置された少なくとも1つの金属層は前記導電体のうちの少なくとも1つと電気的に結合される。

#### 【図面の簡単な説明】

10

20

30

- [0006]

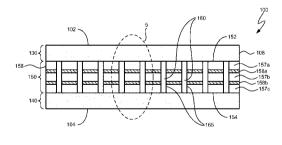

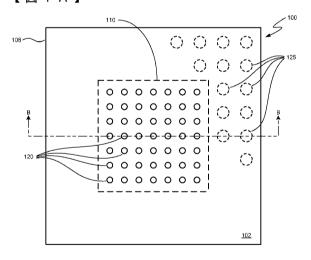

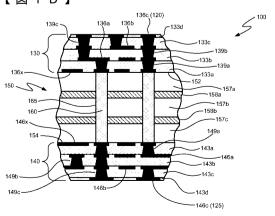

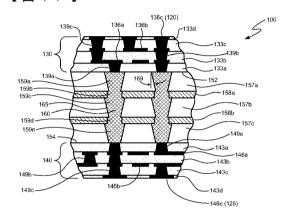

- 【図1A】多層ガラスコアを有する基板の一実施形態の平面図を示す模式図である。

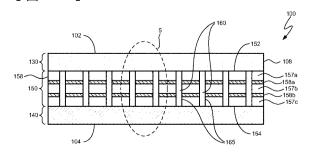

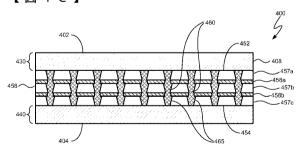

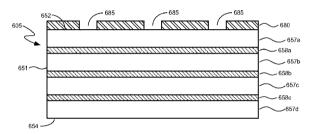

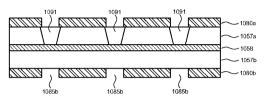

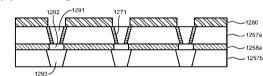

- 【図1B】図1Aの直線B-Bに沿って取られた図1Aに示した多層ガラスコアを有する 基板の立断面図を示す模式図である。

- 【図1C】多層ガラスコアを有する基板の他の一実施形態を示す、図1Bの立断面図の一 部を示す模式図である。

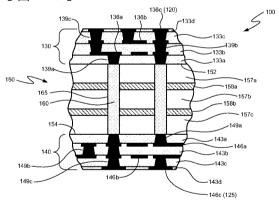

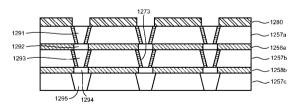

- 【図1D】多層ガラスコアを有する基板の更なる一実施形態を示す、図1Bの立断面図の 一部を示す模式図である。

- 【図1E】多層ガラスコアを有する基板の更なる他の一実施形態を示す、図1Bの立断面 図の一部を示す模式図である。

- 【図1F】多層ガラスコアを有する基板のより更なる一実施形態を示す、図1Bの立断面 図の一部を示す模式図である。

- 【図1G】多層ガラスコアを有する基板の他の代替的な一実施形態を示す、図1Bの立断 面図の一部を示す模式図である。

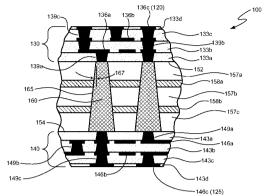

- 【 図 2 】 多 層 ガ ラ ス コ ア を 有 す る 基 板 の 一 実 施 形 態 を 含 む 集 積 回 路 ア セ ン ブ リ の 立 断 面 図 を示す模式図である。

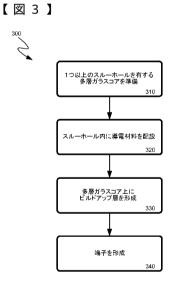

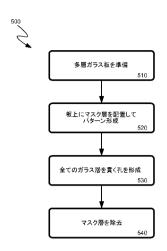

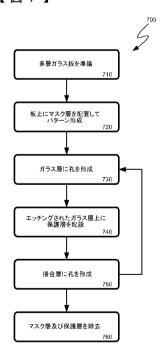

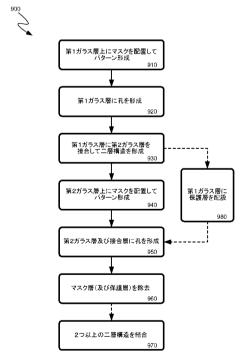

- 【図3】多層ガラスコアを有する基板を形成する方法の実施形態を示すブロック図である

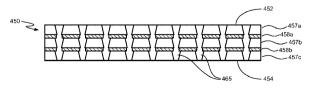

- 【図4A】図3の方法の実施形態を示す模式図である。

- 【図4B】図3の方法の実施形態を示す模式図である。

- 【図4C】図3の方法の実施形態を示す模式図である。

- 【 図 5 】 多 層 ガ ラ ス コ ア を 形 成 す る 方 法 の 一 実 施 形 態 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【図6A】図5の方法の実施形態を示す模式図である。

- 【図6日】図5の方法の実施形態を示す模式図である。

- 【図6C】図5の方法の実施形態を示す模式図である。

- 【図7】多層ガラスコアを形成する方法の他の一実施形態を示すブロック図である。

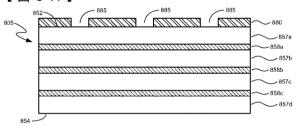

- 【図8A】図7の方法の実施形態を示す模式図である。

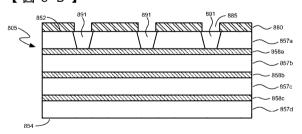

- 【図8B】図7の方法の実施形態を示す模式図である。

- 【図8C】図7の方法の実施形態を示す模式図である。

- 【図8D】図7の方法の実施形態を示す模式図である。

- 【図8E】図7の方法の実施形態を示す模式図である。

- 【図8F】図7の方法の実施形態を示す模式図である。

- 【図8G】図7の方法の実施形態を示す模式図である。

- 【図8H】図7の方法の実施形態を示す模式図である。

- 【図8Ⅰ】図7の方法の実施形態を示す模式図である。

- 【図8J】図7の方法の実施形態を示す模式図である。

- 【 図 9 】 多 層 ガ ラ ス コ ア を 形 成 す る 方 法 の 更 な る 一 実 施 形 態 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【図10A】図9の方法の実施形態を示す模式図である。

- 【図10B】図9の方法の実施形態を示す模式図である。

- 【図10C】図9の方法の実施形態を示す模式図である。

- 【図10D】図9の方法の実施形態を示す模式図である。

- 【図10E】図9の方法の実施形態を示す模式図である。

- 【図10F】図9の方法の実施形態を示す模式図である。

- 【図10G】図9の方法の実施形態を示す模式図である。

- 【図10日】図9の方法の実施形態を示す模式図である。

- 【 図 1 1 】 多 層 ガ ラ ス コ ア を 形 成 す る 方 法 の 更 な る 他 の 一 実 施 形 態 を 示 す ブ ロ ッ ク 図 で あ る。

- 【図12A】図10の方法の実施形態を示す模式図である。

- 【図12B】図10の方法の実施形態を示す模式図である。

- 【図12C】図10の方法の実施形態を示す模式図である。

20

30

40

- 【図12D】図10の方法の実施形態を示す模式図である。

- 【図12E】図10の方法の実施形態を示す模式図である。

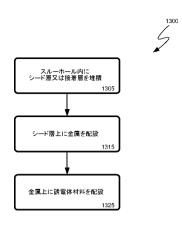

- 【図13】多層ガラスコアのスルーホール内に導電材料を配設する方法の実施形態を示す ブロック図である。

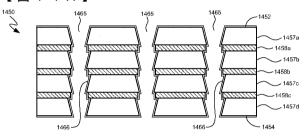

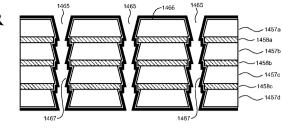

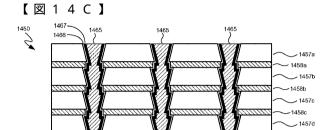

- 【図14A】図13の方法の実施形態を示す模式図である。

- 【図14B】図13の方法の実施形態を示す模式図である。

- 【図14C】図13の方法の実施形態を示す模式図である。

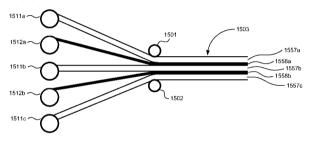

- 【図15】多層ガラス板を製造する方法の一実施形態を示す模式図である。

- 【図16A】多層ガラス板を製造する方法の他の一実施形態を示す模式図である。

- 【図16B】多層ガラス板を製造する方法の他の一実施形態を示す模式図である。

- 【図16C】多層ガラス板を製造する方法の他の一実施形態を示す模式図である。

- 【図16D】多層ガラス板を製造する方法の他の一実施形態を示す模式図である。

- 【図16E】多層ガラス板を製造する方法の他の一実施形態を示す模式図である。

- 【発明を実施するための形態】

#### [0007]

上述のように、開示の実施形態は、複数のガラス層で構成されたコアを有する基板を包 含する。一実施形態によれば、用語"ガラス"は非晶質固体を意味する。記載の実施形態 とともに使用され得るガラス材料の例には、純粋石英(例えば、ほぼ100%のSiO, )、ソーダ石灰ガラス、ホウケイ酸ガラス、及びアルミノケイ酸ガラスがある。しかしな がら、開示の実施形態はシリカベースのガラス組成に限定されず、その他の基材を有する ガラス(例えば、フッ化物ガラス、リン酸塩ガラス、カルコゲナイドガラスなど)も開示 の実施形態とともに使用され得る。また、所望の物理特性を有するガラスを形成するため に、その他の材料及び添加物の如何なる組み合わせがシリカ(又はその他の基材)と組み 合わされてもよい。そのような添加物の例は、上述の炭酸カルシウム(例えば、石灰)及 び炭酸ナトリウム(例えば、ソーダ)のみでなく、マグネシウム、カルシウム、マンガン 、アルミニウム、鉛、ホウ素、鉄、クロム、カリウム、硫黄及びアンチモン、並びにこれ ら 及 び そ の 他 の 材 料 の 炭 酸 塩 及 び / 又 は 酸 化 物 を も 含 む 。 上 述 の ガ ラ ス 及 び 添 加 物 は 、 開 示 の 実 施 形 態 と と も に 適 用 さ れ 得 る 数 多 く の 種 類 の 材 料 及 び 材 料 組 み 合 わ せ の う ち の 幾 つ かの例である。さらに、ガラスの層又は構造は、強度及び/又は耐久性を向上させるため に表面処理及び/又はコーティングを含んでいてもよく、ガラスの層又は構造はまた、内 部応力を低減するためにアニールされてもよい。

# [0008]

概して、用語"ガラス"はここでは、固形の非晶質であり得る有機高分子材料を意味しない。しかしながら、理解されるべきことには、一部の実施形態に従ったガラスは、その材料の成分のうちの1つとして炭素を含んでいてもよい。例えば、ソーダ石灰ガラス及びこのガラス種類の数多くのバリエーションは炭素を含んでいる。

### [0009]

ガラスは、固形物に形成された後に、軟化されたり、場合によって液体形態に再溶融されたりすることができる。ガラス材料の"ガラス転移温度"は、それより低くではガラスの物理特性が固体の物理特性に近く、且つそれより高くではガラス材料が液体のような挙動を示す温度である。ガラスがガラス転移温度より十分に低くにある場合、ガラスの分子群は相対的な可動性をほとんど有しなくなり得る。ガラスは、ガラス転移温度に近付くにつれて軟化し始め、更に温度が増すと最終的に液体状態へと溶融することになる。故に、ガラス体は、その塊の形状の操作を可能にするのに十分な程度まで軟化されることができ、ガラス体内に孔又はその他の造形を形成することが可能になる。

# [0010]

一実施形態によれば、ガラスの"軟化温度"は、開示の実施形態が実行されることを可能にするのに十分な程度までガラスが軟化される温度である。例えば、一実施形態において、ガラスの軟化温度は、ガラスが、その中に孔(若しくはビア)又はその他の造形を形成することを可能にするのに十分な軟らかさになる温度である。2つ以上の異なるガラス

10

20

30

40

材料が同様のガラス転移温度及び/又は軟化温度を有することがあるが、ガラス転移温度及び軟化温度はガラスの固有特性である。また、理解されるべきことには、特定のガラスのガラス転移温度と軟化温度とは必ずしも同一値ではない。

#### [0011]

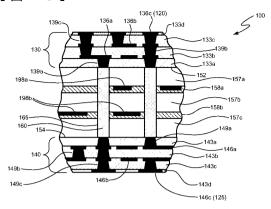

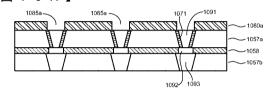

次に図1A及び1Bを参照するに、2つ以上のガラス層を有するコア150を含む基板100の実施形態が示されている。図1Aは基板100の平面図を示し、図1Bは、図1Aの直線B-Bに沿って取られた基板の立断面図を示している。また、多層ガラスコアを有する基板100の様々な選択的な実施形態を図1C乃至1Gに示す。図1C乃至1Gの各々は、図1Bで参照符号5によって大まかに特定される基板100の一部を拡大図にて示している。

#### [0012]

図1A及び1Bを参照するに、基板100は、多数のガラス層157a、157b及び157cを有するコア150を含んでいる。一実施形態において、コア150は更に、ガラス層157a、157b、157cの間に配置された接合層158a及び158bを含む(例えば、層158aがガラス層157aと157bとの間に配置され、等々)。基板100は、第1の面102と、それとは反対側の、第1の面102と概して平行な第2の面104とを有する。基板100の周縁108が第1の面102と第2の面104との間に延在している。一部の実施形態によれば、基板100の周縁108は概して長方形であり、一実施形態において、周縁108の4つ全ての側面は、周縁が正方形を形成するように実質的に相等しい。しかしながら、長方形ではない周縁を有する基板も開示の実施形態の範囲内である。一実施形態において、基板100は0.2mmと1.1mmとの間の厚さを有する。

#### [0013]

多層ガラスコア150は、第1表面152と、それとは反対側の第2表面154とを有する。一実施形態において、第1表面152及び第2表面154は互いに概して平行である。ガラスコア150の周縁158が第1表面152と第2表面154との間に延在しており、一部の実施形態において、ガラスコアの周縁158は基板の周縁108と概して一致する。一実施形態によれば、多層ガラスコア150は50μmと800μmとの間の厚さを有し得る。個々のガラス層157a、157b、157cは好適な如何なる種類のガラスを有していてもよい。一実施形態において、ガラス層157a・157cは同じガラス材料を有するが、他の実施形態において、ガラス層157a・157cのうちの何れかが、その他のガラス層のうちの何れかのガラス材料とは異なるガラス材料を有していてもよい。

#### [0014]

多数の導電体160が多層ガラスコア150内を延在している。各導電体160は孔(ホール)又はビア165内に配置され、各導電体160が第1表面152から第2表面154まで延在し得る。しかしながら、他の実施形態においては、導電体のうちの1つ以上がコア厚さ内を部分的にのみ延在する。一実施形態によれば、導電体160は、導電材料で充填された、コア150を貫いて形成された孔又はビア165を有する。

#### [0015]

導電体160は、金属、複合材料及び導電性ポリマーを含む好適な如何なる導電材料を有していてもよい。好適な金属は、銅、錫、銀、金、ニッケル、アルミニウム及びタングステン、並びにこれら及び/又はその他の金属の合金を含む。孔又はビア165を形成するために使用され得るプロセスは、例えば、エッチング、レーザドリル加工、インプリント、及びサンドブラスティングを含む。導電体160を形成するように、孔又はビア165内に、例えばめっき技術(電解めっき又は無電解めっき)、化学気相成長(CVD)、物理気相堆積(PVD)若しくはスクリーン印刷技術、及びこれら及び/又はその他のプロセスの組み合わせなどの好適プロセスによって、導電材料が堆積され得る。孔165の形成及び導電体160の形成の様々な実施形態については更に詳細に後述する。

### [0016]

10

20

30

20

30

40

50

基板100の第1の面102上に、第1組の導電端子120(図1A参照)が配設される。一実施形態によれば、第1組の端子120は、集積回路(IC)ダイ上に配設された対応する端子アレイと結合するパターンで配列される。図1A・1BはICダイを示しており、端子120はこのダイ領域(ダイシャドウ領域と呼ぶこともある)内にある。端子120は各々、ICダイの端子との電気を形成することが可能な如何なる好適種類の構造を有していてもよい。ピラーとは、アパンプが配設され得る。一実施形態において、ICダイはフリップチップはは100上に配置され、はんだリフロープロセスによって、ダイ上の端子が基板100上のはデンプが配設される。他の一実施形態によれば、ICダイは接着剤の層によって基板100に結合され、ワイヤボンドプロセスによって、ダイ上の端子が基板上の対応する端子につと結合され、ワイヤボンドプロセスによって、ダイ上の端子が基板上の対応する端子に高的に結合され得る(この実施形態において、端子120はダイ領域110の外側にある)。

#### [0017]

基板100の第2の面104上に、第2組の導電端子125(図示の明瞭性及び便宜のため、図1Aには一部のみを示す)が配設される。一実施形態によれば、第2組の端子125は、例えばメインボード、マザーボード又はその他の回路基板などの次階層の部品(図示せず)上に配設された対応する端子アレイと結合するパターンで配列される。端子125は各々、次階層部品の端子との電気接続を形成することが可能な如何なる好適種類の構造を有していてもよい。例として、端子125は、パッド、ランド、はんだバンプ若しくはその他の金属バンプ、又はピンを有し得る。次階層部品は、例えばランドグリッドアレイ(LGA)ソケット又はピングリッドアレイ(PGA)ソケットなど、基板100及び端子125を受け入れるためのソケット(及び保持機構)を含み得る。他の例では、端子125は、はんだリフロープロセスによって次階層部品の端子と結合されてもよい。

#### [0018]

コア 1 5 0 の 第 1 表 面 1 5 2 上 に 第 1 の ビル ド アップ 構 造 1 3 0 が 配 設 され 、 コア の 第 2 表面 1 5 4 上に第 2 のビルドアップ構造 1 4 0 が配設される。第 1 のビルドアップ構造 は、誘電体材料及び金属の1つ以上の交互層を有し、端子120は該第1のビルドアップ 構造130上に配置される(第1の基板面102は一般に第1のビルドアップ構造130 の外表面に相当する)。多層ガラスコア 1 5 0 内の導電体 1 6 0 のうちの少なくとも 1 つ が、 第 1 の ビル ド ア ッ プ 構 造 1 3 0 の 少 な く と も 1 つ の 金 属 層 と 電 気 的 に 結 合 さ れ 、 一 実 施形態において、第1のビルドアップ構造の、コア150に最も近い金属層が、少なくと も 1 つの 導電体 1 6 0 と結合される。同様に、第 2 のビルドアップ構造 1 4 0 は、誘電体 材料及び金属の1つ以上の交互層を有し、端子125は該第2のビルドアップ構造140 上に配置される(第2の基板面104は一般に第2のビルドアップ構造140の外表面に 相 当 す る )。 コ ア 1 5 0 内 の 導 電 体 1 6 0 の う ち の 少 な く と も 1 つ が 、 第 2 の ビ ル ド ア ッ プ構造140の少なくとも1つの金属層と電気的に結合され、一実施形態において、第2 のビルドアップ構造の、コア150に最も近い金属層が、少なくとも1つの導電体160 と結合される。第1及び第2のビルドアップ構造130、140は、第1組の端子120 と第2組の端子125との間で、電力と入力/出力(I/O)信号とをルーティングする (ひいては、基板100上に搭載されたICダイと次階層部品との間での電力送達及び信 号伝達を支援する)。ビルドアップ構造130、140については更に詳細に後述する。

# [ 0 0 1 9 ]

図1Cを参照するに、多層ガラスコア基板100の一実施形態が更に詳細に示されている。上述のように、この基板は、ガラス層157a、157b及び157cを有するコア150を含んでおり、コアは第1表面152とそれと反対側の第2表面154とを有している。上述のように、ガラス層157a・157cの間に接合層158a、158bが配置されている。図1A乃至1Gには3つのガラス層が示されているが、コア150は、基板100の所望の機械特性及び電気特性に応じて、如何なる好適数(例えば、2層、4層

以上など)のガラス層を有していてもよい。ガラス層157a‐157cは好適な如何なる厚さを有していてもよく、一実施形態において、各ガラス層はおよそ50μmと200μmとの間の厚さを有する。また、一実施形態において、ガラス層157a‐157cは、(図示のように)全てが同じ厚さを有していてもよいし、それに代えて、ガラス層157a‐157cのうちの何れか1つがその他のガラス層のうちの1つ以上とは異なる厚さを有していてもよい。接合層158a‐158bもまた、好適な如何なる厚さを有していてもよく、一実施形態において、各接合層はおよそ20μmと100μmとの間の厚さを有する。一実施形態によれば、接合層158a‐158bのじ厚さを有する。しかしながら、他の実施形態においては、接合層158a‐158bのうちの何れか1つがその他の接合層のうちの1つ以上とは異なる厚さを有し得る。

[0020]

別個のガラス層 1 5 7 a 、 1 5 7 b 、 1 5 7 c は、如何なる好適技術によってともに接 合されてもよい。一実施形態において、接合層158a、158bがガラス層間に配置さ れ、これら接合層の各々が2つの隣接するガラス層と結合される(例えば、接合層158 a がガラス層 1 5 7 a 及び 1 5 7 b と結合され、等々)。一実施形態によれば、各接合層 1 5 8 a 、 1 5 8 b は接着剤を含み、更なる一実施形態において、接合層 1 5 8 a 、 1 5 8bは有機材料を有する。一実施形態によれば、各接合層158a、158bは、例えば アクリル樹脂又はエポキシ樹脂を有するフィルムなどのドライフィルム接着材を有する。 しかしながら、理解されるべきことには、開示の実施形態は接着接合に限定されず、また 、多層ガラスコア150は接着剤を用いずに形成されてもよい。一部の実施形態において ガラス層157a-157cは拡散接合によってともに結合され得る。例えば、一実施 形態において、接合層158a-158bは、層157a-157cのガラス材料と拡散 結合を形成することが可能な材料を有する(例えば、接合層158aがガラス層157a 及び 1 5 7 b の各々と拡散結合を形成し、等々)。他の例では、ガラス層 1 5 7 a - 1 5 7cが互いに直接的に拡散結合されてもよく(例えば、ガラス層157aがガラス層15 7 b と拡散結合され、等々)、その場合、接合層 1 5 8 a - 1 5 8 b は省略され得る。他 の実施形態において、ガラス層157a‐157cは機械的に接合され得る。例として、 一 実 施 形 態 に お い て 、 ス ル ー ホ ー ル 1 6 5 内 に 堆 積 さ れ た 導 電 材 料 1 6 0 が 、 ガ ラ ス 層 1 57a-157cをともに固定するよう機能し得る。更なる一実施形態において、ガラス 層157a-157cは直接酸化物間接合を用いてともに固定されてもよい。

[0021]

一実施形態によれば、第1のビルドアップ構造130は、多数の誘電体層133a、133b、133c、133dと、多数の金属層136a、136b、136cを有する。誘電体層133a・133dは好適な如何なる誘電体材料(例えば、ポリマー材料など)を有していてもよく、また、好適な如何なる技術(例えば、堆積、ラミネーションなど)によって形成されてもよい。金属層136a・136cは好適な如何なる導電材料(例えば、銅、アルミニウム、銀など)を有していてもよく、また、好適な如何なる技術(例えば、電解めっき又は無電解めっきなどのめっきプロセス)によって堆積されてもよい。また、金属層136a・136cは各々、電力及びI/O信号のルーティングを容易にするのに好適な数及び構成の配線、電源プレーン、グランドプレーン、及びその他の導電体を形成するようにパターニングされ得る。

[ 0 0 2 2 ]

如何なる2つの隣接する金属層136a-136cの間にも誘電体層133a-133dのうちの1つが配置され(例えば、金属層136aと136bとが誘電体層133bによって離隔され、等々)、誘電体層133aはコア150に隣接し、金属層136aをコアから離隔している。一実施形態によれば、誘電体層133aはコアの第1表面152に直接的に接触する。金属でめっきあるいは充填されたビア139a、139b、139cが、それぞれ、誘電体層133b、133cを貫通して延在し、隣接し合う金属層を相互接続する(例えば、ビア139bが金属層136aと金属層136bとを相互接続し、等々)。また、多層ガラスコア150に最も近い金属層136aは、誘電体層1

10

20

30

40

3 3 a 内に配設されたビア 1 3 9 a によって、導電体 1 6 0 のうちの 1 つ以上と結合される。一実施形態において、コア 1 5 0 の第 1 表面 1 5 2 は、ビルドアップ構造 1 3 0 の誘電体材料との密着性を高めるための表面処理又はコーティングを含んでいてもよい。また、一部の実施形態において、最も外側の誘電体層 1 3 3 d はレジスト層及び/又はパッシベーション層を有し得る。また、一実施形態によれば、最も外側の金属層 1 3 6 c によって、あるいはその上に、端子 1 2 0 が形成される。

[0023]

一実施形態において、第2のビルドアップ構造140は、多数の誘電体層143a、143b、143c、143dと、多数の金属層146a、146b、146cを有する。誘電体層143a・143dは好適な如何なる誘電体材料(例えば、ポリマー材料など)を有していてもよく、また、好適な如何なる技術(例えば、堆積、ラミネーションなど)によって形成されてもよい。金属層146a・146cは好適な如何なる導電材料(例えば、銅、アルミニウム、銀など)を有していてもよく、また、好適な如何なる技術(例えば、電解めっき又は無電解めっきなどのめっきプロセス)によって堆積されてもよい。また、金属層146a・146cは各々、電力及びI/O信号のルーティングを容易にするのに好適な数及び構成の配線、電源プレーン、グランドプレーン、及びその他の導電体を形成するようにパターニングされ得る。

[0024]

如何なる2つの隣接する金属層146a-146cの間にも誘電体層143a-143dのうちの1つが配置され(例えば、金属層146bとが誘電体層143a-143bによって離隔され、等々)、誘電体層143aはコアの第2表面 1450に隣接し、金属層146aと17のの第2表面 150に隣接しての第2表面 150に隣接しての第2表に直接的に接触する。金属でめっきあるいは充填されたビア149b、149c、149b、149cが金属層146cに最后では、ビア149bが金属層146cに最后に最近に表する(例えば、ビア149bが金属層146aは、誘電体層146cによる。また、ションによって、導電416cによいで、コア150の第2表面154は、ビルドアップ構造140のまた、一実施形態において、コア150の第2表面154は、ビルドアップ構造140のまた、一実施形態において、最も外側の誘電体層143dはレジスト層及ではパーション層を有し得る。また、一実施形態によれば、最も外側の金属層146cによって、あるいはその上に、端子125が形成される。

[0025]

図1Cの実施形態(並びに、図1D及び1Gの各々に示す実施形態)においては、第1及び第2のビルドアップ構造は、相等しい数の誘電体層及び金属層を有するとともに、概して相等しい厚さを有している。しかしながら、開示の実施形態はそのように限定されず、他の実施形態においては、第1及び第2のビルドアップ構造は、相異なる厚さ、及び/又は相異なる数の誘電体層及び金属層を有していてもよい。他の一実施形態によれば、ビルドアップ構造は多層ガラスコア150の一方側のみに配設される。また、一部の実施形態において、第1及び第2のビルドアップ構造は同じ誘電体材料及び金属から構築される。しかしながら、他の実施形態においては、第1及び第2のビルドアップ構造は相異なる材料を有していてもよい。

[0026]

図1Cの実施形態においては、誘電体層133a及び143aが多層ガラスコア150に隣接して位置し、コアに最も近い金属層(すなわち、金属層136a及び146a)がこれらの誘電体層によってコアから離隔されている。これに代わる一実施形態においては、図1Dに示すように、多層ガラスコア150に金属層が隣接してもよい。コア150の片側又は両側に隣接して金属層を組み込むことは、"コア層ルーティング"と呼ばれることもある。

[0027]

10

20

30

40

20

30

40

50

図1Dを参照するに、この実施形態に係る基板100は、図1Cに示したものと概して同様である(同様の部分は同じ参照符号によって識別している)。しかしながら、図1Dの実施形態においては、第1のビルドアップ構造130が、多層ガラスコア150に隣接する金属層136×を含んでおり、一実施形態によれば、金属層136×はコアの第1表面152に直に接触する。誘電体層133aは金属層136×(及びコアの露出部分)の上に位置しており、ここでは、コアに最も近い金属層はこの金属層136×であり、導電体160のうちの少なくとも1つが金属層136×に結合される。また、他の一実施形態において、コア150の第1表面152は、金属層136×(及び、恐らくは、誘電体層133aの部分群)との密着性を高めるための表面処理又はコーティングを含み得る。

[0028]

第1のビルドアップ構造130と同様に、図1Dの第2のビルドアップ構造140は、多層ガラスコア150に隣接する金属層146×を含んでおり、一実施形態において、金属層146×はコアの第2表面154に直に接触する。誘電体層143aは金属層146×(及びガラスコアの露出部分)の上に位置しており、ここでは、コアに最も近い金属層146×にある。また、他の一実施形態において、コア150の第2表面154は、金属層146×(及び、恐らくは、誘電体層143aの部分群)との密着性を高めるための表面処理又はコーティングを含み得る。一部の実施形態において、コアの両側の表面152、154のうちの一方のみが隣接する金属層を有する(例えば、第1及び第2のビルドアップ構造130、140それぞれの金属層136×、146×のうちの何れか一方が省略され得る)。

[0029]

図1Eを参照するに、更なる一実施形態に係る多層ガラスコア基板100が示されている。図1Eに示す実施形態に係る基板100は、図1Cに示したものと概して同様である(同様の部分は同じ参照符号によって識別している)。しかしながら、図1Eの実施形態においては、その中に各導電体160が配置される孔又はビア165は、コア150の下さにわたって傾斜を有するテーパー壁を有している。一実施形態において、孔又はロア165のテーパー壁は、該孔の中心線に対して0と45。との間の角度167を有することので、多層ガラスコア150を貫通するために使用することのであり得る。上述のように、孔又はビア165を形成するために使用されるプロセスは、例えば、エッチング、レーザドリル加工、インプリント、及テーパー壁を有する孔165を形成し得る。理解されるように、形成技術及びプロセス条件に応じて、上述の技術のがプロセス条件に応じて、「とでは、図1Eに描かれた直線状のテーパー壁以外の形状を有し得る。例えば、他の実施形態において、ビアの壁は曲線状となり得る(例えば、ビアは扇形の断面形状を有し得る)。

[0030]

次に、図1Fを参照するに、更なる一実施形態に係る多層ガラスコア基板100が示されている。図1Fに示す実施形態に係る基板100は、図1Cに示したものと概して同様である(同様の部分は同じ参照符号によって識別している)。しかしながら、図1Fの実施形態においては、その中に各導電体160が配置される孔又はビア165は、別個のガラス層157a、157b、157c、及び接合層158a、158bの各々に形成された多数の別々の整列された孔を有している。例えば、スルーホール165は、ガラス層157a内のビア159aと、接合層158a内のビア159bと、ガラス層157b内のビア159cと、接合層158b内のビア159dと、ガラス層157c内のビア159eとを有し得る。一般に、これら別々の孔159a‐159eは共通の中心線に沿ってアライメントされるが、一部の実施形態において、これら別々の孔の間にミスアライメントが存在し得る。

[0031]

一実施形態によれば、ガラス層内に形成されるビア(例えば、ビア159a、159c

20

30

40

50

、159e、及び場合により接合層158a、158b)は、そのガラス層(又は接合層)の厚さにわたって傾斜されたテーパー壁を有し得る。一実施形態において、1つのビアのテーパー壁は、その孔の中心線に対して0と45°との間の角度169を有する。ビア(例えば、ビア159a・159e)のテーパー壁は、形成プロセスの結果であり得る。上述のように、ガラス層を貫通する(及び接合層を貫通する)ビアを形成するために使用され得るプロセスは、例えば、エッチング、レーザドリル加工、インプリント、及びサンドブラスティングを含む。処理条件に応じて、上述の技術のうちの何れか1つが、テーパー壁を有するビアを形成し得る。理解されるように、形成技術及びプロセス条件に応じて、ビアは、図1Fに描かれた直線状のテーパー壁以外の形状を有し得る。他の実施形態において、ビアの壁は曲線状となり得る。例えば、ビアは扇形の断面形状を有し得る(例えば、図8Jを参照)。

[0032]

次に、図1Gを参照するに、更なる一実施形態に係る多層ガラスコア基板100が示されている。図1Gに示す実施形態に係る基板100は、図1Cに示したものと概してのよび、図1Gに示すに係る基板100は、図1Cに示したものと概してののである(同様の部分は同じ参照符号によって識別している)。しかしながら、図1Gのの形態においては、接合層158a、158bのうちの何れか1つ以上が導電体を含むことができる。導電体198aを含むことができ、接合層158bは、するための配線、及び/又は電力をルーティングするための配線を有し得る。また場がするための配線、198bは、別との真電体198a、198bは、別との合層158a、158bのうちの何れか1つ以上の導電体198a、198bは、別との合層158a、158bのうちの何れか1つ以上の導電体198a、198bは、別との合層158a、158bの双方が導電体を含んでいるまた、図1Gにおいては接合層158a、158bの双方が導電体を含んでいる。また、図1Gにおいては接合層158a、158bの双方が導電体を含んでいてもよい。

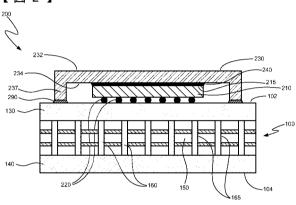

[0033]

図 2 は、多層ガラスコア基板 1 0 0 を含んだアセンブリ(組立体) 2 0 0 の一実施形態 を示している。図2を参照するに、アセンブリ200は、多層ガラスコア150と第1の 面102及び反対側の第2の面104とを有する基板100を含んでいる。基板の第1の 面102上に、集積回路(IC)ダイ210が配置されている。ICダイ210は、多数 のインターコネクト220によって、基板100と電気的(且つ機械的)に結合されてい る。基板の第2の面104上の端子125(例えば、ランド、ピン、はんだバンプなど) (図1A参照)が、例えばマザーボード、メインボード又はその他の回路基板などの次階 層部品との電気接続を形成するために使用され得る。第1表面232と、それと反対側の . ダイの裏面 2 1 5 に面する第 2 表面 2 3 4 と、を有するヒートスプレッダ又は蓋 2 3 0 が、ダイ210上に配設され、サーマルインタフェース(熱接続)材料の層240を介し てダイの裏面 2 1 5 と熱的 ( 恐らくは、且つ機械的に ) に結合される。ガラスコア基板 1 0 0 の第 1 の面 1 0 2 にヒートスプレッダ 2 3 0 を固定するために、接着剤又は封止材 2 90が使用され得る。図2には示していないが、更なる一実施形態において、ヒートシン ク(又はその他の冷却装置)がヒートスプレッダ230と熱的に結合され、ヒートスプレ ッダの第1表面232とヒートシンク(又はその他の装置)との間に別のサーマルインタ フェース材料層が配置されてもよい。

[0034]

ICダイ210は如何なる種類の半導体デバイスを有していてもよい。一実施形態において、ICダイ210は演算処理用のシステム又はデバイスを有する。例えば、ICダイ210はマイクロプロセッサ又はグラフィックプロセッサを有し得る。ICダイ210は、任意数の命令フォーマットを有する任意数のプロセッサアーキテクチャからの命令を実行することができる。一実施形態において、命令は、インテル社によって使用されているような"×86"命令である。しかしながら、他の実施形態において、プロセッサは、その他のアーキテクチャ又はその他のプロセッサ設計者からの命令を実行してもよい。他の

20

30

40

50

一実施形態において、ICダイ210はメモリデバイスを有する。更なる一実施形態によれば、ICダイ210はシステム・オン・チップ(SoC)を有する。更なる他の一実施形態において、ICダイ210は、デジタル回路、アナログ回路、又はアナログ回路及びデジタル回路双方の組み合わせを含んでいてもよい。

#### [0035]

インターコネクト220は、例えばはんだリフロープロセスにより、基板の第1の面102上の端子120(図1A参照)をICダイ210上の端子と結合することによって形成される。上述のように、基板端子120は各々、好適な金属又は複数の金属の組み合わせ(例えば、銅、ニッケル、アルミニウムなど)から形成されたパッド、ピラー又はスタッドバンプを有することができ、ダイ端子もまた、好適な金属又は複数の金属の組み合わせから形成されたパッド、ピラー又はスタッドバンプを有し得る。基板端子及び/又はがら形成されたパッド、ピラー又はスタッドバンプを有しけんだが配置され、そしてダイ端子の上に(例えば、ボール又はバンプの形態をした)はんだが配置され、そしてダイボーコープロセスを用いてこれらの端子が結合される。理解されることが可能なインターコネクトは、基板100とICダイ210との間に形成されることが可能なインターコネクト種類のうちの単なる一例であり、その他の好適種類のインターコネクトが使用されてもよい。また、インターコネクト220の周り、及びICダイ210と基板の第1の面102との間に、アンダーフィル材料の層(図2には図示せず)が配設されてもよい

### [0036]

ヒートスプレッダ230は、好適な如何なる熱伝導材料を有していてもよく、また、好適な如何なる形状又は構造を有していてもよい。一実施形態によれば、ヒートスプレッダ230は、基板の第1の面102に向かって延在する側壁(又は複数の側壁)237を含む蓋を有し、この側壁(又は複数の側壁)が接着剤290によって基板表面102に固定される。上述の蓋は一体化ヒートスプレッダ(integrated heat spreader;IHS)と呼ばれるときもある。ヒートスプレッダ230を構築するために使用され得る材料は、金属(例えば、銅及びその合金)、熱伝導性コンポジット及び熱伝導性ポリマーを含む。

### [ 0 0 3 7 ]

図2に示した実施形態において、アセンブリ200は単一のICダイ210を含んでいる。しかしながら、他の実施形態において、アセンブリ200はマルチチップパッケージを有していてもよい。例えば、1つ以上のその他の集積回路ダイ(例えば、メモリデバイス、電圧調整器など)が基板100上に配置され得る。さらに、例えばキャパシタ及びインダクタなどの受動デバイスが、ガラスコア基板100上に配置されたり、あるいは基板のビルドアップ構造130、140に集積されたりしてもよい。例として、アレイキャパシタ又は薄膜キャパシタが、基板のビルドアップ構造130、140に集積され得る。他の一実施形態において、例えばアンテナ又はRFシールドなどの無線部品が、ガラスコア基板100上に配置されたり、あるいは該基板のビルドアップ構造130、140に集積されたりしてもよい。これらの追加デバイスは、ICダイ、受動デバイス又はその他の部品の何れであろうと、ガラスコア基板100の何れかの側102、104に配置され得る

# [0038]

アセンブリ200は、如何なる種類の計算装置の一部を形成してもよい。一実施形態によれば、アセンブリ200はサーバ又はデスクトップコンピュータの一部を形成し得る。他の一実施形態において、アセンブリ200はラップトップコンピュータ又は同様の移動計算装置(例えば、ネットトップコンピュータ)の一部を形成する。更なる一実施形態において、アセンブリ200は、例えばセル方式電話、スマートフォン又はモバイルインターネット装置(MID)などの手持ち式計算装置の一部を有する。更なる他の一実施形態において、アセンブリ200は埋込計算装置の一部を形成する。

#### [0039]

図3は、多層ガラスコア基板を製造する方法の一実施形態を示している。図3の方法は更に図4A-4Cに示されており、以下の説明では、これらの図を参照する。

#### [0040]

図3のブロック310を参照するに、一実施形態において、1つ以上のスルーホールを有する多層ガラスコアが準備される。これは、コア450を示す図4Aに例示されている。多層ガラスコア450は、図1AA乃至1Gに示して説明したコア150の実施形態である。多層ガラスコア450は、接合層458a、458bによってともに固定された別々のガラス層457a、457cを含んでおり、該コア450に表面452と概して平行な第2表面454まで延にしている。孔又はピア465が第1表面452から第2表面454まで延にしてい如何を有している。孔又はピア465が第1表面452から第2表面454まで延にしてい如何を有しているのガラス層457cは、用途及び/又は所望特性に応いの明までのガラスを有していてもよく、また、円分の道域のガラスを有していてもよく、また、コア450は、2つ以上のる好適していてもよい。一実施形態において、コア450は、2つ以上の場にするサイズ及び構成を有する。更なる一実施形態において、コア450は、2つ以上の場が切り出されるパネルを有する)。1つの表に表によれば、コア450は、2つ以上の場に基板の形成を可能にするサイズ及び構成を有する。更なる一実施形態において、コア450は、2つ以上の場が切り出されるパネルを有する)。200111の名に表が切り出されるパネルを表では、200111の名に対しては更に詳細に後述する。それらの実施形態については更に詳細に後述する。

#### [0041]

ブロック320を参照するに、スルーホール内に導電材料が配置され、導電体が形成される。これは図4Bに例示されており、そこでは、導電材料が孔465内に配置されて導電体460を形成している。

#### [0042]

導電材料460はビア465内に、例えばめっき技術(電解めっき若しくは無電解めっき)、CVD、PVD若しくはスクリーン印刷技術、及びこれら及び/又はその他のプロセスの組み合わせなどの好適プロセスによって堆積され得る。コア450内の導電体460を形成する材料は、金属、複合材料及び導電性ポリマーを含む好適な如何なる導電材料を有していてもよい。好適な金属は、銅、錫、銀、金、ニッケル、アルミニウム及びタングステン、並びにこれら及び/又はその他の金属の合金を含む。

#### [0043]

多層ガラスコアのスルーホール内に導電体を形成する方法の一実施形態を図13に示し、今からそれを説明する。図13の方法の実施形態は更に図14A-14Cの模式図に示されており、以下の説明では、図13及び14A-14Cを参照する。

### [0044]

図13のブロック1305を参照するに、多層ガラスコア内のスルーホールの壁にシード層又は接着層が堆積される。これは更に、コア1450を示す図14Aに示されている。コア1450は、接合層1458a、1458b、1458cによってともに結合されたガラス層1457a、1457b、1457c、1457dを有している(例えば、接合層1458aがガラス層1457a及び1457bの双方に結合され、等々)。スール1465が、コアの第1表面1452から、それと反対側のコアの第2表面1454まで、コア1450を貫いて延在している。孔1465は、例えばエッチング、レードリル加工、インプリント、及びサンドブラスティングなどの好適な方法又は複数の方法りの組み合わせによって形成され得る。スルーホール1465の壁にシード層1466が増でれる。なお、他の実施形態において、シード層1466に先立って、1つ以上のの他の材料層が堆積されてもよい。例えば、シード層1466の堆積に先立って、スルービア1465の壁に誘電体層が堆積され得る(例えば所望のキャパシタンスを達成するため、等々)。

# [0045]

シード層1466の上には、後続の金属層が堆積されることになる。シード層は146 6、層1457a-1457dのガラス材料(及び接合層1458a-1458cの材料 )と、続いて堆積される金属層とに接着することが可能な如何なる材料を有していてもよ い。好適なシード層材料は、銅、チタン、クロム、ニッケル若しくはバナジウム、及びこ 10

20

30

40

20

30

40

50

れら及び / 又はその他の金属の合金を含む。また、シード層1466は、無電解めっき、電解めっき、CVD又はPVDを含む好適な如何なる技術を用いて堆積されてもよい。一実施形態において、ブランケット(全面)堆積技術が用いられ、シード層1466は、図14Aに示すように、コア1450の第1及び第2の表面1452、1454上にも延在し得る。シード層1466は好適な如何なる厚さを有していてもよく、一実施形態において、この層は0.1μmと0.5μmとの間の厚さを有する。

[0046]

ブロック1315にて説明するように、シード層上に金属が配設される。これは図14 Bに示されており、そこでは、金属層1467がシード層1466上に配設されている。 金属層1467は、銅、アルミニウム、ニッケル、銀若しくは金、及びこれら及び/又は その他の金属の合金などの好適な如何なる導電性金属を有していてもよい。金属層146 7は、無電解めっき、電解めっき、CVD又はPVDを含む好適な如何なる技術を用いて 堆積されてもよい。一実施形態において、ブランケット堆積技術が用いられ、金属層14 67は、図14Bに示すように、コア1450の第1及び第2の表面1452、1454 上にも延在し得る。金属層1467は好適な如何なる厚さを有していてもよく、一実施形 態において、この層は5μmと30μmとの間の厚さを有する。他の一実施形態において 、シード層1466上に堆積される金属1467はスルーホール1465を実質的に充填 する。

[0047]

次に、ブロック1325を参照するに、スルーホールを充填するように、金属層上に誘電体材料が配設される。これは図14Cに示されており、そこでは、各孔1465の内部の空隙を充填するように、誘電体材料1468が金属層1467上に配設されている。誘電体材料1468は好適な如何なる材料を有していてもよく、一実施形態において、誘電体材料1468は有機材料を有する。また、誘電体材料1468は、例えばスクリーンが刷、CVD又はPVDなどの好適な如何なる技術を用いて堆積されてもよい。しかしながら、やはり、金属層1467がスルーホール1465を実質的に充填してもよく、その場合、誘電体材料は省略され得る。更なる一実施形態において、図14Cに示すように、余分なシード層1466及び余分な金属層1467が、コア1450の第1及び第2の表面1452、1454から除去され得る。余分なシード層及び金属層は、例えば、研削プロセス、化学的機械的研磨技術又はエッチングプロセスによって表面1452、1454から除去され得る。

[0048]

[0049]

次に、図3のブロック340を参照するに、基板上に導電端子が形成され得る(図4A-4Cには端子は示していない)。第1組の端子が第1のビルドアップ構造430上に形成され、第2組の端子が第2のビルドアップ構造440上に形成され得る。このような端子の構造及び形成法については、図1A乃至1Gを参照した上述の説明にて更に詳細に説

明されている。

#### [0050]

上述のように、一実施形態において、多層ガラスコア 4 5 0、並びに第 1 及び第 2 のビルドアップ構造 4 3 0、 4 4 0 は、 2 つ以上の基板に対応する構造及び機能を含む。この実施形態において、コア 4 5 0 (ビルドアップ構造 4 3 0、 4 4 0を備える)は、(端子の形成の前又は後の何れかで)それら別個の基板へと個片化されることになる。

#### [0051]

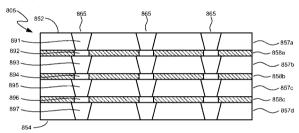

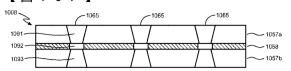

続いて、図5を参照するに、1つ以上のスルーホールを有する多層ガラスコアを形成する方法の一実施形態が示されている。図5に示す方法は更に図6A-6Cの模式図に示されており、以下の説明では、これらの図を参照する。

#### [0052]

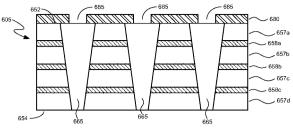

図5のブロック510を参照するに、多層ガラス板が準備される。これは、多層ガラス板605を示す図6Aに例示されている。板605は、接合層658a、658b、658cによってともに貼り付けられた多数のガラス層657a、657b、657c、657dを有している(例えば、接合層658aがガラス層657a及び657bと結合され、等々)。多層ガラス板605はまた、第1表面652と第2表面654との間に延在する周縁651を有する。一実施形態によれば、多層ガラス板605は50µmと800µmとの間の厚さを有し得る。一実施形態において、多層ガラス板は、単一の基板コアの形成を可能にするサイズ及び構成を有する(例えば、板605は、2つ以上の基板コア、すなわち、2つ以上の基板が切り出されることになるパネルを有する)

### [0053]

個々のガラス層657a-657dは、如何なる好適種類のガラスを有していてもよい。一実施形態において、ガラス層657a-657dは同じガラス材料を有する。しかしながら、他の実施形態においては、ガラス層657a-657dのうちの何れか1つが、その他のガラス層のうちの何れかのガラス材料とは異なるガラス材料を有していてもよい。図6A-6Cには4つのガラス層が示されているが、板605は、板605から形成されるコア(又は、複数のコア)の所望の機械特性及び電気特性に応じて、如何なる好適数のガラス層(例えば、二層、三層、5層以上など)を有していてもよい。ガラス層657a-657dは好適な如何なる厚さを有していてもよく、一実施形態において、ガラス層はおよそ50μmから200μmの厚さを有する。また、一実施形態において、ガラス層657a-657dは、(図示のように)全てが同じ厚さを有していてもよいし、それに代えて、ガラス層657a-657dのうちの何れか1つがその他のガラス層のうちの1つ以上とは異なる厚さを有していてもよい。

#### [0054]

接合層658a-658cもまた、好適な如何なる厚さを有していてもよく、一実施形態において、各接合層はおよそ20μmから100μmの厚さを有する。一実施形態によれば、接合層658a-658cは、(図示のように)全てが同じ厚さを有する。しかしながら、他の実施形態においては、接合層658a-658cのうちの何れか1つがその他の接合層のうちの1つ以上とは異なる厚さを有し得る。

#### [0055]

別個のガラス層657a、657b、657c、657dは、如何なる好適技術によってともに接合されてもよい。一実施形態において、図示のように、接合層658a、658b、658cがガラス層間に配置され、これら接合層の各々が2つの隣接するガラス層と結合される(例えば、接合層658aがガラス層657a及び657bと結合され、等々)。一実施形態によれば、各接合層658a・658cは接着剤を含み、更なる一実施形態において、接合層は有機材料を有する。一実施形態において、各接合層658a・658cは、例えばアクリル樹脂又はエポキシ樹脂を有するフィルムなどのドライフィルム接着材を有する。

10

20

30

40

#### [0056]

続いて、図15及び図16A-16Eを参照して、接着性の接合層を用いて複数のガラス層をともに結合する様々な方法を説明する。しかしながら、理解されるべきことには、開示の実施形態は接着接合に限定されず、また、多層ガラス板605(ひいては、この板から形成されるコア)は接着剤を用いずに作製されてもよい。例えば、上述のように、他の実施形態においては、複数のガラス層は、直接酸化物間接合や拡散接合(隣接し合うガラス層間に中間層を有する、あるいは有しないかの何れでもよい)を用いてともに結合されてもよい。あるいは、これらガラス層は、機械的に(例えば、板605を貫いて延在するスルーホール内に堆積された材料によって)ともに固定されてもよいし、これら及び/又はその他の技術の組み合わせによってともに固定されてもよい。

[0057]

図15を参照するに、一実施形態において、多層ガラス板は、ローラーラミネーションプロセスを用いて形成される。図15の実施形態において、第1のガラスシート源1511 b、第2の接着フィルム源1512a、第2のガラスシート源1511 b、第2の接着フィルム源1512 a、第2のガラスシート源1511 b、第2の接着フィルム源1512 b、及び第3のガラスシート源1511 c が、連続的に、ローラー1501と1502との間でともに押し付けられて、多層ガラスラミネート(積層板)1503が形成される。多層ガラスラミネート1503は、図示のように、接着層1558 a及び1558 b によってともに結合された別個のガラス層1557 a、1557 b 及び1557 c を有する。ガラスラミネート1503を形成するために、接着層によって、如何なる好適数のガラスシートがともに結合されてもよい。そして、ガラスラミネート1503は、1つ以上の多層ガラス板(例えば、3つの接着層によってともに結合された4つのガラス層を有する板605など)を形成するように好適な長さに切断され得る。

[0058]

次に、図 1 6 A - 1 6 E を参照するに、他の一実施形態において、多層ガラス板は、取 り外し可能なキャリア上でのラミネーションによって形成される。図16Aに示すように 、 リリース可能な接着剤 1 6 0 4 により、第 1 のガラス層 1 6 5 7 a が取り外し可能キャ リア 1 6 0 2 に接着される。一実施形態において、リリース可能接着剤 1 6 0 4 は、紫外 ( U V ) 光への曝露下で分解する接着剤材料を有する。他の一実施形態において、リリー ス可能接着剤1604は、溶剤への曝露下で分解する接着剤材料を有する。図16Bに示 すように、ガラス層1657a上に第1の接着層1658aが配設される。一実施形態に おいて、接着層1658aはドライフィルム接着材を有し、他の一実施形態において、接 着層1658aは、ガラス層1657a上にスプレー塗布あるいは印刷された後にキュア される液体接着剤を有する。図16Cを参照するに、その後、第1の接着層1658a上 に第2のガラス層1657bが配設され、上述のプロセスが繰り返される。例えば、図1 6 D に示すように、ガラス層 1 6 5 7 b 上に第 2 の接着層 1 6 5 8 b が配設され(ドライ フィルム又は液体の何れかとして設けられる)、この第2の接着層上に第3のガラス層1 6 5 7 c が配設される。図16Eに示すように、リリース可能接着剤1604の分解によ って(例えば、UV光の投与によって、溶剤の投与によってなど)、キャリア1602が リリース(解放)され、独立した多層ガラス板1605が残される。

[0059]

次に、図5に戻るに、ブロック520にて説明されるように、マスク層が多層ガラス板上に配置されてパターニングされる。これは図6Aにも示されており、そこでは、マスク層680が板605の第1表面652上に配置されている。また、マスク層680は、開口685を形成するようにパターニングされている。マスク層680は、層657aに接着することが可能で、且つパターン形成のために改変可能な如何なる材料を有していてもよい。例えば、マスク層680は、フォトリソグラフィ・エッチング技術によってパターニングされることができるフォトレジスト材料を有し得る。さらに、マスク層680は、後続のガラス層及び接合層の一部の除去(例えば、ウェットエッチングプロセス)に耐えることが可能な材料を有する。

[0060]

10

20

30

20

30

40

50

ブロック530にて説明されるように、全てのガラス層及び接合層を貫通するように孔 が形成される。これは図6Bに示されており、そこでは、マスク層680の開口685に 対応する位置にスルーホール665が形成されている。孔665は、全てのガラス層65 7 a - 657dと全ての接合層658a - 658cを貫いて延在している。しかしながら 、他の実施形態において、孔665のうちの1つ以上は板の厚さの一部のみにわたって延 在してもよい。一実施形態によれば、ビア665は、ガラス層及び接合層を除去するエッ チングケミストリ(又は複数のエッチングケミストリ)を使用するウェットエッチングプ ロセス(又は複数のウェットエッチングプロセス)によって形成される。例えば、ガラス を除去することができるエッチャントは、フッ酸(HF)を含む溶液を有することができ 、 あ る い は 、 そ れ に 代 え て 、 酸 化 物 エ ッ チ ン グ 又 は 緩 衝 酸 化 物 エ ッ チ ン グ が 用 い ら れ て も よい。接合層658a-658cの材料を除去することができるエッチャントは、適切な 溶媒を含んだ溶液を有し得る。他の一実施形態において、ビア665はドライエッチング プロセス(例えば、ガラスを除去するフッ化炭素ガスを有するエッチャントと、接合層を 除去する酸素及び/又は水素を有するエッチャント)によって形成されてもよい。スルー ホール665の形成後、ブロック540にて説明され且つ図6Cに示されるように、マス ク層680が多層ガラス板から除去され得る。

[0061]

図5の実施形態(並びに、図7、9及び112それぞれの実施形態)において、様々なガラス層材料及び接合層材料の中にビアを形成するために、エッチングプロセス(又は複数のエッチングプロセス)が使用されている。しかしながら、開示の実施形態は、エッチングによる孔形成に限定されるものではなく、多層コア内にスルーホールを形成するため、且つ/或いは個々のガラス層又は接合層内にビアを形成するために、その他のプロセスが使用されてもよい。例えば、ガラスを軟化温度まで昇温させながらのインプリントプロセスによって、ガラス層内にビアが形成され得る。更なる例として、サンドブラスティングによって、ガラス層又は接合層内にビアが形成され得る。

[0062]

次に、図7を参照するに、1つ以上のスルーホールを有する多層ガラスコアを製造する方法の他の一実施形態が示されている。図7に示す方法の実施形態は更に図8A-8Jの模式図に示されており、以下の説明では、これらの図を参照する。

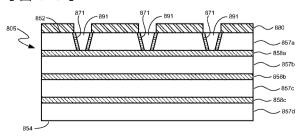

[0063]

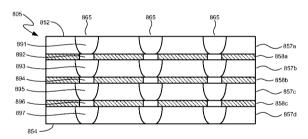

図7のブロック710を参照するに、多層ガラス板が準備される。これは図8Aに示されている。図8Aは、第1表面852とその反対側の第2表面854とを有する多層ガラス板805を示している。板805は、接合層858a、858b及び858cによってともに結合された別個のガラス層857a、857b、857c及び857dを含んでいる。多層ガラス板805は多層ガラス板605(図6A、15及び16、並びにそれらに関連する説明を参照)と同様とし得る。

[0064]

ブロック720にて説明されるように、マスク層が多層ガラス板上に配置されてパターニングされる。これは図8Aにも示されており、そこでは、マスク層880が板805の第1表面852上に配置されている。また、マスク層880は、開口885を形成するようにパターニングされている。マスク層880は、層857aに接着することが可能で、且つパターン形成のために改変可能な如何なる材料を有していてもよい。例として、マスク層880は、フォトリソグラフィ・エッチング技術によってパターニングされることができるフォトレジスト材料を有し得る。さらに、マスク層880は、後続のガラス層及び接合層の一部の除去(例えば、ウェットエッチングプロセス)に耐えることが可能な材料を有する。

[0065]

ブロック 7 3 0 にて説明されるように、ガラス層のうちの 1 つ内に孔又はビアが形成される。これは図 8 B に示されており、そこでは、マスク層 8 8 0 の開口 8 8 5 に対応する位置において、ガラス層 8 5 7 a 内にビア 8 9 1 が形成されている。一実施形態によれば

、ビア891は、ガラス層857aを除去するエッチングケミストリを使用するウェットエッチングプロセスによって形成される。他の一実施形態において、ガラス内にビアを形成するためにドライエッチングプロセスが用いられてもよい。ガラス用の好適なエッチャントの例については上述されている。

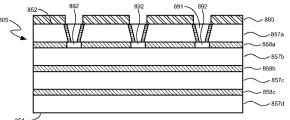

#### [0066]

プロック740にて説明されるように、先ほど孔が形成されたガラス層上に保護層が配置される。これは図8Cに示されており、そこでは、ガラス層857aに形成されたように、接合層及びその他のガラス層に更なるビアが形成されることになるが、保護層871が配設されている。板605にスルーホールを形成するよ71の機能は、それらその他のビアの形成中(例えば、接合層及びその他のガラス層に対うス層を対していて表で、は、上述の後続ビア形成プロセス中)にガラス層857aの材料が除去されることを防止あるえば、実質的に阻止することである。保護層871は、上述の後続ビア形成プロセスに耐えるにが可能な如何なる材料を有していてもよく、例えば、有機材料(例えば、白金若のはでか、ポリテトラフルオロエチレン、ポリイミドなど)、金属(例えば、白金若のは金)、金属酸化物、又は窒化シリコンを有し得る。また、保護層871は、孔891のは金)、金属酸化物、又は窒化シリコンを有し得る。また、保護層871は、孔891のは金)、金属酸化物、又は窒化シリコンを有し得る。また、保護層871は、一実施形態において、保護層871は、ガラスに対して選択性を有するためによって堆積される。他の一実施形態において、保護層を堆積するために非選択のなフェット堆積プロセスが使用され、その後、ビア底から保護材料を除去するために異方性プロセスが使用される。

#### [0067]

ブロック750にて説明されるように、接合層のうちの1つに孔又はビアが形成される。これは図8Dに示されており、そこでは、マスク層880の開口885に対応する位置において、接合層858a内にビア892が形成されている。孔892の各々は、上に位置するガラス層857a内の孔891に対して概してアライメントされる(例えば、孔891の中心線と孔892の中心線とがほぼ一致する)。一実施形態によれば、ビア892はウェットエッチングプロセスによって形成され、他の一実施形態において、ビア892はドライエッチングプロセスを用いて形成され得る。接合層材料用の好適なエッチャントの例については上述されている。

#### [0068]

図7に示すように、多層ガラス板を貫通する孔を形成するように、これらの工程群は必要なだけ繰り返される。故に、ブロック730を再び参照するに、次のガラス層に孔が形成される。これは図8mに示されており、そこでは、ガラス層857b内に孔893が形成されている。孔893は上述のようにして形成されることができ、孔893は、先に形成されたビア891及び892に概してアライメントされる(例えば、孔891、892、893それぞれの中心線がほぼ一致する)。ブロック740にて説明されるように、されが形成されたガラス層上に保護層が配置される。これは図8Fに示されており、そこでは、ガラス層857bに先ほど形成された孔893の壁に保護層873が配設されている。保護層873は、上述の保護層871と同様である。ブロック750を参照するに、次いで、次の接合層に孔又はビアが形成される。これは図8Gに示されており、そこでは、投合層858b内に孔894が形成されており、孔894は、先に形成されたビア891万至893に概してアライメントされている。

### [0069]

ブロック730、740及び750に関して説明した孔形成プロセスが、多層ガラス板805を貫いて延在する孔を形成するように、必要なだけ繰り返され得る。これは図8Hに示されており、そこでは、孔895がガラス層857c内に形成され、孔896が接合層858c内に形成され、そして孔897がガラス層857d内に形成されている。なお、ガラス層857c内の孔895の壁には、上述の保護層871と同様の保護層875が配設されている。孔891乃至897は全て、マスク層880の開口885に対応する位置に形成されており、これらの孔は互いに対して概してアライメントされている(例えば

10

20

30

40

20

30

40

50

、孔891乃至897のそれぞれの中心線がほぼ一致する)。

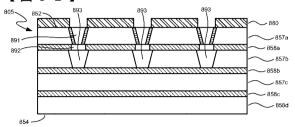

#### [0070]

孔形成が完了すると、ブロック760にて説明されるように、マスク層及び保護層が除去される。これは図8Iに示されており、そこでは、マスク層880と保護層871、873及び875とが除去されている。この段階で、多数の孔865が多層ガラス板805を貫いて、該板の第1表面852からその反対側の第2表面854まで延在する。各スルーホール865は、ガラス層857a-857d及び接合層858a-858cの内部に形成された一連の孔891、892、893、894、895、896及び897を有する。孔又はビアのアスペクト比は、該ビアの長さ(すなわち深さ)を該ビアの最大直径で割ったものとして定義されることができる。図7及び8A-8Iに記載のプロセスの1つの利点は、板805内に高いアスペクト比を有するスルーホールが得られることである。例えば、一実施形態において、多層ガラス板805内のスルーホール865は、およそ2か66の範囲内のアスペクト比を有し得る。

### [0071]

図8A-8Iの実施形態において、ビア891、893、895及び897の各々は、それらそれぞれのガラス層857a、857b、857c及び857dの厚さにわたって、概して直線状に先細る断面形状を有している。しかしながら、上述のように、ガラス層(又は接合層)に形成されるビアの形状は、製造技術(例えば、ウェットエッチング、ドライエッチング、レーザドリル加工など)及びプロセス特性に依存して様々となり得る。他の実施形態において、例えば、ガラス層857a-857dのうちの1つ(又は接合層858a-858cのうちの1つ)に形成されるビアは、湾曲形状を有していてもよい。例として、図8Jに示すように、ビア891、893、895及び897は扇形の断面形状を有していてもよい。開示の実施形態は何れもこのような扇形のビアを組み入れ得る。また、開示の実施形態はこのような扇形に限定されるものではなく、ビアが好適な如何なる形状又はプロファイルを有し得ることは理解されるべきである。

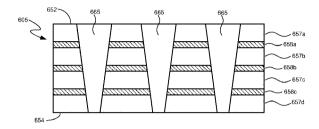

### [0072]

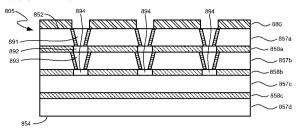

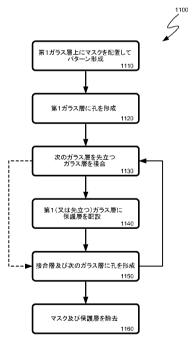

次に、図9を参照するに、1つ以上のスルーホールを有する多層ガラスコアを製造する方法の更なる一実施形態が示されている。図9に示す方法の実施形態は更に図10A-1 0Hの模式図に示されており、以下の説明では、これらの図を参照する。

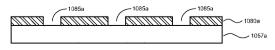

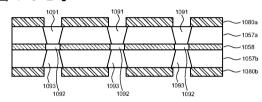

### [0073]

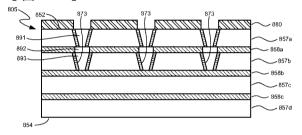

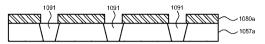

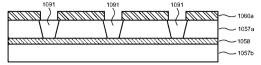

図 9 のブロック 9 1 0 を参照するに、マスク層が第1のガラス層上に配置されてパター ニングされる。これは図10Aに示されており、そこでは、マスク層1080aがガラス 層1057a上に配置されている。マスク層1080aは、開口1085aを形成するよ うにパターニングされている。プロック920にて説明されるように、第1のガラス層に 孔が形成される。これは図10Bに示されており、そこでは、マスク層1080aの開口 1 0 8 5 a に対応する位置において、ガラス層 1 0 5 7 a 内に孔 1 0 9 1 が形成されてい る。図9のブロック930にて説明されるように、二層構造を形成するように第2のガラ ス層が第1のガラス層に接合される。これは図100に示されており、そこでは、接合層 1 0 5 8 によって、ガラス層 1 0 5 7 a に第 2 のガラス層 1 0 5 7 b が結合されている。 ブロック940を参照するに、マスク層が第2のガラス板上に配置されてパターニングさ れる。これは図10Dに示されており、そこでは、マスク層1080bが、ガラス層10 57b上に配置され、且つ開口1085bを形成するようにパターニングされている。そ して、ブロック950にて説明されるように、第2のガラス層及び接合層に孔が形成され る。これは図10mに示されており、そこでは、ガラス層1057b内に孔1093が形 成され、接合層1058内に孔1092が形成されている。孔1091、1092、10 93は概してアライメントされている(例えば、これらの孔それぞれの中心線がほぼ一致 する)。プロック960にて説明されるように、マスク層が除去される。これは図10F に示されており、そこでは、マスク層1080a、1080bが除去されて、スルーホー ル1065を有する二層構造1008が残されている。各スルーホール1065はアライ メントされた一連の孔1091、1092、1093を有する。孔1091、1092、

1 0 9 3 は上述の技術のうちの何れかによって形成されることができ、また、ガラス層 1 0 5 7 a 、 1 0 5 7 b は上述の方法の何れかによってともに結合され得る。

### [0074]

図10Fの二層構造1008は、1つの基板の多層ガラスコアとして(例えば、コア150として、あるいはコア450として)使用され得る。他の例では、二層構造1008は、複数の基板を形成し得るパネルを有し得る。しかしながら、他のして1つの多に(ブロック970参照)、このような二層構造を2つ以上ともに接合して1つの多がのよっな一層構造1008aが第2の二層構造1008aが第2の二層構造1008 bと結合されている。各二層構造10008aが第2の二層構造1008 bを結合することが接合層1058×が第1及び第2の二層構造1008 bを結合することで1065は、接合層1058×内に形成された孔1094×を含んでいる。一とア1065は、接合層1058×内に形成された孔1094×はこれらの二層構造のて、接合層1058×内の孔1094×は二層構造1008 a、1008 bの接合に先のて予め形成され、他の一実施形態において、孔1094×はこれらの二層構造のでででである。

#### [0075]

代替的な一実施形態においては、ブロック980にて説明されるように、第1のガラス層上に保護層が配設される(第2のマスク層1080bは省略され得る)。これは図10日に示されており、そこでは、第1のガラス層1057aに形成されたビア1091の壁上に保護層1071が堆積される。その後、マスク層1080a及び該マスク層の開口1085aを用いて、接合層1058内の孔1092及びガラス層1057b内の孔1093が形成され得る。保護層1071は上述の保護層871と同様とし得る。孔1092、1093の形成後、マスク層1080aと同様に保護層1071が除去される(ブロック960参照)。図10日の二層構造が多層ガラスコアとして(例えば、コア150として、あるいはコア450として)使用されてもよいし、この二層構造が1つ以上の更なる二層構造と結合されてもよい(例えば、図10G参照)。

### [0076]

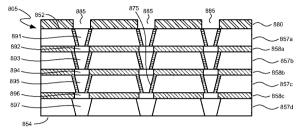

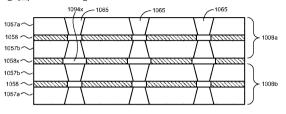

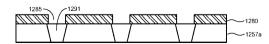

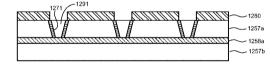

次に、図11を参照するに、1つ以上のスルーホールを有する多層ガラスコアを形成する方法の更なる他の一実施形態が示されている。図11に示す方法の実施形態は更に図1 2A-12Eの模式図に示されており、以下の説明では、これらの図を参照する。

# [0077]

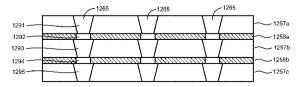

図11のブロック1110を参照するに、マスク層が第1のガラス層上に配置されてパ ターニングされる。これは図12Aに示されており、そこでは、マスク層1280がガラ ス層1257a上に配置されている。マスク層1280は、開口1285を形成するよう にパターニングされている。ブロック1120にて説明されるように、第1のガラス層に 孔が形成される。これも図12Aに示されており、そこでは、マスク層1280の開口1 2 8 5 に対応する位置において、ガラス層 1 2 5 7 a 内に孔 1 2 9 1 が形成されている。 図11のブロック1130にて説明されるように、別のガラス層が第1のガラス層(又は 先立つガラス層)に接合される。これは図12Bに示されており、そこでは、接合層10 5 8 a によって、ガラス層 1 2 5 7 a に第 2 のガラス層 1 2 5 7 b が結合されている。ブ ロック1240を参照するに、保護層が第1のガラス層(又は先立つガラス層)に配設さ れる。これも図12Bに示されており、そこでは、第1のガラス層1257aに形成され た孔1291の壁上に保護層1271が配設されている。保護層1271は上述の保護層 871と同様とし得る。その後、ブロック1150にて説明されるように、接合層及び次 のガラス層に孔が形成される。これは図12Cに示されており、そこでは、接合層125 8 a 内に孔 1 2 9 2 が形成され、第 2 のガラス層 1 2 5 7 b 内に孔 1 2 9 3 が形成されて いる。

# [ 0 0 7 8 ]

10

20

30

20

30

40

50

そして、ブロック1130、1140及び1150に関して説明したプロセスが、所望数のガラス層を有する多層ガラスコアを形成するように、必要なだけ繰り返され得る。例えば、図12Dに示すように、第2の接合層1258bによって第2のガラス層1257bに更なるガラス層1257cが接合され、接合層1258bに孔1294が形成され、ガラス層1257cに孔1295が形成される。なお、ガラス層1257cにおける孔1295の形成に先立って、第2のガラス層1257b内の孔1293の壁に保護層1273が配設される(ブロック1140参照)。

#### [0079]

ブロック1160にて説明されるように、所望数のガラス層が達成された後、マスク層及び保護層を除去することができる。これは図12Eに示されており、そこでは、マスク層1280及び保護層1271、1273が除去され、スルーホール1265を有する多層ガラスコア1205が残されている。各スルーホールは、概してアライメントされた一連の孔1291、1292、1293、1294及び1295を有する(例えば、これらの孔それぞれの中心線がほぼ一致する)。孔1291、1292、1293、1294、1295は上述の技術のうちの何れかによって形成されることができ、また、ガラス層1257a・1257cは上述の方法の何れかによってともに結合され得る。代替的な一実施形態において、多層ガラス構造1205は、複数の基板を形成し得るパネルを有する。他の一実施形態によれば、ガラス上の保護層は省略されてもよい(図11の左側の破線参照)。

### [0800]

なお、図面は、開示の実施形態を理解する助けとして提示した模式的なものであり、いたずらに何らかの限定を課すものではない。場合により、図示の明瞭さ及び容易さのために、比較的少ない数の要素のみを示している。例えば、図示した多層ガラスコア(又は多層ガラス板)を貫いて延在する導電体160、460(又は、孔665、865、1065、1265、1465)の個数は、そのような基板コアに実際に配設され得る導電体(又はスルービア)の個数より実質的に少ないものであり得る。また、図面は縮尺通りに描かれておらず、場合により、理解を容易にするために線(例えば、隠れた線)を省略している。

### [0081]

ガラス材料はおよそ3.2ppmのCTEを有し得る。ただし、CTE値は、温度に依存し、また、特定のガラス材料の組成に依存して異なることになる。シリコン基板及びはおび、これもやはり温度に依存する。パッケージ基板及び路基板の構築に典型的に使用される有機ポリマースの材料は、およそ12又はそれより高いCTE(値はやはり温度及び組成に依存する)を有し得る。このように物質のCTEは温度及び組成に依存する)を有し得る。ことで、ポリマーベースの基板を用いることで、ポリマーベースの基板を開いて、マッチが高に低減される。さらに、一般的に使用される有機ポリマーベースの材料がおよそ25GPaの係数E(Eの値も物質の組成に依存する)を有し得るのに対し、ガラスはおよそ75GPaの係数E(Eの値も物質の組成に依存する)を有し得るのに対し、ガラスはおよそである。ガラスの更なる利点は、一般的なポリマー材料より一貫した平坦性で製造され得る。ガラスの更なる利点は、一般的なポリマー材料より一貫した平坦性で製造され得る。である。

#### [0082]

上述のCTEミスマッチ及び反りの低減は、ダイ・パッケージ間のインターコネクトに、より小さいピッチを使用すること、及びより多数のそれらインターコネクトを使用することを可能にし、I/O能力の増大を提供し得る。例えば、一実施形態において、多層ガラスコア基板を用いると、ダイ・パッケージ間インターコネクトにおいて50μm又はそれ未満のピッチが達成され得る。大きい基板反りは、チップ取付けプロセスにおいてダイ・パッケージ間インターコネクトに非接触オープン不良を生じさせ得るとともに、ダイそれ自体の内部(例えば、ダイの層間誘電体層すなわちILD層の内部)に大きい応力を生

じさせ得る。これらはどちらも、より低い信頼性をもたらし得るものである。故に、開示の多層ガラスコア基板は、信頼性を維持あるいは向上させながら、より高密度 I/Oのパッケージの実装を可能にし得る。

#### [0083]

以上の詳細な説明及び添付の図面は単に例示であって、限定ではない。それらは、主として開示の実施形態の明瞭且つ包括的な理解のために提示されたものであり、それらから不要な限定が推測されるべきでない。ここに記載された実施形態への数多くの追加、削除及び変更、並びに代替構成が、開示の実施形態及び添付の請求項の範囲を逸脱することなく、当業者によって考え出され得る。

#### 【図1A】

### 【図1B】

### 【図1C】

#### 【図1D】

# 【図1E】

# 【図1F】

# 【図4A】

# 【図1G】

# 【図2】

# 【図4B】

# 【図4C】

# 【図5】

# 【図 6 B】

# 【図6C】

# 【図6A】

# 【図7】

# 【図8A】

# 【図8B】

# 【図8C】

# 【図 8 D 】 852 892 892 894

# 【図8E】

# 【図8F】

### 【図8」】

# 【図8G】

### 【図8H】

# 【図8I】

# 【図9】

# 【図10A】

# 【図10B】

# 【図10C】

# 【図10D】

# 【図10E】

# 【図10F】

#### 【図10G】

# 【図10H】

# 【図11】

# 【図12A】

### 【図12B】

# 【図12C】

# 【図12D】

### 【図12E】

# 【図13】

# 【図14A】

【図14B】

# 【図15】

# 【図16A】

# 【図16B】

# 【図16C】

# 【図16D】

# フロントページの続き

(51) Int.CI.

F I

H 0 1 L 21/90 A

(72)発明者 ホゥ,チュワン

アメリカ合衆国 85249 アリゾナ州 チャンドラー イースト グランド キャニオン ドライヴ 1965

(72)発明者 モロウ,パトリック

アメリカ合衆国 97229 オレゴン州 ポートランド ノースウエスト ランディング ドラ

イヴ 6158