# (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) Int. Cl.

GO2F 1/136 (2006.01) HO1L 29/786 (2006.01)

(21) 출원번호 10-2008-0127918

(22) 출원일자 **2008년12월16일** 심사청구일자 **2008년12월16일**

(65) 공개번호 **10-2010-0069270**

(43) 공개일자 2010년06월24일

(56) 선행기술조사문헌

KR1020050113422 A\*

KR1020040094951 A\* KR1020050051446 A\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2011년03월16일

(11) 등록번호 10-1021479

(24) 등록일자 2011년03월04일

(73) 특허권자

#### 성균관대학교산학협력단

경기 수원시 장안구 천천동 300 성균관대학교내

(72) 발명자

#### 최병덕

경기도 용인시 기흥구 보라동 558 신창아파트 202-704

## 이준신

서울 서초구 서초동 1687 서초 유원아파트 101동 401호

(뒷면에 계속)

(74) 대리인

특허법인정직과특허

전체 청구항 수 : 총 16 항

심사관: 임동재

## (54) 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치

### (57) 요 약

본 발명은 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치에 관한 것으로, 기판상에 차례로 배치된 버퍼막 및 반도체막, 상기 반도체막 상에 차례로 배치된 절연패턴 및 게이트 전극패턴을 포함하는 게이트 패턴, 상기 게이트 패턴 하부의 반도체막을 채널영역으로 한정하고, 상기 게이트 패턴 외측의 상기 반도체막에 불순물이 주입되어 상기 채널영역의 양쪽 측면들과 연결된 소오스 및 드레인, 상기 게이트 패턴을 갖는 상기 기판 전면을 덮는 보호막, 상기 소오스 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 소오스를 관통하여 상기 소오스와 전기적으로 연결된 제1금속전극 및 상기 드레인 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 드레인을 관통하여 상기 드레인과 전기적으로 연결된 제2금속전극을 포함한다.

상기와 같은 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치에 의해, 소오스와 드레인 영역에 금속을 침투시켜 박막 트랜지스터의 구동 시에 전류를 분산시킴으로써 전하의 이동도, 박막 트랜지스터의 수명 및 성능을 향상시킬 수 있다.

## 대 표 도 - 도2h

(72) 발명자

## 조재현

## 정성욱

경기도 수원시 권선구 금곡동 강남아파트101-1404

장경수

서울 서대문구 북가좌2동 288-3번지 202호

경상북도 경산시 하양읍 금락1리 130-26

## 특허청구의 범위

#### 청구항 1

기판 상에 차례로 버퍼막, 예비 채널영역, 절연막 및 게이트 전극막을 형성하는 단계;

상기 예비 채널영역의 일 영역을 노출시키도록 상기 게이트 전극막 및 상기 절연막을 차례로 패터닝하여 게이트 패턴을 형성하는 단계;

상기 게이트 패턴을 마스크로 상기 노출된 예비 채널영역을 불순물로 도우핑하여 채널영역을 한정하고, 소오스 및 드레인 영역을 형성하는 단계;

상기 소오스 및 상기 드레인 영역을 갖는 상기 기판의 전면에 보호막을 형성하는 단계;

상기 소오스 및 상기 드레인 영역 상에 형성된 상기 보호막의 일영역 하부를 식각하여 상기 버퍼막을 노출시키는 제1콘택홀 및 제2콘택홀을 형성하는 단계; 및

상기 기판의 전면에 상기 제1콘택홀 및 상기 제2콘택홀을 채우는 금속전극막을 형성하는 단계를 포함하되,

상기 제1콘택홀 및 상기 제2콘택홀을 형성하는 단계는

상기 소오스 및 상기 드레인 영역 상에 형성된 상기 보호막의 일 영역을 노출시키도록 상기 보호막 상에 포토레 지스트 패턴을 형성하는 단계;

상기 포토레지스트 패턴을 갖는 상기 기판에 식각공정을 수행함으로써 상기 노출된 보호막을 식각하여 상기 소오스 및 상기 드레인의 일영역을 노출시키는 단계;

상기 노출된 소오스 및 상기 노출된 드레인 영역을 식각하여 상기 버퍼막의 일영역을 노출시키는 단계; 및

상기 포토레지스트 패턴을 제거하는 단계를 포함하는 것을 특징으로 하는 박막 트랜지스터의 형성방법.

### 청구항 2

삭제

## 청구항 3

제 1 항에 있어서,

상기 금속전극막을 형성한 후에

상기 제1콘택홀과 상기 제2콘택홀 사이에 형성된 상기 보호막 상의 상기 금속전극막을 식각하여 상기 보호막을 노출시키는 단계를 더 포함하는 것을 특징으로 하는 박막 트랜지스터의 형성방법.

## 청구항 4

기판 상에 차례로 버퍼막, 예비 채널영역, 절연막 및 게이트 전극막을 형성하는 단계;

상기 예비 채널영역의 일 영역을 노출시키도록 상기 게이트 전극막 및 상기 절연막을 차례로 패터닝하여 게이트 패턴을 형성하는 단계;

상기 게이트 패턴을 마스크로 상기 노출된 예비 채널영역을 불순물로 도우핑하여 채널영역을 한정하고, 소오스 및 드레인 영역을 형성하는 단계;

상기 소오스 및 상기 드레인 영역을 갖는 상기 기판의 전면에 보호막을 형성하는 단계;

상기 소오스, 상기 드레인 영역 및 상기 게이트 패턴 상에 형성된 상기 보호막의 일영역 하부를 식각하여 상기 버퍼막을 노출시키는 제1콘택홀, 제2콘택홀 및 제3콘택홀을 형성하는 단계; 및

상기 기판의 전면에 상기 제1콘택홀, 상기 제2콘택홀 및 상기 제3콘택홀을 채우는 금속전극막을 형성하는 단계를 포함하되,

상기 제1콘택홀, 상기 제2콘택홀 및 상기 제3콘택홀을 형성하는 단계는

상기 소오스 영역, 상기 드레인 영역 및 상기 게이트 패턴 상에 형성된 상기 보호막의 일 영역을 노출시키도록

상기 보호막 상에 제1포토레지스트 패턴을 형성하는 단계;

상기 제1포토레지스트 패턴을 갖는 상기 기판에 식각공정을 수행함으로써 상기 노출된 보호막을 식각하여 상기 소오스, 상기 드레인 및 상기 게이트 패턴의 일영역을 노출시켜 제1예비 콘택홀, 제2예비 콘택홀 및 제3콘택홀 을 형성하는 단계;

상기 제1포토레지스트 패턴을 제거하는 단계;

상기 제1예비 콘택홀, 상기 제2예비 콘택홀 및 상기 제3콘택홀을 갖는 상기 기판 상에 상기 제1예비 콘택홀 및 상기 제2예비 콘택홀을 노출시키는 제2포토레지스트 패턴을 형성하는 단계;

상기 제2포토레지스트 패턴을 갖는 상기 기판에 식각공정을 수행함으로써 상기 노출된 소오스 및 상기 노출된 드레인 영역을 관통하여 상기 버퍼막을 노출시켜 제1콘택홀 및 제2콘택홀을 형성하는 단계; 및

상기 제2포토레지스트 패턴을 제거하는 단계를 포함하는 것을 특징으로 하는 박막 트랜지스터의 형성방법.

## 청구항 5

삭제

## 청구항 6

제 4 항에 있어서,

상기 금속전극막을 형성한 후에

상기 제1콘택홀과 상기 제3콘택홀 사이에 형성된 상기 보호막 상의 상기 금속전극막 및 상기 제3콘택홀과 상기 제2콘택홀 사이에 형성된 상기 보호막 상의 상기 금속전극막을 식각하여 상기 보호막을 노출시키는 단계를 더 포함하는 것을 특징으로 하는 박막 트랜지스터의 형성방법.

#### 청구항 7

제 1 항 또는 제 4 항에 있어서,

상기 소오스 및 상기 드레인 영역 각각의 두께는 10nm 내지 50nm인 것을 특징으로 하는 박막 트랜지스터의 형성 방법.

#### 청구항 8

제 1 항 또는 제 4 항에 있어서,

상기 채널영역은 비정질 실리콘, 나노결정 실리콘, 마이크로결정 실리콘, 3-5족 반도체, 2-6족 반도체 및 다결 정 실리콘으로 형성되는 것을 특징으로 하는 박막 트랜지스터의 형성방법.

#### 청구항 9

제 1 항 또는 제 4 항에 있어서,

상기 금속전극막은 알루미늄 또는 알루미늄 합금을 포함하는 물질로 형성되는 것을 특징으로 하는 박막 트랜지 스터의 형성방법.

### 청구항 10

기판 상에 차례로 배치된 버퍼막 및 반도체막;

상기 반도체막 상에 차례로 배치된 절연패턴 및 게이트 전극패턴을 포함하는 게이트 패턴;

상기 게이트 패턴 하부의 반도체막을 채널영역으로 한정하고, 상기 게이트 패턴 외측의 상기 반도체막에 불순물이 주입되어 상기 채널영역의 양쪽 측면들과 연결된 소오스 및 드레인;

상기 게이트 패턴을 갖는 상기 기판 전면을 덮는 보호막;

상기 소오스 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 소오스를 관통하여 상기 소오 스와 전기적으로 연결된 제1금속전극; 및 상기 드레인 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 드레인을 관통하여 상기 드레인 영역과 전기적으로 연결된 제2금속전극을 포함하는 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 11

제 10 항에 있어서,

상기 게이트 전극패턴 상의 상기 보호막의 일영역을 관통하여 상기 게이트 전극과 연결된 제3금속전극을 더 포함하는 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 12

제 10 항에 있어서,

상기 제1금속전극 및 상기 제2금속전극의 각각은 알루미늄 전극 또는 알루미늄 합금 전극을 포함하는 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 13

제 10 항에 있어서,

상기 채널영역은 비정질 실리콘, 나노결정 실리콘, 마이크로결정 실리콘, 3-5족 반도체, 2-6쪽 반도체 및 다결 정 실리콘으로 형성된 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 14

제 10 항에 있어서,

상기 소오스 및 상기 드레인 영역 각각의 두께는 10nm 내지 50nm인 것을 특징으로 하는 박막 트랜지스터.

#### 청구항 15

기판 상에 차례로 배치된 버퍼막 및 반도체막;

상기 반도체막 상에 차례로 배치된 절연패턴 및 게이트 전극패턴을 포함하는 게이트 패턴;

상기 게이트 패턴 하부의 반도체막을 채널영역으로 한정하고, 상기 게이트 패턴 외측의 상기 반도체막에 불순물이 주입되어 상기 채널영역의 양쪽 측면들과 연결된 소오스 및 드레인;

상기 게이트 패턴을 갖는 상기 기판 전면을 덮는 보호막;

상기 소오스 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 소오스를 관통하여 상기 소오 스와 전기적으로 연결된 제1금속전극;

상기 드레인 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 드레인을 관통하여 상기 드레인 영역과 전기적으로 연결된 제2금속전극;

상기 제2금속전극을 갖는 상기 기판을 덮은 보호절연막; 및

상기 보호절연막을 갖는 상기 기판 상에 배치되어 상기 드레인 영역과 전기적으로 연결된 유기발광 다이오드를 포함하는 것을 특징으로 하는 평판 표시장치.

## 청구항 16

제 15 항에 있어서,

상기 게이트 전극 상의 상기 보호막의 일영역을 관통하여 상기 게이트 전극패턴과 연결된 제3금속전극을 더 포함하는 것을 특징으로 하는 평판 표시장치.

## 청구항 17

제 15 항에 있어서,

상기 제1금속전극, 상기 제2금속전극 및 상기 제3금속전극의 각각은 알루미늄 전극 또는 알루미늄 합금 전극을

포함하는 것을 특징으로 하는 평판 표시장치.

#### 청구항 18

제 15 항에 있어서,

상기 소오스 및 상기 드레인 영역 각각의 두께는 10nm 내지 50nm인 것을 특징으로 하는 평판 표시장치.

## 명 세 서

## 발명의 상세한 설명

## 기 술 분 야

[0001] 본 발명은 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치에 관한 것으로, 특히 소오스와 드레인 영역에 금속을 침투시켜 박막 트랜지스터의 구동 시에 전류를 분산시킴으로써 전하의 이동도를 향상시키고, 과도한 전류밀도에 의한 드레인 영역의 손실을 방지함으로써 박막 트랜지스터의 수명과 성능을 향상시킬 수 있는 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치에 관한 것이다.

### 배경기술

- [0002] 일반적으로, 전계효과 트랜지스터(Field Effect Transistor; FET)의 한 종류인 박막 트랜지스터(Thin Film Transistor)는 SRAM이나 ROM에도 응용되지만, 주로 능동 행렬형 평판 디스플레이(Active Matrix Flat Panel Display)의 화소(pixel) 스위칭 소자로 사용된다. 예를 들어, 상기 박막 트랜지스터는 액정 디스플레이(Liquid Crystal Display)나 유기 전계 발광 디스플레이(Organic Electro-luminescence Display) 화소의 스위칭 소자 또는 전류 구동 소자로 사용되고 있다. 이러한 스위칭 소자로 사용되는 박막 트랜지스터는 주위 화소들의 전기적 영향으로부터 각각의 화소를 독립시켜 주고 화소에 전기적 신호를 전달해 주는 역할을 수행한다.

- [0003] 상기 박막 트랜지스터에 사용되는 반도체는 주로 비정질 실리콘(amorphous Si)과 다결정 실리콘(poly-Si)이다. 박막 트랜지스터의 전류 구동능력 또는 전하 캐리어의 이동도(mobility)를 고려하면 박막 트랜지스터에 사용되는 반도체로서 폴리 실리콘이 적합할 것이다. 그러나, 공정온도 및 사용 가능한 기판을 고려하면, 박막 트랜지스터에 사용되는 반도체로는 비정질 실리콘이 적합하여 현재까지의 박막 트랜지스터는 대부분 비정질 실리콘이 사용되고 있다.

- [0004] 그러나, 비정질 실리콘을 사용하는 박막 트랜지스터에서 전하 이동도는 0.5㎡/Vs 내외로 낮다. 따라서, 비정질 실리콘으로 형성된 채널을 갖는 박막 트랜지스터를 스위칭 소자로 사용하는 액정표시장치는 동작 속도를 증가시 키기 어렵다. 그 결과, 비정질 실리콘보다 전하 이동도가 높은 물질을 박막 트랜지스터의 채널로 사용하거나, 박막 트랜지스터의 구조를 변경하여 전하 이동도를 높일 수 있는 연구가 진행되고 있다.

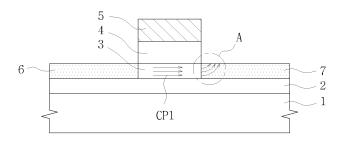

- [0005] 도 1은 종래기술에 따른 박막 트랜지스터에서 발행하는 문제점을 설명하기 위한 개략적인 단면도이다.

- [0006] 도 1에서 도시한 바와 같이, 종래의 박막 트랜지스터는 기판(1) 상에 배치된 완충막(2)을 포함하여 구성된다. 상기 완충막(2) 상에 반도체 패턴(3)이 배치되고, 상기 반도체 패턴(3) 상에 차례로 절연막(4) 및 게이트 전극 (5)이 배치된다. 상기 게이트 전극(5) 하부의 반도체 패턴(3)은 채널영역으로서의 역할을 수행한다. 상기 반도 체 패턴과 나란하게 소오스 영역(6) 및 드레인 영역(7)이 배치된다.

- [0007] 이 경우, 상기 박막 트랜지스터를 액정표시장치의 구동소자로 사용하는 경우, 박막 트랜지스터는 채널영역(3)에서 드레인 영역(7)의 방향으로 넓은 폭을 갖는 전하이동 경로(CP1)를 갖는다. 그러나, 전하가 드레인 영역(7)으로 이동하면서 국소 영역(A)으로 쏠리게 되고, 이에 따라 전하의 산란되는 정도가 국소 영역(A)에서 증가하게된다. 따라서, 전하의 이동도가 줄어든다는 문제점이 발생한다. 또한, 상기 드레인 영역(7)에서 전하의 이동 경로가 수직에 가까워져 국소 영역(A)에 계속적인 스트레스가 가해짐으로 시간이 지남에 따라 박막 트랜지스터의구동 특성이 열화된다는 문제점이 발생한다. 결과적으로, 상기 박막 트랜지스터의 동작특성이 열화되고 수명이줄어들 수 있다.

### 발명의 내용

### 해결 하고자하는 과제

- [0008] 본 발명의 목적은 상술한 바와 같은 문제점을 해결하기 위해 이루어진 것으로서, 소오스와 드레인 영역에 금속을 침투시켜 박막 트랜지스터의 구동 시에 드레인 영역에서 전류를 분산시킴으로써 전하의 이동도를 향상시킬 수 있는 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치를 제공하는 것이다.

- [0009] 또한, 본 발명의 목적은 박막 트랜지스터가 동작하는 동안 과도한 전류밀도에 의한 드레인 영역의 손실을 방지함으로써 박막 트랜지스터의 수명과 성능을 향상시킬 수 있는 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치를 제공하는 것이다.

## 과제 해결수단

- [0010] 상기 목적을 달성하기 위해 본 발명의 일 실시예에 따른 박막 트랜지스터의 형성방법은 기판 상에 차례로 버퍼막, 예비 채널영역, 절연막 및 게이트 전극막을 형성하는 단계, 상기 예비 채널영역의 일부를 노출시키도록 상기 게이트 전극막 및 상기 절연막을 차례로 패터닝하여 게이트 패턴을 형성하는 단계, 상기 게이트 패턴을 마스크로 상기 노출된 예비 채널영역을 불순물로 도우핑하여 채널영역을 한정하고, 소오스 및 드레인 영역을 형성하는 단계, 상기 소오스 및 상기 드레인 영역을 갖는 상기 기판의 전면에 보호막을 형성하는 단계, 상기 소오스및 상기 드레인 영역 상에 형성된 상기 보호막의 일영역 하부를 식각하여 상기 버퍼막을 노출시키는 제1콘택홀및 제2콘택홀을 형성하는 단계 및 상기 기판의 전면에 상기 제1콘택홀 및 상기 제2콘택홀을 채우는 금속전극막을 형성하는 단계를 포함하는 것을 특징으로 한다.

- [0011] 또한, 본 발명의 일 실시예에 따른 박막 트랜지스터의 형성방법에서 상기 제1콘택홀 및 상기 제2콘택홀을 형성하는 단계는 상기 소오스 및 상기 드레인 영역 상에 형성된 상기 보호막의 일부를 노출시키도록 상기 보호막 상에 포토레지스트 패턴을 형성하는 단계, 상기 포토레지스트 패턴을 갖는 상기 기판에 식각공정을 수행함으로써 상기 노출된 보호막을 식각하여 상기 소오스 및 상기 드레인의 일영역을 노출시키는 단계, 상기 노출된 소오스 및 상기 노출된 드레인 영역을 식각하여 상기 버퍼막의 일영역을 노출시키는 단계 및 상기 포토레지스트 패턴을 제거하는 단계를 포함하는 것을 특징으로 한다.

- [0012] 또한, 본 발명의 일 실시예에 따른 박막 트랜지스터의 형성방법은 상기 금속전극막을 형성한 후에 상기 제1콘택홀과 상기 제2콘택홀 사이에 형성된 상기 보호막 상의 상기 금속전극막을 식각하여 상기 보호막을 노출시키는 단계를 더 포함하는 것을 특징으로 한다.

- [0013] 상기 목적을 달성하기 위해 본 발명의 다른 실시예에 따른 박막 트랜지스터의 형성방법에서 기판 상에 차례로 버퍼막, 예비 채널영역, 절연막 및 게이트 전극막을 형성하는 단계, 상기 예비 채널영역의 일부를 노출시키도록 상기 게이트 전극막 및 상기 절연막을 차례로 패터닝하여 게이트 패턴을 형성하는 단계, 상기 게이트 패턴을 마스크로 상기 노출된 예비 채널영역을 불순물로 도우핑하여 채널영역을 한정하고, 소오스 및 드레인 영역을 형성하는 단계, 상기 소오스, 상기 드레인 영역 및 상기 게이트 패턴을 갖는 상기 기판의 전면에 보호막을 형성하는 단계, 상기 소오스 및 상기 드레인 영역 상에 형성된 상기 보호막의 일영역 하부를 식각하여 상기 버퍼막을 노출시키는 제1콘택홀, 제2콘택홀 및 제3콘택홀을 형성하는 단계 및 상기 기판의 전면에 상기 제1콘택홀, 상기 제 2콘택홀 및 상기 제3콘택홀을 채우는 금속전극막을 형성하는 단계를 포함하는 것을 특징으로 한다.

- [0014] 또한, 본 발명의 다른 실시예에 따른 박막 트랜지스터의 형성방법에서 상기 제1콘택홀, 상기 제2콘택홀 및 상기 제3콘택홀을 형성하는 단계는 상기 소오스 영역, 상기 드레인 영역 및 상기 게이트 패턴 상에 형성된 상기 보호 막의 일부를 노출시키도록 상기 보호막 상에 제1포토레지스트 패턴을 형성하는 단계, 상기 제1포토레지스트 패턴을 갖는 상기 기판에 식각공정을 수행함으로써 상기 노출된 보호막을 식각하여 상기 소오스, 상기 드레인 및 상기 게이트 패턴의 일영역을 노출시켜 제1예비 콘택홀, 제2예비 콘택홀 및 제3콘택홀을 형성하는 단계, 상기 제1포토레지스트 패턴을 제거하는 단계, 상기 제1예비 콘택홀, 상기 제2예비 콘택홀 및 상기 제3콘택홀을 갖는 상기 기판 상에 상기 제1예비 콘택홀 및 상기 제2예비 콘택홀을 노출시키는 제2포토레지스트 패턴을 형성하는 단계, 상기 제2포토레지스트 패턴을 찾는 상기 기판에 심각공정을 수행함으로써 상기 노출된 소오스 및 상기 노출된 드레인 영역을 관통하여 상기 버퍼막을 노출시켜 제1콘택홀 및 제2콘택홀을 형성하는 단계 및 상기 제2포토레지스트 패턴을 제거하는 단계를 포함하는 것을 특징으로 한다.

- [0015] 또한, 본 발명의 다른 실시예에 따른 박막 트랜지스터의 형성방법은 상기 금속전극막을 형성한 후에 상기 제1콘 택홀과 상기 제3콘택홀 사이에 형성된 상기 보호막 상의 상기 금속전극막 및 상기 제3콘택홀과 상기 제2콘택홀 사이에 형성된 상기 보호막 상의 상기 금속전극막을 식각하여 상기 보호막을 노출시키는 단계를 더 포함하는 것

을 특징으로 한다.

- [0016] 또한, 본 발명의 실시예에 따른 박막 트랜지스터의 형성방법에서 상기 소오스 및 상기 드레인 영역 각각의 두께는 10nm 내지 50nm인 것을 특징으로 한다.

- [0017] 또한, 본 발명의 실시예에 따른 박막 트랜지스터의 형성방법에서 상기 채널영역은 비정질 실리콘, 나노결정 실리콘, 마이크로결정 실리콘, 3-5족 반도체, 2-6족 반도체 및 다결정 실리콘으로 형성되는 것을 특징으로 한다.

- [0018] 또한, 본 발명의 실시예에 따른 박막 트랜지스터의 형성방법에서 상기 금속전극막은 알루미늄 또는 알루미늄 합금을 포함하는 물질로 형성되는 것을 특징으로 한다.

- [0019] 상기 목적을 달성하기 위해 본 발명의 실시예에 따른 박막 트랜지스터는 기판 상에 차례로 배치된 버퍼막 및 반도체막, 상기 반도체막 상에 차례로 배치된 절연패턴 및 게이트 전극패턴을 포함하는 게이트 패턴, 상기 게이트 패턴 하부의 반도체막을 채널영역으로 한정하고, 상기 게이트 패턴 외측의 상기 반도체막에 불순물이 주입되어 상기 채널영역의 양쪽 측면들과 연결된 소오스 및 드레인, 상기 게이트 패턴을 갖는 상기 기판 전면을 덮는 보호막, 상기 소오스 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 소오스를 관통하여 상기 소오스와 전기적으로 연결된 제1금속전극 및 상기 드레인 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 드레인을 관통하여 상기 드레인 영역과 전기적으로 연결된 제2금속전극을 포함하는 것을 특징으로 한다.

- [0020] 또한, 본 발명의 실시예에 따른 박막 트랜지스터는 상기 게이트 전극패턴 상의 상기 보호막의 일영역을 관통하여 상기 게이트 전극과 연결된 제3금속전극을 더 포함하는 것을 특징으로 한다.

- [0021] 또한, 본 발명의 실시예에 따른 박막 트랜지스터에서 상기 제1금속전극 및 상기 제2금속전극의 각각은 알루미늄 전극 또는 알루미늄 합금 전극을 포함하는 것을 특징으로 한다.

- [0022] 또한, 본 발명의 실시예에 따른 박막 트랜지스터에서 상기 채널영역은 비정질 실리콘, 나노결정 실리콘, 마이크 로결정 실리콘, 3-5족 반도체, 2-6족 반도체 및 다결정 실리콘으로 형성된 것을 특징으로 한다.

- [0023] 또한, 본 발명의 실시예에 따른 박막 트랜지스터에서 상기 소오스 및 상기 드레인 영역 각각의 두께는 10nm 내지 50nm인 것을 특징으로 한다.

- [0024] 상기 목적을 달성하기 위해 본 발명의 실시예에 따른 박막 트랜지스터를 구비하는 평판 표시장치는 기판 상에 차례로 배치된 버퍼막 및 반도체막, 상기 반도체막 상에 차례로 배치된 절연패턴 및 게이트 전극패턴을 포함하는 게이트 패턴, 상기 게이트 패턴 하부의 반도체막을 채널영역으로 한정하고, 상기 게이트 패턴 외측의 상기 반도체막에 불순물이 주입되어 상기 채널영역의 양쪽 측면들과 연결된 소오스 및 드레인, 상기 게이트 패턴을 갖는 상기 기판 전면을 덮는 보호막, 상기 소오스 영역 상에 배치된 상기 보호막의 일영역 및 상기 일영역 하부의 상기 소오스를 관통하여 상기 소오스와 전기적으로 연결된 제1금속전극, 상기 드레인 영역 상에 배치된 상기보호막의 일영역 및 상기 일영역 하부의 상기 드레인을 관통하여 상기 드레인 영역과 전기적으로 연결된 제2금 속전극, 상기 제2금속전극을 갖는 상기 기판을 덮은 보호절연막 및 상기 보호절연막을 갖는 상기 기판 상에 배치되어 상기 드레인 영역과 전기적으로 연결된 유기발광 다이오드를 포함하는 것을 특징으로 한다.

## 直 과

- [0025] 상술한 바와 같이, 본 발명에 따른 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시 장치에 의하면, 소오스와 드레인 영역에 금속을 침투시켜 박막 트랜지스터의 구동 시에 전류를 분산시킴으로써 전하의 이동도를 향상시킬 수 있다는 효과가 얻어진다.

- [0026] 또, 본 발명에 따른 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치에 의하면, 박막 트랜지스터가 동작하는 동안 과도한 전류밀도에 의한 드레인 영역의 손실을 방지함으로써 박막 트랜지스 터의 수명과 성능을 향상시킬 수 있다는 효과가 얻어진다.

## 발명의 실시를 위한 구체적인 내용

[0027] 본 발명의 상기 및 그 밖의 목적과 새로운 특징은 본 명세서의 기술 및 첨부 도면에 의해 더욱 명확하게 될 것

이다.

- [0028] 이하, 도 2a 내지 2h를 참조하여 본 발명에 따른 박막 트랜지스터의 형성방법을 상세하게 설명하기로 한다. 도 2a 내지 2h는 본 발명의 실시 예에 따른 박막 트랜지스터의 형성방법을 도시한 단면도들이다.

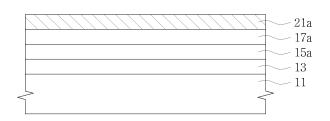

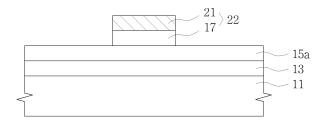

- [0029] 도 2a에서 도시한 바와 같이, 본 발명에 따른 박막 트랜지스터는 유리기판(11) 상에 형성된 버퍼막(13)을 포함한다. 상기 버퍼막(13)은 실리콘 질화막(SiNx) 또는 실리콘 산화막(SiOx)의 단일막이거나, 복수의 층으로 된 막으로 형성될 수 있다. 본 발명의 실시예에서 상기 버퍼막(13)은 열팽창 또는 다른 박막과의 계면 상태 등을 고려하여 유리기판(11) 상에 실리콘 질화막 및 실리콘 산화막이 차례로 적층된 이중막인 것이 바람직하다. 이 경우, 상기 실리콘 질화막의 두께는 200nm이고, 상기 실리콘 산화막의 두께는 100nm로 형성될 수 있다.

- [0030] 상기 버퍼막(13) 상에 전자 또는 정공이 이동하는 경로를 형성하기 위한 예비 채널영역(15a)이 형성된다. 상기 예비 채널영역(15a)은 비정질 실리콘 박막, 나노결정 실리콘 박막, 마이크로결정 실리콘 박막, 다결정 실리콘 박막, 3-5족 반도체 박막, 2-6족 반도체 박막 및 산화물 반도체 박막 중에서 선택된 어느 하나로 형성될 수 있다. 상기 예비 채널영역(15a)이 비정질 실리콘 박막으로 형성된 경우에, 상기 예비 채널영역(15a)은 엑시머 레이저(Eximer Laser crystallization) 결정화, 고상 결정화(solid phase crystallization) 또는 금속 유도 결정화(Metal induced crystallization) 등과 같은 방법으로 결정화(crystallization)될 수 있다.

- [0031] 상기 예비 채널영역(15a) 상에 절연막(17a) 및 게이트 전극막(21a)이 차례로 형성된다. 상기 절연막(17a)은 실리콘 산화막 또는 실리콘 질화막으로 된 단일막으로 형성되거나, 복 수의 막으로 형성될 수 도 있다. 상기 게이트 전극막(21a)은 금속물질 또는 반도체 물질로 형성될 수 있다. 예를 들어, 상기 게이트 전극막(21a)은 알루미늄(A1), 크롬(Cr), 은(Ag) 및 금(Au) 중에서 선택된 물질로 형성되거나, 레이저를 조사하는 방법으로 비정질 실리콘을 결정화시켜 형성될 수 있다.

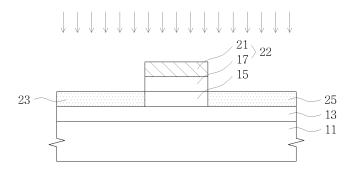

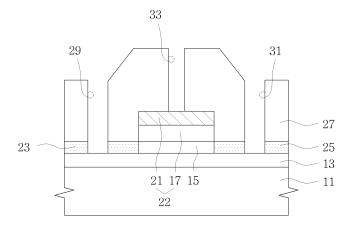

- [0032] 도 2b 내지 도 2d에서 도시한 바와 같이, 상기 예비 채널영역(15a)의 상면을 노출시키도록 게이트 전극막(21a) 및 절연막(17a)을 차례로 패터닝하여 게이트 전극패턴(21) 및 절연패턴(17)을 형성한다. 따라서, 상기 게이트 전극패턴(21) 및 절연패턴(17)은 게이트 패턴(22)을 형성한다. 이 경우, 상기 절연패턴(17)은 실리콘 산화막 또는 실리콘 절화막으로 된 단일막으로 형성되거나, 복 수의 막으로 형성될 수 도 있다.

- [0033] 상기 게이트 패턴(22)을 마스크로 상기 예비 채널영역(15a)을 갖는 기판(11) 상에 불순물 이온들을 도우핑하는 이온 주입공정을 수행한다. 따라서, 상기 게이트 패턴(22)에 이격하는 예비 채널영역(15a)은 소오스(23) 및 드레인(25) 영역으로 형성된다. 또한, 상기 게이트 패턴(22) 하부의 예비 채널영역(15a)은 채널영역(15)으로 한정된다. 상기 소오스(23) 및 드레인(25) 영역 각각의 두께는 10nm 내지 50nm로 형성되는 것이 바람직하다. 상기소오스(23) 및 드레인(25) 영역을 갖는 기판(11)의 전면에 보호막(27)을 형성한다. 상기 보호막(27)은 실리콘질화막 또는 실리콘 산화막으로 형성될 수 있다.

- [0034] 도 2e 및 도 2f에서 도시한 바와 같이, 상기 소오스(23) 및 드레인(25) 영역 상의 보호막(27) 일부를 노출시키도록 상기 보호막(27) 상에 제1포토레지스트 패턴(도시하지 않음)을 형성한다. 상기 제1포토레지스트 패턴을 갖는 기판(11)에 비등방성 식각공정을 수행함으로써 보호막(27)을 관통하여 소오스(23)의 일영역을 노출시키는 제1예비 콘택홀(29a) 및 드레인(25)의 일영역을 노출시키는 제2예비 콘택홀(31a)을 형성한다. 이 경우, 상기 게이트 패턴(22) 상에 형성된 보호막(27)의 일영역을 관통하여 게이트 전극패턴(21)의 일영역을 노출시키는 제3콘택홀(33)을 형성할 수 있다.

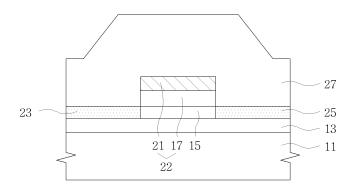

- [0035] 다음으로, 상기 제1포토레지스트 패턴을 제거하고, 상기 제2콘택홀(31)을 갖는 기판(11)의 전면에 제1예비 콘택홀(29a) 및 제2예비 콘택홀(31a)을 노출시키는 제2포토레지스트 패턴(도시하지 않음)을 형성한다. 상기 제2포토레지스트 패턴을 갖는 기판(11) 상에 비등방성 식각공정을 수행함으로써 제1예비 콘택홀(29a) 하부의 소오스(23) 영역을 관통하여 버퍼막(13)을 노출시키는 제1콘택홀(29)을 형성할 수 있다. 또한, 상기 제1콘택홀을 형성하면서, 상기 제2예비 콘택홀(31a) 하부의 드레인(25) 영역을 관통하여 버퍼막(13)을 노출시키는 제2콘택홀(31a) 1)을 형성한 후에 상기 제2포토레지스트 패턴을 제거한다.

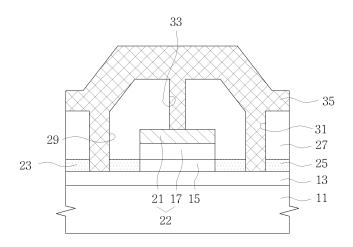

- [0036] 도 2g 및 도 2h에서 도시한 바와 같이, 상기 제1, 제2 및 제3콘택홀(29, 31, 33)을 갖는 기판(11)의 전면에 제 1, 제2 및 제3콘택홀(29, 31, 33)을 채우도록 금속전극막(35)을 형성한다. 상기 금속전극막(35)은 알루미늄 또는 알루미늄 합금을 포함하는 물질로 형성될 수 있다. 상기 금속전극막(35)을 형성한 후에, 상기 제1콘택홀(29)과 제3콘택홀(33) 사이에 형성된 보호막(27) 상의 금속전극막(35)을 식각하여 소오스(23) 영역과 전기적으로 연결된 제1금속전극(37)을 형성한다. 또한, 상기 제3콘택홀(33)과 제2콘택홀(31) 사이에 형성된 보호막(27) 상

의 금속전극막(35)을 식각하여 드레인(25) 영역과 전기적으로 연결된 제2금속전극(39) 및 상기 게이트 전극패턴 (21)과 전기적으로 연결된 제3금속전극(41)을 형성한다.

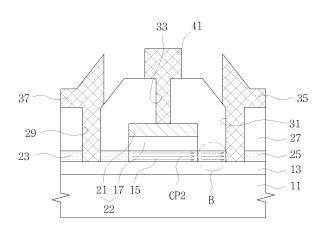

- [0037] 따라서, 본 발명의 실시 예에 따른 박막 트랜지스터는 평판 표시장치의 구동소자로 이용되는 경우 채널영역(15)에서의 전류(CP2)가 드레인 영역(B)에서 분산되어 흐르므로 종래기술 도 1의 국소 영역(A)에 가해지는 스트레스를 줄일 수 있고, 종래기술 도 1에서 도시한 박막 트랜지스터에 대하여 상대적으로 긴 수명을 갖는다. 또한, 본 발명의 실시 예에 따른 박막 트랜지스터는 드레인 영역에서 흐르는 전류의 폭이 넓으므로 향상된 전하이동 특성을 갖는다.

- [0038] 다음으로, 도 2h를 참조하여 본 발명의 실시 예에 따른 박막 트랜지스터에 대하여 설명하기로 한다.

- [0039] 도 2h에서 도시한 바와 같이, 본 발명의 실시 예에 따른 박막 트랜지스터는 기판(11) 상에 차례로 배치된 버퍼막(13) 및 반도체막(15a)을 포함한다. 상기 버퍼막(13)은 실리콘 질화막(SiNx) 또는 실리콘 산화막(SiOx)의 단일막이거나, 다층의 막으로 형성될 수 있다. 예를 들어, 상기 버퍼막(13)은 본 발명의 실시예와 같은 비휘발성 메모리 소자(Non-volatile memory device)에서 열팽창 또는 다른 발막과의 계면 상태 등을 고려하여 유리기판(11) 상에 실리콘 질화막 및 실리콘 산화막이 차례로 적층된 이중막일 수 있다. 이 경우, 상기 실리콘 질화막의 두께는 200nm이고, 상기 실리콘 산화막의 두께는 100nm로 형성되는 것이 바람직하다.

- [0040] 상기 반도체막(15a) 상에 차례로 적충된 절연패턴(17) 및 게이트 전극패턴(21)을 포함하는 게이트 패턴(22)이 배치된다. 상기 절연패턴(17)은 실리콘 산화막 또는 실리콘 질화막으로 된 단일막으로 형성되거나, 복 수의 막으로 형성될 수 도 있다. 상기 게이트 패턴(22) 하부의 반도체막(15a)을 채널영역(15)으로 한정하고, 상기 게이트 패턴(22) 외측의 반도체막(15a)에 불순물이 주입되어 상기 채널영역(15)의 양쪽 측면들과 연결된 소오스(23) 및 드레인(25) 영역이 배치된다. 상기 소오스(23) 및 드레인(25) 영역 각각의 두께는 10nm 내지 50nm인 것이 바람직하다. 상기 채널영역(15)은 게이트 패턴(22)의 폭과 동일한 폭을 갖는다. 상기 채널영역(15)은 비정질 실리콘, 나노결정 실리콘, 마이크로결정 실리콘, 3-5족 반도체, 2-6족 반도체 및 다결정 실리콘 중에서 선택된 어느하나의 물질일 수 있다.

- [0041] 상기 게이트 패턴(22)을 갖는 기판(11)의 전면을 덮는 보호막(27)이 배치된다. 상기 소오스(23) 영역 상에 배치된 보호막(27)의 일영역 및 상기 일영역 하부의 소오스(23)를 관통하여 상기 소오스(23) 영역과 전기적으로 연결된 제1금속전극(37)이 배치된다. 또한, 상기 드레인(25) 영역 상에 배치된 보호막(27)의 일영역 및 상기 일영역 하부의 드레인(25)을 관통하여 상기 드레인(25) 영역과 전기적으로 연결된 제2금속전극(39)이 배치된다. 이경우, 상기 게이트 전극패턴(21) 상에 배치된 보호막(27)의 일영역을 관통하여 게이트 전극패턴(21)과 전기적으로 연결된 제3금속전극(41)이 배치될 수 있다. 상기 제1금속전극(37), 제2금속전극(39) 및 제3금속전극의 각각은 알루미늄 전극 또는 알루미늄 합금 전극을 포함하는 물질일 수 있다.

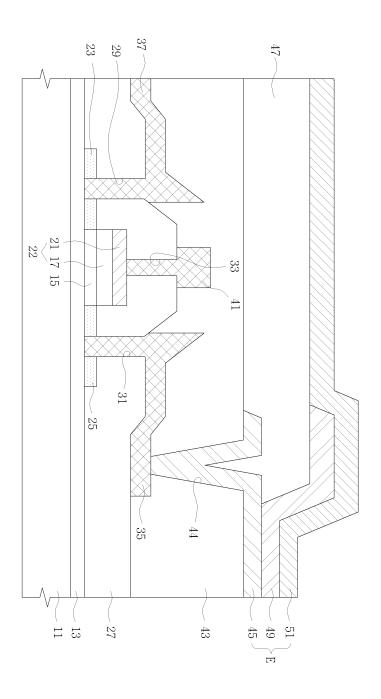

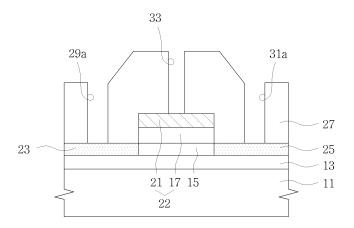

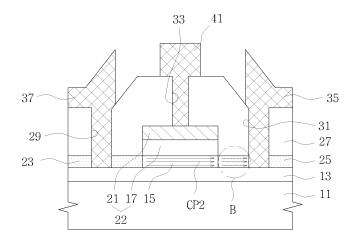

- [0042] 다음으로, 도 2h 및 도 3을 참조하여 본 발명의 실시 예에 따른 박막 트랜지스터를 채택하는 평판 표시장치에 대하여 설명하기로 한다. 도 3은 본 발명의 실시 예에 따른 박막 트랜지스터를 구비하는 평판 표시장치를 개략 적으로 도시한 단면도이다.

- [0043] 도 2h 및 도 3에서 도시한 바와 같이, 평판 표시장치는 박막 트랜지스터를 덮는 보호절연막(17a)을 구비한다. 상기 보호절연막(17a)은 무기 절연막 또는 유기 절연막일 수 있다. 예를 들면, 상기 무기 절연막은 산화 실리콘막, 질화 실리콘막 및 이들의 적층막일 수 있다. 또한, 상기 유기 절연막은 폴리아미드 수지, 폴리이미드 수지 및 아크릴계 수지 등으로 형성된 막일 수 있다. 상기 보호절연막(43) 상에 보호절연막(17a)의 일부를 노출시키는 제1전극(45)이 배치된다.

- [0044] 상기 제1전극(45)은 보호절연막(17a)을 관통하는 비아홀(44)을 채워 박막 트랜지스터의 드레인(25)과 전기적으로 연결된다. 상기 제1전극(45)은 평판 표시장치의 화소별로 패터닝되어 배치될 수 있다. 상기 제1전극(45)은 광투과성 도전막, 광반사성 도전막 또는 이들의 이중막으로 형성될 수 있다. 예를 들어, 상기 광투과성 도전막으로는 인듐 주석산화물(Indium tin oxide;ITO), 인듐 징크 옥사이드(Indium zinc oxide;IZO) 또는 갈륨(Ga)계화합물등으로 형성될 수 있다. 상기 광반사성 도전막으로는 백금(Pt), 금(Au), 이리듐(Ir), 크롬(Cr), 마그네슘(Mg), 은(Ag), 니켈(Ni), 알루미늄(Al) 및 이들의 합금일 수 있다.

- [0045] 상기 노출된 보호절연막(43) 및 상기 비아홀(44)을 채운 제1전극(45)의 일영역 상에 평판 표시장치의 화소를 정의하는 화소 분리막 패턴(47)이 배치된다. 따라서, 상기 화소 분리막 패턴(47)은 평면 상에서 보았을 때 제1전극(45)을 노출하는 격자 형상의 개구부를 갖는다. 다시 말해, 상기 화소 분리막 패턴(47)은 제1전극(45)의 가장자리를 덮도록 기판(11) 상에 배치된다.

- [0046] 상기 화소 분리막 패턴(47)의 가장자리 및 상기 노출된 제1전극(45) 상에 유기발광층(49)이 배치된다. 상기 화소 분리막 패턴(47) 및 상기 유기발광층(49) 상에 제2전극(51)이 배치된다. 상기 제2전극(51)은 마그네슘(Mg), 칼슘(Ca), 알루미늄(Al), 은(Ag) 및 이들의 합금으로 이루어진 군에서 선택된 하나의 물질로 이루어질 수 있다. 상기 유기발광층(49)은 제1전극(45)에서 제공된 제1전하와 제2전극(51)에서 제공된 제2전하가 재결합되면서 영상을 형성하는 빛을 발생한다. 이 경우, 상기 화소 분리막 패턴(47)은 전하 밀도가 높은 제1전극(45)의 가장자리와 제2전극(51) 사이에서 발생할 수 있는 쇼트를 방지하여 유기발광층(49)이 열화되는 것을 막는다. 따라서, 상기 제1전극(45), 유기발광층(49) 및 제2전극(51)은 박막 트랜지스터와 전기적으로 연결된 유기발광 다이오드(E)를 형성한다.

- [0047] 이상 본 발명자에 의해서 이루어진 발명을 상기 실시 예들에서는 반도체 소자의 제조를 일예로 하여 구체적으로 설명하였지만, 본 발명은 상기 실시 예들에 한정되는 것은 아니고 그 요지를 이탈하지 않는 범위에서 자기조립특성을 갖는 나노구조체를 이용한 나노 소자의 제조와 같이 여러 가지로 변경 가능한 것은 물론이다.

- [0048] 도면들에 있어서, 충 및 영역들의 두께는 명확성을 기하기 위하여 과장된 것이다. 또한, 소자(element) 또는 충이 다른 소자 또는 충의 "위(on)" 또는 "상(on)"으로 지칭되는 것은 다른 소자 또는 충의 바로 위 뿐만 아니라 중간에 다른 충 또는 다른 소자를 개재한 경우를 모두 포함한다.

## 산업이용 가능성

[0049] 본 발명은 박막 트랜지스터, 그의 형성방법 및 박막 트랜지스터를 구비하는 평판 표시장치에 관한 것이다. 이와 같은 박막 트랜지스터는 디스플레이 분야에서 폭넓게 응용될 수 있다.

### 도면의 간단한 설명

- [0050] 도 1은 종래기술에 따른 박막 트랜지스터에서 발행하는 문제점을 설명하기 위한 개략적인 단면도.

- [0051] 도 2a 내지 2h는 본 발명의 실시 예에 따른 박막 트랜지스터의 형성방법을 도시한 단면도들.

- [0052] 도 3은 본 발명의 실시 예에 따른 박막 트랜지스터를 구비하는 평판 표시장치를 개략적으로 도시한 단면도.

#### 도면

## 도면1

### 도면2a

## 도면2b

# 도면2c

# 도면2d

# *도면2e*

# *도면2f*

# 도면2g

# 도면2h

# 도면3