### (19) 国家知识产权局

## (12) 发明专利

(10) 授权公告号 CN 114385529 B (45) 授权公告日 2024.11.01

(21)申请号 202011112673.8

(22)申请日 2020.10.16

(65) 同一申请的已公布的文献号 申请公布号 CN 114385529 A

(43) 申请公布日 2022.04.22

(73) 专利权人 瑞昱半导体股份有限公司 地址 中国台湾新竹科学园区创新二路2号

(72) 发明人 林振东 陈月峰

(74) 专利代理机构 中国贸促会专利商标事务所 有限公司 11038

专利代理师 张丹

(51) Int.CI.

**G06F** 13/28 (2006.01)

#### (56) 对比文件

CN 101558396 A,2009.10.14

CN 101796500 A,2010.08.04

审查员 黄子怡

权利要求书2页 说明书7页 附图5页

#### (54) 发明名称

直接记忆体存取控制器、使用其之电子装置以及操作其的方法

#### (57) 摘要

本发明揭露一种直接记忆体存取控制器、使用其之电子装置,以及操作其的方法。该直接记忆体存取控制器用来存取一记忆体,该记忆体包含一特权区域及一普通区域。该操作直接记忆体存取控制器的方法包含:找出该直接记忆体存取控制器中处于一闲置状态的一直接记忆体存取通道;设定该直接记忆体存取通道之一模式暂存器的一暂存值,以令该直接记忆体存取通道操作于一特权模式;设定该直接记忆体存取通道之一地址暂存器及一计数暂存器;以及控制该直接记忆体存取通道基于该地址暂存器及该计数暂存器进行数据搬移。

- 1.一种直接记忆体存取控制器,用来存取一记忆体,该记忆体包含一特权区域及一普通区域,该直接记忆体存取控制器包含:

- 一直接记忆体存取通道;

- 一模式暂存器,用来储存一暂存值,其中当该暂存值为一第一数值时,该直接记忆体存取通道操作于一特权模式,以及当该暂存值为一第二数值时,该直接记忆体存取通道操作于一普通模式;

- 一设定接口,用来接收一控制命令:以及

- 一控制电路, 耦接于该直接记忆体存取通道, 用来根据该控制命令设定该模式暂存器 之该暂存值;

其中,当该直接记忆体存取通道操作于该特权模式时,该直接记忆体存取通道可以存取该特权区域及该普通区域,以及当该直接记忆体存取通道操作于该普通模式时,该直接记忆体存取通道可以存取该普通区域,但无法存取该特权区域。

- 2.根据权利要求1所述之直接记忆体存取控制器,其中该设定接口系一先进外围总线。

- 3.根据权利要求2所述之直接记忆体存取控制器,其中该控制命令包含一特权属性,且该特权属性系对应于该先进外围总线之一保护讯号的其中一比特。

- 4.根据权利要求1所述之直接记忆体存取控制器,其中该直接记忆体存取控制器接收由一处理器所产生之一查询命令,该直接记忆体存取通道回应该查询命令产生一回复内容,该回复内容包含该直接记忆体存取通道之一当前状态。

- 5.根据权利要求4所述之直接记忆体存取控制器,其中当该处理器操作于一特权模式时,该回复内容更包含该直接记忆体存取通道之一当前操作模式。

- 6.根据权利要求1所述之直接记忆体存取控制器,其中该直接记忆体存取控制器接收由一处理器所产生之一查询命令,该直接记忆体存取通道回应该查询命令产生一回复内容,当该直接记忆体存取通道操作于该特权模式且处于一闲置状态,而且该处理器操作于一普通模式时,该回复内容指示该直接记忆体存取通道处于一忙碌状态。

- 7.根据权利要求1所述之直接记忆体存取控制器,其中当该直接记忆体存取通道操作 于该特权模式且收到的该控制命令系一普通模式的控制命令时,该直接记忆体存取通道回 应该普通模式的控制命令产生一中断。

- 8.一种电子装置,包含:

- 一处理器,用来产生一控制命令,其中该控制命令用来设定一直接记忆体存取控制器之一操作模式;

- 一记忆体,包含一特权区域及一普通区域;以及

- 该直接记忆体存取控制器,透过一总线耦接该处理器及该记忆体,包含:

- 一直接记忆体存取通道:

- 一设定接口,其中该直接记忆体存取控制器透过该设定接口接收该控制命令;以及

- 一模式暂存器,用来储存对应于该控制命令的一暂存值,其中当该暂存值为一第一数值时,该直接记忆体存取通道操作于一特权模式,以及当该暂存值为一第二数值时,该直接记忆体存取通道操作于一普通模式;

其中,当该直接记忆体存取通道操作于该特权模式时,该直接记忆体存取通道可以存取该特权区域及该普通区域,以及当该直接记忆体存取通道操作于该普通模式时,该直接

记忆体存取通道可以存取该普通区域,但无法存取该特权区域。

9.一种操作一直接记忆体存取控制器的方法,该直接记忆体存取控制器用来存取一记忆体,该记忆体包含一特权区域及一普通区域,该方法包含:

找出该直接记忆体存取控制器中处于一闲置状态的一直接记忆体存取通道;

设定该直接记忆体存取通道之一模式暂存器的一暂存值,以令该直接记忆体存取通道操作于一特权模式;

设定该直接记忆体存取通道之一地址暂存器及一计数暂存器;

控制该直接记忆体存取通道基于该地址暂存器及该计数暂存器进行数据搬移;以及数据搬移完成之后,判断是否控制该直接记忆体存取通道操作于一普通模式。

10.根据权利要求9所述之方法,其中该设定该直接记忆体存取通道之该模式暂存器的该暂存值的步骤包含:

透过一先进外围总线传送一控制命令以设定该模式暂存器;

其中,该控制命令包含一特权属性,该特权属性系对应于该先进外围总线之一保护讯号的其中一比特。

# 直接记忆体存取控制器、使用其之电子装置以及操作其的 方法

#### 技术领域

[0001] 本发明是关于直接记忆体存取(direct memory access,DMA)控制器,尤其是关于共用DMA控制器,以及操作DMA控制器的方法。

#### 背景技术

[0002] 电子装置通常会将高优先权的数据储存于记忆体中的特权区域(privilege area)(亦称为特权记忆体(privilege memory)),并且将普通(即低优先权)的数据储存于记忆体中的普通区域(normal area)(亦称为普通记忆体(normal memory))。因此,可操作于特权模式及普通模式的系统单芯片(System on a Chip,SoC)通常会为两种模式使用独立的DMA控制器或是独立的DMA通道(DMA channel)。然而,由于DMA控制器或DMA通道不会时时刻刻被同一特权级别(即特权模式或普通模式)使用,所以这样的做法比较耗费资源。

#### 发明内容

[0003] 鉴于先前技术之不足,本发明之一目的在于提供直接记忆体存取控制器、使用直接记忆体存取控制器之电子装置以及操作直接记忆体存取控制器的方法。

[0004] 本发明揭露一种直接记忆体存取控制器,用来存取一记忆体,该记忆体包含一特权区域及一普通区域。该直接记忆体存取控制器包含一直接记忆体存取通道、一模式暂存器、一设定接口以及一控制电路。该模式暂存器用来储存一暂存值。当该暂存值为一第一数值时,该直接记忆体存取通道操作于一特权模式,以及当该暂存值为一第二数值时,该直接记忆体存取通道操作于一普通模式。设定接口用来接收一控制命令。控制电路耦接于该直接记忆体存取通道,用来根据该控制命令设定该模式暂存器之该暂存值。当该直接记忆体存取通道操作于该特权模式时,该直接记忆体存取通道可以存取该特权区域及该普通区域,以及当该直接记忆体存取通道操作于该普通模式时,该直接记忆体存取通道可以存取该普通区域,但无法存取该特权区域。

[0005] 本发明另揭露一种电子装置,包含一处理器、一记忆体以及一直接记忆体存取控制器。该处理器用来产生一控制命令,该控制命令用来设定该直接记忆体存取控制器之一操作模式。该记忆体包含一特权区域及一普通区域。该直接记忆体存取控制器透过一总线耦接该处理器及该记忆体,并且包含一直接记忆体存取通道、一设定接口以及一模式暂存器。该直接记忆体存取控制器透过该设定接口接收该控制命令。该模式暂存器用来储存对应于该控制命令的一暂存值。当该暂存值为一第一数值时,该直接记忆体存取通道操作于一等通模式。当该直接记忆体存取通道操作于一普通模式。当该直接记忆体存取通道操作于该特权模式时,该直接记忆体存取通道可以存取该特权区域及该普通区域,以及当该直接记忆体存取通道操作于该普通模式时,该直接记忆体存取通道可以存取该普通区域,但无法存取该特权区域。

[0006] 本发明另揭露一种操作一直接记忆体存取控制器的方法。该直接记忆体存取控制

器用来存取一记忆体,该记忆体包含一特权区域及一普通区域。该方法包含:找出该直接记忆体存取控制器中处于一闲置状态的一直接记忆体存取通道;设定该直接记忆体存取通道之一模式暂存器的一暂存值,以令该直接记忆体存取通道操作于一特权模式;设定该直接记忆体存取通道之一地址暂存器及一计数暂存器;以及控制该直接记忆体存取通道基于该地址暂存器及该计数暂存器进行数据搬移。

[0007] 本发明之DMA控制器或其DMA通道可以在特权模式与普通模式之间切换。相较于传统技术,本发明之DMA控制器或其DMA通道使用单一的电路或硬体即可实现特权模式之DMA操作及普通模式之DMA操作,因此可以节省硬体资源及降低成本。

[0008] 有关本发明的特征、实作与功效,兹配合图式作实施例详细说明如下。

#### 附图说明

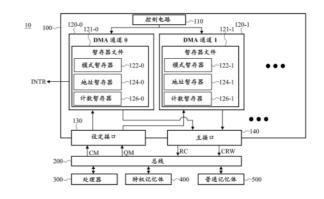

[0009] 图1为本发明DMA控制器之一实施例的功能方块图;

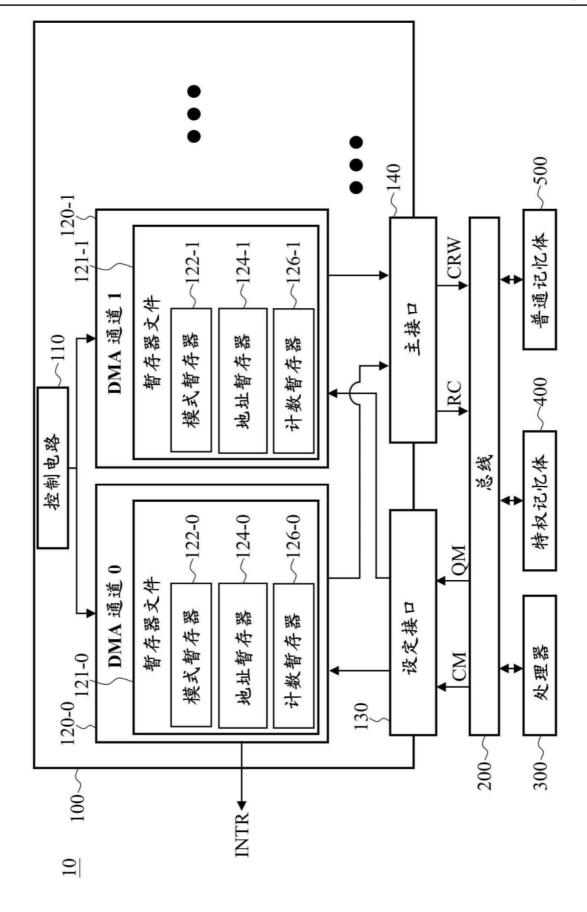

[0010] 图2为本发明操作DMA控制器的方法之一实施例的流程图:

[0011] 图3A为DMA通道120回应轮询的回复内容的一范例;

[0012] 图3B为DMA通道120回应轮询的回复内容的另一范例;

[0013] 图4为DMA通道120用来回应轮询之选择电路的一实施例;以及

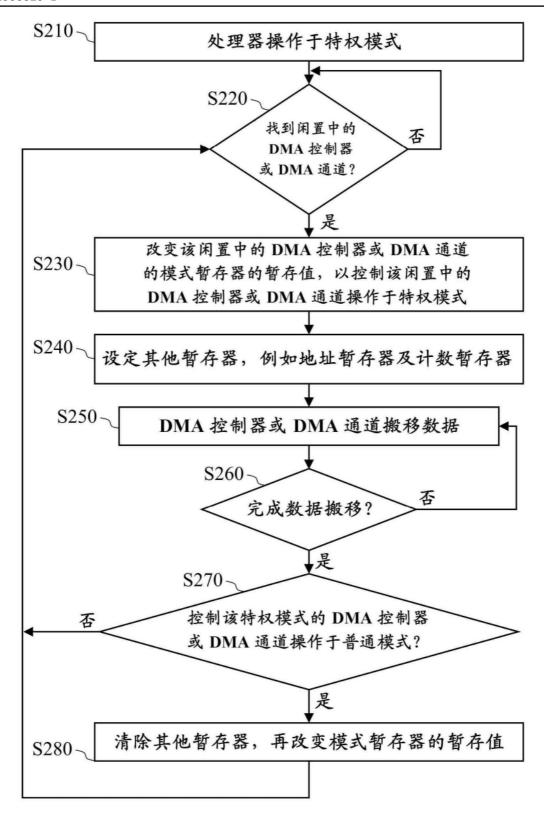

[0014] 图5显示本发明DMA控制器或DMA通道的特权机制之一实施例的流程图。

#### 具体实施方式

[0015] 以下说明内容之技术用语系参照本技术领域之习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语之解释系以本说明书之说明或定义为准。

[0016] 本发明之揭露内容包含直接记忆体存取控制器、使用直接记忆体存取控制器之电子装置以及操作直接记忆体存取控制器的方法。由于本发明之记忆体存取控制器及电子装置所包含之部分元件单独而言可能为已知元件,因此在不影响该装置发明之充分揭露及可实施性的前提下,以下说明对于已知元件的细节将予以节略。

[0017] 在以下的实施例中,DMA控制器包含两个以上的DMA通道,然而,在其他的实施例中,DMA控制器可以只包含一个DMA通道。当DMA控制器可以只包含一个DMA通道时,操作该DMA控制器等效于操作该DMA通道,反之亦然。

[0018] 图1为本发明DMA控制器之一实施例的功能方块图。DMA控制器100包含控制电路110、多个DMA通道120(包含但不限于图中所绘示的两个DMA通道:DMA通道0(120-0)及DMA通道1(120-1))、设定接口(configuration interface)130及主接口(master interface)140。每个DMA通道120包含一个暂存器文件(register file)121,每一个暂存器文件121包含模式暂存器122、地址暂存器(memory address register)124以及计数暂存器(byte count register)126。

[0019] 控制电路110也可以称做DMA控制器100的仲裁器(arbitrator),可以是硬体,或是软体与硬体的组合。当控制电路110由硬体实作时,控制电路110可以是由逻辑电路实作的有限状态机(finite state-machine,FSM)。当控制电路110是硬体与软体的组合时,控制电路110包含计算单元与记忆体。计算单元是具有程序执行能力的电路或电子元件(例如微处理器、微处理单元、数字信号处理器或特殊应用集成电路(application specific

integrated circuit, ASIC)),并且藉由执行储存在记忆体中的程序代码或程序指令来完成控制电路110的功能。

[0020] DMA通道120可以操作在特权模式或普通模式,而且DMA通道0(120-0)与DMA通道1(120-1)互相独立。举例来说,DMA通道0(120-0)及DMA通道1(120-1)可以同时操作在特权模式或普通模式,也可以一者操作在特权模式,另一者操作在普通模式。当DMA通道120的模式暂存器122的暂存值为第一数值(例如逻辑1)时,该DMA通道120操作在特权模式,且当DMA通道120的模式暂存器122的暂存值为第二数值(例如逻辑0)时,该DMA通道120操作在普通模式。

[0021] 当DMA控制器100或DMA通道120被设定为特权模式时,则DMA控制器100或该DMA通道120操作于特权模式,且之后的所有设定或者读取操作,都需要使用特权模式的控制命令来进行。如果是普通模式的控制命令试图读取DMA控制器100或者DMA通道120,或者试图设定DMA控制器100或者DMA通道120来进行数据搬移,则操作于特权模式的DMA控制器100或者操作于特权模式的DMA通道120会拒绝这些操作。在一些实施例中,当普通模式的软体或硬体企图读取操作于特权模式的DMA控制器100的设定或操作于特权模式的DMA通道120的设定时,操作于特权模式的DMA控制器100或操作于特权模式的DMA通道120不回复真实的值,而是回复「0」、保留值(reserved value)或是随机值,以避免普通模式的软体或硬体得知操作于特权模式的DMA控制器100的设定或操作于特权模式的DMA通道120的设定。

[0022] 设定接口130及主接口140透过总线200与处理器300(例如中央处理器、微处理器、微处理单元、数字信号处理器或特殊应用集成电路)、特权记忆体400及普通记忆体500耦接。总线200也可以是连线(interconnect)或总线矩阵。特权记忆体400及普通记忆体500可以是两个独立的实体记忆体(例如动态随机存取记忆体(dynamic random access memory, DRAM)),或是同一个实体记忆体的不同区块或区域(即特权/普通区块,或特权/普通区域)。处理器300透过总线200传送控制命令CM,且DMA控制器100透过设定接口130接收该控制命令CM。控制命令CM可以用来设定DMA通道120的模式暂存器122的暂存值。控制命令CM包含特权属性(privilege attribute),处理器300藉由控制特权属性的值来产生特权模式的控制命令CM或是普通模式的控制命令CM。更明确地说,操作于特权模式的处理器300所产生的控制命令CM的特权属性为第一逻辑值(例如逻辑1),而操作于普通模式的处理器300所产生的控制命令CM的特权属性为第二逻辑值(例如逻辑0)。

[0023] 在一些实施例中,控制电路110根据控制命令CM设定目标DMA通道120的模式暂存器122,更明确地说,控制电路110基于该特权属性来设定目标DMA通道120的模式暂存器122。举例来说,当控制命令CM的特权属性为第一逻辑值(例如逻辑1)时,控制电路110将目标DMA通道120的模式暂存器122的暂存值设为第一逻辑值,且当控制命令CM的特权属性为第二逻辑值(例如逻辑0)时,控制电路110将目标DMA通道120的模式暂存器122的暂存值设为第二逻辑值。在一些实施例中,设定接口130可以是先进外围总线(Advanced Peripheral Bus,APB),且该特权属性为之一保护讯号(Protection signal,Pprot)的其中一比特(例如比特值为0,即Pprot[0])。在其他的实施例中,设定接口130可以是先进高性能总线(Advanced High-performance Bus,AHB)或其他接口。

[0024] 操作于特权模式的处理器300可以读取另一个处理器(图未示)对DMA控制器100或DMA通道120所做的设定,该另一个处理器操作于普通模式。操作于特权模式的处理器300可

以进一步控制DMA控制器100及/或DMA通道120的行为,例如,当DMA控制器100或者DMA通道120被设定为特权模式后,另一个普通模式的处理器是无法获取DMA控制器100或者DMA通道120为自己传输数据的。

[0025] 当DMA通道120操作于特权模式时,DMA通道120可以存取特权记忆体400及普通记忆体500,而当DMA通道120操作于普通模式时,DMA通道120可以存取普通记忆体500,但不能存取特权记忆体400。更明确地说,DMA通道120透过主接口140及总线200传送读写命令CRW给特权记忆体400及/或普通记忆体500。主接口140可以区分特权模式的命令及普通模式的命令。读写命令CRW包含特权属性,而特权记忆体400基于该特权属性来决定是否允许读取及/或写入操作。举例来说,当DMA通道120操作于特权模式时,DMA通道120所发出的读写命令CRW的特权属性为第一逻辑值(对应于特权模式),使得特权记忆体400及普通记忆体500允许读取及/或写入操作;当DMA通道120操作于普通模式时,DMA通道120所发出的读写命令CRW的特权属性为第二逻辑值(对应于普通模式),使得特权记忆体400不允许读取及/或写入操作,但普通记忆体500允许读取及/或写入操作。在一些实施例中,主接口140可以是先进外围总线、先进高性能总线或先进可扩充接口(Advanced eXtensible Interface,AXI)。在一些实施例中,总线200决定是否允许DMA控制器100或DMA通道120存取特权记忆体400。

[0026] 图2为本发明操作DMA控制器的方法之一实施例的流程图。一开始,处理器300操作于特权模式(步骤S210),并且需要寻找一个闲置中(即未被使用)的DMA控制器或DMA通道(步骤S220)。在一些实施例中,处理器300以查询命令QM查询DMA控制器100或DMA通道120的状态,例如以轮询(polling)的方式访问DMA控制器100的每个DMA通道120。回应该轮询讯号,DMA通道120产生回复内容RC,而回复内容RC与处理器300的操作模式(即特权模式或普通模式)有关(如图3A及3B所示)。

[0027] 图3A为当处理器300操作于特权模式时DMA通道120回应轮询讯号的回复内容RC,而图3B为当处理器300操作于普通模式时DMA通道120回应轮询讯号的回复内容RC。在图3A及图3B的例子中,假设DMA通道0至DMA通道3的当前操作模式分别为普通模式、普通模式、特权模式及特权模式,且假设DMA通道0至DMA通道3的当前状态分别为忙碌、闲置、闲置及忙碌。

[0028] 请参阅图3A,当处理器300操作于特权模式时,DMA通道120的回复内容RC包含DMA通道120当下的操作模式以及真实的状态(即闲置或忙碌)。真实的状态指的是DMA通道120的未经调整、修饰或改变过的当前的状态。因此,操作于特权模式的处理器300可以得知DMA通道120当下的操作模式及真实的状态。

[0029] 请参阅图3B,当处理器300操作于普通模式时,DMA通道120的回复内容RC包含状态但不包含操作模式,且回复内容RC中的状态不一定是DMA通道120当下的真实的状态。更明确地说,当操作于普通模式的DMA通道收到来自普通模式的处理器300的轮询讯号时,操作于普通模式的DMA通道回复当下的状态,但不回复操作模式;当操作于特权模式的DMA通道收到来自操作于普通模式的处理器300的轮询讯号时,操作于特权模式的DMA通道一律回复「忙碌」,且不回复操作模式。换言之,虽然DMA通道2事实上处于闲置状态,但是为了避免操作于普通模式的处理器300存取操作于特权模式的DMA通道,所以DMA通道2回复假的状态(fake state)或虚拟的状态(dummy state)。因此,操作于普通模式的处理器300可以得知操作于普通模式的DMA通道的真实的状态,但无法得知操作于特权模式的DMA通道的真实的

状态,而且操作于普通模式的处理器300无法得知DMA通道的操作模式。在这样的设计下,操作于普通模式的处理器300无法设定操作于特权模式的DMA控制器100或操作于特权模式的DMA通道120。

[0030] 在一些实施例中,操作于普通模式的处理器300只能询问DMA控制器100或DMA通道120是否闲置,但是无法终止DMA控制器100或DMA通道120,或是无法使DMA控制器100或DMA通道120离开特权模式。

[0031] 在一些实施例中(如图4所示),操作于特权模式的DMA通道120利用选择电路600 (例如多工器)来基于控制命令CM的特权属性回复真实的状态或虚拟状态。当特权属性为逻辑1(对应于特权模式)时,DMA通道120回复真实的状态;当特权属性为逻辑0(对应于普通模式)时,DMA通道120回复虚拟状态。

[0032] 回到图2。当处理器300没有找到闲置中的DMA控制器或DMA通道(即步骤S220的判断为否)时,处理器300持续寻找闲置中的DMA控制器或DMA通道(步骤S220)。当处理器300找到闲置中的DMA控制器或DMA通道(即步骤S220的判断为是)时,处理器300改变该闲置中的DMA通道的模式暂存器122的暂存值,以控制该闲置中的DMA通道操作于特权模式(步骤S230)。设定完模式暂存器122后,处理器300继续以其他的控制命令设定DMA通道的地址暂存器124及计数暂存器126(步骤S240)。举例来说,处理器300在可以在地址暂存器124中储存待读取或写入的记忆体区块的地址,以及在计数暂存器126中储存数据量。随后,该DMA通道120便基于地址暂存器124中的暂存值及计数暂存器126中的暂存值,透过主接口140发出读写命令CRW以进行数据搬移(步骤S250)。

[0033] 数据搬移完成之后(即步骤S260的判断为是),DMA通道120发出中断通知处理器300数据搬移已完成,然后处理器300判断是否控制该DMA通道操作于普通模式(步骤S270)。如果处理器300要继续使用该DMA通道,则处理器300不控制该DMA通道操作于普通模式(即步骤S270的判断为否),然后于步骤S220中继续选择该DMA通道。如果处理器300不继续使用该DMA通道,则处理器300控制该DMA通道操作于普通模式(即步骤S270的判断为是)。于清除该DMA通道的其他暂存器(包含但不限于地址暂存器124及计数暂存器126)后,处理器300改变该DMA通道的模式暂存器122的暂存值,使该DMA通道操作于普通模式(步骤S280)。如此一来,其他操作于普通模式的处理器300可以在步骤S220中找到该DMA通道。

[0034] 图2的流程虽然以操作于特权模式的处理器300为例,但本技术领域具有通常知识者可以依据上述的说明将本发明应用于操作于普通模式的处理器300,故不再赘述。

[0035] 本发明的DMA控制器或DMA通道应用于电子装置10(例如电脑、可携式电子装置等具有运算能力及数据储存能力的设备,或是系统单芯片),而处理器300可以是电子装置10的中央处理器、微处理器、微处理单元、数字信号处理器或特殊应用集成电路。在一些实施例中,本发明的DMA控制器或DMA通道具有一种特权机制,以保护电子装置10中的机密的或敏感的数据。图5显示该特权机制的流程。操作于特权模式的DMA通道或DMA控制器持续判断所收到的普通模式的控制命令的个数是否大于门槛值(步骤S510、S520)。普通模式的控制命令是指该控制命令的特权属性对应于普通模式,通常是由操作于普通模式的处理器所发出。当操作于特权模式的DMA通道收到的普通模式的控制命令的个数大于门槛值时(即步骤S520的判断为是,代表可能有恶意人士企图窃取特权记忆体400中的数据),操作于特权模式的DMA通道发出中断INTR(步骤S530)。接着,操作于特权模式的处理器300接收该中断

INTR,并且回应该中断INTR重启或关闭电子装置10(步骤S540),以降低数据被窃的风险。

[0036] 在一些实施例中,门槛值可以是零,换言之,只要操作于特权模式的DMA通道或DMA 控制器收到一个普通模式的控制命令,步骤S530及S540就会被执行。

[0037] 在一些实施例中,操作于普通模式的处理器无法接收或得知该中断INTR,以提高此特权机制的可靠性。

[0038] 综上所述,本发明提出了可以操作于特权模式或普通模式的DMA控制器及/或DMA通道,以及操作DMA控制器及/或DMA通道的方法。操作于普通模式的DMA控制器及操作于普通模式的DMA通道无法获取操作于特权模式的DMA控制器所搬移的数据及操作于特权模式的DMA通道所搬移的数据。

[0039] 由于本技术领域具有通常知识者可藉由本案之装置发明的揭露内容来了解本案之方法发明的实施细节与变化,因此,为避免赘文,在不影响该方法发明之揭露要求及可实施性的前提下,重复之说明在此予以节略。请注意,前揭图示中,元件之形状、尺寸、比例以及步骤之顺序等仅为示意,系供本技术领域具有通常知识者了解本发明之用,非用以限制本发明。

[0040] 虽然本发明之实施例如上所述,然而该些实施例并非用来限定本发明,本技术领域具有通常知识者可依据本发明之明示或隐含之内容对本发明之技术特征施以变化,凡此种种变化均可能属于本发明所寻求之专利保护范畴,换言之,本发明之专利保护范围须视本说明书之申请专利范围所界定者为准。

[0041] 【符号说明】

[0042] 10:电子装置

[0043] 100:DMA控制器

[0044] 110:控制电路

[0045] 120-0,120-1:DMA通道

[0046] 121-0,121-1:暂存器文件

[0047] 122-0,122-1:模式暂存器

[0048] 124-0,124-1:地址暂存器

[0049] 126-0,126-1:计数暂存器

[0050] 130:设定接口

[0051] 140:主接口

[0052] 200:总线

[0053] 300: 处理器

[0054] 400:特权记忆体

[0055] 500:普通记忆体

[0056] CM:控制命令

[0057] CRW:读写命令

[0058] QM: 查询命令

[0059] RC:回复内容

[0060] INTR:中断

[0061] 600:选择申路

[0062] S210~S280,S510~S540:步骤

图1

图2

•

DMA通道2 闲置特权模式 闲置 DMA 通道 0

图3A

图3B