# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 116545813 B (45) 授权公告日 2023.09.01

(21) 申请号 202310772007.4

(22) 申请日 2023.06.28

(65) 同一申请的已公布的文献号 申请公布号 CN 116545813 A

(43) 申请公布日 2023.08.04

(73) 专利权人 山东云海国创云计算装备产业创 新中心有限公司

地址 250000 山东省济南市自由贸易试验 区济南片区浪潮路1036号浪潮科技园 S01楼35层

(72) 发明人 展永政 张青 张璐

(74) 专利代理机构 北京集佳知识产权代理有限 公司 11227

专利代理师 马德胜

(51) Int.CI.

H04L 25/03 (2006.01)

### (56) 对比文件

CN 115021747 A,2022.09.06

CN 116016059 A, 2023.04.25

CN 1402546 A,2003.03.12

US 4833691 A,1989.05.23

李易."基于时间数字转换器的全数字锁相 环设计"、《中国硕士学位论文全文数据库信息科 技辑》.2017, (第第11期期), 全文.

审查员 王茜

权利要求书4页 说明书14页 附图7页

#### (54) 发明名称

一种服务器、通信设备、通信芯片以及前向 均衡电路

#### (57) 摘要

本发明公开了一种服务器、通信设备、通信 芯片以及前向均衡电路,属于信号传输领域,用 于对信号进行前向均衡处理。考虑到若利用串行 的延时线电路直接对来自于数据源的连续数据 进行延时线处理,会存在码间干扰问题,因此本 发明中的信号分解模块可以将指定数据源的数 据链路拆分为多个信号链路,然后再利用延时线 处理模块分别对每个信号链路的信号进行延时 线处理以得到多个不同相位的延时信号,接着信 号复接模块可以基于所有的延时信号复接得到 多个不同相位的指定数据源的原始信号,以便完 四 成前向均衡,由于每个信号链路传输的数据在指 定数据源的原始信号中并不连续,因此延时线处 理并不会产生数据的码间干扰,提升了前向均衡 效果以及信号传输可靠性。

1.一种前向均衡电路,其特征在于,包括:

信号分解模块,用于将指定数据源的二进制数据链路拆分为多个信号链路,以便通过多个所述信号链路同时发送所述指定数据源的数据;

延时线处理模块,用于分别对每个所述信号链路的信号进行延时线处理,得到每个所述信号链路对应的多个不同相位的延时信号;

信号复接模块,用于基于所有的所述延时信号,复接得到所述指定数据源的多个不同相位的原始信号;

系数加权模块,用于对各个不同相位的所述原始信号进行系数加权处理,以便完成前向均衡:

其中,每个所述信号链路中相邻的数据,在所述指定数据源的原始信号中的位置不相邻。

- 2.根据权利要求1所述的前向均衡电路,其特征在于,所述信号链路的数量、每个所述信号链路对应的延时信号的数量以及复接得到的所述原始信号的数量均相等,且为预设数值。

- 3. 根据权利要求2所述的前向均衡电路,其特征在于,所述延时线处理模块包括:

与所述信号链路一一对应的多个延时线处理子电路,用于将对应的所述信号链路的信号进行延时线处理,并输出所述信号链路对应的多个不同相位的延时信号。

- 4.根据权利要求3所述的前向均衡电路,其特征在于,所述延时线处理子电路均为树状结构的延时线处理电路。

- 5.根据权利要求4所述的前向均衡电路,其特征在于,所述预设数值为4,每个所述延时 线处理子电路均包括:

输入端与自身对应的所述信号链路连接的第一触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第一延时信号;

输入端与所述第一触发器的输出端连接的第二触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第二延时信号;

输入端与所述第一触发器的输出端连接的第三触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第三延时信号;

输入端与所述第一触发器的输出端连接的第四触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第四延时信号;

其中,第一次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为上升沿触发器,第三触发器与第四触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

第二次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为上升沿触发器,第二触发器与第三触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度;

第三次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为下降沿触发器,第三触发器与第四触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

第四次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为下降沿触发器,第二触发器与第三触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度。

- 6.根据权利要求3所述的前向均衡电路,其特征在于,所述延时线处理子电路均为串行结构的延时线处理电路。

- 7.根据权利要求6所述的前向均衡电路,其特征在于,所述预设数值为4,每个所述延时 线处理子电路均包括:

输入端与自身对应的所述信号链路连接的第五触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第一延时信号;

输入端与第一触发器的输出端连接的第六触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第二延时信号;

输入端与第二触发器的输出端连接的第七触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第三延时信号;

输入端与第三触发器的输出端连接的第八触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第四延时信号;

其中,第一次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为上升沿触发器,第三触发器与第四触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

第二次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为上升沿触发器,第二触发器与第三触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度;

第三次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为下降沿触发器,第三触发器与第四触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

第四次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为下降沿触发器,第二触发器与第三触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度。

8.根据权利要求5所述的前向均衡电路,其特征在于,所述信号复接模块包括四个复接 子电路;

每个所述复接子电路均包括:

输入端分别与自身对应的所述信号链路的两个所述延时信号连接的第一二比一复接器,用于将接收到的两个信号复接为一个信号后输出;

输入端分别与自身对应的所述信号链路的另外两个所述延时信号连接的第二二比一 复接器,用于将接收到的两个信号复接为一个信号后输出;

两个输入端分别与所述第一二比一复接器的输出端以及所述第二二比一复接器的输出端连接的第三二比一复接器,用于将接收到的两个信号复接为一种相位的所述指定数据源的原始信号;

其中,所述第一二比一复接器与所述第二二比一复接器的共四个输入信号分别为四个

所述信号链路对应的序号相同的延时信号,所述第一二比一复接器与所述第二二比一复接器的时钟信号均为基础频率,所述第三二比一复接器的时钟信号的频率为二倍的基础频率。

9. 根据权利要求8所述的前向均衡电路,其特征在于,所述系数加权模块包括:

与所述第三二比一复接器一一对应的乘法器,用于将自身对应的所述第三二比一复接器输出的所述原始信号与抽头系数相乘后得到乘积;

分别与各个所述第三二比一复接器的输出端连接的加法器,用于将各个所述乘法器输出的乘积叠加得到均衡处理后的待发送信号。

10.根据权利要求1所述的前向均衡电路,其特征在于,所述信号分解模块包括:

输入端与所述指定数据源的一个信号输出链路连接的第一二比一解复接器,用于将所述信号输出链路分解为两个信号链路:

输入端与所述第一二比一解复接器的一个输出端连接的第二二比一解复接器,用于将输入端的一个信号链路分解为两个信号链路;

输入端与所述第一二比一解复接器的另一个输出端连接的第三二比一解复接器,用于将输入端的一个信号链路分解为两个信号链路。

11.根据权利要求1至10任一项所述的前向均衡电路,其特征在于,该前向均衡电路还包括:

与所述系数加权模块的输出端连接的信号制式转换模块,用于将所述系数加权模块输出的二进制的待发送信号转换为目标制式,以便通过发射机发送目标制式的所述待发送信号。

- 12.根据权利要求11所述的前向均衡电路,其特征在于,所述目标制式为四电平脉冲幅度调制信号。

- 13.根据权利要求12所述的前向均衡电路,其特征在于,所述信号制式转换模块包括:

输入端与所述系数加权模块的输出端连接的幅值倍增单元,用于对所述待发送信号进行幅值倍增;

输入端与所述系数加权模块的输出端连接的延时单元,用于对所述待发送信号进行一个周期的延迟:

输入端分别与所述幅值倍增单元的输出端以及所述延时单元的输出端连接的加法单元,用于对分别经过所述幅值倍增单元以及所述延时单元的所述待发送信号进行叠加处理,以便得到目标制式的所述待发送信号;

其中,所述延时单元的时钟信号的频率为四倍的基础频率。

14.根据权利要求13所述的前向均衡电路,其特征在干,所述幅值倍增单元为:

可控倍增单元,用于在接收到的控制电压的控制下,将自身的幅值倍增倍数设置为两倍或者零倍。

15.根据权利要求14所述的前向均衡电路,其特征在于,该前向均衡电路还包括用于提供所述前向均衡电路中各个时钟信号的时钟电路;

所述时钟电路包括:

参考时钟源,用于提供具有参考频率的参考时钟;

输入端分别与所述参考时钟源以及频率相位处理单元的输出端连接的频率提升单元,

用于根据所述参考时钟以及频率相位处理单元输出的反馈时钟,生成具有四倍基础频率的第四时钟信号:

输入端与所述频率提升单元的输出端连接的所述频率相位处理单元,用于根据所述第四时钟信号生成具有二倍基础频率的第三时钟信号、均为单倍基础频率的第一时钟信号与第二时钟信号以及所述参考时钟对应的所述反馈时钟;

其中,所述第一时钟信号与所述第二时钟信号中一者的相位为零度,另一者的相位为90度,所述第四时钟信号连接至所述信号制式转换模块,所述第三时钟信号连接至所述信号复接模块,所述第二时钟信号以及所述第一时钟信号均连接至所述延时线处理模块以及所述信号复接模块。

16.根据权利要求15所述的前向均衡电路,其特征在于,所述频率提升单元包括:

输入端作为所述频率提升单元的输入端的鉴频鉴相器,用于根据所述参考时钟以及所述频率相位处理单元输出的反馈时钟的相位差与频率差生成脉冲信号;

输入端与所述鉴频鉴相器的输出端连接的电荷泵,用于将所述脉冲信号转换为电流信号;

低通滤波器,用于在所述电流信号的控制下调节自身内部电容的电压;

压控振荡器,用于在所述低通滤波器的电容电压的控制下,输出具有四倍基础频率的 第四时钟信号。

- 17.根据权利要求16所述的前向均衡电路,其特征在于,所述频率相位处理单元包括:

- 第一二分频单元,用于对所述第四时钟信号进行二分频,得到具有二倍基础频率的第三时钟信号;

- 第二二分频单元,用于对所述第三时钟信号进行二分频,得到单倍基础频率且相位为 零度的第一时钟信号;

- 第一延迟单元,用于将所述第一时钟信号的相位增加为九十度,得到单倍基础频率且相位为90度的第二时钟信号:

相位处理单元,用于对所述第二时钟信号进行相位调节,得到相位与所述参考时钟相等的反馈时钟。

- 18.根据权利要求17所述的前向均衡电路,其特征在于,所述相位处理单元包括:

- 第二延迟单元,用于将所述第二时钟信号的相位增加90度,得到相位为180度的时钟信号;

反相器,用于将所述相位为180度的时钟信号进行反相处理,得到相位与所述参考时钟相等的反馈时钟。

- 19.一种通信芯片,其特征在于,包括通信芯片本体,还包括:

- 设于所述通信芯片本体的如权利要求1至18任一项所述的前向均衡电路。

- 20.一种通信设备,其特征在于,包括通信设备本体以及与所述通信设备本体连接的如权利要求19所述的通信芯片。

- 21.一种服务器,其特征在于,包括服务器本体以及与所述服务器本体连接的如权利要求20所述的通信设备。

# 一种服务器、通信设备、通信芯片以及前向均衡电路

## 技术领域

[0001] 本发明涉及信号传输领域,特别是涉及一种前向均衡电路,本发明还涉及一种服务器、通信设备及其通信芯片。

# 背景技术

[0002] 随着信息速率不断提高,数据传输过程中信道引起信号完整性问题和带宽问题越来越严重,均衡技术成为解决这一问题的有效方法之一,均衡技术具体包括在数据发送前进行数据处理的前向均衡(FFE,Feed Forward Equalization),前向均衡可以在数据到达发射机之前对其进行均衡处理,从而降低由于信道问题引起的信号畸变,目前缺少一种成熟的前向均衡电路,前向均衡效果较差,从而导致信号畸变率较高。

[0003] 因此,如何提供一种解决上述技术问题的方案是本领域技术人员目前需要解决的问题。

## 发明内容

[0004] 本发明的目的是提供一种前向均衡电路,由于每个信号链路传输的数据在指定数据源的原始信号中并不连续,因此延时线处理并不会产生数据的码间干扰,提升了前向均衡效果以及信号传输可靠性;本发明的另一目的是提供一种包括上述前向均衡电路的通信芯片、通信设备以及服务器,由于每个信号链路传输的数据在指定数据源的原始信号中并不连续,因此延时线处理并不会产生数据的码间干扰,提升了前向均衡效果以及信号传输可靠性。

[0005] 为解决上述技术问题,本发明提供了一种前向均衡电路,包括:

[0006] 信号分解模块,用于将指定数据源的二进制数据链路拆分为多个信号链路,以便通过多个所述信号链路同时发送所述指定数据源的数据:

[0007] 延时线处理模块,用于分别对每个所述信号链路的信号进行延时线处理,得到每个所述信号链路对应的多个不同相位的延时信号;

[0008] 信号复接模块,用于基于所有的所述延时信号,复接得到所述指定数据源的多个不同相位的原始信号:

[0009] 系数加权模块,用于对各个不同相位的所述原始信号进行系数加权处理,以便完成前向均衡;

[0010] 其中,每个所述信号链路中相邻的数据,在所述指定数据源的原始信号中的位置不相邻。

[0011] 一方面,所述信号链路的数量、每个所述信号链路对应的延时信号的数量以及复接得到的所述原始信号的数量均相等,且为预设数值。

[0012] 一方面,所述延时线处理模块包括:

[0013] 与所述信号链路一一对应的多个延时线处理子电路,用于将对应的所述信号链路的信号进行延时线处理,并输出所述信号链路对应的多个不同相位的延时信号。

[0014] 一方面,所述延时线处理子电路均为树状结构的延时线处理电路。

[0015] 一方面,所述预设数值为4,每个所述延时线处理子电路均包括:

[0016] 输入端与自身对应的所述信号链路连接的第一触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第一延时信号;

[0017] 输入端与所述第一触发器的输出端连接的第二触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第二延时信号;

[0018] 输入端与所述第一触发器的输出端连接的第三触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第三延时信号;

[0019] 输入端与所述第一触发器的输出端连接的第四触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第四延时信号;

[0020] 其中,第一次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为上升沿触发器,第三触发器与第四触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

[0021] 第二次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为上升沿触发器,第二触发器与第三触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度;

[0022] 第三次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为下降沿触发器,第三触发器与第四触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

[0023] 第四次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为下降沿触发器,第二触发器与第三触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度。

[0024] 一方面,所述延时线处理子电路均为串行结构的延时线处理电路。

[0025] 一方面,所述预设数值为4,每个所述延时线处理子电路均包括:

[0026] 输入端与自身对应的所述信号链路连接的第五触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第一延时信号;

[0027] 输入端与所述第一触发器的输出端连接的第六触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第二延时信号;

[0028] 输入端与所述第二触发器的输出端连接的第七触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第三延时信号:

[0029] 输入端与所述第三触发器的输出端连接的第八触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的所述信号链路的第四延时信号;

[0030] 其中,第一次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为上升沿触发器,第三触发器与第四触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均

为90度;

[0031] 第二次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为上升沿触发器,第二触发器与第三触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度;

[0032] 第三次序的所述信号链路的所述延时线处理子电路中的第一触发器与第二触发器为下降沿触发器,第三触发器与第四触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

[0033] 第四次序的所述信号链路的所述延时线处理子电路中的第一触发器与第四触发器为下降沿触发器,第二触发器与第三触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度。

[0034] 一方面,所述信号复接模块包括四个复接子电路;

[0035] 每个所述复接子电路均包括:

[0036] 输入端分别与自身对应的所述信号链路的两个所述延时信号连接的第一二比一复接器,用于将接收到的两个信号复接为一个信号后输出;

[0037] 输入端分别与自身对应的所述信号链路的另外两个所述延时信号连接的第二二比一复接器,用于将接收到的两个信号复接为一个信号后输出;

[0038] 两个输入端分别与所述第一二比一复接器的输出端以及所述第二二比一复接器的输出端连接的第三二比一复接器,用于将接收到的两个信号复接为一种相位的所述指定数据源的原始信号;

[0039] 其中,所述第一二比一复接器与所述第二二比一复接器的共四个输入信号分别为四个所述信号链路对应的序号相同的延时信号,所述第一二比一复接器与所述第二二比一复接器的时钟信号均为基础频率,所述第三二比一复接器的时钟信号的频率为二倍的基础频率。

[0040] 一方面,所述系数加权模块包括:

[0041] 与所述第三二比一复接器一一对应的乘法器,用于将自身对应的所述第三二比一复接器输出的所述原始信号与抽头系数相乘后得到乘积;

[0042] 分别与各个所述第三二比一复接器的输出端连接的所述加法器,用于将各个所述乘法器输出的乘积叠加得到均衡处理后的待发送信号。

[0043] 一方面,所述信号分解模块包括:

[0044] 输入端与所述指定数据源的一个信号输出链路连接的第一二比一解复接器,用于将所述信号输出链路分解为两个信号链路;

[0045] 输入端与所述第一二比一解复接器的一个输出端连接的第二二比一解复接器,用于将输入端的一个信号链路分解为两个信号链路;

[0046] 输入端与所述第一二比一解复接器的另一个输出端连接的第三二比一解复接器,用于将输入端的一个信号链路分解为两个信号链路。

[0047] 一方面,该前向均衡电路还包括:

[0048] 与所述系数加权模块的输出端连接的信号制式转换模块,用于将所述系数加权模块输出的二进制的待发送信号转换为目标制式,以便通过发射机发送目标制式的所述待发送信号。

[0049] 一方面,所述目标制式为四电平脉冲幅度调制信号。

[0050] 一方面,所述信号制式转换模块包括:

[0051] 输入端与所述系数加权模块的输出端连接的幅值倍增单元,用于对所述待发送信号进行幅值倍增;

[0052] 输入端与所述系数加权模块的输出端连接的延时单元,用于对所述待发送信号进行一个周期的延迟;

[0053] 输入端分别与所述幅值倍增单元的输出端以及所述延时单元的输出端连接的加 法单元,用于对分别经过所述幅值倍增单元以及所述延时单元的所述待发送信号进行叠加 处理,以便得到目标制式的所述待发送信号;

[0054] 其中,所述延时单元的时钟信号的频率为四倍的基础频率。

[0055] 一方面,所述幅值倍增单元为:

[0056] 可控倍增单元,用于在接收到的控制电压的控制下,将自身的幅值倍增倍数设置为两倍或者零倍。

[0057] 一方面,该前向均衡电路还包括用于提供所述前向均衡电路中各个时钟信号的时钟电路;

[0058] 所述时钟电路包括:

[0059] 参考时钟源,用于提供具有参考频率的参考时钟;

[0060] 输入端分别与所述参考时钟源以及频率相位处理单元的输出端连接的频率提升单元,用于根据所述参考时钟以及频率相位处理单元输出的反馈时钟,生成具有四倍基础频率的第四时钟信号:

[0061] 输入端与所述频率提升单元的输出端连接的所述频率相位处理单元,用于根据所述第四时钟信号生成具有二倍基础频率的第三时钟信号、均为单倍基础频率的第一时钟信号与第二时钟信号以及所述参考时钟对应的所述反馈时钟;

[0062] 其中,所述第一时钟信号与所述第二时钟信号中一者的相位为零度,另一者的相位为90度,所述第四时钟信号连接至所述信号制式转换模块,所述第三时钟信号连接至所述信号复接模块,所述第二时钟信号以及所述第一时钟信号均连接至所述延时线处理模块以及所述信号复接模块。

[0063] 一方面,所述频率提升单元包括:

[0064] 输入端作为所述频率提升单元的输入端的鉴频鉴相器,用于根据所述参考时钟以及所述频率相位处理单元输出的反馈时钟的相位差与频率差生成脉冲信号;

[0065] 输入端与所述鉴频鉴相器的输出端连接的电荷泵,用于将所述脉冲信号转换为电流信号;

[0066] 低通滤波器,用于在所述电流信号的控制下调节自身内部电容的电压;

[0067] 压控振荡器,用于在所述低通滤波器的电容电压的控制下,输出具有四倍基础频率的第四时钟信号。

[0068] 一方面,所述频率相位处理单元包括:

[0069] 第一二分频单元,用于对所述第四时钟信号进行二分频,得到具有二倍基础频率的第三时钟信号;

[0070] 第二二分频单元,用于对所述第三时钟信号进行二分频,得到单倍基础频率且相位为零度的第一时钟信号;

[0071] 第一延迟单元,用于将所述第一时钟信号的相位增加为九十度,得到单倍基础频率且相位为90度的第二时钟信号;

[0072] 相位处理单元,用于对所述第二时钟信号进行相位调节,得到相位与所述参考时钟相等的反馈时钟。

[0073] 一方面,所述相位处理单元包括:

[0074] 第二延迟单元,用于将所述第二时钟信号的相位增加90度,得到相位为180度的时钟信号:

[0075] 反相器,用于将所述相位为180度的时钟信号进行反相处理,得到相位与所述参考时钟相等的反馈时钟。

[0076] 为解决上述技术问题,本发明还提供了一种通信芯片,包括通信芯片本体,还包括:

[0077] 设于所述通信芯片本体的如上所述的前向均衡电路。

[0078] 为解决上述技术问题,本发明还提供了一种通信设备,包括通信设备本体以及与所述通信设备本体连接的如上所述的通信芯片。

[0079] 为解决上述技术问题,本发明还提供了一种服务器,包括服务器本体以及与所述服务器本体连接的如上所述的通信设备。

[0080] 有益效果:本发明提供了一种前向均衡电路,考虑到若利用串行的延时线电路直接对来自于数据源的连续数据进行延时线处理,会存在码间干扰问题,因此本发明中的信号分解模块可以将指定数据源的数据链路拆分为多个信号链路,然后再利用延时线处理模块分别对每个信号链路的信号进行延时线处理以得到多个不同相位的延时信号,接着信号复接模块可以基于所有的延时信号复接得到多个不同相位的指定数据源的原始信号,以便完成前向均衡,由于每个信号链路传输的数据在指定数据源的原始信号中并不连续,因此延时线处理并不会产生数据的码间干扰,提升了前向均衡效果以及信号传输可靠性。

[0081] 本发明还提供了一种服务器、通信设备及其通信芯片,具有如上前向均衡电路相同的有益效果。

#### 附图说明

[0082] 为了更清楚地说明本发明实施例中的技术方案,下面将对相关技术和实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

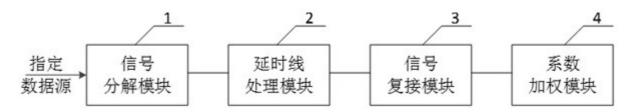

[0083] 图1为本发明提供的一种前向均衡电路的结构示意图;

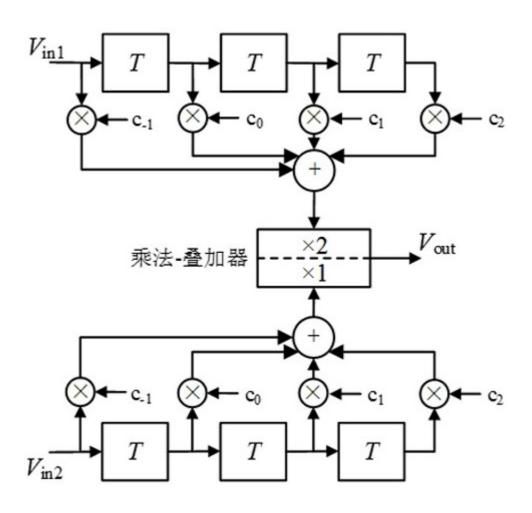

[0084] 图2为相关的一种前向均衡电路的结构示意图:

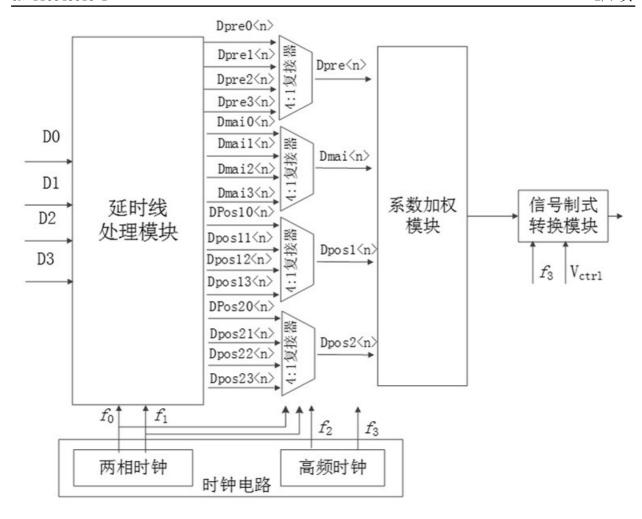

[0085] 图3为本发明提供的另一种前向均衡电路的结构示意图;

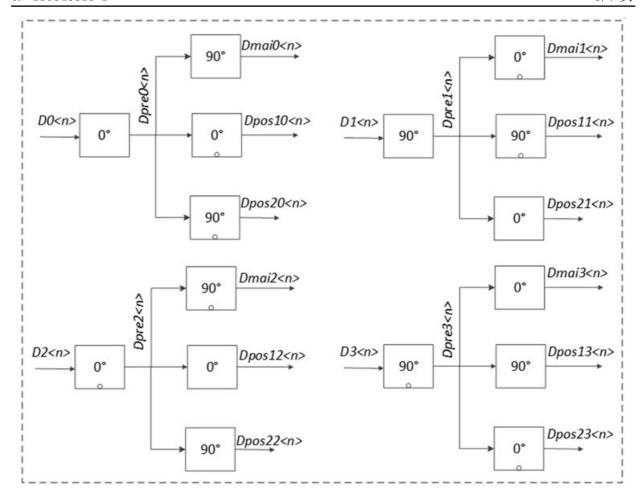

[0086] 图4为本发明提供的树状结构的延时线处理子电路的结构示意图:

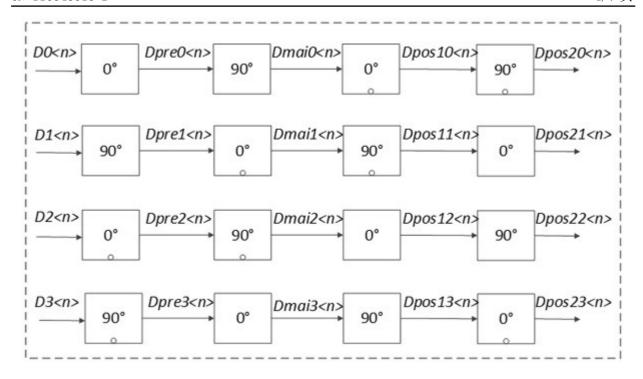

[0087] 图5为本发明提供的串行结构的延时线处理子电路的结构示意图:

[0088] 图6为本发明提供的一种前向均衡电路的工作时序图;

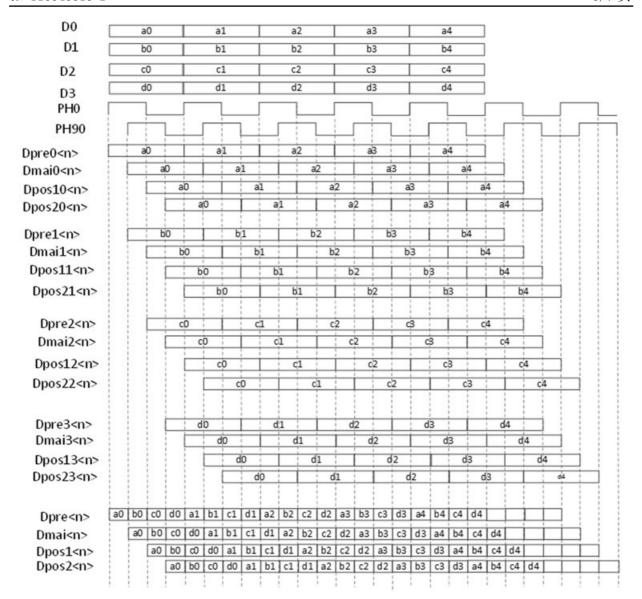

[0089] 图7为本发明提供的一种复接子电路的结构示意图;

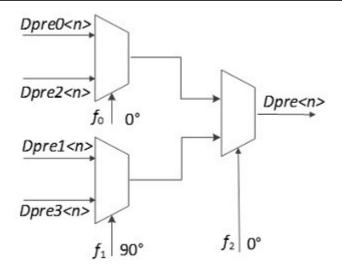

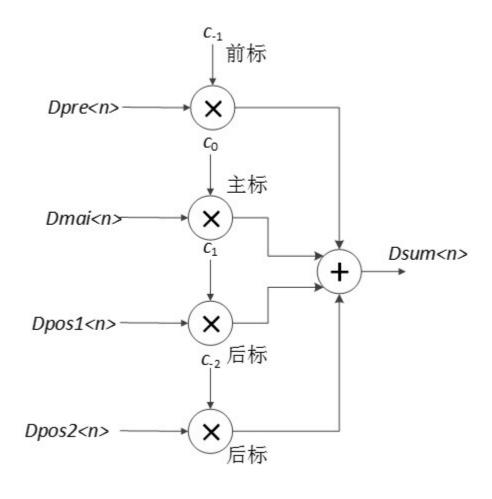

[0090] 图8为本发明提供的一种系数加权模块的结构示意图;

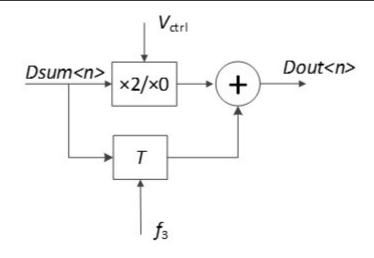

[0091] 图9为本发明提供的一种信号制式转换模块的结构示意图;

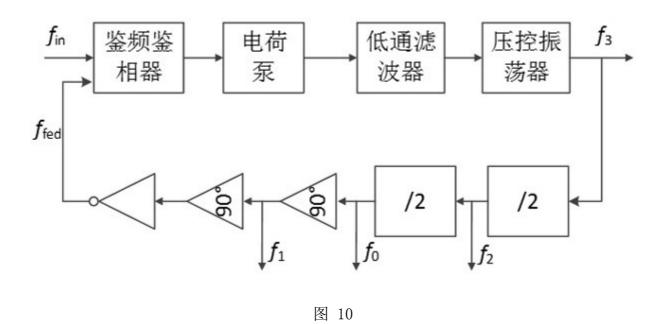

[0092] 图10为本发明提供的一种时钟电路的结构示意图。

## 具体实施方式

[0093] 本发明的核心是提供一种前向均衡电路,由于每个信号链路传输的数据在指定数据源的原始信号中并不连续,因此延时线处理并不会产生数据的码间干扰,提升了前向均衡效果以及信号传输可靠性;本发明的另一核心是提供一种包括上述前向均衡电路的通信芯片、通信设备以及服务器,由于每个信号链路传输的数据在指定数据源的原始信号中并不连续,因此延时线处理并不会产生数据的码间干扰,提升了前向均衡效果以及信号传输可靠性。

[0094] 为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0095] 请参考图1,图1为本发明提供的一种前向均衡电路的结构示意图,该前向均衡电路包括:

[0096] 信号分解模块1,用于将指定数据源的二进制数据链路拆分为多个信号链路,以便通过多个信号链路同时发送指定数据源的数据;

[0097] 延时线处理模块2,用于分别对每个信号链路的信号进行延时线处理,得到每个信号链路对应的多个不同相位的延时信号:

[0098] 信号复接模块3,用于基于所有的延时信号,复接得到指定数据源的多个不同相位的原始信号:

[0099] 系数加权模块4,用于对各个不同相位的原始信号进行系数加权处理,以便完成前向均衡;

[0100] 其中,每个信号链路中相邻的数据,在指定数据源的原始信号中的位置不相邻。

[0101] 为了更好地对本发明实施例进行说明,请参考图2,图2为相关的一种前向均衡电路的结构示意图,图2中传统的PAM4(4-level Pulse Amplitude Modulation,四电平脉冲幅度调制)FFE(Feed Feedback Equalization,前向均衡)电路结构包括6个延时单元(T)、6个乘法器、2个加法器和1个乘法-叠加器。整个电路分为两条延时线,每条延时线通过具有相同抽头系数(ci,i=-1~2)的FFE对输入NRZ(Non-Return to Zero,不归零码)信号(Vin1, Vin2)进行加权处理,然后再以×2和×1的倍数进行幅值倍增和幅值叠加,最后输出PAM4信号。在上支路和下支路中任一支路实现信号传输,最后输出NRZ信号(也即二进制信号)。

[0102] 其中,传统PAM4 FFE结构简单,受工艺截止频率的限制,难以实现高速率传输。而且延时线是线性结构,前后信号之间存在严重的码间干扰,直接影响了均衡效果。另外,传统PAM4 FFE整体架构是对称型的,需要相同的均衡结构,增加了均衡功耗。

[0103] 具体的,考虑到如上背景技术中的技术问题,又结合考虑到针对上述的码间干扰问题,根本原因在于:"通过串行结构的延时线电路直接对来自同一数据源(例如Vin1)的连续数据进行延时线处理",再考虑到可以将来自同一数据源连续的二进制数据拆分为多个信号链路同时进行数据传输,如此一来,拆分得到的每个信号链路所传输的各个数据在该数据源的原始信号中的位置便不是连续的,在这种情况下通过对各个信号链路的信号进行延时线处理以及复接,最终完成前向均衡处理,由于延时线处理的信号链路中的数据在该数据源的原始信号中的位置不连续,因此便不存在码间干扰问题,从而提升了前向均衡的效果,并降低了信号畸变率,提升了用户体验。

[0104] 具体的,基于上述考虑,本发明实施例中可以首先通过信号分解模块1将指定数据源的二进制数据链路拆分为多个信号链路,以便通过多个信号链路同时发送指定数据源的数据,例如假设信号链路的数量为N,那么便可以将指定数据源的数据按照顺序,每次通过所有信号链路同时发送N位数据,信号链路也存在次序,且每次发送的时候,低次序的信号链路发送顺序靠前的数据,N为预设数值,可以进行自主设定,经过如上分解,可以保证每个信号链路所传输的各个数据,在指定数据源中的位置不相邻,从而在对信号连续进行延时线处理时便不会产生码间干扰。

[0105] 其中,在将指定数据源的二进制数据链路拆分为多个信号链路后,需要基于所有信号链路的信号生成指定数据源的多个不同相位的原始信号,以便进行系数加权从而完成前向均衡,因此本发明实施例中可以通过延时线处理模块2分别对每个信号链路的信号进行延时线处理,得到每个信号链路对应的多个不同相位的延时信号,然后再通过信号复接模块3基于所有的延时信号,复接得到指定数据源的多个不同相位的原始信号,便为后续的系数加权做好了准备,最后再通过系数加权模块4对各个不同相位的原始信号进行系数加权处理,以便完成前向均衡。

[0106] 具体的,本发明实施例中的前向均衡电路的原理以及结构均较简洁,且直接对一路数据源进行处理即可,电路成本以及体积较小,且功耗较低。

[0107] 在上述实施例的基础上:

[0108] 作为一种实施例,信号链路的数量、每个信号链路对应的延时信号的数量以及复接得到的原始信号的数量均相等,且为预设数值。

[0109] 具体的,由于前向均衡过程中最终的系数加权处理需要多个相位不同的原始信号,因此本发明实施例中信号链路的数量以及每个信号链路对应的延时信号的数量均可以和复接得到的原始信号的数量保持一致,从而提升电路设计统一性,也使得电路更加简洁,有利于进一步降低电路成本与体积。

[0110] 作为一种实施例,延时线处理模块2包括:

[0111] 与信号链路一一对应的多个延时线处理子电路,用于将对应的信号链路的信号进行延时线处理,并输出信号链路对应的多个不同相位的延时信号。

[0112] 为了更好地对本发明实施例进行说明,请参考图3,图3为本发明提供的另一种前向均衡电路的结构示意图,具体的,为了进一步提升电路简洁性以及保证每个信号链路进行延时线处理的独立性,本发明实施例中的延时线处理模块2可以包括与信号链路一一对应的多个延时线处理子电路,用于将对应的信号链路的信号进行延时线处理,并输出信号链路对应的多个不同相位的延时信号。

[0113] 当然,除了该具体结构外,延时线处理模块2还可以为其他多种类型,本发明实施例在此不做限定。

[0114] 作为一种实施例,延时线处理子电路均为树状结构的延时线处理电路。

[0115] 具体的,树状结构由于层级较少的原因,具有处理速度快的优点,因此本发明实施例中的延时线处理子电路可以统一设计为树状结构的延时线处理电路。

[0116] 当然,除了该具体形式外,延时线处理子电路还可以为其他类型,本发明实施例在此不做限定。

[0117] 作为一种实施例,预设数值为4,每个延时线处理子电路均包括:

[0118] 输入端与自身对应的信号链路连接的第一触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第一延时信号;

[0119] 输入端与第一触发器的输出端连接的第二触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第二延时信号;

[0120] 输入端与第一触发器的输出端连接的第三触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第三延时信号;

[0121] 输入端与第一触发器的输出端连接的第四触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第四延时信号;

[0122] 其中,第一次序的信号链路的延时线处理子电路中的第一触发器与第二触发器为上升沿触发器,第三触发器与第四触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

[0123] 第二次序的信号链路的延时线处理子电路中的第一触发器与第四触发器为上升沿触发器,第二触发器与第三触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度;

[0124] 第三次序的信号链路的延时线处理子电路中的第一触发器与第二触发器为下降沿触发器,第三触发器与第四触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

[0125] 第四次序的信号链路的延时线处理子电路中的第一触发器与第四触发器为下降沿触发器,第二触发器与第三触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度。

[0126] 为了更好地对本发明实施例进行说明,请参考图4,图4为本发明提供的树状结构的延时线处理子电路的结构示意图,具体的,预设数值可以进行自主设定,预设数值为4时,如上的前向均衡电路的设计较为简洁且实用,图4中展示了四个延时线处理子电路,每个延时线处理子电路包括四个触发器,每个延时线处理子电路中最左侧的为第一触发器,其余三个按照从上到下的顺序依次为第二、第三与第四触发器,每个第一触发器输入端标记了对应信号链路的信号(图4中的D0<n>、D1<n>、D2<n>、D3<n>),每个触发器的输出端即为分解得到的一个信号链路所传输的信号名称(例如Dpre0<n>、Dmai0<n>、Dpos10<n>、Dpos20<n>)。

[0127] 具体的,在图4中,以D0<n>为例,D0<n>在相位为0°的时钟信号的上升沿触发下,输出Dpre0<n>;然后,在相位为90°的时钟信号的上升沿触发、相位为0°的时钟信号的下降沿触发、相位为90°的时钟信号的下降沿触发下,分别输出Dmai0<n>、Dpos10<n>和Dpos20<n>。

其他信号D1<n>、D2<n>、D3<n>均是相同过程,只是每个触发器所对应的时钟相位不同。图4中相位为0°的时钟信号的上升沿触发的触发器分别与相位为90°的时钟信号的上升沿触发的触发器、与相位为0°的时钟信号的下降沿触发的触发器、与相位为90°的时钟信号的下降沿触发的触发器之间的相位差为90°、180°和270°,因此图4中关键路径为相位为0°的时钟信号的上升沿触发的触发器与相位为90°的时钟信号的上升沿触发的触发器,最小相位差为90°。

[0128] 具体的,本发明实施例中的树状结构的延时线处理电路具有结构简单、成本低以及体积小等优点。

[0129] 当然,除了该具体构造外,延时线处理子电路还可以为其他具体类型,本发明实施例在此不做限定。

[0130] 作为一种实施例,延时线处理子电路均为串行结构的延时线处理电路。

[0131] 具体的,考虑到串行结构的延时线处理电路具有结构简单以及设计简单的优点, 因此本发明实施例中的延时线处理子电路可以均为串行结构的延时线处理电路。

[0132] 当然,除了该具体形式外,延时线处理子电路还可以为其他构造,本发明实施例在此不做限定。

[0133] 作为一种实施例,预设数值为4,每个延时线处理子电路均包括:

[0134] 输入端与自身对应的信号链路连接的第五触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第一延时信号;

[0135] 输入端与第一触发器的输出端连接的第六触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第二延时信号;

[0136] 输入端与第二触发器的输出端连接的第七触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第三延时信号;

[0137] 输入端与第三触发器的输出端连接的第八触发器,用于结合与自身对应的时钟信号对接收到的信号进行延时处理,得到与自身对应的信号链路的第四延时信号;

[0138] 其中,第一次序的信号链路的延时线处理子电路中的第一触发器与第二触发器为上升沿触发器,第三触发器与第四触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度:

[0139] 第二次序的信号链路的延时线处理子电路中的第一触发器与第四触发器为上升沿触发器,第二触发器与第三触发器为下降沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度;

[0140] 第三次序的信号链路的延时线处理子电路中的第一触发器与第二触发器为下降沿触发器,第三触发器与第四触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为零度,第二触发器与第四触发器对应的时钟信号的相位均为90度;

[0141] 第四次序的信号链路的延时线处理子电路中的第一触发器与第四触发器为下降沿触发器,第二触发器与第三触发器为上升沿触发器,第一触发器与第三触发器对应的时钟信号的相位均为90度,第二触发器与第四触发器对应的时钟信号的相位均为零度。

[0142] 为了更好地对本发明实施例进行说明,请参考图5以及图6,图5为本发明提供的串行结构的延时线处理子电路的结构示意图,图6为本发明提供的一种前向均衡电路的工作时序图,具体的,每个延时线处理子电路同样由四个触发器构成,且延时线处理子电路最左

侧输入端输入的是对应的信号链路的信号,每个触发器的输出端输出的是一种相位的延时信号,具体可以结合图6的时序图来进一步深入了解本发明中前向均衡电路的工作原理,图6中的PH0为相位为零度,频率为单倍基础频率的时钟信号,PH90为相位90度,频率为单倍基础频率的时钟信号,Dpre0<n>、Dmai0<n>、Dpos10<n>、Dpos20<n>为第一次序的信号链路D0对应的四个延时信号,Dpre1<n>、Dmai1<n>、Dpos11<n>、Dpos21<n>为第二次序的信号链路D1对应的四个延时信号.....依次类推,Dpre2<n>、Dmai2<n>、Dpos12<n>、Dpos12<math><n>、Dpos22<n>为第三次序的信号链路D2对应的四个延时信号,Dpre3<n>、Dmai3<math><n>、Dpos13<math><n>、Dpos23<math><n>为第三次序的信号链路D3对应的四个延时信号,而Dpre<n>、Dmai<math><n>、Dmai<math><n>、Dpos1<n>、Dpos2<math><n>则为复接得到的指定数据源的四个不同相位的原始信号。

[0143] 具体的,在图5中,以D0 $\langle n \rangle$ 为例,D0 $\langle n \rangle$ 在相位为0°的时钟信号的上升沿触发下,输出Dpre0 $\langle n \rangle$ ;接着,在相位为90°的时钟信号的上升沿触发下,输出Dmai0 $\langle n \rangle$ ;然后,在相位为0°的时钟信号的下降沿触发下,输出Dpos10 $\langle n \rangle$ ;最后,在相位为90°的时钟信号的下降沿触发下,输出Dpos20 $\langle n \rangle$ 。其他信号D1 $\langle n \rangle$ 、D2 $\langle n \rangle$ 、D3 $\langle n \rangle$ 均是相同过程,只是每个触发器所对应的时钟相位不同。

[0144] 其中,图5中上一级触发器和下一级触发器之间的相位差均为90°,需要对每一对前后触发器都要保持相同的时序要求.

[0145] 当然,除了该具体构造外,延时线处理子电路还可以为其他具体形式,本发明实施例在此不做限定。

[0146] 作为一种实施例,信号复接模块3包括四个复接子电路;

[0147] 每个复接子电路均包括:

[0148] 输入端分别与自身对应的信号链路的两个延时信号连接的第一二比一复接器,用于将接收到的两个信号复接为一个信号后输出;

[0149] 输入端分别与自身对应的信号链路的另外两个延时信号连接的第二二比一复接器,用于将接收到的两个信号复接为一个信号后输出;

[0150] 两个输入端分别与第一二比一复接器的输出端以及第二二比一复接器的输出端连接的第三二比一复接器,用于将接收到的两个信号复接为一种相位的指定数据源的原始信号;

[0151] 其中,第一二比一复接器与第二二比一复接器的共四个输入信号分别为四个信号链路对应的序号相同的延时信号,第一二比一复接器与第二二比一复接器的时钟信号均为基础频率,第三二比一复接器的时钟信号的频率为二倍的基础频率。

[0152] 为了更好地对本发明实施例进行说明,请参考图7,图7为本发明提供的一种复接子电路的结构示意图,具体的,本发明实施例中的复接子电路仅包括三个2:1的复接器,结构简单且成本较低。

[0153] 具体的,图7给出基于两相时钟的复接器,是由3个2:1复接器组成,每个复接器是由1个上升沿触发的触发器和1个下降沿触发的触发器组成。以Dpre0<n>Dpre1<n>Dpre2<n>Dpre3<n>为例,在相位为0°的时钟信号上升沿/下降沿触发下,上支路复接器将<math>Dpre0<nDpre2<n>进行复接;在相位为90°的时钟信号的上升沿/下降沿触发下,下支路复接器将Dpre1<n>Dpre1<n>Dpre3<n>进行复接;然后在相位为0°的时钟信号的上升沿/下降沿触发下,将两路的复接信号再次进行复接,输出<math>Dpre<n>。其他3路4:1复接器分别输出Dmai<n>Dpos1<n

>, Dpos2<n>.

[0154] 当然,除了该具体构造外,复接子电路还可以为其他多种类型,本发明实施例在此不做限定。

[0155] 作为一种实施例,系数加权模块4包括:

[0156] 与第三二比一复接器一一对应的乘法器,用于将自身对应的第三二比一复接器输出的原始信号与抽头系数相乘后得到乘积:

[0157] 分别与各个第三二比一复接器的输出端连接的加法器,用于将各个乘法器输出的乘积叠加得到均衡处理后的待发送信号。

[0158] 为了更好地对本发明实施例进行说明,请参考图8,图8为本发明提供的一种系数加权模块4的结构示意图,具体的,本发明实施例中的系数加权模块4的结构简单,从而减少了电路体积并降低了成本。

[0159] 当然,除了该具体构造外,系数加权模块4还可以为其他多种类型,本发明实施例在此不做限定。

[0160] 作为一种实施例,信号分解模块1包括:

[0161] 输入端与指定数据源的一个信号输出链路连接的第一二比一解复接器,用于将信号输出链路分解为两个信号链路;

[0162] 输入端与第一二比一解复接器的一个输出端连接的第二二比一解复接器,用于将输入端的一个信号链路分解为两个信号链路;

[0163] 输入端与第一二比一解复接器的另一个输出端连接的第三二比一解复接器,用于将输入端的一个信号链路分解为两个信号链路。

[0164] 具体的,信号分解模块1的结构和复接子电路的结构呈镜像,该结构有利于降低电路体积与成本。

[0165] 当然,除了该具体构造外,信号分解模块1还可以为其他多种类型,本发明实施例在此不做限定。

[0166] 作为一种实施例,该前向均衡电路还包括:

[0167] 与系数加权模块4的输出端连接的信号制式转换模块,用于将系数加权模块4输出的二进制的待发送信号转换为目标制式,以便通过发射机发送目标制式的待发送信号。

[0168] 具体的,考虑到不同制式的信号在通过信道传输的过程中的衰减程度不同,因此为了降低信号衰减度,本发明实施例中还可以通过信号制式转换模块将系数加权模块4输出的二进制的待发送信号转换为目标制式,以便通过发射机发送目标制式的待发送信号。

[0169] 作为一种实施例,目标制式为四电平脉冲幅度调制信号。

[0170] 具体的,四电平脉冲幅度调制信号在信道中的抗衰减效果较好,从而能够增强信号传输的稳定性。

[0171] 当然,除了四电平脉冲幅度调制信号外,目标制式还可以为其他多种类型,本发明实施例在此不做限定。

[0172] 作为一种实施例,信号制式转换模块包括:

[0173] 输入端与系数加权模块4的输出端连接的幅值倍增单元,用于对待发送信号进行幅值倍增;

[0174] 输入端与系数加权模块4的输出端连接的延时单元,用于对待发送信号进行一个

周期的延迟;

[0175] 输入端分别与幅值倍增单元的输出端以及延时单元的输出端连接的加法单元,用于对分别经过幅值倍增单元以及延时单元的待发送信号进行叠加处理,以便得到目标制式的待发送信号;

[0176] 其中,延时单元的时钟信号的频率为四倍的基础频率。

[0177] 为了更好地对本发明实施例进行说明,请参考图9,图9为本发明提供的一种信号制式转换模块的结构示意图,具体的,本发明实施例中的信号制式转换模块具有结构简单、提交小以及成本低等优点。图9中的Dsum<n>为二进制的待发送信号,具有x2/x0符号的模块即为幅值倍增单元,其可以在控制电压 $V_{\rm ctrl}$ 的控制下变换倍增倍数为2倍或者0倍,T为延迟单元, $f_3$ 为四倍基础频率的第四时钟信号,加号为加法单元,其输出Dout<n>为目标制式的待发送信号。

[0178] 具体的,当 $V_{\rm ctrl}$ 低电平时,幅值倍增单元选择 $\times$ 0,Dsum $\langle n \rangle$ 经过延时单元重定时后输出NRZ信号;当 $V_{\rm ctrl}$ 高电平时,幅值倍增单元选择 $\times$ 2,Dsum $\langle n \rangle$ 分别经过幅值倍增单元和延时单元,在加法单元中进行叠加处理,输出PAM4信号。

[0179] 当然,除了该具体构造外,信号制式转换模块还可以为其他具体构造,本发明实施例在此不做限定。

[0180] 作为一种实施例,幅值倍增单元为:

[0181] 可控倍增单元,用于在接收到的控制电压的控制下,将自身的幅值倍增倍数设置为两倍或者零倍。

[0182] 具体的,考虑到在不同的情况下,存在以二进制/目标制式进行信号传输的不同需求,因此为了满足不同需求,本发明实施例中的幅值倍增单元为可控倍增单元,可以在接收到的控制电压的控制下,将自身的幅值倍增倍数设置为两倍或者零倍。

[0183] 作为一种实施例,该前向均衡电路还包括用于提供前向均衡电路中各个时钟信号的时钟电路:

[0184] 时钟电路包括:

[0185] 参考时钟源,用于提供具有参考频率的参考时钟;

[0186] 输入端分别与参考时钟源以及频率相位处理单元的输出端连接的频率提升单元,用于根据参考时钟以及频率相位处理单元输出的反馈时钟,生成具有四倍基础频率的第四时钟信号;

[0187] 输入端与频率提升单元的输出端连接的频率相位处理单元,用于根据第四时钟信号生成具有二倍基础频率的第三时钟信号、均为单倍基础频率的第一时钟信号与第二时钟信号以及参考时钟对应的反馈时钟;

[0188] 其中,第一时钟信号与第二时钟信号中一者的相位为零度,另一者的相位为90度, 第四时钟信号连接至信号制式转换模块,第三时钟信号连接至信号复接模块3,第二时钟信 号以及第一时钟信号均连接至延时线处理模块2以及信号复接模块3。

[0189] 为了更好地对本发明实施例进行说明,请参考图10,图10为本发明提供的一种时钟电路的结构示意图,具体的,第四时钟信号在图中为 $f_3$ ,第三时钟信号在图中为 $f_2$ ,第二时钟信号可以为 $f_1$ ,第一时钟信号可以为 $f_0$ , $f_{\rm in}$ 为参考时钟, $f_{\rm fed}$ 为反馈时钟,本发明实施例中提供的时钟电路具有结构简单、体积小以及成本低等优点。

[0190] 具体的,时钟电路包括PFD (Phase Frequency Detector,鉴频鉴相器)、CP (Charge Pump,电荷泵)、LPF (Low Pass Filter,低通滤波器)、VCO (Voltage Controlled Oscillator,压控振荡器)、两个高速二分频、两个相位差90°的延迟单元和1个反相器。PFD 检测输入时钟信号  $f_{\rm in}$ 和反馈时钟信号  $f_{\rm fed}$ 之间的相位差和频率差,并输出脉冲信号,CP将脉冲信号转换为电流信号,在开关管的作用下对LPF中电容进行充放电,从而增加或减小电容上电压  $V_{\rm ctrl}$ 。在高频频率下,VCO选择 LC电感电容结构,电压  $V_{\rm ctrl}$ 控制 VCO中的电容,输出频率为  $f_{\rm 3}$ 的振荡信号;经过一级高速二分频,输出频率为  $f_{\rm 2}$ 的振荡信号;然后经过一个相位差为  $f_{\rm 3}$ 0的远迟单元,输出与频率  $f_{\rm 0}$ 1 相等相位差相差  $f_{\rm 2}$ 00°的同频振荡信号;经过一个反相器,输出相位差为  $f_{\rm 3}$ 0°的反馈信号  $f_{\rm fed}$ 0°的同频振荡信号;经过一个反相器,输出相位差为  $f_{\rm 2}$ 0°的反馈信号  $f_{\rm fed}$ 0°

[0191] 具体的,时钟信号的频率关系可以是 $f_0=f_1=f_2/2=f_3/4$ ,其中 $f_0$ 和 $f_1$ 的相位差为90°。 对于100Gb/s PAM4信号或50Gb/s NRZ信号, $f_3=50$ GHz, $f_2=25$ GHz, $f_0=f_1=12.5$ GHz。

[0192] 当然,除了该具体构造外,时钟电路还可以为其他形式,本发明实施例在此不做限定。

[0193] 作为一种实施例,频率提升单元包括:

[0194] 输入端作为频率提升单元的输入端的鉴频鉴相器,用于根据参考时钟以及频率相位处理单元输出的反馈时钟的相位差与频率差生成脉冲信号;

[0195] 输入端与鉴频鉴相器的输出端连接的电荷泵,用于将脉冲信号转换为电流信号;

[0196] 低通滤波器,用于在电流信号的控制下调节自身内部电容的电压;

[0197] 压控振荡器,用于在低通滤波器的电容电压的控制下,输出具有四倍基础频率的第四时钟信号。

[0198] 具体的,本发明实施例中的频率提升单元具有结构简单以及可靠性强等优点。

[0199] 当然,除了该具体构造外,频率提升单元还可以为其他多种形式,本发明实施例在此不做限定。

[0200] 作为一种实施例,频率相位处理单元包括:

[0201] 第一二分频单元,用于对第四时钟信号进行二分频,得到具有二倍基础频率的第三时钟信号:

[0202] 第二二分频单元,用于对第三时钟信号进行二分频,得到单倍基础频率且相位为零度的第一时钟信号;

[0203] 第一延迟单元,用于将第一时钟信号的相位增加为九十度,得到单倍基础频率且相位为90度的第二时钟信号;

[0204] 相位处理单元,用于对第二时钟信号进行相位调节,得到相位与参考时钟相等的反馈时钟。

[0205] 具体的,本发明实施例中的频率相位处理单元具有结构简单、成本低以及稳定性强等优点。

[0206] 当然,除了该具体构造外,频率相位处理单元还可以为其他形式,本发明实施例在此不做限定。

[0207] 作为一种实施例,相位处理单元包括:

[0208] 第二延迟单元,用于将第二时钟信号的相位增加90度,得到相位为180度的时钟信号;

[0209] 反相器,用于将相位为180度的时钟信号进行反相处理,得到相位与参考时钟相等的反馈时钟。

[0210] 具体的,本发明实施例中的第二延迟单元与反相器可以使得第二时钟信号的相位增加270度,从而与参考时钟相位一致,得到了参考时钟的反馈时钟,具有结构简单以及成本低的优点。

[0211] 当然,除了该具体构造外,相位处理单元还可以为其他具体形式,本发明实施例在此不做限定。

[0212] 本发明还提供了一种通信芯片,包括通信芯片本体,还包括:

[0213] 设于通信芯片本体的如前述实施例中的前向均衡电路。

[0214] 对于本法明实施例提供的通信芯片的介绍请参照前述的前向均衡电路的实施例, 本发明实施例在此不再赘述。

[0215] 本发明还提供了一种通信设备,包括通信设备本体以及与通信设备本体连接的如前述实施例中的通信芯片。

[0216] 对于本法明实施例提供的通信设备的介绍请参照前述的前向均衡电路的实施例,本发明实施例在此不再赘述。

[0217] 本发明还提供了一种服务器,包括服务器本体以及与服务器本体连接的如前述实施例中的通信设备。

[0218] 对于本法明实施例提供的服务器的介绍请参照前述的前向均衡电路的实施例,本发明实施例在此不再赘述。

[0219] 本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。还需要说明的是,在本说明书中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语"包括"、"包含"或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句"包括一个……"限定的要素,并不排除在包括该要素的过程、方法、物品或者设备中还存在另外的相同要素。

[0220] 对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其他实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9