# (19) 中华人民共和国国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 114228725 A (43) 申请公布日 2022. 03. 25

(21) 申请号 202111396753.5

(22)申请日 2021.11.23

(71) 申请人 深圳元戎启行科技有限公司 地址 518000 广东省深圳市福田区福保街 道福保社区桃花路与槟榔道交汇处西 北深九科技创业园6号楼C701 (7-8层)

(72) 发明人 吴童童

(74) 专利代理机构 深圳市威世博知识产权代理 事务所(普通合伙) 44280

代理人 李莉

(51) Int.CI.

**B60W** 50/00 (2006.01)

权利要求书1页 说明书6页 附图2页

#### (54) 发明名称

车载控制系统以及无人驾驶车辆

#### (57) 摘要

本申请公开了车载控制系统以及无人驾驶车辆。该车载控制系统包括:存储器;第一处理单元,与存储器连接,用于对存储器进行数据读写操作;其中,第一处理单元基于FPGA的逻辑资源实现;第二处理单元,与第一处理单元和存储器连接,用于对存储器进行数据读写操作;其中,第一处理单元和第二处理单元在存储器中共享数据地址。通过上述方式,能够减少第二处理单元的资源消耗。

1.一种车载控制系统,其特征在于,所述车载控制系统包括:存储器;

第一处理单元,与所述存储器连接,用于对所述存储器进行数据读写操作;其中,所述 第一处理单元基于FPGA的逻辑资源实现;

第二处理单元,与所述第一处理单元和所述存储器连接,用于对所述存储器进行数据读写操作;

其中,所述第一处理单元和所述第二处理单元在所述存储器中共享数据地址。

2.根据权利要求1所述的车载控制系统,其特征在于,所述车载控制系统还包括:

传感器,所述传感器与所述第一处理单元连接,用于向所述第一处理单元传输传感器数据;

所述第一处理单元用于将所述传感器数据存储至所述存储器的目标共享地址;

所述第二处理单元用于从所述目标共享地址读取所述传感器数据。

- 3.根据权利要求2所述的车载控制系统,其特征在于,所述第一处理单元具体用于将所述传感器数据分多次存储至所述存储器的目标共享地址;以及在最后一次存储完成后,向所述第二处理单元发送存储完成指令。

- 4.根据权利要求2所述的车载控制系统,其特征在于,所述第二处理单元具体用于确定 所述存储器中的所述目标共享地址,并将所述目标共享地址发送至所述第一处理单元。

- 5.根据权利要求2所述的车载控制系统,其特征在于,所述目标共享地址的数量为多个;

所述第一处理单元用于将所述传感器数据按照所述目标共享地址的顺序存储至所述 存储器:

所述第二处理单元用于按照从所述目标共享地址的顺序读取所述传感器数据。

- 6.根据权利要求5所述的车载控制系统,其特征在于,在多个所述目标共享地址占用完后,所述第一处理单元用于在检测所述第二处理单元读取任一所述目标共享地址中的所述 传感器数据时,将所述传感器数据写入空闲的所述目标共享地址。

- 7.根据权利要求2所述的车载控制系统,其特征在于,所述传感器的数量为多个; 所述第一处理单元包括:

多个数据接口,所述多个数据接口用于分别连接多个所述传感器;

多个预处理单元,所述多个预处理单元分别连接所述多个数据接口,用于分别对相应的所述传感器数据进行并行预处理,并将预处理后的所述传感器数据存储至所述目标共享地址。

- 8.根据权利要求1所述的车载控制系统,其特征在于,所述第二处理单元与所述第一处理单元之间通过PCIE接口连接。

- 9.根据权利要求1所述的车载控制系统,其特征在于,所述存储器为DDR。

- 10.一种无人驾驶车辆,其特征在于,所述无人驾驶车辆包括如权利要求1-9任一项所述的车载控制系统。

# 车载控制系统以及无人驾驶车辆

#### 技术领域

[0001] 本申请涉及无人驾驶技术领域,特别涉及车载控制系统以及无人驾驶车辆。

## 背景技术

[0002] 在无人驾驶车辆方面,无人驾驶车辆上的车载控制系统通常具有两个处理器,一个是处理器作为主处理器,另一个处理器作为从处理器。

[0003] 发明人长期研究发现,从处理器对数据的读写需要通过主处理器才能够实现,在此过程中一定程度上对主处理器造成了影响。

## 发明内容

[0004] 为了解决上述问题,本申请提供车载控制系统以及无人驾驶车辆,能够减少第二处理单元的资源消耗。

[0005] 为解决上述技术问题,本申请采用的一个技术方案是:提供一种车载控制系统,该车载控制系统包括:存储器;第一处理单元,与存储器连接,用于对存储器进行数据读写操作;其中,第一处理单元基于FPGA的逻辑资源实现;第二处理单元,与第一处理单元和存储器连接,用于对存储器进行数据读写操作;其中,第一处理单元和第二处理单元在存储器中共享数据地址。

[0006] 其中,车载控制系统还包括:传感器,传感器与第一处理单元连接,用于向第一处理单元传输传感器数据;第一处理单元用于将传感器数据存储至存储器的目标共享地址;第二处理单元用于从目标共享地址读取传感器数据。

[0007] 其中,第一处理单元具体用于将传感器数据分多次存储至存储器的目标共享地址;以及在最后一次存储完成后,向第二处理单元发送存储完成指令。

[0008] 其中,第二处理单元具体用于确定存储器中的目标共享地址,并将目标共享地址发送至第一处理单元。

[0009] 其中,目标共享地址的数量为多个;第一处理单元用于将传感器数据按照目标共享地址的顺序存储至存储器;第二处理单元用于按照目标共享地址的顺序读取传感器数据。

[0010] 其中,在多个目标共享地址占用完后,第一处理单元用于在检测第二处理单元读取任一目标共享地址中的传感器数据时,将传感器数据写入空闲的目标共享地址。

[0011] 其中,传感器的数量为多个;第一处理单元包括:多个数据接口,多个数据接口用于分别连接多个传感器;多个预处理单元,多个预处理单元分别连接多个数据接口,用于分别对相应的传感器数据进行并行预处理,并将预处理后的传感器数据存储至目标共享地址。

[0012] 其中,第二处理单元与第一处理单元之间通过PCIE接口连接。

[0013] 其中,存储器为DDR。

[0014] 为解决上述技术问题,本申请采用的另一个技术方案是:提供一种无人驾驶车辆,

该无人驾驶车辆包括如上述技术方案提供的车载控制系统。

[0015] 本申请实施例的有益效果是:区别于现有技术,本申请提供的车载控制系统,该车载控制系统包括:存储器;第一处理单元,与存储器连接,用于对存储器进行数据读写操作;其中,第一处理单元基于FPGA的逻辑资源实现;第二处理单元,与第一处理单元和存储器连接,用于对存储器进行数据读写操作;其中,第一处理单元和第二处理单元在存储器中共享数据地址。通过上述方式,一方面改变了存储器、第一处理单元和第二处理单元之间的连接关系,改善了相关技术中第一处理单元需要通过中断第二处理单元进行数据存储的过程,减少了数据存储过程中第二处理单元的中断次数,进而减少第二处理单元的资源消耗,另一方面,通过第一处理单元直接对存储器进行数据读写,无需通过中断第二处理单元来完成数据读写,减少了第二处理单元对数据处理的时间,提高了数据的时效性和价值。

# 附图说明

[0016] 为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。其中:

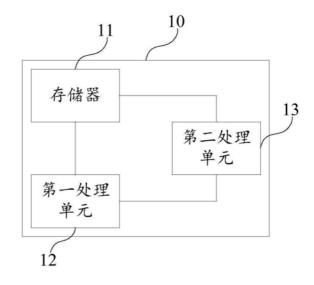

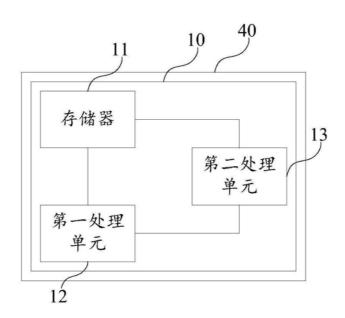

[0017] 图1是本申请提供的车载控制系统第一实施例的结构示意图:

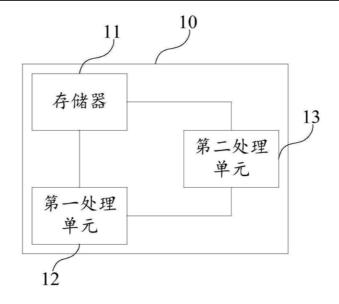

[0018] 图2是本申请提供的车载控制系统第二实施例的结构示意图;

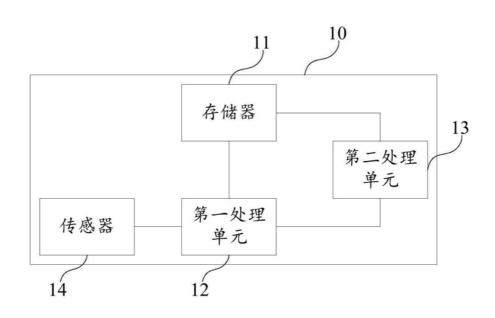

[0019] 图3是本申请提供的车载控制系统第三实施例的结构示意图:

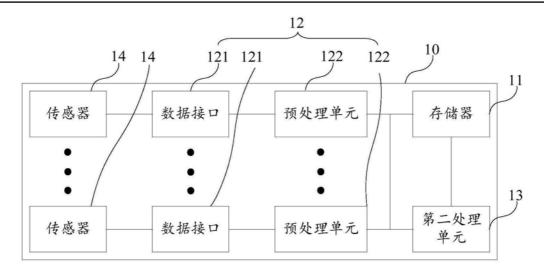

[0020] 图4是本申请提供的无人驾驶车辆一实施例的结构示意图。

## 具体实施方式

[0021] 下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。可以理解的是,此处所描述的具体实施例仅用于解释本申请,而非对本申请的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本申请相关的部分而非全部结构。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

[0022] 在本文中提及"实施例"意味着,结合实施例描述的特定特征、结构或特性可以包含在本申请的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

[0023] 发明人长期研究发现,从处理器对数据的读写需要通过主处理器才能够实现,在此过程中需要对主处理器进行中断,进而使主处理器进行数据读写,这一定程度上对主处理器造成了影响,基于此,本申请提出以下任一技术方案记进行解决。

[0024] 参阅图1,图1是本申请提供的车载控制系统第一实施例的结构示意图。该车载控制系统10包括:存储器11、第一处理单元12和第二处理单元13。

[0025] 其中,第一处理单元12与存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12基于FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)的逻辑资源实现。

[0026] FPGA采用了逻辑单元阵列LCA (Logic Cell Array) 这样一个概念,内部包括可配置逻辑模块CLB (Configurable Logic Block)、输入输出模块IOB (Input Output Block)和内部连线 (Interconnect) 三个部分。现场可编程门阵列 (FPGA) 是可编程器件,与传统逻辑电路和门阵列 (如PAL,GAL及CPLD器件) 相比,FPGA具有不同的结构。FPGA利用小型查找表 (16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/0,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/0模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/0间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

[0027] 第二处理单元13与第一处理单元12和存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12和第二处理单元13在存储器11中共享数据地址。

[0028] 在一些实施例中,可以将存储器11中的数据地址进行预处理,以确定出共享数据地址和非共享数据地址。具体地,可以通过第二处理单元13进行共享数据地址的确定。如,第二处理单元13先确定出存储器11中当前的空闲数据地址。然后按照预设比例,从空闲数据地址中确定出共享数据地址。如,当前空闲地址为500个,预设比例为20%,则从500个空闲地址中确定出100个为共享数据地址。在确定出共享数据地址后,将共享数据地址发送至第一处理单元12,以使第一处理单元12能够知晓具体的共享数据地址。可以理解,预设比例可以根据存储器11中空闲数据地址的具体数量进行动态设置。如,在空闲数据地址较少时,将预设比例调低,在空闲数据地址较多时,将预设比例调高。

[0029] 在一应用场景中,当第一处理单元12接收到数据A时,则可以把该数据A直接存储至共享数据地址中。第二处理单元13也可以在共享数据地址中获取到该数据A。

[0030] 在另一应用场景中,当第一处理单元12需要读取数据A,则可以直接在共享数据地址中进行读取,无需向第二处理单元13发送中断指令,进而使第二处理单元13中断。此时的第二处理单元13不用响应中断指令,减少与第一处理单元12的交互,进而减少对第二处理单元13的资源消耗,第二处理单元13可以继续处理其他任务,进而提升处理效率。

[0031] 在本实施例中,该车载控制系统10包括:存储器11;第一处理单元12,与存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12基于FPGA的逻辑资源实现;第二处理单元13,与第一处理单元12和存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12和第二处理单元13在存储器11中共享数据地址。通过上述方式,一方面改变了存储器11、第一处理单元12和第二处理单元13之间的连接关系,改善了相关技术中第一处理单元12需要通过中断第二处理单元13进行数据存储的过程,减少了数据存储过程中第二处理单元13的中断次数,进而减少第二处理单元13的资源消耗,另一方面,通过第一处理单元12直接对存储器11进行数据读写,无需通过中断第二处理单元13来完成数据读写,减少了第二处理单元13对数据处理的时间,提高了数据的时效性和价值。

[0032] 参阅图2,图2是本申请提供的车载控制系统第二实施例的结构示意图。该车载控制系统10包括:存储器11、第一处理单元12、第二处理单元13和传感器14。

[0033] 其中,传感器14与第一处理单元12连接,用于向第一处理单元12传输传感器数据。 在一些实施例中,传感器14可以是雷达传感器和/或图像传感器。 [0034] 第一处理单元12用于将传感器数据存储至存储器11的目标共享地址。

[0035] 在第二处理单元13需要使用该传感器数据时,第二处理单元13用于从目标共享地 址读取传感器数据。

[0036] 在一应用场景中,第一处理单元12具体用于将传感器数据分多次存储至存储器11的目标共享地址;以及在最后一次存储完成后,向第二处理单元13发送存储完成指令。

[0037] 如,目标共享地址包括目标共享地址A、目标共享地址B和目标共享地址C。第一处理单元12将传感器数据分为3份,存储至目标共享地址中。在第三份存储至目标共享地址完成后,第一处理单元12向第二处理单元13发送存储完成指令。

[0038] 在此过程中,第一处理单元12相当于只向第二处理单元13发送了一次中断指令,相比于相关技术中每一次存储数据均需要向第二处理单元13发送中断指令,以使第二处理单元13对数据进行存储的方式,通过第一处理单元12直接对存储器11进行数据读写,无需通过中断第二处理单元13来完成数据读写,减少了第二处理单元13对数据处理的时间,提高了数据的时效性和价值。

[0039] 在另一应用场景中,第二处理单元13具体用于确定存储器11中的目标共享地址,并将目标共享地址发送至第一处理单元12。第一处理单元12在知晓目标共享地址时,则可以直接从目标共享地址读取相应的数据,或者向目标共享地址写入相应的数据。无需通过中断第二处理单元13来完成数据读写,减少了第二处理单元13对数据处理的时间,提高了数据的时效性和价值。

[0040] 在另一应用场景中,目标共享地址的数量为多个;第一处理单元12用于将传感器数据按照目标共享地址的顺序存储至存储器11;第二处理单元13用于按照目标共享地址的顺序读取传感器数据。

[0041] 如,目标共享地址包括目标共享地址A、目标共享地址B和目标共享地址C。存储顺序为A-C。第一处理单元12用于将传感器数据按照目标共享地址的顺序存储至存储器11即可为第一处理单元12用于将传感器数据先存储至目标共享地址A、在目标共享地址A占用完后,再存储至目标共享地址B,在目标共享地址B占用完后,再存储至目标共享地址C。

[0042] 与此同时,第二处理单元13可以按照存储顺序进行数据读取。如,第二处理单元13 先从目标共享地址A读取数据,在读取完成后可以将目标共享地址A进行擦除操作,以便于目标共享地址A为空闲地址,便于第二处理单元13再次在空闲的目标共享地址A中写入数据。

[0043] 在另一应用场景中,在多个目标共享地址占用完后,第一处理单元12用于在检测第二处理单元13读取任一目标共享地址中的传感器数据时,将传感器数据写入空闲的目标共享地址。

[0044] 参阅图3,图3是本申请提供的车载控制系统第三实施例的结构示意图。该车载控制系统10包括:存储器11、第一处理单元12、第二处理单元13和传感器14。其中,传感器14的数量为多个。

[0045] 第一处理单元12包括:多个数据接口121和多个预处理单元122。其中,多个数据接口121用于分别连接多个传感器14。多个预处理单元122分别连接多个数据接口121,用于分别对相应的传感器数据进行并行预处理,并将预处理后的传感器数据存储至存储器11中的目标共享地址。

[0046] 在本实施例中,通过利用多个预处理单元122对相应的传感器数据进行并行预处理,使每一传感器14对应的传感器数据能够被同步处理,减少对传感器数据的延时,且能够减少对第二处理单元13的资源占用以及可以做到实时对传感器数据进行数据预处理,不需要对传感器数据进行整体缓存,能够减少对传感器数据的处理时间,保证传感器数据的实时性,提高对车辆控制的及时性。

[0047] 在上述任一实施例中,第二处理单元13与第一处理单元12之间通过PCIE (peripheral component interconnect express,高速串行计算机扩展总线标准)接口连接。存储器11为DDR (Double rate synchronous dynamic random access memory,双倍速率同步动态随机存储器)。在其他实施例中,存储器11还可以是其他类型的存储器,如DRAM (Dynamic Random Access Memory,动态随机存储器)、MRAM (Magnetoresistive Random Access Memory,非挥发性的磁性随机存储器)等。

[0048] 相关技术中的基于PCIE数据交互,一次数据传输存在一次中断信号,保证通用数据交互的准确性。本申请通过可以定制化PCIE传输机制。利用第二处理单元13分配好共享的数据地址,即使第一处理单元12对一帧数据分多次传输,也不需要中断通知第二处理单元13,在数据传输完毕后再通知第二处理单元13。减少了第二处理单元13的中断响应,对于第二处理单元13的处理效率有很大提升。

[0049] 参阅图4,图4是本申请提供的无人驾驶车辆一实施例的结构示意图。该无人驾驶车辆40包括车载控制系统10。其中,该车载控制系统10包括:存储器11、第一处理单元12和第二处理单元13。

[0050] 其中,第一处理单元12与存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12基于FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)的逻辑资源实现。

[0051] 第二处理单元13与第一处理单元12和存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12和第二处理单元13在存储器11中共享数据地址。

[0052] 在一些实施例中,可以将存储器11中的数据地址进行预处理,以确定出共享数据地址和非共享数据地址。具体地,可以通过第二处理单元13进行共享数据地址的确定。如,第二处理单元13先确定出存储器11中当前的空闲数据地址。然后按照预设比例,从空闲数据地址中确定出共享数据地址。如,当前空闲地址为500个,预设比例为20%,则从500个空闲地址中确定出100个为共享数据地址。在确定出共享数据地址后,将共享数据地址发送至第一处理单元12,以使第一处理单元12能够知晓具体的共享数据地址。可以理解,预设比例可以根据存储器11中空闲数据地址的具体数量进行动态设置。如,在空闲数据地址较少时,将预设比例调低,在空闲数据地址较多时,将预设比例调高。

[0053] 在一应用场景中,当第一处理单元12接收到数据A时,则可以把该数据A直接存储至共享数据地址中。第二处理单元13也可以在共享数据地址中获取到该数据A。

[0054] 在另一应用场景中,当第一处理单元12需要读取数据A,则可以直接在共享数据地址中进行读取,无需向第二处理单元13发送中断指令,进而使第二处理单元13中断。此时的第二处理单元13不用响应中断指令,减少与第一处理单元12的交互,进而减少对第二处理单元13的资源消耗,第二处理单元13可以继续处理其他任务,进而提升处理效率。

[0055] 在本实施例中,无人驾驶车辆40中的车载控制系统10包括:存储器11;第一处理单

元12,与存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12基于FPGA的逻辑资源实现;第二处理单元13,与第一处理单元12和存储器11连接,用于对存储器11进行数据读写操作;其中,第一处理单元12和第二处理单元13在存储器11中共享数据地址。通过上述方式,一方面改变了存储器11、第一处理单元12和第二处理单元13之间的连接关系,改善了相关技术中第一处理单元12需要通过中断第二处理单元13进行数据存储的过程,减少了数据存储过程中第二处理单元13的中断次数,进而减少第二处理单元13的资源消耗,另一方面,通过第一处理单元12直接对存储器11进行数据读写,无需通过中断第二处理单元13来完成数据读写,减少了第二处理单元13对数据处理的时间,提高了数据的时效性和价值。

[0056] 综上,本申请通过上述任一实施例,自定义PCIE传输和共享数据地址传输。提高了数据传输效率,极大减少了第二处理单元13的负担,可以让第二处理单元13做更多其他模块的处理,能够解决了无人驾驶车辆中第二处理单元13资源紧缺的问题。

[0057] 在本申请所提供的几个实施方式中,应该理解到,所揭露的方法以及设备,可以通过其它的方式实现。例如,以上所描述的设备实施方式仅仅是示意性的,例如,所述电路或单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。

[0058] 所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施方式方案的目的。

[0059] 另外,在本申请各个实施方式中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

[0060] 以上所述仅为本申请的实施方式,并非因此限制本申请的专利范围,凡是根据本申请说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。

图1

图2

图3

图4