# (19) **日本国特許庁(JP)**

# (12) 公 表 特 許 公 報(A)

(11)特許出願公表番号

特表2005-507083 (P2005-507083A)

(43) 公表日 平成17年3月10日(2005.3.10)

| (51) Int.C1.'                     | F 1                                       |             |                      | テーマコード   | (参考)   |

|-----------------------------------|-------------------------------------------|-------------|----------------------|----------|--------|

| GO1L 5/00                         | GO1L                                      | 5/00 1      | l O 1 Z              | 2F051    |        |

| GO1B 7/00                         | GO1B                                      | 7/00        | K                    | 2F055    |        |

| GO1G 3/00                         | GO1G                                      | 3/00        | A                    | 2F063    |        |

| GO1L 1/14                         | GO1L                                      | 1/14        | L                    | 5B087    |        |

| GO1L 9/12                         | GO1L                                      | 9/12        |                      |          |        |

|                                   | 審査請求 未                                    | 請求 予備審      | 查請求 未請求              | (全 82 頁) | 最終頁に続く |

| (21) 出願番号                         | 特願2003-539020 (P2003-539020)              | (71) 出願人    | 504162257            |          |        |

| (86) (22) 出願日                     | 平成14年10月24日 (2002.10.24)                  |             | プレッシャー・プロファイル・システムズ  |          |        |

| (85) 翻訳文提出日                       | 平成16年4月23日 (2004.4.23)                    |             | ・インコーポレーテッド          |          |        |

| (86) 国際出願番号                       | PCT/US2002/034135                         |             | アメリカ合衆国カリフォルニア州9004  |          |        |

| (87) 国際公開番号                       | 国際公開番号 W02003/036612 5, ロサンジェルス, センチュリー・ブ |             | リー・ブー                |          |        |

| (87) 国際公開日 平成15年5月1日 (2003.5.1)   |                                           |             | ルヴァード 5757, スイート 700 |          |        |

| (31) 優先権主張番号 60/347,599           |                                           | (74) 代理人    | 100089705            |          |        |

| (32) 優先日 平成13年10月24日 (2001.10.24) |                                           |             | 弁理士 社本               | 一夫       |        |

| (99) 属生接主非国                       | 水田 (元4)                                   | (71) AN IRE | 100070001            |          |        |

(33) 優先権主張国 米国 (US) (74) 代理人 100076691

弁理士 増井 忠弐

平成13年10月24日 (2001.10.24) (74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

#### (54) 【発明の名称】アレイ・センサ電子回路

米国 (US)

(31) 優先権主張番号 60/343,714

# (57)【要約】

(32) 優先日

(33) 優先権主張国

センサおよびセンサ・アレイ(102,104)の出力 信号を検出し増幅する回路および方法を提供する。ある 形態によれば、センサ・エレメントを含む非線形フィー ドバック・ループは、非線形の変換を提供し、この変換 は、センサ・エレメントの対応する非線形応答を補償し 、これによって、線形化した最終の出力信号を提供する 。他の形態においては、アイドルのセンサは、非アイド ルのセンサ・エレメント上の基準に結合する。他の形態 は、センサおよび増幅回路を含む、これは、在来のフィ ルタ処理およびスイッチングのエレメントなしで動作し 、これにより、より高いスループットを実現し、また従 来のトランジェントに起因するセトリングタイムをが不 要となり、これによって、より大きなセンサ・アレイの 高速の走査を可能にする。本発明のある実施形態は、可 変ギャップ容量性センサ・アレイとその信号処理電子回 路に向けたものである。

#### 【特許請求の範囲】

# 【請求項1】

センサ・システムであって、

複数のセンサ・エレメントを有するセンサ・アレイと、

前記センサ・アレイのうちの少なくとも1つのセンサ・エレメントであって、刺激を検知する前記センサ・エレメントを指示するアドレス可能の接続を有する、前記の少なくとも 1つのセンサ・エレメントと、

前記センサ・エレメントの周囲のフィードバック構成で配置した増幅器であって、前記センサ・エレメントの出力に対応する入力信号を受けそして前記センサ・エレメントを駆動する出力信号を供給する、前記の増幅器と、

を備えたセンサ・システム。

#### 【請求項2】

請求項 1 記載のシステムにおいて、前記センサ・エレメントは、容量性センサ・エレメントから成り、前記センサ・アレイは、容量性センサ・アレイから成ること、を特徴とするセンサ・システム。

#### 【請求項3】

請求項1記載のシステムにおいて、前記刺激は、第1の導電性ストリップと第2の導電性ストリップとの間の分離距離を変化させること、を特徴とするセンサ・システム。

#### 【請求項4】

請求項1記載のシステムにおいて、前記刺激は、力、重さ、圧力、変位および加速のうちの任意のものであること、を特徴とするセンサ・システム。

#### 【請求項5】

請求項1記載のシステムであって、さらに、前記増幅器から出力信号を受ける振幅検出器 を備えたこと、を特徴とするセンサ・システム。

#### 【請求項6】

請求項1記載のシステムであって、さらに、前記増幅器の非線形出力を、前記刺激を表す対応する実質上線形の信号に変換する非線形トランスフォーマを備えたこと、を特徴とするセンサ・システム。

### 【請求項7】

請求項6記載のシステムにおいて、前記非線形トランスフォーマは、前記センサ・エレメントを含むフィードバック・ループであること、を特徴とするセンサ・システム。

# 【請求項8】

請求項1記載のシステムにおいて、前記増幅器の出力信号は、前記センサ・エレメントを 駆動する複数の信号のうちの1つであること、を特徴とするセンサ・システム。

#### 【請求項9】

請求項1記載のシステムにおいて、前記フィルタ処理回路は、デジタル制御される積分器であること、を特徴とするセンサ・システム。

### 【請求項10】

請求項1記載のシステムにおいて、前記センサ・エレメントは、個々に制御されるゲインと個々に制御されるオフセットを有すること、を特徴とするセンサ・システム。

# 【請求項11】

請求項1記載のシステムにおいて、チューニング可能なフィルタ・エレメントは、前記センサ・エレメントに結合し、前記チューニング可能なフィルタ・エレメントは、前記センサ・エレメントの物理的近辺に配置して、環境の影響に対し同相除去を提供すること、を特徴とするセンサ・システム。

# 【請求項12】

請求項1記載のシステムであって、さらに、発振器信号を有する発振器に結合したチューニング可能なフィルタであって、前記発振器信号の位相をシフトさせて位相シフトした信号を供給する前記のチューニング可能なフィルタと、加算回路であって、前記増幅器出力を前記位相シフトされた信号と加算して前記センサ・システムの1部分における発振器バ

10

20

30

40

イアスを実質上キャンセルする前記の加算回路と、を備えたこと、を特徴とするセンサ・ システム。

#### 【請求項13】

請求項1記載のシステムであって、さらに、前記センサ・エレメントから、前記センサ・エレメントに選択的に結合する共通電位への経路を備えたこと、を特徴とするセンサ・システム。

# 【請求項14】

請求項1記載のシステムにおいて、前記センサ・エレメントは、該センサ・エレメントが 駆動あるいはサンプリングされていないとき、グランド電位に選択的に結合すること、を 特徴とするセンサ・システム。

#### 【請求項15】

請求項1記載のシステムにおいて、前記センサ・エレメントは、電磁的影響から個々にシールドされた電気ラインに結合すること、を特徴とするセンサ・システム。

# 【請求項16】

請求項1記載のシステムであって、さらに、少なくとも1つの他のセンサ・システムに結合され、これにより請求項1のシステムと前記少なくとも1つの他のセンサ・システムとが、請求項1のシステムが覆う面積または前記少なくとも1つの他のシステムが覆う面積よりも大きな面積を有する組み合わせの対象領域を覆うこと、を特徴とするセンサ・システム。

#### 【請求項17】

センサ・アレイ上の刺激を測定する方法であって、

前記センサ・アレイの少なくとも 1 つのセンサ・エレメントを使用して前記刺激を検知するステップと、

前記検知した刺激に対応するセンサ・エレメント出力信号を発生するステップと、

前記センサ・エレメント出力信号を増幅して、物理的特性を表す増幅した信号を発生する ステップと、

前記センサ・エレメントを駆動するため、前記増幅した信号をフィードバックするステップと、

を備えた測定方法。

# 【請求項18】

請求項17記載の方法であって、さらに、前記センサ・エレメントを駆動するため発振信号を供給するステップと、前記発振信号の位相をシフトして位相シフトした信号を供給するステップと、前記センサ・エレメント出力と前記位相シフトした信号を加算して前記センサ・システムの1部分における発振器バイアスを実質上キャンセルするステップと、を備えたこと、を特徴とする測定方法。

### 【請求項19】

非線形センサ応答を線形化する方法であって、

センサ・エレメントを使用して刺激を検知するステップと、

前記刺激に対応するセンサ出力信号を発生するステップと、

前記センサ出力信号を、前記非線形センサ応答に対応する非線形トランスフォーマ・フィードバック・ループを通して前記センサの入力にフィードバックするステップと、

を備えた線形化方法。

# 【請求項20】

請求項19記載の方法であって、さらに、前記フィードバック・ループ内に配置した増幅 器を使用して前記センサ出力信号を増幅するステップを含むこと、を特徴とする線形化方 法。

#### 【請求項21】

請求項19記載の方法において、前記非線形センサ応答は、容量性センサ・エレメントに 印加される圧力への非線形応答であること、を特徴とする線形化方法。

### 【請求項22】

50

10

20

30

容量性センサ・アレイにおける寄生容量を低減する方法であって、前記センサ・アレイ内の少なくとも 1 つのセンサ・エレメントを、前記センサ・エレメントがアイドルの時間の間共通電位に選択的に結合すること、を備えた寄生容量低減方法。

#### 【請求項23】

請求項22記載の方法において、前記共通電位は、グランド電位であること、を特徴とする寄生容量低減方法。

### 【請求項24】

請求項22記載の方法において、前記寄生容量は、前記センサ・アレイとグランドとの間の容量であること、を特徴とする寄生容量低減方法。

# 【請求項25】

請求項22記載の方法において、前記寄生容量は、アレイ駆動回路とグランドとの間の容量であること、を特徴とする寄生容量低減方法。

#### 【発明の詳細な説明】

【技術分野】

[0001]

#### 関連出願

本願は、2001年10月24日出願の"容量性アレイ・センサ電子回路(Capacitive A rray Sensor Electronics)"と題する同時係属中の米国仮特許出願第60/347,599号に対し、35U.S.C§119(e)に基づく優先権主張をする。さらに、本願は、2001年10月24日出願の"線形アレイ・データの時間空間視覚化(Time Spatial Visualization of Linear Array)"と題する同時係属中の米国仮特許出願第60/343,714号に関係したものである。本願は、また、同日付けで出願した"有機体内で検出された物理的特性の値の時間に関する視覚化(Visualization of Values of a Physical Property Detected in an Organism Over Time)"(代理人ドケット番号P00660.70004.US)に関係している。上記の出願の各々は、その全体を援用することとする。

#### [0002]

### 技術分野

本願は、容量性アレイ・センサのようなセンサ・システムに関するものである。詳細には、本願は、センサおよびセンサ・アレイから受けた信号を捕捉し、増幅し処理するための回路およびシステムに関している。

#### [0003]

# 背 景

センサは、刺激に応答し、そして刺激の大きさを表す信号、またはその刺激に関係した他の特性を表す信号を発生するデバイスである。この刺激は、センサに影響を与えることができ任意の物理的な量またはパラメータとすることができ、そしてこれは、通常、測定可能なパラメータまたは効果である。センサのアレイは、個々のセンサの集合であって、各々、別個の場所に配置され、そして少なくともある種の面で互いに関係したものである。

#### [0004]

センサ・アレイは、イメージングのような用途において使用され、そして一般には、複数の個々のセンサが、互いに関連するように配置して、実効上より大きなセンサがそれらセンサ・アレイにより形成されるようにする。すなわち、センサを、対象とする領域上に、複数の別個の場所にて配置するとき、対象の領域全体上における刺激のある種の判定または評価を行うことが可能となる。外挿や内挿は、個別のセンサをそれ自体含んでいないスポットにおいて、刺激の大きさの評価を提供することができる。さらに、対象とする領域全体もしくはこの対象領域内のより小さな領域上に刺激の集合した測定値は、個々のセンサから得た信号に対し平均またはその他の処理を行うことにより得ることもできる。

#### [00005]

このようなセンサ・アレイが有用な用途には、タッチパッド、および対象とする領域に対 し印加された力または圧力の場所および大きさの指示を提供する分布センサが含まれる。

# [0006]

50

10

20

30

20

30

40

50

1つのタイプのセンサ・アレイは、容量性センサ・アレイである。このアレイは、グリッタをこのアレイの領域上に分布させて用い、そしてこれらは、グリセセグので記列することができる。センサのグリッドは、としたりのできないしたりできる。特定のセンサをアドレス可能としたりできる。特定のセンサをアドレス対したりできる。特定のセンサをアドレス対対ののとはアレクサ選択言号にしたがって使用して駆動すべきまたはサンプリングすべといっとを決めることにより、実現することができまたはサンプリングするといいできまたはサンプリングするといいできまたはサンプリングするといいできまたはサンプリングするといいできまたはサンプリングするといいできまたはサンプリングするといいできまたはサンプリングするといいできまたはカーン、概してそのセンサを励起またはそのセンサを活性化する。1つのセンサンにおりがするというできないからのはでは、そのセンサからの出力信号を受けて、刺激に対するセンサがらのおいは検出するということを意味する。かあるいは検出するということを意味する。のに使用することができる。マルチプレクサは、測定を希望するその特定の行列を決めるのに使用することができる。

[0007]

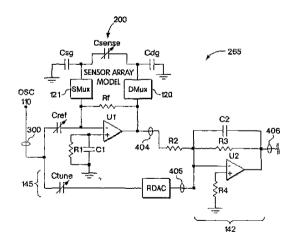

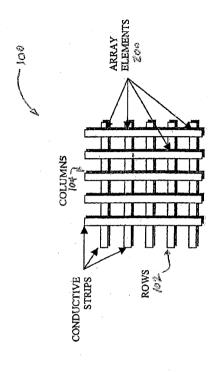

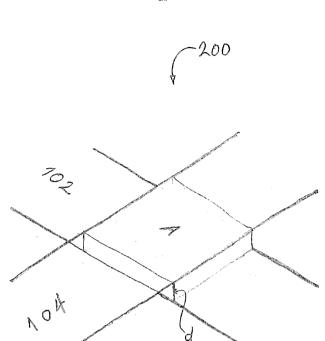

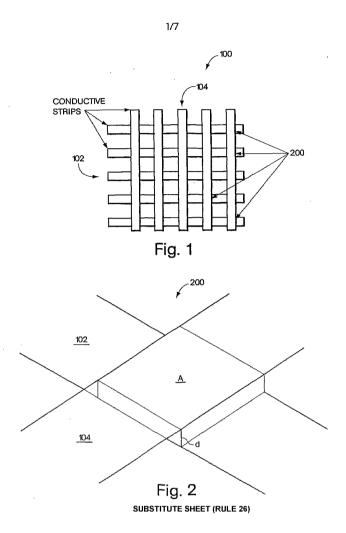

容量性アレイ・センサは、誘電体材料で分離された導電性ストリップの行列で構成されてきている。図1は、容量性アレイ100を示していて、行102および列104に沿って配列した導電性ストリップを有している。容量性アレイ100の行102と列104は、シリコーン・ゲルのような可撓性で変形可能な材料により分離するようにできる。このシリコーン・ゲル(不図示)は、容量性アレイ100の表面に加えられる圧力に応答して変形することになる。シリコーン・ゲルまたは他の可撓性の物質のこの変形は、容量性アレイ100の行102および列104を、互いにより近づけたりあるいはより遠ざけたりすることができる。ギャップ距離(d)は、容量性アレイ100の行102および列104の交差により形成されるキャパシタ200の容量を決めるファクタである。容量性アレイ100の行102および列104が電気接続体および外部回路に結合されると、それら行102および列104の交差により形成されるキャパシタ200の各々の容量は、個々に測定することができる。

[ 0 0 0 8 ]

センサ・アレイは、一時に1つのセンサをあるいはグループでもしくはその全体で、駆動しサンプリングすることができる。容量性アレイ100を走査してその個々のエレメント200の各々から信号または測定値を得ることにより、容量性アレイ100に加えられた圧力のリアルタイム画像を形成することが可能となる。

[0009]

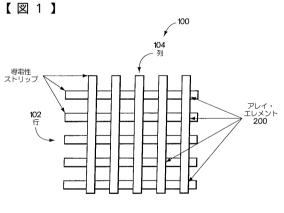

図2は、単一の容量性アレイ・エレメント200を示している。エレメント200は、容量性アレイ100の行102および列104の交差により形成される。この図は、距離またはギャップ(d)を示しており、これは、行102および列104の導電性ストリップを分離している。キャパシタ200の容量は、概して、距離はだけ分けられた行102と列104の交差により形成される面積に比例する。したがって、距離はの変化は、キャパシタ200の値の変化を生じさせる。キャパシタ200の容量と刺激例えば印加圧力との間の関係は、種々の理由から非線形となることがある。それらの理由には、可撓性で変形可能な材料、例えばシリコーン・ゲルの変形反応、並びにこの可変ギャップ容量エレメント200の他の物理的および電気的な応答が含まれる。

【発明の開示】

【発明が解決しようとする課題】

[0010]

大きなアレイに対しては、センサ・アレイ全体の高速の測定または走査を行う際に技術的難問が生じる。例えば、選択した 1 つの行列(これの上で測定を実行する)をサンプリングするマルチプレクサのようなサンプリング回路は、特定の用途により要求される測定値を提供するのに十分なレートにて、すべての行および列(アレイのすべてのエレメント)

をサイクル動作しなければならない。

#### [0011]

個々のキャパシタおよび刺激例えば印加圧力から得る信号における非線形応答は、センサ 回路全体の設計を複雑にする。さらに、測定した信号は、通常、このキャパシタ・アレイ を駆動する駆動信号と比べ小さい。これにより、測定中の量を反映した有用な変調信号を 得ようとするとき、信号対ノイズ比が劣ったものとなる。これは、単純な信号増幅を使用 するとき、信号が測定されるだけでなくノイズが増幅されるからである。

#### [0012]

在来のセンサ回路は、フィルタおよびスイッチを用いており、これらは、アレイの種々のエレメントからの測定値獲得と測定値獲得との間で減衰する必要があるトランジェントを生じさせることにより、獲得時間を遅くする。例えば、センサ・アレイの走査において、スイッチは、在来のアレイの個々のセンサ間で切り換え、これが、トランジェント信号を生じさせる。トランジェントは、1つの完全なセンサ・アレイ走査の獲得を遅くするだけでなく、検知した信号にノイズを導入することによって、刺激の測定値の品質に影響を与えることがある。

#### [0013]

さらにまた、在来のセンサ・アレイは、センサ・エレメントと回路の他の部分例えばグランドとの間にかなりの寄生容量を含んでいる。これら寄生容量は、検知した信号を、ノイズおよび外部からの信号成分で汚染することがあり、またこの寄生容量に対する補償を行うため、余分なフィルタリング回路並びに処理時間を必要とすることがある。

【課題を解決するための手段】

#### [ 0 0 1 4 ]

本発明の1実施形態の面は、センサ・システムに向けたものであり、このセンサ・システムは、複数のセンサ・エレメントを有するセンサ・アレイと、前記センサ・アレイのうちの少なくとも1つのセンサ・エレメントであって、刺激を検知する前記センサ・エレメントを指示するアドレス可能の接続を有する、前記の少なくとも1つのセンサ・エレメントと、前記センサ・エレメントの周囲のフィードバック構成で配置した増幅器であって、前記センサ・エレメントの出力に対応する入力信号を受けそして前記センサ・エレメントを駆動する出力信号を供給する、前記の増幅器と、を備える。

#### [ 0 0 1 5 ]

別の実施形態は、センサ・アレイ上の刺激を測定する方法に向けた面を備え、この測定方法は、前記センサ・アレイの少なくとも 1 つのセンサ・エレメントを使用して前記刺激を検知するステップと、前記検知した刺激に対応するセンサ・エレメント出力信号を発生するステップと、前記センサ・エレメントと駆動するため、前記増幅した信号をを発生するステップと、前記センサ・エレメントを駆動するため、前記増幅した信号をフィードバックするステップと、を備える。

# [0016]

さらに別の実施形態は、非線形センサ応答を線形化する方法に向けた面を備え、この方法は、センサ・エレメントを使用して刺激を検知するステップと、前記刺激に対応するセンサ出力信号を発生するステップと、前記センサ出力信号を、前記非線形センサ応答に対応する非線形トランスフォーマ・フィードバック・ループを通して前記センサの入力にフィードバックするステップと、を備える。

### [0017]

本発明の別の実施形態は、容量性センサ・アレイにおける寄生容量を低減する方法に向けた面を備え、この方法は、前記センサ・アレイ内の少なくとも 1 つのセンサ・エレメントを、前記センサ・エレメントがアイドルの時間の間共通電位に選択的に結合すること、を備える。

## [0018]

#### 詳細な説明

図面において、種々の図に示した各々の類似のコンポーネントは、類似の番号で示してい

20

10

30

50

るが、但し、これは、それらコンポーネントが同一のものであることを必ずしも意味する ものではない。簡単のため、各図面において、すべてのコンポーネントにラベル付けして いない。

### [0019]

本記述は、本発明の好ましい実施形態の種々の面を説明するものである。ある種の面は、他の同時係属の出願において記述してある。詳細には、本出願は、2001年10月24日出願の"容量性アレイ・センサ電子回路(Capacitive Array Sensor Electronics)"と題する同時係属中の米国仮特許出願第60/347,599号に対し、35U.S.C§119(e)に基づく優先権主張をする。さらに、本願は、2001年10月24日出願の"線形アレイ・データの時間空間視覚化(Time Spatial Visualization of Linear Array)"と題する同時係属中の米国仮特許出願第60/343,714号に関係したものである。本願は、また、同日付けで出願した"有機体内で検出された物理的特性の値の時間に関する視覚化(Visualization of Values of a Physical Property Detected in an Organism Over Time)"(代理人ドケット番号P00660.70004.US)に関係する。上記の出願の各々は、その全体を援用することとする。

#### [0020]

本発明は、この好ましい実施形態の以下の詳細な記述および図面に記載した構成の詳細およびコンポーネントの配置にその応用が限定されるものではない。本発明は、他の実施形態を包含するものであって、種々の方法で実施および実行することができる。また、本文で使用する用語は、説明の目的のためのものであり、本発明の種々の面および実施形態を説明するのに使用するとき、限定するものとしてみなされるべきものではない。"備える"、"から成る"、"有する"、"含む"等、およびこれらの変形した表現は、オープン形式(open-end)のものであって、それ以降に列挙するものを少なくとも包含するものである。

#### [0021]

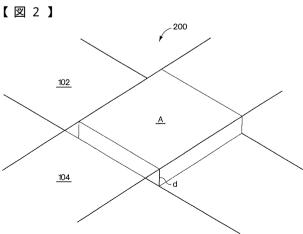

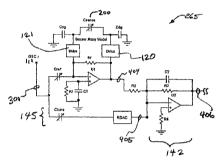

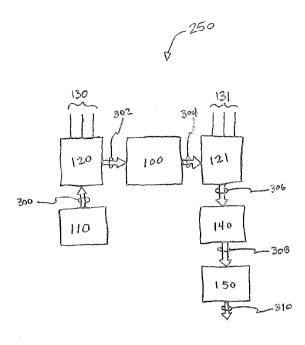

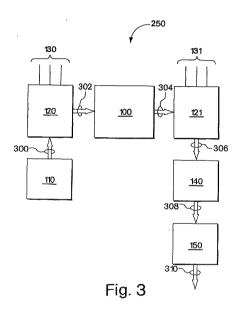

図3は、容量性アレイ100を駆動しサンプリングするのに使う容量性アレイ走査システム250の種々の面を示している。発振器110は、発振器信号300を入力マルチプレクサ(MUX)120に供給し、そしてこのマルチプレクサは、容量性アレイ100のエレメントから、少なくとも発振器信号300により駆動すべき1つ以上のエレメントを選択する。駆動すべきこの1つ以上のエレメントの選択は、入力選択ライン130におけるデータを使用して行う。駆動すべき個々のエレメントまたはエレメントのグループの適切な識別により、電圧または電流を、先に説明した選択したセンサ・エレメント200に対し供給することができる。発振器信号300は、エレメント200を駆動する複数の信号のうちの1つとすることもできる。

# [0022]

アレイ入力信号302は、駆動信号を提供し、そしてこの信号は、選択したセンサ・エレメント200に供給される。このアレイ入力信号302によりいったん励起あるいは駆動されると、この容量性アレイは、アレイ出力信号304を提供する。出力マルチプレクサ121は、アレイ出力信号304を受け、そして出力選択ライン131に供給されるデータに依存して、出力マルチプレクサ121は、選択された信号306を提供する。同じく、この選択信号306は、容量性アレイ100からの1つ以上の選択されたサンプルで構成することができる

ある種の実施形態においては、選択信号306は、増幅器140が増幅する。増幅器140は、アナログ・タイプまたはデジタル・タイプを含む任意のタイプのものが可能であって、これは、増幅された信号308を提供する。ある種の面によれば、この選択信号306の増幅は、刺激の測定の分解能および正確さを向上させる。増幅器140は、1よりも大きいあるいはそれより小さいゲイン並びにユニティ・ゲインを含む任意のゲインを提供することができる。したがって、増幅信号308は、選択信号306よりも大きな振幅を有する信号に制約されることはない。

### [0023]

40

20

増幅信号308は、振幅検出器150が検出し、そしてこの振幅検出器150は、代表的には、増幅信号308において与えられる予測振幅範囲に整合させている。ここで、ある種の実施形態では、トランスコンダクタンス増幅器、エネルギ変換器、あるいは1つのタイプの信号を別のものに変換する他のエレメントを用いることができる。例えば、電圧のような電気信号は、それに対応する光信号に変換することもできる。

[0024]

振幅検出器150は、信号のサイズ、強さあるいは振幅を検出することができる任意の適当な振幅検出器とすることができる。例えば、振幅検出器150は、電圧測定回路または電流測定回路もしくは周波数測定回路で構成することができ、そしてこれらは、簡単のため、本文では振幅検出器として説明する。理解されるべきであるが、増幅器140は、選択信号306の任意のタイプの特性を増幅することができること、また増幅信号308は、単に、特性を増強してこの特性を読み取るかあるいは測定するのを一般により簡単にすることを示すことである。前述のように、交流(AC)電圧信号の振幅は、振幅検出器150を使用して増幅し測定すべき都合の良い特性となることがあるが、本発明は、これに限定されるものではない。

[0025]

振幅検出器150は、検出器出力信号310を提供し、この信号は、増幅信号に対応し、そしてさらに容量性アレイ100の1つエレメントまたはエレメント群から得た選択された信号に対応する。

[0026]

理解されるべきであるが、図3は、容量性アレイ走査システムの単に1つの回路実施形態であり、これにしたがって種々の構成および等価な回路を構成することができる。本文に記述しないが、他の補助的なエレメントおよび回路コンポーネントも、当面のニーズに依存して、種々の応用および実施形態において使用することができる。例えば、ハイパスフィルタ、バンドパスフィルタ、ローパスフィルタのようなフィルタは、望ましくないノイズを低減したり、あるいは走査システム250全体に対し他の信号条件付け機能を提供したりすることができる。さらにまた、ハードウェアおよびソフトウェアの一方または両方において実現される信号処理技術も、走査システム250内の1つ以上の位置において使用することができ、これにより、スペクトル特性または他の機能を、上述の種々の信号に対し付加したりあるいはそれら信号から除去することができる。

[0027]

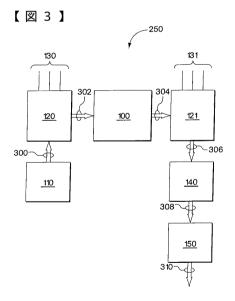

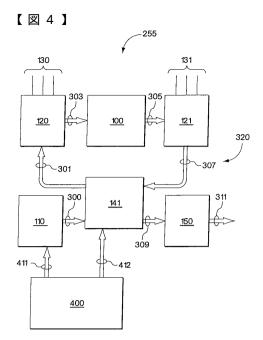

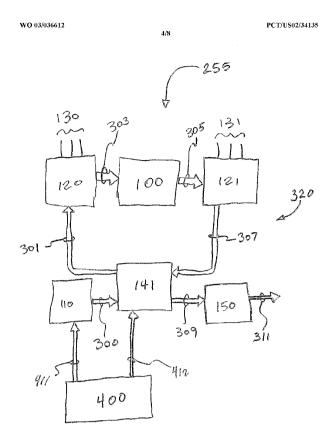

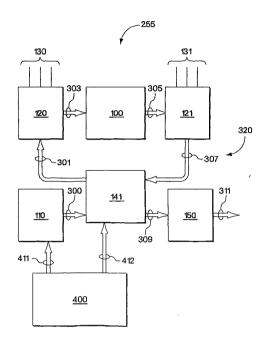

図4は、容量性アレイ走査システム255において使用する本発明の種々の面を示す実施形態を図示している。同じく、この走査システムは、上述の容量性アレイ・センサに対する応用に限定されるものではなく、より一般的には、他のタイプのセンサにも適用することができる。走査システム255は、フィードバック・ループ320を備え、これは、ある種の実施形態においては、以下で説明する線形化機能を提供する。

[0028]

発振器110は、発振器信号300を増幅器141に提供する。この増幅器141は、発振器信号300を増幅し、そして増幅された入力信号を入力マルチプレクサ120に供給する。尚、入力マルチプレクサ120は、駆動マルチプレクサ(DMUX)と呼ぶこともある。入力マルチプレクサ120は、その増幅された入力信号301並びにデータを、上述のように、入力選択ライン130に受ける。アレイ入力信号303は、アレイ入力信号303は、アレイ1100のアレイ・エレメント・メンバ200(不図示)を選択的に駆動する。容量性アレイ100のアレイ・エレメント・メンバ200(不図示)を選択的に駆動する。容量性アレイ1000は、上述したように、アレイ入力信号303より選択的に駆動あるいは励起される。アレイ出力信号305は、容量性アレイ100が出力マルチプレクサ121に提供する。尚、出力マルチプレクサ121は、サンプリング・マルチプレクサ(SMUX)ともある。出力マルチプレクサ121は、選択したアレイ・エレメントを出力サンプリング・ライン131上のデータにしたがってサンプリングする。

[0029]

20

30

50

10

20

30

40

50

出力マルチプレクサ121は、選択された信号307を、増幅器141に供給し戻す。このようにして、増幅器141、容量性アレイ100および他のエレメントは、フィードバック・ループ320内に配置され、そしてこのループにより、増幅入力信号301と選択された信号307とは、容量性アレイの出力の1部分をその入力に戻すように働く。図4のこの実施形態では、入力マルチプレクサ120および出力マルチプレクサ121は、それぞれ、フィードバック・ループ320が増幅器141と容量性アレイ100を結合するエレメントである。

#### [0030]

選択された信号307は、いったん増幅器141に供給されると、増幅されそして増幅された出力信号309として振幅検出器150に供給される。ある種の実施形態においては、信号301および信号309は、同じであるかあるいは同じ値を有するものである。振幅検出器150は、図3に関して説明したのと同様に、検出器出力信号311を提供する。同様に、図4に開示したこの実施形態は、限定するものではなく、当面の用途により要求されるように、適合させそして1つ以上のエレメントまたは補助の回路、フィルタ、増幅器等と置き換えるようにすることもできる。

#### [0031]

また、理解されるように、本実施形態に示した配列は、この走査システムのエレメントの物理的レイアウトを示すものではない。例えば、走査システム255のある種のエレメントは、同じ回路上で実現するのとは対照的に、リモートの回路上で実現することもできる。また、走査システム255の全体は、マイクロチップ上であるいはこの走査システムの機能を実行する他の集積回路上で実現することもできる。さらにまた、走査システム255の種々の機能は、ソフトウェアまたはファームウェアで実行したり、あるいは適当なハードウェアおよびソフトウェアの任意の組合せで実行したりすることができる。この例には、フィルタ処理および増幅を含む種々の機能を実行するデジタル信号処理(DSP)のハードウェアおよびソフトウェアの一方または両方、並びに特定用途向け集積回路(ASIC)が含まれる。

### [ 0 0 3 2 ]

発振器110は、AC波形のような出力電圧信号を供給する。ある種の実施形態では、発振器出力信号300は、実質上、単一周波数の正弦波で構成される。発振器110は、用途に応じて、自走のものとしたりあるいはバースト・モードで使用したりすることができる。本発明のある種の面によれば、発振器出力信号300の振幅および周波数の一方または両方を変更することによって、走査システム255の測定品質、走査レート、別の適で他の動作パラメータを向上させることができる。さらにまた、発振器110は、別の適づなコンポーネントであって、定常的なあるいはパルス状でもしくはプログラム・モードの周期的な駆動信号を提供することができるものと置き換えたりすることができる。1つの例は、発振器110を、マイクロコンピュータあるいは他のデジタル処理制御ユニットであって、発振器出力信号として上述したのと実質上等価な信号を提供するものと置き換えることができる。発振器110は、制御信号411を供給するマイクロプロセッサ400で制御するようにできる。

#### [0033]

入力マルチプレクサ120と出力マルチプレクサ121は、本発明のある種の面において実質上類似の設計のものとすることができる。ある種の実施形態によれば、マルチプレクサ120,121は、単一の行102と列104を容量性アレイ100から選択する。この選択は、アレイ100の単一のエレメント200を指示する。しかし、入力マルチプレクサ120、出力マルチプレクサ121も、多数の行および列を同時に選択するのに使用することもできる。

#### [0034]

高速のセトリングタイムをもつマルチプレクサ設計は、ある種の実施形態では好ましいが、その理由は、高いサンプリング・レートで各センサ・エレメント間の高速のスイッチングを可能にし、これによって走査システム255に対する全帯域幅を改善するからである

0

[0035]

マルチプレクサ120、121の入力選択ライン130と出力選択ライン131におけるデータは、多くの方法で提供することができる。例えば、選択ライン130,131は、マイクロコントローラまたはデジタル信号処理ユニット400によって設定することができ、そしてまた、有限ステートマシンで行われるように自動的に増分するように設定することもできる。加えて、別個の増幅器を、マルチプレクサ120、121の一方または双方において、これらマルチプレクサの入力および出力のいずれにおいても含めることができる。また、マルチプレクサ120、121が使用する多重化技法の1部分として、増幅器を構成することもできる。

10

20

30

40

[0036]

本発明のある種の面によれば、増幅器141を容量性アレイ100とマルチプレクサ12 0、121で構成されるフィードバック・ループ320内に配置することは、より高いゲインを可能にし、またこれによって走査システム255全体においてより高い感度を可能にする。

[0037]

増幅器140および増幅器141の一方または双方は、上述のように実現することもでき、そしてまた、それら増幅器のゲインおよびオフセットを調節するための手段を含めることもできる。増幅器140および増幅器141の一方または双方のそれらゲインおよび増幅器141の一方または双方のそれらゲインおよびオフセットは、エレメント毎に定めたり、あるいはすべてのエレメントに適当な単一のセッティングとして定めたりすることもできる。すなわち、各々の個々のセンサ・エレメントに対し使用する増幅のゲインおよび技法は、そのエレメントに対し個別に定めることもでき、またそのゲインは、アレイ100全体に対し一定に保持するようにすることもできる。アプローチは、適宜使用することができる。マイクロコントローラまたはデジタル信号処理ユニット400は、制御信号412を使用して、総合的な結果を最良のものとするため上記のオフセットおよびゲインの補正を制御することもできる。

[0038]

図4は、マイクロコントローラまたはデジタル信号処理ユニット400を示しており、これは、制御信号411と412をそれぞれ発振器110と増幅器141に供給する。マイクロコントローラ400は、当面の応用に最も適するように、ハードウェアまたはソフトウェアで、またはDSPコンポーネントを含むハードウェアとソフトウェアの組合せで実現することができる。

[0039]

振幅検出器 1 5 0 は、選択された信号 3 0 7 を、通常はアレイ走査レートよりも大きなサンプリング・レートでサンプリングする。 1 実施形態によれば、 1 0 × 1 0 アレイを 1 0 0 H z で走査する場合、走査レートは 1 0 K H z である。この実施形態では、振幅検出器 1 5 0 は、 1 0 K H z よりも大きなレートで個々の測定を完了することになる。

[0040]

本発明のある種の実施形態によれば、振幅検出器 1 5 0 は、出力マルチプレクサ 1 2 1 の出力を整流する整流器を使用して実現し、これによって、非線形トランスフォーマとして作用する。これにより実現される非線形変換は、その結果のトランスフォーマ出力信号を整数個の周期にわたって積分することにより、増大することがある。 1 実施形態では、この積分は、1 0 サイクルにわたって行う。

[ 0 0 4 1 ]

上記の非線形変換は、その信号において、検知された信号 3 0 5 または選択された信号 3 0 7 の振幅に比例した D C 成分を生成する機能を構成することができる。限定目的で本文において記述するものではないが、そのような非線形変換の例には、全波整流または半波整流、原駆動用 A C 信号との位相補正乗算 (phase-corrected multiplication)、並びに出力信号をそれ自身と乗算して二乗した出力信号を得ること、が含まれる。さらに、振幅検

出器150は、実効値(RMS)測定回路、ピーク検出器回路、包絡線検出器回路、または振幅変調回路およびローパスフィルタ回路で構成することもできる。振幅検出はまた、ある種の実施形態においては、アナログ・デジタル・コンバータ(A/D)を使ってAC波形をサンプリングし、そしてデジタル信号プロセッサまたはマイクロコントローラを使ってそのサンプリングしたデータから測定した信号の振幅を計算することにより実現することもできる。上記のように、デジタル方法およびアナログ方法の両方を、振幅検出に使用することもできる。

# [ 0 0 4 2 ]

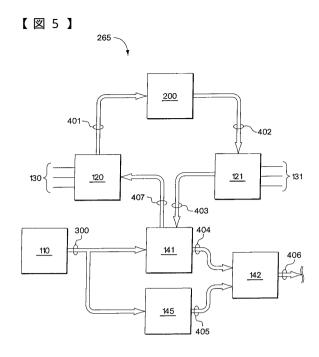

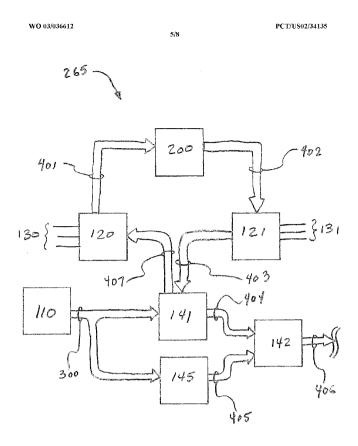

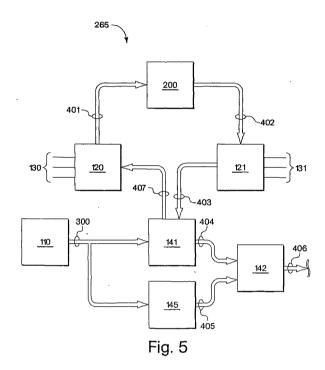

図5は、バイアス・キャンセル力をもつセンサ・システム 2 6 5 の例示的実施形態を示している。ある種の実施形態では、駆動発振器信号に起因するバイアスをキャンセルして、これにより検知したセンサ信号がよりうまく増幅され他の信号から弁別されるようにすることが有利である。図5に示したシステムは、単なる例示的実施形態であり、容量性アレイ走査システムに関して以下で説明するが、しかしこのシステムは、そのように限定されるものではなく、そのセンサは、前述したようにキャパシタ以外のセンサとすることもできる。

#### [0043]

発振器110は、先に述べた通り、発振器出力信号300を供給する。発振器出力信号3 00は、増幅器141を使って増幅して、増幅された入力信号407を発生する。増幅された入力信号407は、先に説明したように入力マルチプレクサ120に供給し、そして次に入力マルチプレクサ120は入力選択ライン130におけるデータに基づきセンサ入力信号401を供給する。

#### [0044]

図5は、先に説明した容量性アレイ100のようなセンサ・アレイ全体ではなく、単一のセンサ200を示している。しかし、理解されるべきであるが、1つ以上のセンサまたはこのようなセンサのアレイが、アレイ入力信号のような入力信号を受けるようにしたり、あるいは本実施形態では、入力マルチプレクサ120からのセンサ入力信号401を受けるようにしたりできる。

#### [0045]

前述のように、センサ200は、センサ入力信号401に基づき、また、力、圧力等の検知した刺激に対応してセンサ出力信号402を供給する。センサ出力信号402は、出力マルチプレクサ121が受け、そしてこのマルチプレクサは、容量性アレイ100(不図示)のようなセンサ・アレイ内の複数のセンサから特定のセンサ200を選択する。出力マルチプレクサ121は、出力選択ライン131にあるデータに基づき、センサ出力信号402を選択する。選択されたデータ403は、出力マルチプレクサ121から増幅器141に供給され、そしてこれは、前述のフィードバック・ループを形成することができる。増幅器141は、増幅された出力信号404を供給し、そしてこれは、通常、その大きさが増幅された選択された信号403に対応する。

#### [0046]

図5に示された実施形態においては、増幅された出力信号404は、振幅検出器に送るのではなくさらに処理される。ここで、発振器出力信号300の第2の分岐は、位相シフタ145が受け、そしてこのシフタは、位相シフトした信号405を供給する。増幅出力信号404と位相シフト信号405の双方は、積分器142に入力され、そしてこの積分器は、実質上、それら2つの信号404,405の和をとる。

# [0047]

積分器142は、信号404,405を、発振器の数サイクルにわたって積分するようにできる。積分器142は、時間積分した信号406を出力として供給する。積分器142は、増幅器と積分フィードバック容量を有する加算回路で構成することができる。積分器142の出力における記号は、この検知システム265が、容量性アレイ走査システムのようなより大きな検出システム全体の1部分のみを構成できることを示している。

# [ 0 0 4 8 ]

50

40

10

20

10

20

30

40

50

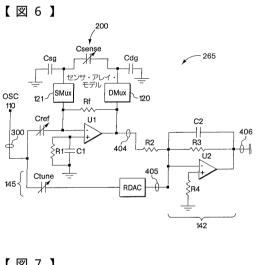

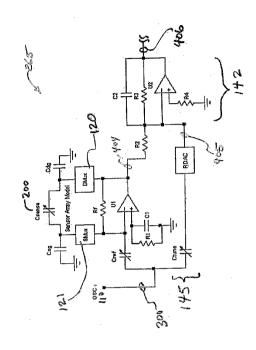

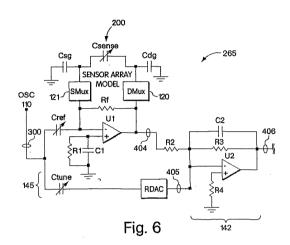

図6は、図5において上述したのと同様のセンサ・システム265のより詳細な例を示している。この実施形態では、電荷増幅器回路を開示しており、これは、可変容量センサCsense200を有し、これは、検知センサ200上に印加された圧力に応答して可変の容量を有する。正弦波発振器110は、発振器出力信号300を、センサ200と、電荷増幅器回路265の残りの部分へ供給する。発振器出力信号300は、基準キャパシタCrefを通り、そしてこれは検知センサ200へ駆動マルチプレクサ120(DMux)を介して供給される。次に、検知キャパシタ200は、刺激に対応するセンサ出力信号を選択マルチプレクサ121(SMux)へ供給する。増幅器U1は、前の図面における増幅器141として動作する。このため、検知キャパシタ200と増幅器U1との間のマルチプレクサ120、121を経るフィードバック・ループが作成される。

[0049]

バイアス・キャンセル回路は、バイアス・キャンセル用キャパシタCtuneおよびゲイン調節用キャパシタGrefの使用により提供する。このバイアス・キャンセル用キャパシタは、製造時に調節し、そして駆動用キャリア信号300のAC振幅をキャンセルまたは低減するように設定する。発振器信号300は、キャパシタCrefを含む分岐を通って増幅器U1の反転入力に至り、一方、キャパシタCtuneは、フィルタとして動作して、抵抗形デジタル・アナログ・コンバータ(RDAC)の出力における発振器信号300の位相をシフトさせる。このように、キャパシタCtuneおよびRDACは、図5のブロック145により上述したように位相シフタを形成する。

[0050]

増幅器U1の出力は、抵抗器R2を介して、増幅器U2、キャパシタC2および抵抗器R3が形成する積分器回路に供給される。CtuneおよびRDACの直列結合により供給される位相シフトとした信号はまた、増幅器U2の反転入力にも供給される。増幅器U2の非反転入力は、抵抗器R4を介してグランドに結合される。キャパシタC2と抵抗器R3は、増幅器U2の周りのフィードバック・インピーダンスを形成し、これにより、増幅器U2の入力における入力信号を積分する。図5のブロック142として前述したこの積分器回路はまた、加算回路と考えることもでき、そしてこの回路は、(a)増幅された出力404と(b)位相シフトされた発振器出力信号405の和をとる。

[0051]

ある種の面によれば、図6に提示した配置は、非線形センサ200の存在の下でシステムの応答を線形化する。上述のフィードバックを含むセンサ・ループは、この検知回路の出力を、刺激(例えば、圧力キャパシタ・ギャップ等)に対し線形に対応するようにし、従来のように、キャパシタ変化に対し反比例ではなく直接応答するセンサ化回路において提供される非線形関係ではない。このように、フィードバック・ループは、非線形トランスフォーマとして作用し、そしてこれは、センサ200の非線形の振る舞いを相殺して線形化された出力を発生する。

[0052]

ある種の実施形態においては、発振器110は、単一極性の励起ソースであり、これは、 1KHzから数MHzの範囲(例えば、50KHz~100KHz)内の周波数をもつ安 定化した正弦波波形を提供し、その周波数は、検知キャパシタ200の静止容量およびセ ンサ・レンジ、感度および線形性間のトレードオフのような他の設計考慮事項とに依存す る。

[ 0 0 5 3 ]

図6においてCsenseで表した容量性センサ200またはセンサ・アレイ100は、一般に、CsgおよびCdgとして表したグランドへの寄生容量も構成している。寄生容量Csgは、センサ・ラインからグランドへの寄生容量を表している。寄生キャパシタCdgは、駆動ラインとグランドとの間の寄生容量を表している。寄生容量を低減あるいは除去するために、センサ200、またはアイドル(駆動されていないあるいはサンプリングされていない)であるセンサ・アレイの1部分は、グランドに結合され、これにより寄生容量効果が非アイドルのセンサの測定値に影響を与えるのを防止する。ある種の面にお

20

30

40

50

いては、寄生容量のグランドへのこの分路は、システムのスループット、線形性および帯域幅を改善する。

[0054]

キャパシタCrefは、通常、Csenseの倍数に選択され、例えばCrefは、Csenseの値の3倍に等しい値とすることができる。キャパシタCrefのCsenseに対する比率に、発振器の励起振幅を乗算したものは、増幅器U1の出力の大きさを決める。したがって、Csenseを増加させるにつれ、増幅器U1の出力は、検知キャパシタCsenseの設計により決まる感度にて、減少する。

[0055]

他の設計考慮事項は、増幅器U1の特性の性質を決め、これは、その適当なゲイン帯域幅に対し選択することができ、また位相遅れ効果を最小限にする。

さらにまた、容量性アレイ100との間での駆動ラインおよび検知ラインは、個々にシールドすることができる。このようにして、それら個々のライン間の相互容量効果(cross-capacitance effects)が、測定した容量に対し、アレイ100との間で走るケーブル・バンドルの捻りあるいは曲げのような影響に起因してインパクトを与えるのを防ぐ。

[0056]

センサ・エレメント 2 0 0 の近くに任意のチューニング可能なフィルタを物理的に配置して、温度変化のような環境影響に対する同相除去を提供することは、ある種の面においては利益がある。

[0057]

前述のように、積分器または加算増幅器U2においてキャパシタCtuneを通しての位相シフトした信号を増幅器U1の出力と組み合わせると、このセンサの感度を性のものとする、あるいは言い換えればその極性を反転し、そしてバイアス・キャリアセルを可能にする。キャパシタCtuneは、任意の必要な位相遅れ調節を提供する一方で、RDACは、デジタル・ポテンショメータとして働いて各センサ・エレメント200に対する精密なバイアス・トリミングを可能にする。RDACの値は、加算増幅器U2の出力における測定値に基づき、センサ200とその静止容量状態とで調節する。このような調節を使用することによって、同様の幾何学形状および電極表面領域をもつ各センサ・エレメント200のバイアスおよびゲインの双方に対し十分なトリムを提供する。

[0058]

本発明のある種の面によれば、上述のセンサ回路調節は、校正プロセスを簡単化することができる。校正は通常、反復的プロセスで実行し、そして時間がかかるものである。本設計はまた、校正手順と校正手順との間で必要なインターバルを減少させることができる。

[0059]

抵抗器 R f は、フィードバック抵抗器であり、そしてある種の実施形態においては、回路に対し安定性を提供する。 R f もまた、この検知回路の感度および線形性を最適化するのに選択でき、そしてある種の実施形態においては、セトリングタイムを改善して大きなセンサ・アレイのスループットを増大させることができる。

[0060]

先に述べたように、発振器110は、種々の発振器信号300を提供することができる。 このような信号は、励起波形として使用することができ、これは、正弦波だけでなく、非 正弦波波形とすることができる。また、二重極性励起は、その使用が特定の回路設計に対 し有利な場合には可能である。

[0061]

ある代替の実施形態は、抵抗器 R 1 , R 4 およびキャパシタ C 1 および C 2 のいずれかあるいはそのすべての削除を可能にする。

図6の検知回路265の出力は、ある種の実施形態においては、振幅検出を実行する前に、整流器のようなACまたはDC変換回路の入力へ、また第2段の増幅回路へ供給する。

[0062]

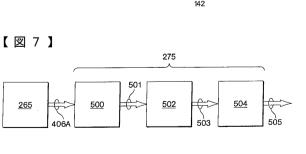

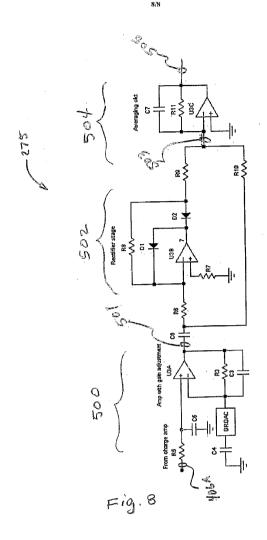

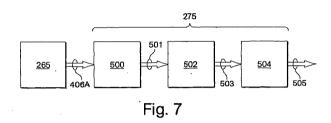

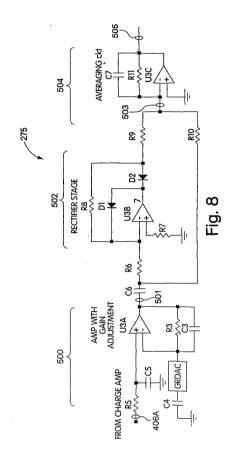

図7は、第2段回路275の例示的実施形態を示しており、これは、先に述べた検知回路

265の下流で用いることができる。検知回路265は、検知回路出力信号406Aを供給し、これは、積分された信号406と同じものとすることができる。この信号406Aは、測定された刺激を表す検出エレメント200からの情報、並びに、任意の残りのバイアス、ノイズ、および検知回路265から供給される他の信号人工物を含んでいる。検知回路出力信号406Aは、第2段増幅器500に供給し、そしてこの増幅器は、所望の測定値に対応するその信号を増幅する。ある種の実施形態においては、この信号406Aは、ほぼ200mVの振幅でほぼ50~100KHzの周波数をもつAC正弦波信号で構成されたものとすることができる。

[0063]

第2段増幅器500からの出力信号501は、整流器502に供給する。整流器502は、任意の適当な方法で構成し、そしてAC信号をDC信号に変換する。整流された信号503は、第2段積分器504に供給し、そしてこの積分器は、信号503を数サイクルの時間にわたって積分する。ある種の面によれば、ローパスフィルタ段ではなく第2段積分器504を使用することにより、改善した応答時間を提供し、またローパスフィルタ回路においてはそうであったトランジェントが減衰するまで待機する必要性を回避できる。積分器504における積分は、ある種の実施形態においては、およそ10サイクルに渡って実行される。

[0064]

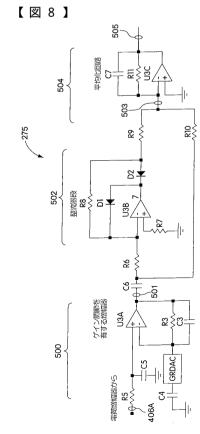

図8は、図7に記述したのと同様の1実施形態の第2段増幅回路275を示している。検知回路出力信号406Aは、回路265のような検知回路から受ける。信号406Aは、電荷増幅器回路からの出力を表し、これは、発振器信号300と実質上同じ周波数で発振している。信号406Aは、R5から受け、そしてこれの出力は、フィルタとして作用するキャパシタC5を通してグランドに結合される。

[0065]

第 2 段調節可能ゲイン増幅器 U 3 A は、信号 4 0 6 A から非反転入力を受ける。増幅器 U 3 A は、励起周波数にて適当な中間バンド・ゲインを提供する一方で、非常に低い周波数でおよそユニティ・ゲインを維持するように構成される。この中間バンド・ゲインは、ゲイン抵抗型デジタル・アナログ・コンバータ(G R D A C )を介して調節可能である。キャパシタ C 4 は、確実に、 D C 周波数近辺のゲインを低くあるいはほぼユニティとする。

[0066]

第2段増幅器回路500に続き、信号501は、整流器段502に供給される。整流器段502は、増幅器U3Bで構成され、そして、低い入力振幅レベルに対する整流を含む精密な全波整流を、特にその励起周波数にて実行する。

[0067]

整流器段502の出力は、ライン503で平均化回路504に送られる。平均化回路504は、増幅器U3Cで構成され、そして平均化回路出力505を出力し、これは、実質上、センサ200から送られた刺激に対応するDC信号である。図8の回路全体は、図6に示した電荷増幅器回路265からの振幅変調された信号のAC-DC変換を実行するための例示のシステムを表している。上述の回路は、それらの機能を、多くの既存の同期位相復調回路におけるのと同じスイッチング・エレメントを必要とせずに実行する。

[0068]

尚、整流器段502のダイオードD1とD2の極性を反転させることにより、整流器段502を、負および正の入力に対するゲインを提供するように構成でき、またR10経路を除去することにより半波整流を提供することができる。

[0069]

第2段増幅回路275の出力は、振幅が4VACで変調が2VのAC信号505とすることができ、これは、測定した信号を反映ししかも50~100KHzの周波数を有する。このような信号は、センサ・エレメント200からの可変であるが実質上DCの変調信号の測定のためのより良好なベースを提供する。

[0070]

50

40

20

10

20

30

40

50

本発明のある種の実施形態は、上記の種々の面のうちの1つ以上を、有機体に結合していて有機体の物理的パラメータまたは特性を検出するシステムに組み込む。時系列の生物学的データの収集は、そのような実施形態のうちの1つの例である。例えば、上述の回路および方法は、ヒトまたは動物の患者における生物学的データを収集する非侵襲性デバイスあるいは最小侵襲性のデバイスを含む、カテーテルまたは他のデバイスと共に使用することができる。穴(orifice)または腔(cavity)内で測定される時間および空間の一方または双方における圧力プロファイルは、格納、処理または分析のため、ユーザまたはマシンに対し提示するために収集することができる。これは、何等かの医学的状態の診断のためのベースを形成したり、あるいは、有機体の何等かの他の状態に対する前兆として使用したりできる。

[0071]

1 実施形態においては、線状フォーム・ファクタ(linear form factor)に実質上配列された一連のセンサは、食道のような体腔内に配置され、そしてこの腔内の圧力を時間の関数として測定する。これら食道の圧力は、次に、グラフィック・ディスプレイ上に図形で表示することができ、これにより、せきあるいは飲み込みのような動作の生物学的シーケンスを示す。

[0072]

本発明のさらに別の形態では、対象とする大きな領域の高い分解能の測定を得るために、上述のシステムおよび方法の使用を可能にする。本発明のある種の実施形態においては、いくつかのセンサ・アレイ・グリッドを利用し、その各々が、上述のように、それ自身のセンサ駆動 / サンプリング電子回路を有することによって、同時あるいは順次の測定を実行する。多重化電子回路をある種の実施形態において使用することにより、多数のセンサ・アレイからのデータを収集する。これら実施形態は、ある種の点で、上述のコンセプトのスケーラブルのあるいは並列の実現例と考えることができる。

[0073]

1 例として、対象とするある大きな領域を、刺激例えば圧力に関するデータを収集するるセンサで覆う場合について考える。この場合、センサ・エレメントの数は、必要とこのが場合、センサ・面積とに依存する。このが変化である。このが変化でするで、大きな数のをでは、大きな数のセンサには駆動ができな数のセンサには対していまったが伴う。大きな数のセンサには対していまったが伴う。大きな数のセンサには対していまったがは、カートを遅くしてサイクルがある。カードである。カードである。カードを遅くしてリング・レートを遅くしてリング・レートを遅くとがであるに対けながでをは、対象とする領域を、対り、カートである。これらサンプリング・なりはに分解にでサンプリングを対していまったがである。これらサブ領域の各々は、サイルのセンサ・アレイで覆を増加させる。これらサブ領域の各々は、カートである。これらサブ領域の各々はカートである。これらサブ領域の各々はカートである。これらサブ領域の各々はカートである。これらサブ領域の各々はカートである。これらサブ領域の各々はカートである。アプレクサのような回路で読み取ることができる。

[0074]

認識されるように、この技術は、反復的形式で使用することができ、これにより、検知システム全体を入れ子にしたりあるいはスケーリング・アップあるいはスケーリング・ダウンして、ニーズに依存して、ほとんど任意の面積または分解能もしくはサンプリング・レートを得ることができるようにする。すなわち、ある種の形態では、時間的性能または空間的性能は、追加のハードウェアまたは処理センサ電子回路という犠牲を払って得ることもできる。

[0075]

以上、本発明の少なくとも 1 つの実施形態の種々の面について説明してきたが、理解されるように、種々の変更、修正、改良が、当業者には生じ得るものである。このような変更、修正、改良は、本開示の 1 部分を成すことを意図しており、したがって本発明の要旨お

よび範囲内に入るものである。したがって、本記述および図面は、例としてのみ与えたものである。

【図面の簡単な説明】

[0076]

【図1】図1は、いくつかの行列の導電性ストリップをもつ容量性センサ・アレイの概観を示す。

【図2】図2は、サイズ(d)の誘電体ギャップによって分離した2つの導電性ストリップの重なりにより形成されたセンサ・エレメントの概観を示す。

【図3】図3は、センサ・アレイを駆動しサンプリングし振幅検出を行うためため例示のシステムの概略図を示す。

【図4】図4は、フィードバック・ループを含む、センサ・アレイを駆動しサンプリングするための例示のシステムの概略図を示す。

【図 5 】図 5 は、バイアス・キャンセルを含む、センサ・アレイを駆動しサンプリングするための例示のシステムの概略図を示す。

【図 6 】図 6 は、フィードバック・ループとバイアス・キャンセル能力を含む、センサ・アレイを駆動しサンプリングする例示の回路を示す。

【図7】図7は、センサ・アレイと共に使用できる、例示の第2段増幅および整流装置の概略図を示す。

【図8】図8は、図7の概略図による例示の回路を示す。

# 【国際公開パンフレット】

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization International Bureau

#

# (43) International Publication Date 1 May 2003 (01.05.2003)

PCT

#### (10) International Publication Number WO 03/036612 A1

| (51) | International | Patent | Classification?: | • | G09G |

|------|---------------|--------|------------------|---|------|

|      |               |        |                  |   |      |

(21) International Application Number: PCT/US02/34135

(25) Filing Language:

(26) Publication Language:

English

(30) Priority Data: 60/347.599

60/343,714

24 October 2001 (24.10.2001) US 24 October 2001 (24.10.2001) US

(71) Applicant (for all designated States except US): PRES-SURE PROFILE SYSTEMS, INC. [US/US]; 5757 Cen-tury Boulevard, Suite 700, Los Angeles, CA 90045 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): PEINE, William [US/US]: 163 Locust Street, Holliston, MA 01746 (US).

PRATICO, Robert [US/US]: 27515 Prectown Lane,

Agoura Hills, CA 91301 (US). SON, Jae, S. [US/US]; Apartment D101, 6542 Ocean Crest Drive, Rancho Palos Verdes, CA 90275 (US).

(22) International Filing Date: 24 October 2002 (24.10.2002) (74) Agent: ENGELSON, Gary, S.; Wolf, Greenfield & Sacks, P.C., 600 Atlantic Avenue, Boston, MA 02210 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GB, GE, GH, GM, HR, HU, DI, H., BN, SP, KE, KG, FK, RK, ZL, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZW.

(84) Designated States (regional): ARIPO patent (GII, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR, OAPT patent (BF, BL, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

[Continued on next page]

(54) Title: ARRAY SENSOR ELECTRONICS

(57) Abstract: Circuits and methods for detecting and amplifying sensor and sensor array (102, 104) output signals are presented. According to some aspects, a nonlinear feedback loop containing a sensor element provides a nonlinear transformation that compensates for a corresponding nonlinear response of the sensor element thereby providing a linearized final output signals. In other aspects, idle sensors are coupled to a reference on non-idd sensor elements. Other aspects include sensor and amplification circuits which operate without traditional filtering or switching elements, such that a higher throughput is achieved and no settling time is required due to traditional transients, thus allowing for faster seanning of larger sensor arrays. Some embodiments of the present invention are directed to variable gap capacitive sensor arrays and the signal processing electronics.

# WO 03/036612 A1

Published:

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

WO 03/036612 PCT/US02/34135

#### ARRAY SENSOR ELECTRONICS

#### RELATED APPLICATIONS

This application claims priority under 35 U.S.C. § 119(e) to co-pending U.S. Provisional Patent Application Serial No. 60/347,599, entitled "CAPACITIVE ARRAY SENSOR ELECTRONICS," filed on October 24, 2001. This application further relates to co-pending U.S. Provisional Patent Application Serial No. 60/343,714, entitled "TIME SPATIAL VISUALIZATION OF LINEAR ARRAY DATA," filed on October 24, 2001. This application also relates to a co-pending U.S. Patent Application entitled "VISUALIZATION OF VALUES OF A PHYSICAL PROPERTY DETECTED IN AN ORGANISM OVER TIME," filed on even date herewith under attorney docket number P00660.70004.US. Each of the above-cited applications is hereby incorporated by reference in its entirety.

#### TECHNICAL FIELD

The present application relates to sensor systems such as capacitive array sensors. More particularly, the present application relates to circuits and systems for capturing, amplifying and processing signals received from sensors and sensor arrays.

#### BACKGROUND

Sensors are devices that respond to a stimulus and produce a signal indicative of the stimulus' magnitude or other characteristic related to the stimulus. The stimulus may be any physical quantity or parameter which can affect a sensor and is usually a measurable parameter or effect. An array of sensors is a collection of individual sensors that are positioned at discrete locations and are related to one another in at least some aspects.

Sensor arrays are used in applications such as imaging, and generally involve a plurality of individual sensors placed in relation to one another such that an effectively larger sensor is formed by the array of sensors. That is, when placing sensors at a plurality of discrete locations over a region of interest it is possible to make some determination or estimate of the stimulus over the entire region of interest.

Extrapolation or interpolation can provide an estimate of the magnitude of the stimulus

PCT/US02/34135

-2-

at a spot which does not itself contain a discrete sensor. Furthermore, aggregate measures of the stimulus over the entire region of interest or smaller regions within the region of interest may be obtained by averaging or other operations performed on signals derived from individual sensors.

Applications in which such sensor arrays are useful include touch pads and distributed sensors that provide an indication of the location and magnitude of a force or a pressure applied to a region of interest.

One type of sensor array is a capacitive sensor array. This array employs a number of discrete capacitors distributed over a region of the array which may be arranged in a pattern forming a grid. A grid of sensors may comprise a plurality of capacitive sensors which may be individually addressable or addressable in groups or in their entirety. Addressing specific sensors may be accomplished using multiplexers coupled to the sensor array according to data or select signals on multiplexer select lines to determine the individual sensors to be driven or sampled. By driving a sensor it is meant the process of generally exciting the sensor or energizing the sensor so as to produce a measurement of the stimulus at the sensor. By sampling a sensor it is meant receiving an output signal from the sensor to read or detect the sensor response to the stimulus. Thus, it is possible to selectively measure a signal from a given capacitive sensor element located at a particular column and row of the capacitive array. Multiplexers may be used to determine the particular row and column from which a measurement is desired.

Capacitive array sensors have been constructed of rows and columns of conductive strips separated by a dielectric material. Figure 1 illustrates a capacitive array 100 having conductive strips arranged along rows 102 and columns 104. The rows 102 and columns 104 of the capacitive array 100 may be separated by a flexible deformable material such as a silicone gel. The silicone gel (not shown) will deform in response to pressure applied to a surface of the capacitive array 100. The deformation of the silicone gel or other flexible substance can cause the rows 102 and columns 104 of the capacitive array 100 to become nearer or more distant to one another. Gap distance (d) is a factor which determines the capacitance of the capacitors 200 formed by an intersection of the rows 102 and columns 104 of the capacitive array 100. If the rows 102 and columns 104 of the capacitive array 100 are coupled to electrical

PCT/US02/34135

- 3 -

connections and to an external circuit, the capacitance of each of the capacitors 200 formed by the intersection of the rows 102 and columns 104 can be measured individually.

A sensor array can be driven and sampled, one sensor at a time or in groups, or in its entirety. By scanning the capacitive array 100 to obtain a signal or measurement from each of its individual elements 200, it is possible to form a real-time picture of the pressure applied to the capacitive array 100.

Figure 2 illustrates a single capacitive array element 200. The element 200 is formed by an intersection of a row 102 and a column 104 of the capacitive array 100. The figure illustrates a distance or gap (d) that separates the row 102 and column 104 conductive strips. The capacitance of the capacitor 200 is generally proportional to the area formed by the intersection of the row 102 and column 104 divided by the distance d. Hence, changes in the distance d result in changes in the value of the capacitor 200. The relationship between the capacitance of the capacitor 200 and the stimulus, e.g., applied pressure, may be nonlinear for a variety of reasons. These reasons include the deformation response of the flexible deformable material, e.g., the silicone gel, as well as other physical and electrical responses of the variable gap capacitance element 200.

For large arrays, technical challenges arise in making fast measurements or scans of the entire sensor array. For example, a sampling circuit such as a multiplexer that samples a selected row and column on which to perform a measurement would have to cycle through all rows and all columns (all elements of the array) at a rate sufficient to provide the measurements as required by the specific application.

Nonlinear responses in the signals derived from the individual capacitors and the stimulus, e.g., applied pressure, complicate the design of an overall sensor circuit. Furthermore, the measured signal is typically small compared to the driving signal which drives the capacitive array. This results in a poor signal-to-noise ratio when attempting to derive a useful modulation signal reflecting the quantity being measured. This is because noise becomes amplified as well as the signal being measured when using simple signal amplification.

Traditional sensor circuits employ filters and switches that slow acquisition times by causing transients which need to decay between acquiring measurements from the various elements of an array. For example, in scanning a sensor array, a switch

PCT/US02/34135

- 4.

switches between the individual sensors of a traditional array, causing a transient signal to occur. Not only do transients slow the acquisition of a complete sensor array scan, but they can affect the quality of a measurement of a stimulus by introducing noise into sensed signals.

Furthermore, conventional sensor arrays contain considerable parasitic capacitances between sensor elements and other parts of the circuit, such as ground. These parasitic capacitances can contaminate sensed signals with noise and extraneous signal components and can require extra filtering circuitry and processing time to compensate for the parasitic capacitance.

#### SUMMARY

Aspects of one embodiment of the present invention are directed to a sensor system, comprising a sensor array having a plurality of sensor elements; at least one sensor element of the sensor array, having addressable connections designating the sensor element, that senses a stimulus; and an amplifier, disposed in a feedback arrangement around the sensor element, the amplifier receiving an input signal corresponding to an output of the sensor element and providing an output signal that drives the sensor element.

Another embodiment comprises aspects directed to a method for measuring a stimulus on a sensor array, comprising sensing the stimulus using at least one sensor element of the sensor array; generating a sensor element output signal corresponding to the sensed stimulus; amplifying the sensor element output signal to generate an amplified signal representative of the physical property; and feeding back the amplified signal to drive the sensor element.

Still another embodiment comprises aspects directed to a method for linearizing a non-linear sensor response, comprising sensing a stimulus using a sensor element; generating a sensor output signal corresponding to the stimulus; feeding back the sensor output signal to an input of the sensor through a non-linear transformer feedback loop corresponding to the non-linear sensor response.

Another embodiment of the invention comprises aspects directed to a method for reducing parasitic capacitance in a capacitive sensor array, comprising selectively

PCT/US02/34135

- 5 -

coupling at least one sensor element in the sensor array to a common potential during a time period in which the sensor element is idle.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In the drawings, each similar component that is illustrated in various figures is represented by a like numeral, although this does not necessarily signify that the components are identical. For purposes of clarity, not every component may be labeled in every drawing. In the drawings:

Figure 1 illustrates an overview of a capacitive sensor array having several rows and columns of conducting strips;

Figure 2 illustrates an overview of a sensor element formed by the overlap of two conducting strips separated by a dielectric gap of size (d);

Figure 3 illustrates a schematic representation of an exemplary system for driving and sampling a sensor array and amplitude detection;

Figure 4 illustrates a schematic representation of an exemplary system for driving and sampling a sensor array, including a feedback loop;

Figure 5 illustrates a schematic representation of an exemplary system for driving and sampling a sensor array, including bias cancellation;

Figure 6 illustrates an exemplary circuit for driving and sampling a sensor array, including a feedback loop and bias cancellation capability;

Figure 7 illustrates a schematic representation of an exemplary second stage amplification and rectification apparatus which can be used with sensor arrays; and

Figure 8 illustrates an exemplary circuit according to the schematic representation of Figure 7.

#### DETAILED DESCRIPTION

The present description describes various aspects of preferred embodiments of the invention. Some aspects have been described in other co-pending applications. Specifically, this application claims priority under 35 U.S.C. § 119(e) to co-pending U.S. Provisional Patent Application Serial No. 60/347,599, entitled "CAPACITIVE ARRAY SENSOR ELECTRONICS," filed on October 24, 2001. This application further relates to co-pending U.S. Provisional Patent Application Serial No.

PCT/US02/34135

-6-

60/343,714, entitled "TIME SPATIAL VISUALIZATION OF LINEAR ARRAY DATA," filed on October 24, 2001. This application also relates to a co-pending U.S. Patent Application entitled "VISUALIZATION OF VALUES OF A PHYSICAL PROPERTY DETECTED IN AN ORGANISM OVER TIME," filed on even date herewith under attorney docket number P00660.70004.US. Each of the above-cited applications is hereby incorporated by reference in its entirety.

The present invention is not limited in its application to the details of construction and the arrangement of components set forth in the following detailed description of the preferred embodiment and drawings. Rather, the invention encompasses other embodiments and may be practiced and carried out in various ways. Also, the terminology used herein is for the purpose of description and should not be regarded as limiting when used to describe aspects and embodiments of the invention. The use of "including," "comprising," or "having," "containing," etc., and variations thereof are meant to be open-ended and encompass at least the items listed thereafter.

Figure 3 illustrates aspects of a capacitive array scanning system 250 used to drive and sample a capacitive array 100. An oscillator 110 provides an oscillator signal 300 to an input multiplexer (MUX) 120 which selects from the elements of capacitive array 100 one or more elements to be driven by at least the oscillator signal 300. Selection of the one or more elements to be driven is made using data on the input select lines 130. By proper identification of the individual or group of elements to be driven, a voltage or current may be supplied to selected sensor elements 200 as described previously. Oscillator signal 300 may be one of a plurality of signals driving elements 200.

Array input signal 302 provides a driving signal which is delivered to selected sensor elements 200. Once excited or driven by the array input signal 302, the capacitive array provides an array output signal 304. An output multiplexer 121 receives the array output signal 304 and, depending on the data provided to output select lines 131, the output multiplexer 121 provides a selected signal 306. Again, the selected signal 306 may comprise one or more selected samples from the capacitive array 100.

In some embodiments, the selected signal 306 be amplified by an amplifier 140. The amplifier 140 may be of any type, including analog or digital types, that provides

PCT/US02/34135

-7-

an amplified signal 308. According to some aspects, amplification of the selected signal 306 improves resolution and accuracy of the measurement of the stimulus. An amplifier 140 may provide any gain, including gains greater than or less than unity and unity gains. The amplified signal 308 is therefore not constrained to be a signal having an amplitude greater than the selected signal 306.

The amplified signal 308 is detected by an amplitude detector 150, which is typically matched to the range of expected amplitudes provided in the amplified signal 308. Note that some embodiments may employ transconductance amplifiers, energy converters, or other elements that convert one type of signal into another. For example, an electrical signal such as a voltage may be converted into a corresponding optical signal.

The amplitude detector 150 may be any suitable amplitude detector that may detect the size, strength or amplitude of a signal. For example, the amplitude detector 150 may comprise a voltage-measuring circuit or a current-measuring circuit or a frequency measuring circuit, together described herein as amplitude detectors for the sake of simplicity. It should be appreciated that the amplifier 140 may amplify any type of characteristic of the selected signal 306 and that the amplified signal 308 merely indicates that characteristic is enhanced to generally make it simpler to read or measure the characteristic. As mentioned, the amplitude of an alternating current (AC) voltage signal may be a convenient characteristic to amplify and measure using the amplitude detector 150, however, the present invention is not so limited.

The amplitude detector 150 provides a detector output signal 310 corresponding to the amplified signal and in turn corresponding to the selected signal obtained from the element or elements of the capacitive array 100.

It is to be appreciated that Figure 3 is merely one schematic embodiment of a capacitive array scanning system, and that various configurations and equivalent circuits may be constructed accordingly. Other auxiliary elements and circuit components, not described herein, may be used in various applications and embodiments, depending on the need at hand. For example, filters such as high-pass filters, band-pass filters and low-pass filters may reduce unwanted noise or provide other signal conditioning functions to the overall scanning system 250. Furthermore, signal processing techniques, implemented in hardware and/or software may be used at

PCT/US02/34135

- 8

one or more positions in the scanning system 250 to add or remove spectral characteristics or other features to or/from the various signals described above.

Figure 4 illustrates an embodiment showing aspects of the present invention used in a capacitive array scanning system 255. Again, the scanning system is not limited in applicability to the capacitive array sensors described herein, but is more generally applicable to other types of sensors as well. The scanning system 255 comprises a feedback loop 320, which in some embodiments provides a linearizing function, as will be described below.

An oscillator 110 provides an oscillator signal 300 to amplifier 141. The amplifier 141 amplifies the oscillator signal 300 and provides an amplified input signal to input multiplexer 120, sometimes referred to as a driving multiplexer (DMUX). The input multiplexer 120 receives the amplified input signal 301 as well as data on input select lines 130, as described earlier. The array input signal 303 is provided by the input multiplexer 120 to selectively drive array element members 200 (not shown) of the capacitive array 100. The capacitive array 100 is driven or excited selectively by the array input signal 303, as was described above. An array output signal 305 is provided from the capacitive array 100 to an output multiplexer 121, sometimes referred to as a sampling multiplexer (SMUX). The output multiplexer 121 samples the selected array elements according to the data on output sampling lines 131.

The output multiplexer 121 provides a selected signal 307 back to the amplifier 141. In this way, the amplifier 141, the capacitive array 100 and other elements, are arranged in a feedback loop 320 by which the amplified input signal 301 and the selected signal 307 act to return a portion of the capacitive array's output to its input. In the embodiment of Figure 4, input and output multiplexers, 120 and 121 respectively, are the elements to which and from which the feedback loop 320 couples the amplifier 141 and the capacitive array 100.

The selected signal 307, once provided to amplifier 141 is also amplified and provided as an amplified output signal 309 to amplitude detector 150. In some embodiments, signals 301 and 309 are the same or have the same value. The amplitude detector 150 provides a detector output signal 311, similar to that which was discussed with regard to Figure 3. Again, the exact embodiment disclosed in Figure 4 is not

PCT/US02/34135

-9-

limiting, but may be adapted and substituted with one or more elements or auxiliary circuits, filters, amplifiers, etc., as called for by the application at hand.

It is also to be appreciated that the arrangement shown in the present embodiment does not depict a physical layout of the elements of the scanning system. For instance, some elements of the scanning system 255 may be implemented on remote circuits, as opposed to being implemented on the same circuit. Also, the entire scanning system 255 may be implemented on a microchip or other integrated circuit that performs the scanning system's function. Furthermore, various functions of the scanning system 255 may be carried out in software or in firmware or in any combination of hardware and software suitable. Examples include digital signal processing (DSP) hardware and/or software to perform various functions, e.g. filtering and amplification and application-specific integrated circuits (ASICs).

The oscillator 110 provides an output voltage signal such as an AC waveform. In some embodiments, the oscillator output signal 300 substantially comprises a single frequency sinusoid. The oscillator 110 may be free-running or may be used in a burst mode depending on the application. According to some aspects of the invention, the amplitude and/or frequency of the oscillator output signal 300 may be altered to improve measurement quality or scan rate or another operating parameter of the scanning system 255. Furthermore, the oscillator 110 may be replaced by another suitable component that can provide a periodic driving signal in a steady or pulsed or programmed mode. One example may be to replace the oscillator 110 with a microcontroller or other digital processing control unit that provides a signal substantially equivalent to that described as the oscillator output signal. The oscillator 110 may be controlled by a microprocessor 400 that supplies a control signal 411.

The input multiplexer 120 and the output multiplexer 121 may be of substantially similar design in some aspects of the present invention. According to some embodiments, the multiplexers 120, 121 select a single row 102 and column 104 from the capacitive array 100. This selection designates a single element 200 of the array 100. However, the input and output multiplexers 120, 121 may also be used to select multiple rows and columns simultaneously.

Multiplexer designs having a fast settling time are preferred in some embodiments because they allow for fast switching between sensor elements at a high

PCT/US02/34135

- 10 -

sampling rate, thus improving the overall bandwidth for the scanning system 255.

The data on the input select lines 130 and the output select lines 131 of the multiplexers 120 and 121 respectively, may be provided in a number of ways. For example, the selection lines 130 and 131 may be set by a microcontroller or digital signal processing unit 400 and may also be set to increment automatically as would be done with a finite state machine. Additionally, separate amplifiers may be included in either or both of the multiplexers 120 and 121 at any of the inputs and outputs of said multiplexers. Also, an amplifier may be constructed as part of the multiplexing scheme used by the multiplexers 120 and 121.

According to some aspects of the present invention, placing the amplifier 141 in the feedback loop 320 comprising the capacitive array 100 and the multiplexers 120 and 121, allows for a higher gain and thus a higher sensitivity in the overall scanning system 255.

Amplifiers 140 and/or 141 may be implemented as described above and can also include provisions for adjusting the gain and offset of said amplifiers. Said gain and offset of amplifiers 140 and/or 141 may be prescribed on an element-to-element basis or as a single setting suitable for all elements. That is, the amplification gain or scheme used for each individual sensor element may be individually tailored to that element, or the gain may be held constant for the entire array 100. An approach combining the element-to-element setting and the single setting for all elements may be used as appropriate. A microcontroller or digital signal processing unit 400 may control said offset and gain corrections for best overall results using control signal 412.

Figure 4 illustrates a microcontroller or digital signal processing unit 400 which provides control signals 411 and 412 to the oscillator 110 and to the amplifier 141, respectively. The microcontroller 400 may be implemented in hardware or in software or in a combination of hardware and software, including a DSP component, as best suits the application at hand.

The amplitude detector 150 samples the selected signal 307 at a sampling rate which is typically greater than the array scan rate. According to one embodiment, if a 10 by 10 array is scanned at 100Hz, then the scan rate is 10kHz. In this embodiment, the amplitude detector 150 would complete individual measurements at a rate greater than 10kHz.

PCT/US02/34135

- 11 -

According to some embodiments of the present invention, the amplitude detector 150 is implemented using a rectifier that rectifies the output of the output multiplexer 121, thereby acting as a nonlinear transformer. The nonlinear transformation achieved thereby may be subsequently augmented by integrating the resulting transformer output signal over an integer number of periods. In one embodiment the integration is carried out over 10 cycles.

The nonlinear transformation mentioned above may comprise a function that creates a DC component in the signal proportional to the amplitude of the sensed signal 305 or the selected signal 307. While not recited herein for purposes of limitation, examples of such nonlinear transformation include full-wave or half-wave rectification, phase-corrected multiplication with the original driving AC signal, as well as multiplying the output signal with itself to obtain the output signal squared. The amplitude detector 150 may further comprise a root-mean-square (RMS) measuring circuit, a peak detector circuit an envelope detector circuit, or an amplitude modulation circuit and a low-pass filter circuit. Amplitude detection could also be accomplished in some embodiments by sampling the AC waveform using an analog to digital (A/D) converter and using a digital signal processor or microcontroller to compute the measured signal amplitude from the sampled data. As mentioned above, both digital and analog methods may be used for amplitude detection.

Figure 5 illustrates an exemplary embodiment of a sensor system 265 having a bias-canceling capability. In some embodiments it is advantageous to cancel a bias due to the driving oscillator signal so that a sensed sensor signal may be better amplified and discriminated from other signals. The system shown in Figure 5 is only an illustrative embodiment, and will be described below with respect to a capacitive array scanning system, however the system is not so limited and the sensor may be a sensor other than a capacitor, as described previously.

An oscillator 110 provides an oscillator signal 300, as mentioned earlier. The oscillator signal 300 is amplified using amplifier 141 to produce an amplified input signal 407. The amplified input signal 407 is provided to input multiplexer 120 as previously described and the input multiplexer 120 subsequently provides a sensor input signal 401 based on data at input select lines 130.

PCT/US02/34135

- 12 -

Figure 5 illustrates a single sensor 200 rather than an entire sensor array such as a capacitive array 100 discussed earlier. However, it should be understood that one or more sensors or an array of such sensors may receive an input signal such as an array input signal or, in the present embodiment, a sensor input signal 401 from the input multiplexer 120.

As discussed previously, sensor 200 will provide a sensor output signal 402 based on the sensor input signal 401 and corresponding to a sensed stimulus, such as force, pressure, etc. The sensor output signal 402 is received by an output multiplexer 121 which selects the particular sensor 200 from among a plurality of sensors in a sensor array such as a capacitive sensor array 100 (not shown). The output multiplexer 121 selects the sensor output signal 402 on the basis of data presented on output select lines 131. The selected data 403 is provided from the output multiplexer 121 to the amplifier 141 and may form a feedback loop as previously described. The amplifier 141 provides an amplified output signal 404 which typically corresponds to the selected signal 403 and being amplified in its magnitude.

In the embodiment shown if Figure 5, the amplified output signal 404 is further processed rather than merely being delivered to an amplitude detector. Here, a second branch of the oscillator signal 300 is received by a phase-shifter 145 which provides a phase-shifted signal 405. Both the amplified output signal 404 and the phase-shifted signal 405 are input to an integrator 142 that substantially sums the two signals 404 and 405.

The integrator 142 may integrate the signals 404 and 405 over several cycles of the oscillator. The integrator 142 provides a time-integrated signal 406 as an output. The integrator 142 may comprise a summing circuit having an amplifier and an integrating feedback capacitance. The symbol at the output of the integrator 142 indicates that the sensing system 265 may comprise only a portion of a larger overall sensing system such as a capacitive array scanning system.

Figure 6 illustrates a more detailed example of a sensor system 265 similar to that described above in Figure 5. In this embodiment, a charge amplifier circuit is disclosed having a variable capacitance sensor Csense 200 which has a variable capacitance in response to applied pressure on the sensing capacitor 200. A sine wave oscillator 110 provides an oscillator signal 300 to the sensor 200 and to the rest of the

PCT/US02/34135

- 13 -

charge amplifier circuit 265. The oscillator signal 300 passes through a reference capacitor Cref and is provided to the sensing capacitor 200 through a drive multiplexer 120 (DMux). The sensing capacitor 200 then provides a sensor output signal corresponding to the stimulus to the select multiplexer 121 (SMux). Amplifier U1 operates as amplifier 141 in the previous figures. Thus, a feedback loop between the sensing capacitor 200 and amplifier U1 going through multiplexers 120 and 121 is created

A bias cancellation circuit is provided by use of bias-canceling capacitor Ctune and gain-adjusting capacitor Gref. The bias-canceling capacitor is adjusted at the time of manufacture and is set in a way such as to cancel or reduce the AC amplitude of the driving carrier signal 300. Oscillator signal 300 passes through the branch containing capacitor Cref to the inverting input of amplifier U1, while capacitor Ctune operates as a filter to shift the phase of the oscillator signal 300 at the output of the resistive digital to analog converter (RDAC). In this way capacitor Ctune and RDAC form a phase shifter as was described by block 145 in Figure 5 above.

The output of amplifier U1 is provided through resistor R2 to an integrator circuit formed by amplifier U2, capacitor C2 and resistor R3. The phase-shifted signal provided by the series combination of Ctune and RDAC is also provided to the inverting input of amplifier U2. The non-inverting input of amplifier U2 is coupled to ground through a resistor R4. Capacitor C2 and resistor R3 form a feedback impedance around amplifier U2 thus integrating the input signals at the input of amplifier U2. The integrator circuit, mentioned previously as block 142 in Figure 5, can also be considered a summing circuit which sums (a) the amplified output 404 and (b) the phase-shifted oscillator output signal 405.

According to some aspects, the arrangement presented in Figure 6 linearizes the system's response in the presence of a nonlinear sensor 200. The sensor loop including the feedback described previously make the output of the sensing circuit correspond linearly to the stimulus (e.g., pressure capacitor gap, etc.) rather than the nonlinear relationship traditionally provided in sensor circuits responding directly (rather than inversely) to capacitance changes. Thus, the feedback loop acts as a nonlinear transformer that counteracts the nonlinear behavior of the sensor 200 to yield a linearized output.

PCT/US02/34135

- 14 -

In some embodiments, the oscillator 110 is a single polarity excitation source providing a stabilized sinusoidal waveform with a frequency in a range from 1kHz to several megahurtz, for example from 50kHz to 100kHz, depending on the rest capacitance of the sensing capacitor 200 and other design considerations such as a tradeoff between sensor range, sensitivity and linearity.

The capacitive sensor 200 or a sensor array 100, represented in Figure 6 by Csense, commonly also comprises parasitic capacitances to ground represented as Csg and Cdg. Parasitic capacitance Csg represents the parasitic capacitance from the sensor line to ground. Parasitic capacitor Cdg represents the parasitic capacitance between the drive lines and ground. To reduce or eliminate parasitic capacitance, a sensor 200 or a portion of a sensory array which is idle (not being driven or sampled) is coupled to ground to prevent parasitic capacitance effects from influencing the measurements of the non-idle sensors. In some aspects this shunting to ground of the parasitic capacitance improves system throughput, linearity and bandwidth.

Capacitor Cref is normally selected to be a multiple of Csense, for example Cref may have a value equal to three times the value of Csense. The ratio of capacitors Cref over Csense multiplied by the excitation amplitude of the oscillator determines the magnitude of the output of amplifier U1. Thus, as Csense is increased the output of amplifier U1 will decrease with a sensitivity dictated by the design of the sensing capacitors Csense.

Other design considerations determine the nature of amplifier U1 characteristics that can be selected for the appropriate gain bandwidth and to minimize phase lag effects.

Furthermore, the driving and sensing lines to and from the sensor array 100 may be individually shielded. In this way it is possible to prevent cross-capacitance effects between the individual lines from impacting the measured capacitance due to effects such as twisting or bending of the cable bundle running to or from the array 100.

It may be advantageous in some aspects to physically place any tunable filter elements near the sensor elements 200 to provide common mode rejection to environmental effects such as temperature changes.

As described previously, combining a phase-shifted signal through the capacitor Ctune with the output of amplifier U1 in the integrator or summing amplifier U2 makes WO 03/036612 PCT/US02/34135

- 15 -

the sensor's sensitivity positive, or in other words inverts the polarity, and allows for bias cancellation. Capacitor Ctune provides any necessary phase lag adjustment while the RDAC acts as a digital potentiometer to allow for precise bias trimming for each sensor element 200. The value of the RDAC is adjusted based on a measurement at the output of summing amplifier U2 with the sensor 200 and its rest capacitance state. Such an adjustment is used to provide sufficient trim for both the bias and gain of each sensor element 200 having similar geometry or electrode surface area.

According to some aspects of the invention, the above-described sensor circuit adjustment may simplify the calibration process. Calibration is normally performed in an iterative process and is time consuming. The present design may also reduce the intervals required between calibration procedures.

Resistor Rf is a feedback resistance and in some embodiments provides stability to the circuit. Rf may also be selected to optimize the sensitivity and linearity of the sensing circuit and in some embodiments improve the settling time to increase the throughput of large sensor arrays.

As mentioned earlier, the oscillator 110 may provide a variety of oscillator signals 300. Such signals may be used as excitation waveforms which can be sinusoidal as well as non-sinusoidal waveforms. Also, dual polarity excitation is possible if its use is advantageous to a particular circuit design.

An alternative embodiment allows for the deletion of any or all of resistors R1, R4 and capacitors C1 and C2.

The output of the sensing circuit 265 Figure 6 is provided in some embodiments to an input of an AC to DC conversion circuit such as a rectifier and to a second stage amplification circuit before amplitude detection is performed.

Figure 7 illustrates an exemplary embodiment of a second stage circuit 275 which may be employed downstream of the previously-described sensing circuit 265. The sensing circuit 265 provides a sensing circuit output signal 406A, which may be the same as the integrated signal 406. This signal 406A contains information from the sensing element 200 indicative of the measured stimulus as well as any remaining bias, noise and other signal artifacts provided from the sensing circuit 265. The sensing circuit output signal 406A is provided to a second stage amplifier 500 which amplifies the signal corresponding to the desired measurement. In some embodiments this signal

PCT/US02/34135

WO 03/036612

- 16 -

406A may comprise an AC sinusoidal signal having an amplitude of approximately 200mV and a frequency of approximately 50-100kHz.

An output signal 501 from the second stage amplifier 500 is provided to a rectifier 502. The rectifier 502 is constructed in any appropriate way and converts an AC signal to a DC signal. A rectified signal 503 is provided to a second stage integrator 504 which integrates signal 503 over several cycles in time. According to some aspects, using the second stage integrator 504 instead of a low pass filter stage provides improved response time and avoids the need to wait until transients decay as is the case in low pass filter circuits. Integration in the integrator 504 is carried out over approximately 10 cycles in some embodiments.

Figure 8 illustrates one embodiment of a second stage amplification circuit 275similar to that described in Figure 7. A sensing circuit output signal 406A is received from a sensing circuit such as circuit 265. The signal 406A represents an output from a charge amplifier circuit which is oscillating at substantially the same frequency as the oscillator signal 300. The signal 406A is received from R5, the output of which is coupled to ground through a capacitor C5 that acts as a filter.

A second stage adjustable gain amplifier U3A receives a non-inverting input from signal 406A. The amplifier U3A is configured to provide an appropriate midband gain at the excitation frequency while maintaining approximately unity gain at very low frequencies. The mid-band gain is adjustable via the gain resistive digital-to-analog converter (GRDAC). Capacitor C4 ensures that the gain near DC frequencies is low or approximately unity.

Following the second stage amplification circuit 500 a signal 501 is provided to a rectifier stage 502. The rectifier stage 502 comprises an amplifier U3B and performs precision full-wave rectification, especially at the excitation frequencies, including rectification for low input amplitude levels.

The output of rectifier stage 502 is delivered on line 503 to averaging circuit 504. Averaging circuit 504 comprises amplifier U3C and outputs an averaging circuit output 505 that is substantially a DC signal corresponding to the stimulus delivered from the sensor 200. The overall circuit of Figure 8 represents an exemplary system for performing AC to DC conversion of the amplitude modulated signal from the charge amplifier circuit 265 shown in Figure 6. The circuits provided above perform their

PCT/US02/34135

- 17 -

function without requiring a switching element as in numerous existing synchronous phase demodulator circuits.

Note that by reversing the polarity of the diodes D1 and D2 of the rectifier stage 502 the rectifier stage 502 can be configured to provide gain for negative or positive inputs and removing the R10 path can provide for half-wave rectification.

The output of the second stage amplification circuit 275 may be an AC signal 505 having an amplitude of 4VAC and a modulation of 2V, reflecting the measured signal and having a frequency of 50 to 100 kHz. Such a signal provides a better basis for measurement of variable, but substantially DC, modulation signals from the sensor

Some embodiments of the present invention incorporate one or more of the above-described aspects into a system which is coupled to an organism and detects physical parameters or properties of the organism. Time-series collection of biological data is one example of such an embodiment. For example, the circuits and methods described above may be used in conjunction with a catheter or other device, including non-invasive devices or minimally-invasive devices to collect biological data on a human or animal patient. Pressure profiles measured within an orifice or a cavity in time and/or space can be collected for presentation to a user or machine for storage, processing, or analysis. This may form a basis for a diagnosis of some medical condition or be used as a predictor for some other condition of the organism.

In one embodiment, a series of sensors arranged substantially in a linear form factor, are placed within a body cavity such as the esophagus and measure pressures in this cavity as a function of time. These esophageal pressures may then be displayed graphically on a graphical display, showing the physiological sequence of an action such as coughing or swallowing.

Yet another aspect of the present invention permits the use of the above-described systems and methods to obtain high-resolution measurements of large regions of interest. Some embodiments of the invention utilize several sensor array grids, each having its own sensor driving and sampling electronics, as described above, to carry out simultaneous or sequential measurements. Multiplexing electronics are used in some embodiments to collect data from the multiple sensor arrays. These embodiments may

PCT/US02/34135

- 18 -

in some regards be considered scalable or parallel implementations of the concepts described above.

As an example, consider the case where a large region of interest is to be covered by sensors which collect data regarding a stimulus, e.g. pressure. The number of sensor elements will depend on the resolution required (i.e. the grid spacing) and the overall area of the region of interest. If the grid spacing is tight (fine resolution) then the number of sensor elements becomes large. In this case, interrogating or diving and sampling of each of the large number of sensors might entail cycling through the sensors in the manner described above. For a large number of sensors this can become time-consuming and slows down the sampling rate possible for sampling each member of the array. To increase the sampling rate or to increase the possible resolution for a given sampling rate or to increase the overall area that can be sampled at some resolution at a given sampling rate the region of interest may be broken into adjacent (tiled) sub-regions. Each of the sub-regions can be covered by a sensor array as described earlier, and the output from each of the sub-regions can be read by a circuit such as a multiplexer that switches between each of the sub-regions in turn.

It can be appreciated that this technique can be used in an iterative fashion, thus nesting or scaling up or down the overall sensing system so that an almost arbitrary area or resolution or sampling rate can be obtained, depending on the need. That is, in some aspects temporal performance or spatial performance may be procured at the cost of additional hardware or processing sensor electronics.

Having thus described several aspects of at least one embodiment of this invention, it is to be appreciated that various alterations, modifications, and improvements may occur to those skilled in the art. Such alterations, modifications, and improvements are intended to be part of this disclosure, and are intended to be within the spirit and scope of the invention. Accordingly, the present description and drawings are given by way of example only.

What is claimed is:

PCT/US02/34135

- 19 -

## <u>CLAIMS</u>

- A sensor system, comprising:

a sensor array having a plurality of sensor elements;

at least one sensor element of the sensor array, having addressable connections designating the sensor element, that senses a stimulus; and

an amplifier disposed in a feedback arrangement around the sensor

- an amplifier, disposed in a feedback arrangement around the sensor element, the amplifier receiving an input signal corresponding to an output of the sensor element and providing an output signal that drives the sensor element.

- The system of claim 1, wherein the sensor element comprises a

capacitive sensor element and the sensor array comprises a capacitive sensor array.

- The system of claim 1, wherein the stimulus alters a distance of separation between a first conductive strip and a second conductive strip.

- 4. The system of claim 1, wherein the stimulus is any of a force, a weight, a pressure, a displacement and an acceleration.

- The system of claim 1, further comprising an amplitude detector which receives an output signal from the amplifier.

- 6. The system of claim 1, further comprising a nonlinear transformer which transforms a nonlinear output of the amplifier into a corresponding substantially-linear signal representing the stimulus.

- 7. The system of claim 6, wherein the nonlinear transformer is a feedback loop comprising the sensor element.

- The system of claim 1, wherein the amplifier's output signal is one of a plurality of signals which drive the sensor element.

PCT/US02/34135

- 20 -

- The system of claim 1, wherein the filtering circuit is a digitallycontrolled integrator.

- 10. The system of claim 1, wherein the sensor element has an individually-controlled gain and an individually-controlled offset.

- 11. The system of claim 1, wherein a tunable filter element is coupled to the sensor element and wherein the tunable filter element is placed in physical proximity to the sensor elements to provide common mode rejection to environmental effects.

- 12. The system of claim 1, further comprising a tunable filter, coupled to an oscillator having an oscillator signal, which shifts a phase of the oscillator signal to provide a phase-shifted signal and a summing circuit which sums the amplifier output with the phase-shifted signal to substantially cancel out oscillator bias in a portion of the sensor system.

- 13. The system of claim 1, further comprising a path from the sensor element to a common potential which is selectably coupled to the sensor element.

- 14. The system of claim 1, wherein the sensor element is selectably coupled to a ground potential when the sensor element is not being driven or sampled.

- 15. The system of claim 1 wherein the sensor element is coupled to an electrical line which is individually shielded from electromagnetic effects.

- 16. The system of claim 1, further coupled to at least one other sensor system such that the system of claim 1 and the at least one other sensor system cover a combined region of interest having a greater area than an area covered by the system of claim 1 or an area covered by the at least one other sensor system.

PCT/US02/34135

- 21 -

17. A method for measuring a stimulus on a sensor array, comprising: sensing the stimulus using at least one sensor element of the sensor

array;

$\label{eq:constraint} \mbox{generating a sensor element output signal corresponding to the sensed stimulus;}$