(11) **EP 1 835 374 B1**

(12)

## **FASCICULE DE BREVET EUROPEEN**

(45) Date de publication et mention de la délivrance du brevet: 22.07.2015 Bulletin 2015/30

(51) Int Cl.: **G05F 3/20** (2006.01)

(21) Numéro de dépôt: 07104336.8

(22) Date de dépôt: 16.03.2007

# (54) Dispositif et procédé d'adaptation du potentiel du substrat d'un transistor MOS

Vorrichtung und Verfahren zur Anpassung des Potenzials des Substrats eines MOS-Transistors Device and method of adapting the potential of the substrate of an MOS transistor

(84) Etats contractants désignés: **DE FR GB IT**

(30) Priorité: 17.03.2006 FR 0650938

(43) Date de publication de la demande: 19.09.2007 Bulletin 2007/38

(73) Titulaires:

- STMICROELECTRONICS S.A. 92120 Montrouge (FR)

- Commissariat à l'Énergie Atomique et aux Énergies Alternatives 75015 Paris (FR)

- (72) Inventeurs:

- Thomas, Olivier 38320, HERBEYS (FR)

- Belleville, Marc 38120, SAINT EGREVE (FR)

- Liot, Vincent 38000, GRENOBLE (FR)

- Flatresse, Philippe 38190, FROGES (FR)

- (74) Mandataire: Thibon, Laurent et al Cabinet Beaumont1, rue Champollion38000 Grenoble (FR)

- (56) Documents cités:

US-A- 4 491 746 US-A- 5 184 030 US-A- 5 210 446 US-B1- 6 175 263

EP 1 835 374 B1

Il est rappelé que: Dans un délai de neuf mois à compter de la publication de la mention de la délivrance du brevet européen au Bulletin européen des brevets, toute personne peut faire opposition à ce brevet auprès de l'Office européen des brevets, conformément au règlement d'exécution. L'opposition n'est réputée formée qu'après le paiement de la taxe d'opposition. (Art. 99(1) Convention sur le brevet européen).

### Description

20

30

35

40

45

50

#### Domaine de l'invention

<sup>5</sup> **[0001]** La présente invention concerne un dispositif et un procédé de polarisation du substrat d'un transistor à effet de champ à semiconducteur métal-oxyde, ou transistors MOS.

## Exposé de l'art antérieur

[0002] De façon théorique, lorsque la tension entre la grille et la source d'un transistor MOS à canal N est supérieure à une tension de seuil, un courant est susceptible de s'écouler entre le drain et la source du transistor en fonction de la tension drain-source appliquée. Le transistor est alors passant ou dit à l'état actif. Lorsque la tension grille-source est inférieure à la tension de seuil, le transistor est bloqué ou dit à l'état inactif et est équivalent à un interrupteur ouvert. Toutefois, en pratique, on observe à l'état inactif le passage d'un courant, appelé courant de fuite, entre le drain et la source du transistor MOS.

[0003] Pour certaines applications, on souhaite obtenir des circuits électroniques dont la consommation est la plus faible possible. Il s'agit par exemple des téléphones portables, des consoles de jeu portables, etc., qui sont alimentées par des batteries. Il est alors nécessaire de réduire les courants de fuite des transistors de tels circuits électroniques pour diminuer la consommation du circuit électronique à l'état inactif.

[0004] Plusieurs facteurs influent sur l'amplitude du courant de fuite d'un transistor à l'état inactif. En particulier, pour un transistor MOS à canal N, le courant de fuite est d'autant plus important que la tension de seuil du transistor est faible, que la tension entre le substrat (en anglais body ou bulk) et la source du transistor est élevée ou que la tension entre la grille et la source du transistor est élevée.

[0005] Un procédé classique de réduction du courant de fuite d'un transistor MOS à canal N dont la source est reliée à la masse consiste à polariser le substrat du transistor MOS à canal N à un potentiel inférieur au potentiel de la source. Pour un transistor MOS à canal P dont la source reçoit une tension d'alimentation, un tel procédé consiste à polariser le substrat du transistor à un potentiel supérieur au potentiel de la source. Un tel procédé est appelé procédé de polarisation inverse du substrat (en anglais reverse bulk biasing).

[0006] Le principal inconvénient d'un tel procédé est que la polarisation du substrat du transistor est généralement réalisée par une source de tension connectée, à l'état inactif, au substrat du transistor. La réalisation d'une telle source de tension peut être relativement complexe. En outre, le fonctionnement d'une telle source de tension se traduit par une consommation supplémentaire qui limite la diminution de la consommation totale due à la réduction du courant de fuite du transistor.

[0007] Le brevet US 4 491 746 décrit un dispositif de polarisation d'une couche semiconductrice d'un circuit intégré.

## Résumé de l'invention

[0008] La présente invention vise à pallier tout ou partie des inconvénients des dispositifs et procédés connus de polarisation du substrat d'un transistor MOS.

[0009] La présente invention vise plus particulièrement un dispositif de polarisation du substrat d'un transistor MOS qui a une consommation propre réduite.

**[0010]** Selon un autre objet de l'invention, le dispositif de polarisation a une structure relativement simple et peut être réalisé à coût réduit.

**[0011]** La présente invention vise également plus particulièrement un procédé de polarisation du substrat d'un transistor MOS dont la mise en oeuvre entraîne une consommation supplémentaire réduite.

**[0012]** Pour atteindre tout ou partie de ces objets, la présente invention prévoit un circuit de polarisation du substrat d'un transistor MOS, le substrat du transistor MOS étant entouré d'un caisson assurant une isolation électrique du substrat. Le circuit comprend un élément capacitif reliant le substrat du transistor MOS à une source d'une tension alternative à une première valeur pendant une première durée et à une seconde valeur pendant une seconde durée inférieure à la moitié de la première durée.

[0013] Selon un exemple de réalisation de la présente invention, l'élément capacitif comprend une électrode reliée directement au substrat.

**[0014]** Selon un exemple de réalisation de la présente invention, la source est adaptée à fournir la tension alternative à la première valeur pendant la première durée et à la seconde valeur pendant la seconde durée inférieure à 1/10 de la première durée

**[0015]** Selon un exemple de réalisation de la présente invention, le transistor MOS est un transistor à canal N, la seconde valeur étant la tension nulle et la première valeur étant supérieure à la chute de tension en direct de la jonction substrat-source du transistor MOS.

[0016] Selon un exemple de réalisation de la présente invention, le circuit comprend un moyen adapté à relier le substrat et la grille du transistor MOS lorsque le transistor MOS est à l'état inactif.

**[0017]** Selon un exemple de réalisation de la présente invention, le circuit comprend un transistor MOS supplémentaire dont les bornes principales relient le substrat à la grille du transistor MOS et un moyen adapté à relier la grille du transistor supplémentaire à la grille du transistor MOS lorsque le transistor MOS est à l'état inactif.

[0018] Selon un exemple de réalisation de la présente invention, le moyen est adapté à relier la grille du transistor MOS supplémentaire au substrat du transistor MOS lorsque le transistor MOS est à l'état actif.

[0019] Selon un exemple de réalisation de la présente invention, le transistor MOS est formé au niveau d'un support de type SOI, GeOI ou SON.

[0020] Selon un exemple de réalisation de la présente invention, le transistor MOS comprend une première borne principale reliée à une borne d'un circuit électronique et une seconde borne principale reliée à une source d'un potentiel de référence, l'ensemble constitué par le transistor MOS, l'élément capacitif et la source de la tension alternative formant une pompe des charges du substrat du transistor MOS, le transistor MOS jouant par ailleurs le rôle d'interrupteur pour le circuit électronique.

[0021] La présente invention prévoit également un procédé de polarisation du substrat d'un transistor MOS, le substrat du transistor MOS étant entouré d'un caisson assurant une isolation électrique du substrat. Le procédé consiste à relier le substrat du transistor MOS à une source d'une tension alternative par un élément capacitif, la tension alternative étant à une première valeur pendant une première durée et à une seconde valeur pendant une seconde durée inférieure à la moitié de la première durée.

[0022] Selon un exemple de réalisation de la présente invention, la seconde durée est inférieure à 1/10 de la première durée.

[0023] Selon un exemple de réalisation de la présente invention, le procédé consiste, en outre, à prévoir un transistor MOS supplémentaire dont les bornes principales relient le substrat à la grille du transistor MOS et à relier la grille du transistor supplémentaire à la grille du transistor MOS lorsque le transistor MOS est à l'état inactif et à relier la grille du transistor MOS supplémentaire au substrat du transistor MOS lorsque le transistor MOS est à l'état actif.

### Brève description des dessins

10

20

25

30

35

40

45

50

55

**[0024]** Ces objets, caractéristiques et avantages, ainsi que d'autres de la présente invention seront exposés en détail dans la description suivante d'exemples de réalisation particuliers faite à titre non-limitatif en relation avec les figures jointes parmi lesquelles :

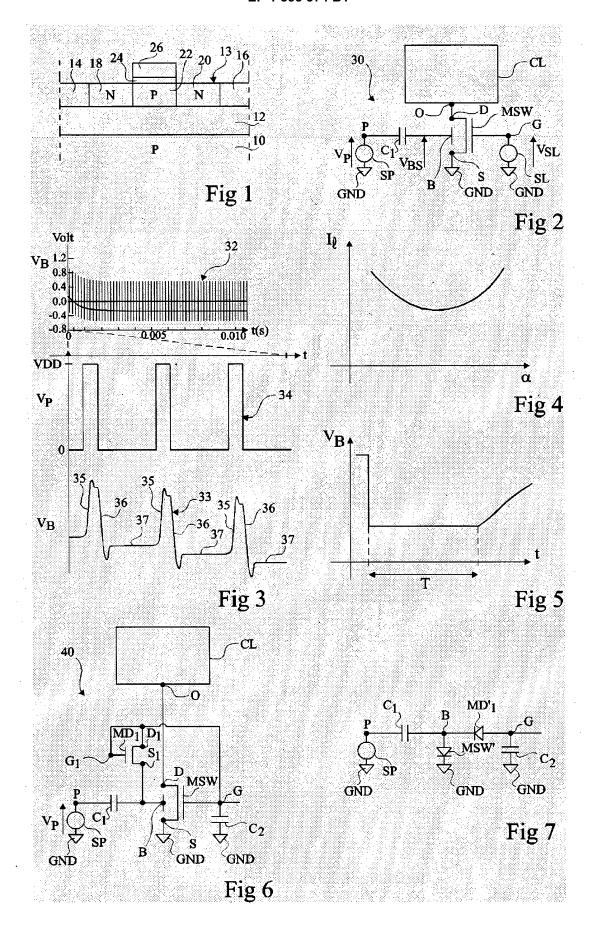

la figure 1 est une coupe schématique d'un transistor MOS à canal N réalisé au niveau d'un substrat de type SOI ; la figure 2 est un premier exemple de réalisation d'un dispositif de polarisation du substrat d'un transistor MOS selon l'invention ;

la figure 3 représente des courbes d'évolution de potentiels lors de la mise en oeuvre du procédé de polarisation selon l'invention ;

la figure 4 représente l'évolution du courant de fuite du circuit de la figure 2 en fonction du rapport cyclique d'une tension du circuit ;

la figure 5 illustre le principe de détermination de la période d'une tension utilisée par le circuit de la figure 2 ;

la figure 6 représente un deuxième exemple de réalisation du dispositif de polarisation selon l'invention ;

la figure 7 est un schéma d'un circuit électrique équivalent au dispositif représenté en figure 6 ;

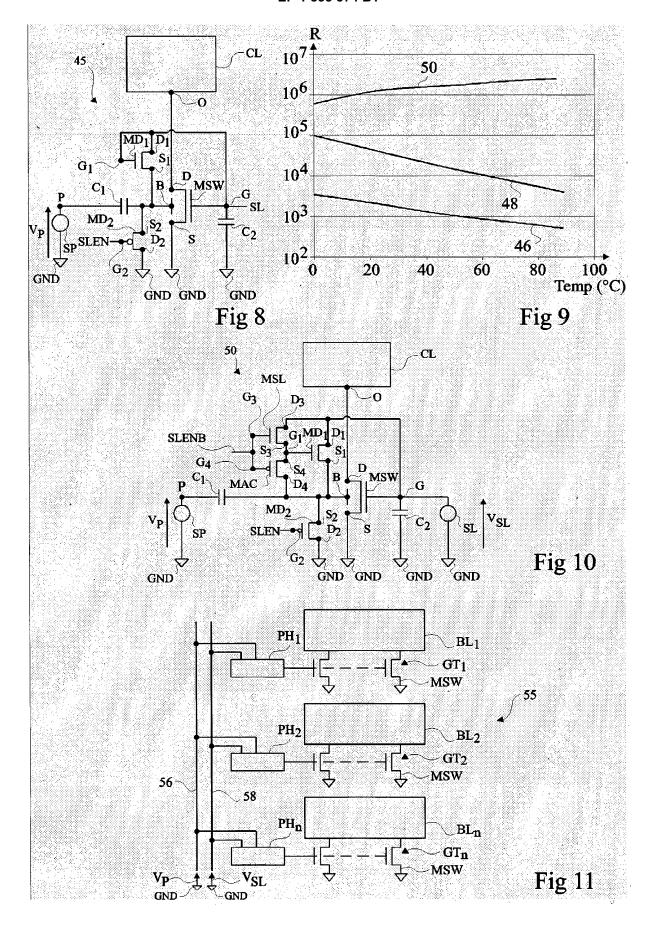

la figure 8 représente un troisième exemple de réalisation du dispositif de polarisation selon l'invention;

la figure 9 représente trois courbes d'évolution du gain en consommation pour trois procédés de réduction des courants de fuite ; et

les figures 10 et 11 représentent respectivement des quatrième et cinquième exemples de réalisation du dispositif de polarisation selon l'invention.

## Description détaillée

**[0025]** Par souci de clarté, de mêmes éléments ont été désignés par de mêmes références aux différentes figures et, de plus, comme cela est habituel dans la représentation des circuits intégrés, les diverses figures ne sont pas tracées à l'échelle. Dans la suite de la description, les potentiels de noeuds d'un circuit électronique sont mesurés par rapport à la masse du circuit électronique, le potentiel de la masse étant pris égal à 0 V.

[0026] La présente invention vise à modifier le potentiel du substrat d'un transistor MOS à l'état inactif pour diminuer le courant de fuite du transistor, la modification du potentiel du substrat étant obtenue par un procédé qui entraîne seulement une très faible consommation supplémentaire. La présente invention s'applique à un transistor pour lequel le potentiel du substrat est susceptible d'être modifié. La présente invention peut donc s'appliquer à un transistor MOS

à substrat isolé, par exemple un transistor MOS réalisé au niveau d'un substrat de type silicium sur isolant ou SOI (Silicon On Insulator), d'un substrat de type germanium sur isolant ou GeOI (Germanium On Insulator) ou d'un substrat de silicium à film ultra-mince ou SON (Silicon On Nothing). Le substrat du transistor est au moins partiellement entouré d'un caisson d'un matériau isolant assurant une isolation électrique du substrat. La présente invention peut également s'appliquer à un transistor MOS réalisé au niveau d'une tranche de silicium pour lequel le substrat du transistor est électriquement isolé du reste de la tranche, par exemple par l'intermédiaire d'un caisson ayant un type de dopant adapté entourant le transistor. Dans ce dernier cas, la polarisation du caisson est adaptée à assurer l'isolation du substrat du transistor, c'est-à-dire que le caisson est polarisé en inverse vis-à-vis des autres jonctions adjacentes pour assurer une isolation électrique du substrat du transistor.

[0027] Par rapport à la technologie pour laquelle les substrats des transistors MOS ne sont pas flottants, l'avantage de la technologie SOI partiellement désertée ou PD-SOI, en termes de performances, est lié à la modulation dynamique de la tension de seuil des transistors. Cette modulation dynamique est due à la variation du potentiel du substrat flottant des transistors. L'inconvénient d'un procédé classique de réduction des courants de fuite d'un transistor MOS est que le substrat n'est plus laissé flottant. A l'état actif, on perd l'avantage de la modulation dynamique de la tension de seuil du transistor. L'intérêt de l'invention est de pouvoir contrôler la polarisation du substrat en mode inactif tout en laissant la possibilité de laisser le substrat flottant en mode actif. Pour cela, le potentiel du substrat flottant du transistor est contrôlé par la modulation de sa charge.

[0028] La figure 1 représente, de façon très schématique, une coupe d'un transistor MOS à canal N réalisé au niveau d'un substrat de type SOI. Un support 10, par exemple une tranche de silicium dopée de type P est recouverte d'une couche isolante 12, par exemple de l'oxyde de silicium. Des zones actives 13 de silicium monocristallin séparées par des régions isolantes 14, 16 sont réalisées sur la couche isolante 12. Le transistor MOS est réalisé au niveau de l'une des zones actives 13 et comprend deux régions 18, 20 dopées de type N séparées par une région 22 dopée de type P. Les régions 18, 20 correspondent au drain et à la source du transistor MOS et la région 22 correspond au substrat du transistor MOS. La région 22 est recouverte d'une couche isolante 24, correspondant à l'oxyde de grille, elle-même recouverte d'une région conductrice 26, correspondant à la grille du transistor. Un tel transistor est dit réalisé selon une technologie SOI Partiellement Déserté, ou SOI-PD, dans la mesure où le substrat 22 du transistor est laissé flottant.

[0029] La présente invention va être maintenant décrite dans le cadre d'une application particulière pour la réduction du courant de fuite d'un transistor MOS de puissance utilisé comme interrupteur d'un circuit électronique. Un transistor MOS de puissance est un transistor MOS susceptible d'accepter des courants élevés à l'état actif et dont le courant de fuite à l'état inactif est faible par rapport aux courants de fuite des transistors MOS classiquement utilisés dans les circuits électroniques et dits à commutation rapide. Un transistor MOS de puissance peut, de façon classique, être utilisé comme interrupteur pour réduire la consommation d'un circuit électronique à l'état inactif. Pour ce faire, on dispose généralement le transistor MOS de puissance entre le circuit électronique et la masse. Le transistor MOS de puissance est bloqué lorsque le circuit électronique est à l'état inactif (ou en stand-by) pour limiter les pertes électriques totales. La présente invention permet de polariser le substrat du transistor MOS de puissance pour réduire le courant de fuite du transistor utilisé comme interrupteur et donc de réduire encore davantage la consommation du circuit électronique à l'état inactif. Toutefois, il est clair que la présente invention peut s'appliquer de façon générale à n'importe quel type de transistor MOS dont on veut réduire le courant de fuite à l'état inactif.

30

35

50

55

[0030] La figure 2 représente un premier exemple de réalisation d'un circuit 30 de polarisation du substrat d'un transistor MOS de puissance MSW, à canal N, disposé entre une borne de sortie O d'un circuit électronique CL et une source d'un potentiel de référence GND, par exemple la masse. Le circuit électronique CL comprend, par exemple, des transistors MOS à tension de seuil faible qui ont des vitesses de commutation supérieures à celle du transistor MOS de puissance MSW. Le transistor MSW comprend une source S, un drain D, un substrat B et une grille G. Le transistor MSW est, par exemple, réalisé au niveau d'un substrat de type SOI et a la structure représentée en figure 1. La source S est reliée à la masse GND et le drain D est relié à la borne de sortie O. La grille G est reliée à une borne d'une source de tension SL dont l'autre borne est reliée à la masse GND. On appelle V<sub>SL</sub> la tension aux bornes de la source de tension SL.

[0031] Selon le premier exemple de réalisation, le circuit 30 comprend un condensateur C<sub>1</sub> dont une électrode est reliée directement au substrat B et dont l'autre électrode est reliée à une borne d'une source de tension SP. L'autre borne de la source de tension SP est reliée à la masse GND. On appelle V<sub>P</sub> la tension aux bornes de la source de tension SP. A titre d'exemple, le condensateur C<sub>1</sub> comprend deux électrodes métalliques séparées par un matériau diélectrique. Dans ce cas, par rapport à la structure représentée en figure 1, la région 22 comprend une extension, non représentée, permettant la réalisation d'un plot de contact afin de relier le substrat du transistor à une électrode du condensateur C<sub>1</sub>. Selon un autre exemple, le condensateur C<sub>1</sub> comprend deux électrodes de silicium polycristallin, ou une première électrode métallique et une seconde électrode de silicium polycristallin. Par rapport à la structure représentée en figure 1, la région 22 peut comprendre une extension, non représentée, directement en contact avec la seconde électrode. Selon un autre exemple, le condensateur C<sub>1</sub> comprend une électrode métallique ou en silicium polycristallin et une électrode correspondant à une région de silicium dopée, qui est, par exemple, au contact du substrat. Les sources de tension SP et SL peuvent correspondre à tout type de circuit électronique adapté à fournir les tensions

$V_P$  et  $V_{SL}$  recherchées. En particulier, les tensions  $V_P$  et  $V_{SL}$  peuvent être obtenues à partir d'une source de tension unique. **[0032]** A l'état inactif, la tension  $V_P$  correspond à une tension rectangulaire périodique variant, par exemple, entre la tension nulle et la tension d'alimentation VDD. La période de la tension  $V_P$  est par exemple de l'ordre de 100 ms. Le rapport cyclique  $\alpha$  de la tension  $V_P$  correspond au rapport entre la durée pendant laquelle la tension  $V_P$  est égale à VDD et la durée pendant laquelle la tension  $V_P$  est égale à 0 V. Selon le premier exemple de réalisation, le rapport cyclique  $\alpha$  est inférieur à 1, par exemple inférieur à 1/2, de préférence inférieur à 1/10, voire inférieur à 1/100, par exemple de l'ordre de 1/500 pour un circuit réalisé par une technologie SOI. A titre d'exemple, pour le noeud technologique 130 nm SOI-PD, le rapport cyclique  $\alpha$  peut être inférieur à 1/500.

[0033] La figure 3 représente une courbe d'évolution 32 du potentiel du substrat B, appelé  $V_B$ , du transistor MSW à l'état inactif, une courbe d'évolution 33 qui correspond à un agrandissement de la courbe d'évolution 32 du potentiel  $V_B$  pour les premières périodes du signal  $V_P$  lors de la mise à l'état inactif du transistor MSW et une courbe d'évolution 34 du signal  $V_P$ . La courbe 32 est tracée à l'échelle. Par contre, les courbes 33 et 34 ne sont pas tracées à l'échelle.

[0034] Selon le premier exemple de réalisation, le circuit 30 permet, à l'état inactif, de diminuer globalement le potentiel  $V_B$  du substrat B du transistor MSW à un potentiel négatif de façon à diminuer le courant de fuite du transistor MSW. La présente invention utilise le fait que pour un transistor MOS dont le substrat B n'est pas directement relié à une source d'un potentiel constant, le potentiel  $V_B$  dépend de la quantité de charge  $Q_B$  stockée au niveau du substrat B.

[0035] Pour le circuit 30 représenté en figure 2, le potentiel V<sub>B</sub> est obtenu, à un instant donné, à partir de la relation suivante :

$$V_{B} = (Q_{B} + C_{D}V_{D} + C_{S}V_{S} + C_{G}V_{G} + C_{1}V_{P}) / C_{T}$$

(1)

20

30

35

50

où  $V_D$ ,  $V_S$  et  $V_G$  correspondent respectivement au potentiel du drain D, de la source S et de la grille G, où  $C_D$ ,  $C_S$  et  $C_G$  correspondent respectivement à la capacité de drain, de source et de grille et où  $C_T$  correspond à la somme des capacités  $C_G$ ,  $C_S$ ,  $C_D$  et  $C_1$ .

[0036] La quantité de charge  $Q_B$  varie en fonction du taux de charge et du taux de décharge du substrat B à un instant donné. Le taux de charge du substrat B est représentatif des phénomènes entraînant la génération de porteurs (par exemple la formation d'un courant tunnel, des phénomènes d'ionisation par impact, etc.), c'est-à-dire entraînant une augmentation de  $Q_B$ . Le taux de décharge du substrat B est représentatif des phénomènes entraînant la recombinaison de porteurs (par exemple la formation d'un courant de jonction drain-substrat ou source-substrat), c'est-à-dire entraînant une diminution de  $Q_B$ . De façon générale, les phénomènes entraînant la recombinaison de porteurs sont beaucoup plus rapides que les phénomènes entraînant la génération de porteurs d'un facteur pouvant varier de 100 à 1000.

**[0037]** A l'équilibre statique, la quantité de charges  $Q_B$  est sensiblement constante et fixée par les potentiels  $V_B$ ,  $V_D$ ,  $V_S$ ,  $V_G$  et la tension  $V_B$ . Lorsqu'on modifie les valeurs des potentiels  $V_D$ ,  $V_S$ ,  $V_G$ , la charge  $Q_B$  évolue, pendant une phase de transition plus ou moins longue, vers un nouvel équilibre statique. Pendant cette phase de transition, le transistor MSW se trouve à un état intermédiaire entre deux états d'équilibre.

[0038] La présente invention consiste à commander la quantité de charge  $Q_B$  en faisant varier la tension  $V_P$ . Plus précisément, la présente invention utilise le fait que la durée nécessaire à la charge du substrat est beaucoup plus longue que la durée nécessaire à la décharge du substrat de sorte qu'il suffit, pour commander la quantité de charge  $Q_B$ , de mettre la tension  $V_P$  à VDD de façon périodique pendant une durée très brève. La majorité du temps, la tension  $V_P$  est laissée à 0 V, la quantité de charge  $Q_B$  évoluant alors peu et fixant le potentiel  $V_B$  à une valeur sensiblement constante et négative. De ce fait, sauf au niveau des impulsions de la tension  $V_P$ , le potentiel  $V_B$  est pratiquement en permanence constant et négatif.

[0039] A titre d'exemple, on suppose initialement que les potentiels  $V_D$ ,  $V_S$  et  $V_G$  sont nuls, que la tension  $V_P$  est nulle et que le transistor MSW a atteint un état d'équilibre correspondant à une quantité de charge  $Q_{B0}$  initiale. Lorsque la tension  $V_P$  passe à VDD, le potentiel  $V_B$  augmente en raison du couplage capacitif dû au condensateur  $C_1$  (portion ascendante 35 de la courbe 33). Toutefois, l'augmentation de  $V_B$  par rapport à  $V_S$  qui est à zéro tend à rendre passante la jonction entre le substrat B et la source S du transistor MSW. Des charges négatives sont alors injectées dans le substrat B ce qui entraîne la diminution de la quantité de charge  $Q_B$  de  $Q_{B0}$  à  $Q_{B1}$  en raison des phénomènes de recombinaison de porteurs.

[0040] Lorsque la tension  $V_P$  passe de VDD à 0 V, le potentiel  $V_B$  diminue en raison du couplage capacitif dû au condensateur  $C_1$  (portion descendante 36 de la courbe 33). La jonction substrat-source du transistor MSW n'est alors plus passante de sorte que les phénomènes de recombinaison de porteurs tendent à s'arrêter. La charge  $Q_B$  devrait augmenter lentement de  $Q_{B1}$  à  $Q_{B0}$  en raison des phénomènes de génération de porteurs. Toutefois, ces phénomènes étant lents par rapport à la fréquence de commutation de  $V_P$ , tout se passe comme si la quantité de charges restait constante et égale à  $Q_{B1}$ . Le potentiel  $V_B$  se stabilise donc à la valeur correspondant à  $Q_{B1}$  donnée par la relation (1) et varie peu avant le prochain passage de  $V_P$  de 0 V à VDD (portion constante 37 de la courbe 33). Comme  $Q_{B1}$  est

inférieur à  $Q_{B0}$ , le potentiel  $V_B$  a diminué. Ce phénomène se répète pour les premiers cycles de la tension  $V_P$  de sorte que le potentiel  $V_B$  diminue au niveau des portions constantes 37.

**[0041]** Après plusieurs cycles successifs de la tension  $V_P$ , le potentiel  $V_B$  a suffisamment diminué de sorte que lorsque la tension  $V_P$  passe de 0 V à VDD, le potentiel  $V_B$  n'est pas élevé suffisamment pour rendre complètement passante la jonction substrat-source mais seulement légèrement passante pour compenser la génération de charges. La quantité de charge  $Q_B$  n'évolue alors sensiblement plus et le potentiel  $V_B$  se maintient, lorsque  $V_P$  est à 0 V, à une valeur négative par exemple entre -0,5 V à -1 V.

[0042] L'ensemble constitué par la source de tension SP, le condensateur  $C_1$  et le transistor MSW se comporte donc comme une pompe de charges adaptée à diminuer la quantité de charge  $Q_B$ .

**[0043]** De façon générale, les valeurs entre lesquelles varie  $V_P$  peuvent être différentes de 0 V et VDD. La seule condition est que la variation de  $V_P$  entraı̂ne par effet capacitif une variation du potentiel  $V_B$  suffisante pour rendre passante la jonction substrat-source du transistor MSW, au moins au début du passage à l'état inactif.

[0044] La figure 4 représente l'évolution du courant de fuite  $I_1$  du circuit 30 en fonction du rapport cyclique  $\alpha$ . Pour déterminer le rapport cyclique  $\alpha$  qui permet l'obtention du courant de fuite le plus faible, on peut procéder par essais successifs. Pour ce faire, on peut attribuer plusieurs valeurs de rapport cyclique à la tension  $V_P$ , déterminer les courants de fuite correspondants et choisir le rapport cyclique qui donne le courant de fuite minimal. On peut également utiliser les logiciels de simulation utilisés en CAO (Conception Assistée par Ordinateur) tel que le simulateur de type SPICE (acronyme anglais pour Simulation Program with Integrated Circuit Emphasis), par exemple les simulateurs ELDO ou HSIM.

**[0045]** La période du signal  $V_P$  est déterminée pour que la consommation dynamique du circuit 30 soit la plus faible. Une partie de la consommation dynamique est due à la commutation de la tension  $V_P$  sur un front montant ou descendant. Pour réduire la consommation dynamique, la période du signal  $V_P$  est choisie la plus grande possible pour limiter le nombre de commutations de la tension  $V_P$ .

[0046] La figure 5 représente l'évolution du potentiel  $V_B$  en fonction du temps lorsqu'on applique un front descendant sur  $V_P$  (passage d'une valeur haute à une valeur basse). L'échelle des abscisses est une échelle logarithmique. Par couplage capacitif, lorsque la tension  $V_P$  diminue, on observe une diminution du potentiel  $V_B$  qui se stabilise à une valeur basse. On détermine alors la durée T pendant laquelle  $V_B$  reste sensiblement constant à la valeur basse avant d'augmenter. La période du signal  $V_P$  peut correspondre à la durée T ainsi déterminée. On appelle F la fréquence du signal  $V_P$ . [0047] Lorsque le circuit 30 passe de l'état actif à l'état inactif (ou en stand-by), on peut, dans une phase initiale, accélérer la fréquence du signal  $V_P$  par rapport à la fréquence F déterminée précédemment, afin de faire diminuer le potentiel  $V_B$  du transistor MSW le plus rapidement possible. Ensuite, la fréquence du signal  $V_P$  est remise à la fréquence F de façon à maintenir le potentiel  $V_B$  à la valeur basse tout en réduisant la consommation dynamique du circuit 30.

30

35

50

[0048] La figure 6 représente un deuxième exemple de réalisation d'un circuit de polarisation 40 selon l'invention. Le circuit 40 correspond au circuit 30 représenté en figure 2 dans lequel on a ajouté un transistor MOS MD<sub>1</sub> à canal N, monté en diode, dont la grille G<sub>1</sub> et le drain D<sub>1</sub> sont reliés à la grille G du transistor MSW. La source S<sub>1</sub> du transistor MD<sub>1</sub> est reliée au substrat B du transistor MSW. Un condensateur C<sub>2</sub> est prévu entre la grille G et la masse GND. Selon une variante du deuxième exemple de réalisation, le condensateur C<sub>2</sub> n'est pas présent. A l'état inactif, la source de tension SL est à haute impédance et n'est pas représentée en figure 6. Le circuit 40 permet de mettre le substrat B à un potentiel négatif à l'état inactif, et, parallèlement, de mettre la grille G du transistor MSW à un potentiel négatif. En effet, le courant de fuite d'un transistor MOS à canal N est d'autant plus élevé que la tension entre la grille et la source est grande. On diminue ainsi encore davantage le courant de fuite du transistor MSW à l'état inactif.

[0049] La figure 7 représente un schéma électrique équivalent au circuit 40 représenté en figure 6 à l'état inactif. Le transistor MSW équivaut à une diode MSW' dont l'anode est connectée au substrat B et dont la cathode est connectée à la masse GND. Le transistor  $MD_1$  équivaut à une diode  $MD_1$ ' dont l'anode est connectée à la grille G et dont la cathode est connectée au substrat B. Selon un tel montage, le potentiel  $V_G$  suit en moyenne le potentiel  $V_B$ . Le condensateur  $C_2$ , s'il est présent, permet de stabiliser le potentiel  $V_G$ . La figure 7 correspond également au schéma d'une pompe de charge. Ceci signifie que le transistor MSW a deux fonctions : la première est celle d'interrupteur de puissance et la seconde est celle d'élément actif de la pompe de charge.

[0050] Selon une variante du circuit 40, le transistor MD<sub>1</sub> peut être remplacé par une diode dont l'anode est connectée à la grille G et dont la cathode est connectée au substrat B.

**[0051]** La figure 8 représente un circuit de polarisation 45 selon un troisième exemple de réalisation de l'invention dans lequel, par rapport au circuit 40 représenté en figure 6, on a ajouté, entre le substrat B et la masse GND, un transistor MOS  $MD_2$  à canal P dont la grille  $G_2$  est commandée par un signal SLEN, dont le drain  $D_2$  est relié à la masse GND et dont la source  $S_2$  est reliée au substrat B. Lorsque le transistor  $MD_2$  est passant, ce qui correspond au signal SLEN mis à 0 V, le transistor  $MD_2$  se comporte comme une diode dont l'anode est reliée au substrat B et dont la cathode est reliée à la masse GND. Cette diode supplémentaire se trouve donc en parallèle de la jonction substrat-source du transistor MSW qui tend à devenir passante lorsque la tension  $V_P$  passe à VDD. Une telle diode supplémentaire permet, lorsque la tension  $V_P$  passe à VDD, d'assurer que le potentiel  $V_B$  ne s'élève pas au-delà de 0,5-0,6 V et d'accentuer

l'évacuation des charges du substrat B.

10

30

35

50

[0052] La demanderesse a déterminé, par simulation, le gain en consommation dans le cas où le circuit électronique CL correspond à un oscillateur en anneau comportant 141 étages et constitué de transistors MOS à commutation rapide (c'est-à-dire ayant une tension de seuil faible, par exemple de l'ordre de 240 mV) réalisés en technologie SOI-PD avec une largeur de grille de 130 nanomètres, et pour une tension d'alimentation de 1,2 V. L'interrupteur de puissance MSW utilisé est du type permettant une pénalité en délai inférieure à 2 %. Les transistors MD<sub>1</sub>, MD<sub>2</sub> du circuit 45 sont des transistors du type à faible fuite (tension de seuil élevée de l'ordre de 350 mV) . Le ratio de réduction de la consommation, R, est défini par la relation suivante:

$$R = I_{cir}/I_{sw}$$

(2)

où I<sub>cir</sub> correspond au courant de fuite à la borne de sortie O du circuit électronique CL lorsqu'il est connecté directement à la masse GND et I<sub>SW</sub> correspond au courant de fuite mesuré à la borne de sortie O lorsque le circuit électronique CL est relié à la masse GND via le transistor de puissance MSW.

**[0053]** La figure 9 représente l'évolution du ratio en fonction de la température. La courbe 46 correspond à l'évolution du ratio obtenue lorsque le substrat du transistor MSW est laissé flottant. La courbe 48 correspond à l'évolution du ratio obtenue lorsque le substrat B du transistor MSW est connecté en permanence à la masse GND. La courbe 50 correspond à l'évolution du ratio obtenue lorsque le circuit de polarisation 45 est associé au transistor MSW.

[0054] On remarque que le circuit de polarisation 45 selon la présente invention permet d'obtenir une forte augmentation du gain de consommation par rapport à ce qui était obtenu de façon classique. En outre, pour les courbes 46 et 48, le gain en consommation tend à diminuer lorsque la température augmente. Au contraire, pour la présente invention, le gain en consommation augmente avec la température.

**[0055]** La figure 10 représente un circuit de polarisation 50 selon un quatrième exemple de réalisation de l'invention dans lequel, par rapport au circuit 45 de la figure 8, on a ajouté un transistor MOS MSL à canal N dont le drain  $D_3$  est connecté au drain  $D_1$  du transistor MD $_1$  et dont la source  $S_3$  est connectée à la grille  $G_1$  du transistor MD $_1$ . Le circuit 50 comporte également un transistor MOS MAC à canal P dont le drain  $D_4$  est connecté au substrat B du transistor MSW et dont la source  $S_4$  est connectée à la grille  $G_1$  du transistor MD $_1$ . Les grilles  $G_3$ ,  $G_4$  des transistors MSL et MAC reçoivent le signal SLENB qui est le complémentaire du signal SLEN.

[0056] Lorsque le circuit électronique CL est à l'état inactif, le signal SLEN est à l'état bas, par exemple à 0 V et le signal SLENB est à l'état haut, par exemple à VDD. Dans ce cas, le transistor MAC est bloqué et le transistor MSL est passant. De plus, le transistor MD<sub>2</sub> est passant et monté en diode. Le circuit 50 est alors identique au circuit 45. Son fonctionnement correspond donc à ce qui a été décrit précédemment. Lorsque le circuit électronique CL est à l'état actif, le signal SLEN est à l'état haut et le signal SLENB est à l'état bas. Les transistors MD<sub>2</sub> et MSL sont alors bloqués. Le transistor MAC est passant et équivaut sensiblement à un interrupteur fermé. La grille G<sub>1</sub> du transistor MD<sub>1</sub> est donc reliée au substrat B du transistor MSW. Le transistor MD<sub>1</sub> fonctionne alors comme un limiteur de courant et équivaut à une diode dont l'anode est reliée au substrat B et la cathode à la grille G.

[0057] A l'état actif, les tensions Vp et  $V_{SL}$  sont à VDD. Le transistor  $MD_1$  permet d'amener  $V_B$  à une valeur supérieure à 0 V tout en assurant que le potentiel  $V_B$  reste inférieur à 0,6 V de façon qu'il n'y ait pas de polarisation en direct de la jonction substrat-source du transistor MSW. Le fait de mettre la tension  $V_P$  à VDD permet d'élever initialement le potentiel  $V_B$  par couplage capacitif, le potentiel  $V_B$  étant maintenu par la suite à une valeur positive par l'intermédiaire du transistor  $MD_1$ .

[0058] On obtient ainsi un transistor MSW dont le substrat est polarisé positivement à l'état actif. Ceci permet de diminuer la tension de seuil du transistor et d'améliorer la conduction du transistor MSW à l'état actif. Pour un même courant à conduire, on peut alors réduire les dimensions du transistor MSW par rapport à un transistor MOS dont le substrat serait maintenu à la masse à l'état actif. L'utilisation d'un transistor MSW de dimensions réduites permet de réduire les courants de fuite à l'état inactif. Le circuit 50 permet de diminuer d'environ 15 % la surface occupée par le transistor MSW. De façon plus générale, le circuit 50 permet d'obtenir un transistor MSW à deux tensions de seuil modulées dynamiquement, une première tension de seuil basse à l'état actif (le substrat B étant polarisé positivement) assurant une meilleure conduction et une seconde tension de seuil élevée à l'état inactif (le substrat étant polarisé négativement) permettant de réduire le courant de fuite.

[0059] La figure 11 représente un sixième exemple de réalisation du circuit de polarisation 55 selon l'invention utilisé pour réduire les courants de fuite de plusieurs transistors de puissance MSW. Les transistors de puissance MSW sont répartis en groupes de transistors de puissance GT<sub>i</sub>, i étant un entier compris entre 1 et n, chaque groupe GT<sub>i</sub> étant associé à un circuit électronique BL<sub>i</sub> constitué, par exemple, de transistors à commutation rapide. Les grilles des transistors MSW de chaque groupe de transistors GT<sub>i</sub> sont connectées à un circuit partiel de polarisation PH<sub>i</sub>. Chaque circuit PH<sub>i</sub> comprend les transistors MOS MD<sub>1</sub>, MD<sub>2</sub>, MSL, MAC, et les condensateurs C<sub>1</sub>, C<sub>2</sub> du circuit 50. Chaque circuit

partiel PH<sub>i</sub> est relié à une première ligne 56 reliée à la source de tension SP, non représentée, et à une seconde ligne 58 reliée à la source de tension SL, non représentée. Des sources de tension uniques SP et SL sont donc connectées à chaque circuit PH<sub>i</sub>. De mêmes éléments des circuits de polarisation étant associés à plusieurs transistors, on diminue ainsi l'augmentation de surface due à l'utilisation du circuit de polarisation selon l'invention.

**[0060]** Avantageusement, afin d'éviter une dégradation du transistor MSW, par exemple par claquage de la couche d'oxyde dû à une différence de potentiel entre le drain et la grille du transistor MSW supérieure à la tension d'alimentation, on peut utiliser un transistor MSW avec un oxyde de grille épais, adapté à fonctionner à des tensions d'alimentation élevées. Un tel transistor à oxyde de grille épais est, par exemple, du type GO2, l'épaisseur de l'oxyde de grille étant d'environ 2,7 nm, les autres transistors du circuit ayant une épaisseur d'oxyde de l'ordre de 1,5 nm.

[0061] Bien entendu, la présente invention est susceptible de diverses variantes et modifications qui apparaîtront à l'homme de l'art. En particulier, la source de tension SP peut fournir un signal autre que rectangulaire. Il peut s'agir d'un signal constant à 0 V comportant périodiquement des impulsions triangulaires. En outre, la présente invention a été décrite pour la polarisation du substrat d'un transistor MOS à canal N. Toutefois, la présente invention peut s'appliquer à la polarisation du substrat d'un transistor MOS à canal P dont la source est reliée à une source d'un potentiel de référence haut, par exemple VDD. Dans ce cas, le substrat du transistor est mis, à l'état inactif, à un potentiel supérieur au potentiel de la source en faisant varier V<sub>P</sub> entre 0 V (impulsions de courtes durées) et VDD. En outre, le potentiel de la grille peut être amené à un potentiel supérieur au potentiel de la source à l'état inactif. De plus, le potentiel du substrat peut être amené à un potentiel inférieur au potentiel de la source à l'état actif.

#### Revendications

- 1. Circuit (30 ; 40 ; 45 ; 50 ; 55) de polarisation du substrat (B) d'un transistor MOS (MSW), caractérisé en ce que le substrat du transistor MOS est entouré d'un caisson (12) assurant une isolation électrique du substrat, le circuit comprenant un élément capacitif (C<sub>1</sub>) reliant le substrat (B) du transistor MOS à une source (SP) adaptée à fournir une tension (Vp) alternative à une première valeur pendant une première durée et à une seconde valeur (VDD) pendant une seconde durée inférieure à la moitié de la première durée.

- 2. Circuit selon la revendication 1, dans lequel l'élément capacitif (C<sub>1</sub>) comprend une électrode reliée directement au substrat (B).

- 3. Circuit selon la revendication 1, dans lequel la source (SP) est adaptée à fournir la tension alternative (V<sub>P</sub>) à la première valeur pendant la première durée et à la seconde valeur (VDD) pendant la seconde durée inférieure à 1/10 de la première durée.

- 4. Circuit selon la revendication 1, dans lequel le transistor MOS (MSW) est un transistor à canal N, la seconde valeur étant la tension nulle et la première valeur étant supérieure à la chute de tension en direct de la jonction substrat-source du transistor MOS (MSW).

- Circuit selon la revendication 1, comprenant un moyen (MD<sub>1</sub>) adapté à relier le substrat (B) et la grille (G) du transistor MOS (MSW) lorsque le transistor MOS est à l'état inactif.

- 6. Circuit selon la revendication 1, comprenant un transistor MOS supplémentaire (MD<sub>1</sub>) dont les bornes principales (S<sub>1</sub>, D<sub>1</sub>) relient le substrat (B) à la grille (G) du transistor MOS (MSW) et un moyen (MSL, MAC) adapté à relier la grille (G<sub>1</sub>) du transistor supplémentaire à la grille (G) du transistor MOS (MSW) lorsque le transistor MOS est à l'état inactif.

- 7. Circuit selon la revendication 6, dans lequel le moyen (MSL, MAC) est adapté à relier la grille (G<sub>1</sub>) du transistor MOS supplémentaire (MD<sub>1</sub>) au substrat (B) du transistor MOS (MSW) lorsque le transistor MOS est à l'état actif.

- **8.** Circuit selon la revendication 1, dans lequel le transistor MOS (MSW) est formé au niveau d'un support de type SOI, GeOI ou SON.

- 9. Circuit selon la revendication 1, dans lequel le transistor MOS (MSW) comprend une première borne principale (D) reliée à une borne d'un circuit électronique (CL) et une seconde borne principale (S) reliée à une source d'un potentiel de référence (GND), l'ensemble constitué par le transistor MOS, l'élément capacitif (C<sub>1</sub>) et la source (SP) de la tension (Vp) alternative formant une pompe des charges du substrat (B) du transistor MOS, le transistor MOS jouant par ailleurs le rôle d'interrupteur pour le circuit électronique.

20

25

10

35

50

45

- 10. Procédé de polarisation du substrat (B) d'un transistor MOS (MSW), caractérisé en ce que le substrat du transistor MOS est entouré d'un caisson (12) assurant une isolation électrique du substrat, le procédé consistant à relier le substrat du transistor MOS à une source (SP) d'une tension alternative (Vp) par un élément capacitif (C<sub>1</sub>), la tension alternative étant à une première valeur pendant une première durée et à une seconde valeur (VDD) pendant une seconde durée inférieure à la moitié de la première durée.

- 11. Procédé selon la revendication 10, dans lequel l'élément capacitif (C<sub>1</sub>) comprend une électrode reliée directement au substrat (B).

- 12. Procédé selon la revendication 10, dans lequel la seconde durée est inférieure à 1/10 de la première durée.

- 13. Procédé selon la revendication 10, consistant, en outre, à prévoir un transistor MOS supplémentaire (MD<sub>1</sub>) dont les bornes principales (S<sub>1</sub>, D<sub>1</sub>) relient le substrat (B) à la grille (G) du transistor MOS (MSW) et à relier la grille (G<sub>1</sub>) du transistor supplémentaire à la grille (G) du transistor MOS (MSW) lorsque le transistor MOS est à l'état inactif et à relier la grille (G<sub>1</sub>) du transistor MOS supplémentaire (MD<sub>1</sub>) au substrat (B) du transistor MOS (MSW) lorsque le transistor MOS est à l'état actif.

## Patentansprüche

20

15

5

- 1. Eine Schaltung (30; 40; 45; 50; 55) zum Vorspannen der Masse (B) eines MOS-Transistors (MSW), dadurch gekennzeichnet, dass die Masse des MOS-Transistors umgeben ist von einer Vertiefung (12), die eine elektrische Isolierung des Substrats vorsieht, wobei die Schaltung ein kapazitives Element (C1) aufweist, welches die Masse (B) des MOS-Transistors mit einer Quelle (SP) verbindet, die in der Lage ist, eine Wechselspannung (VD) mit einem ersten Wert für eine erste Zeitperiode und mit einem zweiten Wert (VDD) für eine zweite Zeitperiode kürzer als die Hälfte der ersten Zeitperiode vorzusehen.

- 2. Die Schaltung nach Anspruch 1, wobei das kapazitive Element (C<sub>1</sub>) eine direkt mit dem Substrat (B) verbundene Elektrode aufweist.

30

25

3. Die Schaltung nach Anspruch 1, wobei die Quelle (SP) in der Lage ist, die Wechselspannung (V<sub>P</sub>) mit dem ersten Wert für die erste Zeitperiode und mit dem zweiten Wert (VDD) für die zweite Zeitperiode kürzer als ein Zehntel der ersten Zeitperiode vorzusehen.

35

- 4. Die Schaltung nach Anspruch 1, wobei der MOS-Transistor (MSW) ein N-Kanaltransistor ist, wobei der zweite Wert die Nullspannung ist und der erste Wert größer ist als der Durchlasspannungsabfall der Masse-Quelle -Grenzschicht (junction) des MOS-Transistors (MSW).

- 5. Schaltung nach Anspruch 1, die Mittel (MD<sub>1</sub>) aufweist, die in der Lage sind, die Masse (B) und das Gate (G) des 40 MOS-Transistors (MSW) zu verbinden, wenn der MOS-Transistor sich in dem inaktiven Zustand befindet.

Die Schaltung nach Anspruch 1, die einen zusätzlichen MOS-Transistor (MD<sub>1</sub>) aufweist, dessen Hauptanschlüsse (S<sub>1</sub>, D<sub>1</sub>) die Masse (B) mit dem Gate (G) des MOS-Transistors (MSW) verbinden und ferner Mittel (MSL, MAC) aufweist, die in der Lage sind, das Gate (G<sub>1</sub>) des zusätzlichen Transistors mit dem Gate (G) des MOS-Transistors (MSW) zu verbinden, wenn der MOS-Transistor sich in dem inaktiven Zustand befindet.

45

7. Die Schaltung nach Anspruch 6, wobei die Mittel (MSL, MAC) in der Lage sind, das Gate (G<sub>1</sub>) des zusätzlichen MOS-Transistors (MD<sub>1</sub>) mit der Masse (B) des MOS-Transistors (MSW) zu verbinden, wenn der MOS-Transistor im aktiven Zustand ist.

50

8. Schaltung nach Anspruch 1, wobei der MOS-Transistor (MSW) auf dem Niveau eines SOI-, GeOI- oder SON-Typträger gebildet ist.

55

9. Die Schaltung nach Anspruch 1, wobei der MOS-Transistor (MSW) einen ersten Hauptanschluss (D), verbunden mit einem Anschluss einer elektronischen Schaltung (CL) und ferner einen zweiten Hauptanschluss (S) verbunden mit einer Quelle einer Referenzspannung (GND) aufweist wobei die Anordnung gebildet durch den MOS-Transistor, das kapazitive Element (C<sub>1</sub>) und die Quelle (SP) der Wechselspannung (V<sub>P</sub>) eine Pumpe der Ladungen der MOS-Transistormasse (B) bilden, wobei der MOS-Transistor ferner sich als ein Schalter für die elektronische Schaltung

verhält.

5

20

25

30

35

45

50

55

- 10. Ein Verfahren zum Vorspannen der Masse (B) eines MOS-Transistors (MSW), dadurch gekennzeichnet, dass die Masse des MOS-Transistors umgeben ist von einer Vertiefung (12), die eine elektrische Isolierung des Substrats vorsieht, wobei das Verfahren folgendes vorsieht: die Verbindung der MOS-Transistormasse mit einer Quelle (SP) einer Wechselspannung (V<sub>P</sub>) durch ein kapazitives Element (C<sub>1</sub>), wobei die Wechselspannung einen ersten Wert hat für eine erste Zeitperiode und ein zweiten Wert (VDD) für eine zweite Zeitperiode kürzer als die Hälfte der ersten Zeitperiode.

- 10 **11.** Das Verfahren nach Anspruch 10, wobei das kapazitive Element (C<sub>1</sub>) eine Elektrode aufweist direkt verbunden mit dem Substrat (B).

- 12. Das Verfahren nach Anspruch 10, wobei die zweite Zeitperiode kürzer ist als ein Zehntel der ersten Zeitperiode.

- 15 13. Das Verfahren nach Anspruch 10, welches ferner folgendes aufweist:

Vorsehen eines zusätzlichen MOS-Transistors  $(MD_1)$ , dessen Hauptanschlüsse  $(S_1, D_1)$ , die Masse (B) mit dem Gate (G) des MOS-Transistors (MSW) verbinden, verbinden des Gates  $(G_1)$  des zusätzlichen Transistors mit dem Gate (G) des MOS-Transistors (MSW), wenn der MOS-Transistor sich in dem inaktiven Zustand befindet, und verbinden des Gates  $(G_1)$  des zusätzlichen MOS-Transistors  $(MD_1)$  mit der Masse (B) des MOS-Transistors (MSW), wenn der MOS-Transistor sich in dem aktiven Zustand befindet.

#### Claims

- 1. A circuit (30; 40; 45; 50; 55) for biasing the bulk (B) of a MOS transistor (MSW), characterized in that the bulk of the MOS transistor is surrounded by a well (12) providing an electric insulation of the substrate, the circuit comprising a capacitive element (C<sub>1</sub>) connecting the bulk (B) of the MOS transistor to a source (SP) capable of providing an A.C. voltage (Vp) at a first value for a first time period and at a second value (VDD) for a second time period shorter than half of the first time period.

- 2. The circuit of claim 1, wherein the capacitive element (C<sub>1</sub>) comprises an electrode directly connected to the substrate (B).

- 3. The circuit of claim 1, wherein the source (SP) is capable of providing the A.C. voltage (Vp) at the first value for the first time period and at the second value (VDD) for the second time period shorter than 1/10 of the first time period.

- 4. The circuit of claim 1, wherein the MOS transistor (MSW) is an N-channel transistor, the second value being the zero voltage, and the first value being greater than the forward voltage drop of the bulk-source junction of the MOS transistor (MSW).

- **5.** The circuit of claim 1, comprising means (MD<sub>1</sub>) capable of connecting the bulk (B) and the gate (G) of the MOS transistor (MSW) when the MOS transistor is in the inactive state.

- **6.** The circuit of claim 1, comprising an additional MOS transistor (MD<sub>1</sub>) having its main terminals (S<sub>1</sub>, D<sub>1</sub>) connecting the bulk (B) to the gate (G) of the MOS transistor (MSW) and means (MSL, MAC) capable of connecting the gate (G<sub>1</sub>) of the additional transistor to the gate (G) of the MOS transistor (MSW) when the MOS transistor is in the inactive state.

- 7. The circuit of claim 6, wherein the means (MSL, MAC) are capable of connecting the gate (G<sub>1</sub>) of the additional MOS transistor (MD<sub>1</sub>) to the bulk (B) of the MOS transistor (MSW) when the MOS transistor is in the active state.

- 8. The circuit of claim 1, wherein the MOS transistor (MSW) is formed at the level of an SOI, GeOI or SON-type support.

- 9. The circuit of claim 1, wherein the MOS transistor (MSW) comprises a first main terminal (D) connected to a terminal of an electronic circuit (CL) and a second main terminal (S) connected to a source of a reference voltage (GND), the assembly formed by the MOS transistor, the capacitive element (C<sub>1</sub>), and the source (SP) of the A.C. voltage

(Vp) forming a pump of the charges of the MOS transistor bulk (B), the MOS transistor further behaving as a switch for the electronic circuit.

- 10. A method for biasing the bulk (B) of a MOS transistor (MSW), characterized in that the bulk of the MOS transistor is surrounded by a well (12) providing an electric insulation of the substrate, the method comprising the connection of the MOS transistor bulk to a source (SP) of an A.C. voltage (Vp) by a capacitive element (C<sub>1</sub>), the A.C. voltage being at a first value for a first time period and at a second value (VDD) for a second time period shorter than half of the first time period.

- **11.** The method of claim 10, wherein the capacitive element (C<sub>1</sub>) comprises an electrode directly connected to the substrate (B).

- 12. The method of claim 10, wherein the second time period is shorter than 1/10 of the first time period.

- 13. The method of claim 10, further comprising the provision of an additional MOS transistor (MD<sub>1</sub>) having its main terminals (S<sub>1</sub>, D<sub>1</sub>) connecting the bulk (B) to the gate (G) of the MOS transistor (MSW) and the connection of the gate (G<sub>1</sub>) of the additional transistor to the gate (G) of the MOS transistor (MSW) when the MOS transistor is in the inactive state and the connection of the gate (G<sub>1</sub>) of the additional MOS transistor (MD<sub>1</sub>) to the bulk (B) of the MOS transistor (MSW) when the MOS transistor is in the active state.

## RÉFÉRENCES CITÉES DANS LA DESCRIPTION

Cette liste de références citées par le demandeur vise uniquement à aider le lecteur et ne fait pas partie du document de brevet européen. Même si le plus grand soin a été accordé à sa conception, des erreurs ou des omissions ne peuvent être exclues et l'OEB décline toute responsabilité à cet égard.

# Documents brevets cités dans la description

• US 4491746 A [0007]