# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-196910 (P2006-196910A)

(43) 公開日 平成18年7月27日(2006.7.27)

| (51) Int.C1. |         |           | FI            |           | テーマコート    | ぶ (参考) |

|--------------|---------|-----------|---------------|-----------|-----------|--------|

| HO1L         | 21/205  | (2006.01) | HO1L 21/205   |           | 4 K O 3 O |        |

| HO1L         | 21/304  | (2006.01) | HO1L 21/304 6 | 4 5 B     | 5 F O 4 5 |        |

| C23C         | 16/02   | (2006.01) | C 2 3 C 16/02 |           | 5F048     |        |

| HO1L         | 21/8238 | (2006.01) | HO1L 27/08 3: | 2 1 E     | 5 F 1 4 O |        |

| HO1L         | 27/092  | (2006.01) | HO1L 29/78 3  | 0 1 S     |           |        |

|              |         |           | 審查請求 未請求 請求項の | )数 32 O L | (全 20 頁)  | 最終頁に続く |

(21) 出願番号 特願2006-7969 (P2006-7969) (22) 出願日 平成18年1月16日 (2006.1.16)

(31) 優先権主張番号 10-2005-0003892

(32) 優先日 平成17年1月14日 (2005.1.14)

(33) 優先権主張国 韓国 (KR) (31) 優先権主張番号 11/232, 955

(32) 優先日 平成17年9月23日 (2005. 9. 23)

(33) 優先権主張国 米国(US)

(71) 出願人 390019839 三星電子株式会社 Samsung Electronics Co., Ltd. 大韓民国443-742京畿道水原市霊通

(74) 代理人 100064908

弁理士 志賀 正武

区梅灘洞416

(74)代理人 100089037

弁理士 渡邊 隆

(74)代理人 100108453

弁理士 村山 靖彦

(74)代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】半導体基板のインサイチュ洗浄方法及びこれを採用する半導体素子の製造方法

# (57)【要約】

【課題】半導体基板のインサイチュ洗浄方法及びこれを 採用する半導体素子の製造方法を提供する。

【解決手段】一実施例によるエピタキシャル層の製造方法は反応チャンバ内に露出した半導体表面を有する基板をローディングさせるステップを具備する。前記露出した半導体表面上に存在する酸化物が分解されて酸素を除去する洗浄条件が成立するように前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱する。前記酸化物が除去されるように前記洗浄条件を洗浄時間の間に維持して清浄な半導体表面を形成する。前記清浄な半導体の表面上にエピタキシャル層を形成する。前記基板を前記反応チャンバからアンローディングさせる。

## 【選択図】図1

## 【特許請求の範囲】

## 【請求項1】

反応チャンバ内に露出した半導体表面を有する基板をローディングさせる段階と、 前記露出した半導体表面上に存在する酸化物が分解されて酸素を除去する洗浄条件が成立するように、前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱する段階と、

前記酸化物が除去されるように前記洗浄条件を洗浄時間の間に維持して清浄な半導体表面を形成する段階と、

前記清浄な半導体表面上にエピタキシャル層を形成する段階と、

前記基板を前記反応チャンバからアンローディングさせる段階と、

を含むことを特徴とするエピタキシャル層の製造方法。

#### 【請求項2】

前記洗浄圧力は約1mTorr以下であり、前記洗浄温度は約800 以下であることを特徴とする請求項1記載のエピタキシャル層の製造方法。

#### 【請求項3】

前記基板を前記反応チャンバ内にローディングさせる前に、前記露出した半導体表面を予備洗浄する段階をさらに含むことを特徴とする請求項1記載のエピタキシャル層の製造方法。

### 【請求項4】

前記洗浄圧力は約1mTorr以下であり、前記洗浄温度は約500 ~約750 であり、前記洗浄時間は約200秒以下であることを特徴とする請求項1記載のエピタキシャル層の製造方法。

## 【請求項5】

前記洗浄圧力は約0.1mTorr以下であり、前記洗浄温度は約730 ~約790であり、前記洗浄時間は約120秒以下であることを特徴とする請求項1記載のエピタキシャル層の製造方法。

## 【請求項6】

前記洗浄時間の間に前記反応チャンバ内にキャリアガスを注入する段階をさらに含むことを特徴とする請求項1記載のエピタキシャル層の製造方法。

#### 【請求項7】

前記キャリアガスは水素、アルゴン、ネオン、クリプトン及びこれらの混合ガスからなる群で選択することを特徴とする請求項6記載のエピタキシャル層の製造方法。

#### 【請求項8】

前記洗浄圧力は約50mTorr以下であり、前記洗浄温度は約800 以下であり、前記洗浄時間は約200秒以下であることを特徴とする請求項7記載のエピタキシャル層の製造方法。

#### 【請求項9】

前記キャリアガスは前記洗浄条件として前記反応チャンバ内の酸素ガスを飽和量の約50%以下で維持することができる流量で注入されることを特徴とする請求項6記載のエピタキシャル層の製造方法。

# 【請求項10】

前記キャリアガスは約500sccm以下の流量で注入されることを特徴とする請求項9記載の半導体素子の製造方法。

# 【請求項11】

前記キャリアガスは前記洗浄条件として前記反応チャンバ内の酸素ガスを飽和量の約 1 0 % 以下で維持することができる流量で注入されることを特徴とする請求項 6 記載のエピタキシャル層の製造方法。

## 【請求項12】

前記露出した半導体表面はシリコン、ゲルマニウム、二元化合物半導体、三元化合物半導体、四元化合物半導体及びそれらの組合せからなる群で選択することを特徴とする請求

10

20

30

40

項1記載のエピタキシャル層の製造方法。

## 【請求項13】

前記エピタキシャル層を形成する段階と前記基板を反応チャンバからアンローディングさせる段階との間に冷却条件として前記基板を維持させる段階をさらに含み、前記冷却条件は前記エピタキシャル層の酸化を抑制した条件であることを特徴とする請求項1記載のエピタキシャル層の製造方法。

#### 【請求項14】

前記エピタキシャル層を形成する段階と前記基板を前記反応チャンバからアンローディングさせる段階との間に前記反応チャンバ内に冷却ガスを注入する段階をさらに含むことを特徴とする請求項13記載のエピタキシャル層の製造方法。

【請求項15】

前記冷却ガスは水素、アルゴン、ネオン、クリプトン及びこれらの混合ガスからなる群で選択することを特徴とする請求項14記載のエピタキシャル層の製造方法。

### 【請求項16】

前記基板を前記反応チャンバ内にローディングさせた後、前記洗浄条件に到達する前に、前記基板を昇温雰囲気で維持する段階をさらに含み、前記昇温雰囲気は前記露出した半導体表面の酸化が抑制された雰囲気であることを特徴とする請求項 1 記載のエピタキシャル層の製造方法。

#### 【請求項17】

前記基板を前記反応チャンバ内にローディングさせた後、前記洗浄条件に到達するまで前記反応チャンバ内に昇温ガスを注入する段階をさらに含むことを特徴とする請求項16記載のエピタキシャル層の製造方法。

### 【請求項18】

前記昇温がスは水素、アルゴン、ネオン、クリプトン及びこれらの混合ガスからなる群で選択することを特徴とする請求項17記載のエピタキシャル層の製造方法。

#### 【請求項19】

半導体基板を処理して露出した半導体表面を有する中間素子構造物を形成する段階と、前記中間素子構造物を反応チャンバ内にローディングする段階と、

前記露出した半導体表面上に存在する酸化物が分解されて酸素を除去する洗浄条件が成立されるように、前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱する段階と、

前記酸化物が除去されるように前記洗浄条件を洗浄時間の間に維持して清浄な半導体表面を形成する段階と、

前記清浄な半導体表面上にエピタキシャル層を形成する段階と、

前記半導体基板を前記反応チャンバからアンローディングする段階と、

を含むことを特徴とする半導体素子の製造方法。

#### 【請求項20】

前記露出した半導体表面は、ソース / ドレイン領域であることを特徴とする請求項 1 9 記載の半導体素子の製造方法。

### 【請求項21】

前記露出した半導体表面は、ソース/ドレイン領域及びゲート電極表面であることを特徴とする請求項19記載の半導体素子の製造方法。

## 【請求項22】

前記エピタキシャル層は単結晶半導体構造、多結晶半導体構造、非晶質半導体構造及びこれらの組合せからなる群から選択された一つのエピタキシャル層構造を有することを特徴とする請求項19記載の半導体素子の製造方法。

#### 【請求項23】

前記露出した半導体表面上に一種類のエピタキシャル層構造が形成されることを特徴とする請求項22記載の半導体素子の製造方法。

## 【請求項24】

50

40

10

20

前記半導体基板を処理して露出した半導体表面を有する中間素子構造物を形成することは、

前記半導体基板上に活性領域を画定する段階と、

前記活性領域の表面の第1部分の上にゲートパターンを形成する段階と、

前記活性領域の表面の第2部分を露出する段階と、

を含むことを特徴とする請求項22記載の半導体素子の製造方法。

#### 【請求項25】

前記半導体基板を処理して露出した半導体表面を有する中間素子構造物を形成することは、

前記半導体基板上に活性領域を画定する段階と、

前記活性領域の表面の第1部分の上にゲートパターンを形成する段階と、

前記活性領域の表面及び前記ゲートパターン上の半導体表面の第2部分を露出する段階と、

を含むことを特徴とする請求項22記載の半導体素子の製造方法。

## 【請求項26】

反応チャンバ内に露出した半導体表面を有する基板をローディングする段階と、

前記露出した半導体表面上に存在する酸化物が分解されて除去されるか、還元反応によってシリコンに転換される洗浄条件が成立されるように、前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱する段階と、

前記酸化物が除去されるように前記洗浄条件を洗浄時間の間に維持して清浄な半導体表面を形成する段階と、

前記清浄な半導体表面上にエピタキシャル層を形成する段階と、

前記基板を前記反応チャンバからアンローディングさせる段階と、

を含むことを特徴とするエピタキシャル層の製造方法。

## 【請求項27】

反応チャンバ内に露出した半導体表面を有する基板をローディングする段階と、

前記露出した半導体表面上に存在する酸化物が分解されて除去される第1洗浄条件が成立するように、前記工程チャンバ内を第1洗浄圧力で排気させて前記基板を第1洗浄温度で加熱する段階と、

前記露出した半導体表面上に残存する酸化物が還元反応によってシリコンに転換される第2洗浄条件が成立されるように前記工程チャンバ内を第2洗浄圧力で排気させて前記基板を第2洗浄温度で加熱する段階と、

前記残存する酸化物が転換されるように前記第2洗浄条件を第2洗浄時間の間に維持して清浄な半導体表面を形成する段階と、

前記清浄な半導体表面上にエピタキシャル層を形成する段階と、

前記基板を前記反応チャンバからアンローディングさせる段階と、

を含むことを特徴とするエピタキシャル層の製造方法。

#### 【請求項28】

露出した半導体表面上に存在する酸化物が分解されて除去される洗浄条件が成立するように前記反応チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱する段階を含むことを特徴とする露出した半導体表面の洗浄方法。

#### 【請求項29】

前記酸化物を除去することは、前記露出した半導体表面上の酸化物を還元反応によって除去する段階をさらに含むことを特徴とする請求項28記載の露出した半導体表面の洗浄方法。

## 【請求項30】

前記反応チャンバ内を前記洗浄温度で酸素ガスの分圧が平衡分圧の約50%以下になる洗浄圧力で維持する段階をさらに含むことを特徴とする請求項28記載の露出した半導体表面の洗浄方法。

## 【請求項31】

50

10

20

30

30

40

50

前記洗浄温度は、約800 以下であることを特徴とする請求項28記載の露出した半導体表面の洗浄方法。

# 【請求項32】

前記反応チャンバ内を前記洗浄温度で酸素ガスの分圧が平衡分圧の約50%以下になる洗浄圧力で維持する段階をさらに含むことを特徴とする請求項31記載の露出した半導体表面の洗浄方法。

【発明の詳細な説明】

## 【技術分野】

### [0001]

本発明は、半導体素子の製造方法に関し、特に、半導体基板のインサイチュ洗浄方法及びこれを採用するエピタキシャル層の製造方法(methods for in-situcleaning of semiconductor substrates and methods of semiconductor device fabrication employing the same)に関するものである。

#### 【背景技術】

### [0002]

半導体素子の製造工程は、半導体基板上に導電性または絶縁性薄膜を形成してこれらをパターン化することを含む。前記半導体基板上に形成される前記薄膜の品質は工程環境の清浄(cleanliness)と前記薄膜が形成される前記半導体基板の表面状態に大きく影響を受ける。前記半導体基板は、前記半導体基板は工程チャンバにローディングされる前に大気中に露出することができる。この場合、前記半導体基板の表面は、大気中の汚染物質によって汚染することができる。特に、前記半導体基板の表面上に非化学両論的な組成を有して形成される自然酸化膜は前記半導体基板上に形成される半導体素子の電気的な特性を低下させることができる。よって、前記半導体基板の表面上の汚染物質、特に前記自然酸化膜は個々の薄膜形成工程の前に別途の洗浄工程を介して除去されるべきである。

#### [00003]

一方、エピタキシャル成長工程(epitaxial growth process)は単結晶半導体の基板上に単結晶半導体層を形成するための優れた手段として提供される。前記エピタキシャル成長工程は、初期にバイポーラトランジスタの動作特性を向上させるために用いられていたが、近年は、CMOS直接回路の製造に広く用いられている。例えば、MOSトランジスタの単チャンネル効果及び電流駆動力を改善させるための上昇されたソース/ドレイン構造(elevated source/drain structure)を具現するために選択的エピタキシャル成長工程(selective epitaxial growth process)が適用されている。その外に、MOSトランジスタのキャリア移動度を向上させるための引張られたチャンネル(strained channel)を形成するために異種エピタキシャル成長工程(hetero‐epitaxial growth process)が適用されている。

# [ 0 0 0 4 ]

前記エピタキシャル成長工程によって半導体基板上に形成されるエピタキシャル層は前記半導体基板の結晶構造に付いて成長される。よって、前記エピタキシャル成長工程において前記半導体基板の表面状態は前記エピタキシャル層の品質に大きな影響を及ぼす。上述したように、半導体基板の表面上に形成された自然酸化膜はエピタキシャル層にスリップ(slip)またはスタッキングフォールト(stacking fault)のような格子欠陥を誘発するので完全に除去するのが好ましい。これのために、エピタキシャル層を成長させるための半導体基板が反応チャンバ内にローディングされる前に洗浄工程が実施される。前記洗浄工程は適切な化学溶液を使用した湿式洗浄または化学乾式エッチング(chemical dry etch)工程によって実施される。さらに、洗浄され

20

30

40

50

た半導体基板が反応チャンバ内にローディングされた後にインサイチュ洗浄工程がさらに実施される。しかしながら、従来の水素ベーク(hydrogen bake)とも呼ばれる前記インサイチュ洗浄工程は、通常850 ~1200 の水素雰囲気で実施される高温工程である。よって、前記インサイチュ洗浄工程中に、半導体基板内にドーピングされた不純物の拡散によってMOSトランジスタのスレッショルド電圧が減少することができる。また、前記半導体基板がSOI基板の場合には前記インサイチュ洗浄工程中に上部シリコン層(top silicon layer)の凝集が発生することができる。

[00005]

結論的に、エピタキシャル成長工程において半導体素子の電気的特性が劣化されるのを 抑制するためには前記インサイチュ洗浄工程の温度を低めることが必要である。

【発明の開示】

【発明が解決しようとする課題】

[0006]

本発明が解決しようする技術的課題は、低温において半導体基板表面上の自然酸化膜のような不純物を有効に除去することができる半導体基板のインサイチュ洗浄方法及びこれを採用するエピタキシャル層の製造方法を提供することにある。

【課題を解決するための手段】

[0007]

本発明は、後続のエピタキシャル蒸着中に用いる温度及び従来の洗浄方法に用いる温度よりも実質的に低い温度を用いることによって、温度と係わる問題、例えば、不純物の非正常的な拡散、自動ドーピング(auto doping)、スリップ(slip)及びストレス問題を低減させるとともに全体の工程時間を短縮させることができるインサイチュ洗浄方法を提供する。

[00008]

エピタキシャル層を形成する前に、洗浄及びシリコン表面から不純物の除去のために用いられる低い温度は製造工程の熱バジェット(budget)を低減することができて、 基板上にあらかじめ形成されたCMOS素子の性能を維持させることができる

[0009]

反応チャンバ内で維持する温度及び圧力の組合せは、前記基板表面からシリコン酸化物を十分に蒸発させる。ポンプ及び/または反応チャンバ内に導入するキャリアガス(carrier gas)は前記反応チャンバからシリコン酸化物の蒸気を十分に除去することによって平衡条件に達することを防止する。特に、前記反応チャンバは前記反応チャンバ内においてシリコン酸化物の蒸気の濃度が洗浄条件から平衡蒸気圧の50%以下、さらに10%以下になるように維持することができる。前記反応チャンバ内でシリコン酸化物の蒸気の分圧を低減することによって前記シリコン酸化物の蒸発に有利な反応が促進されて前記シリコン酸化物の蒸発率は増加することができる。

[0010]

本発明の実施例は、反応チャンバ内に露出した半導体表面を有する基板をローディングさせて(loading)、前記露出した半導体表面上に存在する酸化物が分解されて酸素を除去する洗浄条件が成立するように(establish)、前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱し、前記酸化物が除去されるように前記洗浄条件を洗浄中に維持して清浄な半導体表面(clean semiconductor surface)を形成し、前記清浄な半導体表面上にエピタキシャル(epitaxial)層を形成して前記基板を前記反応チャンバからアンローディング(unloading)することを含むエピタキシャル層の製造方法を具備する。

[0011]

約50mTorr以下の洗浄圧力及び約800 以下の洗浄温度において約200秒以下の洗浄時間で維持することによって前記半導体表面から自然酸化物は十分に除去することができる。ここで、「約」という用語は一つ以上のパラメータを調節及び/または測定して前記方法を実施するのに用いられる装置及び/または関連設備の性能に因る偏差を含

30

40

50

むために用いられる。例えば、800 で設定された加熱設備は一般的に正確な設定温度を維持することができず、設定温度に対して高いかまたは低い許容範囲内での偏差を見せる場合がある。よって、「約」という用語の使用はこのような予想可能な偏差が請求されたパラメータの範囲内で考慮されなければならないことを示す。

#### [0012]

キャリアガス、例えば、水素(hydrogen)、アルゴン(argon)、ネオン(Neon)、クリプトン(Krypton)及びこれらの混合ガスからなる群かららったがれたガスが前記インサイチュ洗浄工程の少なくともある時間にて前記反応チャンバ内を真空条件に注入することができる。前記インサイチュ洗浄工程間に前記反応チャンバ内を真空条件で維持し、前記キャリアガスを前記反応チャンバ内に注入することによって、または可して、またはすることによって前記反応チャンバ内の酸化物蒸気の分圧(partial presecとによって前記反応チャンバ内の酸化物蒸気の分圧(partial presec)を用いられた温度及び圧力に対する平衡条件以下で十分に低減させることができるの反応チャリアガスは実質的に使われた流量よりも少ない約25%以下、または約10%以下とすることができる。例えば、水素が使用される場合、前記水素の流量は従来の水素ベーク工程で使われた流量よりも少ない約25%以下、または約10%以下とすることができる。

# [0013]

前記反応チャンバ内の酸素ガスの分圧を平衡値の約50%以下、さらに10%以下に低減することによって半導体酸化物の分解を促進させ、清浄な半導体表面を取得するのに必要とされる工程時間が短縮できるものと期待されている。この場合、基板上において他の構造物の腐食や損傷なしで酸化物を除去するためには前記基板上に露出した他の材料の蒸気圧が考慮されなければならないし、このような考慮に従って温度及び圧力条件が設定されなければならない。

### [0014]

以下で詳しく説明されるように、前記インサイチュ洗浄工程の適用は、シリコン表面に制限されず、他の半導体表面、例えばゲルマニウム(germanium)、シリコン / ゲルマニウムのように二成分系で成り立つ二元化合物半導体材料(binary semiconductor material)、四成分系からなる三元化合物半導体材料(tertiary semiconductor material)、四成分系からなる四元化合物半導体材料(quaternary semiconductor material)及びそれらの組合せを含む半導体材料の洗浄に適用されることができる。

## [0015]

本発明の実施例は、半導体基板を処理して露出した半導体表面を有する中間素子構造物を形成し、前記中間素子構造物を反応チャンバ内にローディングさせて、前記露出した半導体表面上に存在する酸化物が分解されて酸素を除去する洗浄条件が成立するように(establish)、前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱し、前記酸化物が除去されるように前記洗浄条件を洗浄時間中に維持して清浄な半導体表面(clean semiconductor surface)を形成し、前記清浄な半導体表面上にエピタキシャル(epitaxial)層を形成して、前記半導体基板を前記反応チャンバからアンローディング(unloading)させることを含む半導体素子の製造方法を具備する。

# [0016]

前記露出した半導体表面は、例えば、ソース/ドレイン(source/drain) 領域、及び/またはゲート電極表面を含むことができる。また、前記エピタキシャル層の 構造は単結晶構造、多結晶構造、非晶質構造及びこれらの組合せを含むことができる。

## [0017]

本発明の実施例は、反応チャンバ内に露出した半導体表面を有する基板をローディングさせて(loading)、前記露出した半導体表面上に存在する酸化物が分解されて除

去されたり還元反応によってシリコンに転換される洗浄条件が成立するように(establish)、前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱し、前記酸化物が除去できるように前記洗浄条件を洗浄時間中に維持して清浄な半導体表面(cleansemiconductorsurface)を形成し、前記清浄な半導体表面上にエピタキシャル(epitaxial)層を形成して、前記基板を前記反応チャンバからアンローディング(unloading)させることを含むエピタキシャル層の製造方法を具備する。

# [0018]

いくつかの場合に、前記エピタキシャル層の製造方法は、前記露出した半導体表面上に存在する酸化物が分解されて除去される第1洗浄条件が成立するように(establish)、前記工程チャンバ内を第1洗浄圧力で排気させて前記基板を第1洗浄温度で加熱し、前記露出した半導体表面上に残存する酸化物が還元反応によってシリコンに転換される第2洗浄条件が成立するように(establish)前記工程チャンバ内を第2洗浄圧力で排気させて前記基板を第2洗浄温度で加熱し、前記残存する酸化物が転換するように前記第2洗浄条件を第2洗浄時間中に維持させて清浄な半導体表面(cleansemiconductorsurface)を形成し、前記清浄な半導体表面上にエピタキシャル(epitaxial)層を形成して、前記基板を前記反応チャンバからアンローディング(unloading)させることを含むエピタキシャル層の製造方法を具備する。

## [0019]

本発明の実施例は、露出した半導体表面上に存在する酸化物が分解されて除去される洗浄条件が成立するように(establish)前記工程チャンバ内を洗浄圧力で排気させて前記基板を洗浄温度で加熱することを含む露出した半導体表面の洗浄方法を具備する。前記分解ステップは前記露出した半導体表面上に残存する酸化物を除去する還元ステップとともに実施することができる。

## 【発明の効果】

## [0020]

本発明によれば、低温で半導体基板表面上の自然酸化膜のような汚染物質を有効にインサイチュ洗浄できる。その結果、エピタキシャル層の品質低下を防止することができるし、半導体素子の電気的特性の劣化を最小化することができる。

【発明を実施するための最良の形態】

# [0021]

以下、添付した図面を参照して本発明の好ましい実施例を詳しく説明する。しかしながら、本発明はここで説明された実施例に限定されず、他の形態で具体化することもできる。むしろ、ここで紹介される実施例は開示された内容が徹底的で完全になるように、そして当業者に本発明の思想が十分に伝達できるようにするために提供されるものである。図面において、層及び領域の厚さは明確性を期するために誇張されたものである。明細書の全般において同一参照番号は同一構成要素を示す。

## [0022]

半導体基板の露出したシリコン表面上に優れた品質を有するエピタキシャルシリコン層を成長させるためには前記露出したシリコン表面が可能な限り完璧な結晶表面でなければならない。特に、シリコン表面の汚染を除去するための工程が実行されなければならないし、シリコン表面には後続のエピタキシャル工程中に形成されるエピタキシャル層の結晶格子構造の劣化を防止するためにピット(pit)または他の結晶欠陥のような表面不規則があってはならない。例えば、シリコン表面上の酸化物、金属及び/または有機物のような汚染物質は多様な結晶欠陥を有するエピタキシャル層が形成される原因となり得る。

#### [0023]

周知のように、規則的な単結晶格子より不規則な結晶格子を有するエピタキシャル層は 製造工程の収率、素子特性及び/または素子信頼性を低下させる。例えば、汚染と係わる 欠陥は製造工程中のインライン(in-line)品質検査の失敗をもたらしてウエハ収 20

10

30

50

30

40

50

率を落として工程単価を増加させることになる。例えば、望まない移動性の(mobile)イオン汚染物質により素子特性が変化されて、最初デザインした用途の素子に不適合でありチップの収率が低下される。また、素子の信頼性は素子構造物を通じて移動し素子不良を誘発させる、例えば、微小量の金属汚染物質によって不利な影響を受けることができる。よって、エピタキシャル層の品質を向上させて最終的に製造される半導体素子の収率、性能及び信頼性に及ぶ不利な影響を低減したり防止するためにはシリコン表面上の汚染物質及び表面不規則を除去するのが重要である。

## [0024]

シリコン表面から除去すべき汚染物質の形態は、微粒子、有機残留物、及び無機残留物が含まれる。前記微粒子は、ほこり及び煙粒子だけでなく、空気中に一般的にある他の不純物及び湿式処理の際に表面で成長し除去されてないバクテリアも含まれる。前記有機路留物は、例えば、オイル、フォトリソグラフィエ程間に使用されるフォトレジスト、または化学的機械研磨(Chemical Mechanical Polishing;CMP)スラーリー(slurry)組成物内に含まれる化合物のような炭素を含有するの機化合物を含む組成物と係わる。また、前記無機残留物は、例えば、半導体製造工程中の以前ステップで用いられる塩酸、フッ酸、または保護されてないシリコン表面が酸化雰囲気に露出されることによって生成する酸化物のように炭素を含まない化合物と係わる。上述した例から示したように、前記汚染源は、上述のような環境から不可避な炭素及び酸素のような材料を含むだけでなく半導体素子の製造工程中における他のステップで用いられたり発する材料を含む。

#### [0025]

エピタキシャル蒸着工程の前に基板表面を洗浄する方法としての一つは、過酸化物が充填された塩酸及びアンモニア水酸化物を順に適用させることである。この場合、シリコン表面は、殆どが酸及び塩基に耐性を有するので非常に強い溶媒が用いられることができる。しかしながら、上述したように、前記シリコン表面は空気や水溶液中にいつも存在する不純物と直ちに反応して結合することになる。一方、シリコン酸化物(SiO₂)ように完全に酸化されたシリコン表面は相対的に不活性である。よって、エピタキシャル工程が実施される前にシリコン酸化物やその外の残留汚染物質はシリコン表面から除去すべきである。

# [0026]

インサイチュ洗浄工程は、後続のエピタキシャル工程と同一のチャンバ内で実行されるのでエピタキシャル工程に適する、酸化されてない清浄なシリコン表面を提供することができる。しかしながら、上述したように従来のインサイチュ洗浄工程は、基板を約850以上、多くは1200 まで加熱することを含む。このような高温工程は、清浄な表面を提供することはできるが、結晶構造における損傷の危険があり最終的な半導体素子の全般的な熱バジェット(budget)を増加させることができる。半導体素子の寸法が持続的に縮小することによって半導体素子の製造工程は素子の電気的特性の劣化を防止するためにさらに厳しい熱バジェットの要求を満足しなければならない。特に、主な素子パラメータであるスレッショルド電圧は製造工程中の過度な加熱に因る過度な不純物の拡散に敏感に影響を受け得る。。

# [ 0 0 2 7 ]

#### < 第 1 実 施 例 >

以下では、シリコン表面を有する半導体基板に対して説明することになるが、本発明は、これに限らず、多様な基板、例えば単結晶シリコン基板、単結晶シリコンを有するSOI基板、単結晶シリコンゲルマニウム基板に適用することができる。また、本発明に適用することができる基板は、単結晶ゲルマニウム基板及び単結晶シリコンカーバイド基板だけではなく多様な三元化合物の半導体基板、四元化合物の半導体基板及びこの技術分野で周知された他の半導体化合物基板を含むことができる。

#### [0028]

本発明による洗浄方法は、処理されない基板及び半導体製造工程中の一部工程を終了し

30

40

50

て処理された基板に対して用いられることができる。前記処理された基板はウェル、ソース / ドレイン領域、接合、ゲート電極構造物、多様な誘電体及びお互いに機能的に関連付けられた導電膜を含む回路構造物を含むことができる。工程の進行程度に関わらず、前記基板はエピタキシャル成長のために露出したシリコン表面を少なくとも一部領域に含むことができる。

### [0029]

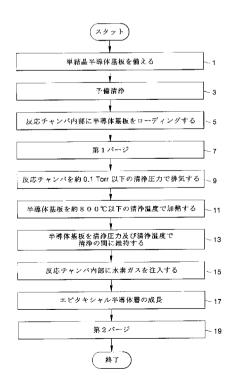

図1のフローチャートに示すように、まず、予備洗浄工程(S3)が実施される。前記予備洗浄工程(S3)は、基板が反応チャンバ内にローディングされる前に完了する。前記予備洗浄工程(S3)は、基板上に存在するバルク(bulk)自然酸化物及び他の汚染物質を除去するために乾式及び/または湿式の方法で実施することができる。この場合、通常のRCA洗浄及び/またはピラニア(piranha;H₂ O₂ /H₂ SO₄ )湿式洗浄工程に適用される酸性溶液が表面から有機及び/または無機汚染物質を除去するために用いられることができる。

# [0030]

前記RCA洗浄は、(1)5:1:1のH2O2:NH4OH溶液を用いて不溶性有機汚染物質を除去するステップ、(2)HFがH2Oに対して1:50に希釈された溶液を用いて自然酸化物及び金属汚染物質を除去するステップ、(3)6:1:1のH2O2:HC1溶液を用いてイオン及び重金属原子の汚染物質を除去するステップ、(3)6:1:1のH2O2 :HC1溶液を用いてイオン及び重金属原子の汚染物質を除去するステップは、乾式エッチング工程によって代替されたり補完することができる。また機械的スクラバー(scrubber)よって代替されたり補完することができる。また機械的スクラバー(scrubber)及び/またはリンス(rinse)工程が前記基板表面上の微粒子を減少させるために角することができる。上述したように殆どの自然酸化物は、HF溶液または緩衝HF(buffered HF;BHF)溶液内で除去されるが、非常に高い反応性を有するシリコン表面は、表面に適用された多様な化学物質を除去するために用いられる前記リンス

程及び乾燥ステップの間に少なくとも部分的に酸化することができる。よって、エピタキシャル層を形成する前にインサイチュ洗浄を実施する必要がある。

## [0031]

図1及び度図2に示すように、前記基板Sが予備洗浄された後、前記基板Sは処理装置11に具備された反応チャンバ13内にローディングされる。(S5)前記反応チャンバ13内で前記基板Sはチャック(chuck)組立体15上に位置して支持される。

#### [0032]

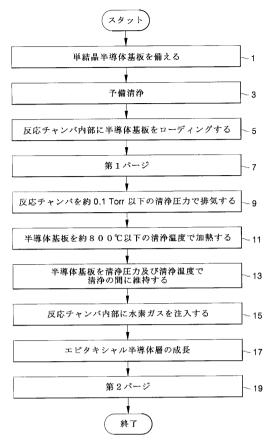

図2に示すように、前記反応チャンバ13は、一つ以上の真空ポンプと連結される。前記真空ポンプは、例えば前記反応チャンバ13内の圧力を約10<sup>19</sup> Torrに減圧することができるターボ分子ポンプのような高真空ポンプ17及び前記反応チャンバ13から大きい体積のガスを除去して前記反応チャンバ13内の圧力を約10<sup>3</sup> Torrに減圧することができるラフ(rough)ポンプ19を含むことができる。前記それぞれのポンプは、一つ以上のバルブ21、23によって調節される排気ラインによって前記反応チャンバ13と連結することができる。

## [0033]

前記基板Sが平盤(platen)またはウエハ支持台(wafer supporter)とも呼ばれる前記チャック組立体15上に位置された後、第1パージ工程(S7)を実施する。前記第1パージ工程(S7)は前記ラフポンプ19を用いて前記反応チャンバ13内を約100Torr以下の圧力に減圧することを含むことができる。さらに、第1パージ工程(S7)は、前記反応チャンバ13を排気しながら前記反応チャンバ13内に水素ガスを注入することを含むことができる。このように、前記第1パージ工程(S7)の間、前記ラフポンプ19を用いて前記反応チャンバ13内のガスを持続的に除去しながら、前記水素ガスを前記反応チャンバ13内に注入させることによって前記反応チャンバ13内に存在する残留窒素、残留酸素及び残留水蒸気を実質的に除去することができる。前記第1パージ工程(S7)の間、さらに詳しくは、殆どの酸化性物質が前記反応チャンバ13内から除去されて前記反応チャンバ13内の雰囲気が比較的に純粋水素雰囲気に

30

40

50

(11)

なった後、前記反応チャンバ13及び前記基板Sは約300 ~約600 の温度で予熱することができる。

### [0034]

#### [0035]

前記反応チャンバ13内の圧力が前記洗浄圧力で維持された後、前記基板Sは約800以下の洗浄温度で加熱される。(S11)本発明によれば、前記反応チャンバ13内の圧力は、上述したような前記洗浄圧力で維持される。よって、約800 以下の前記洗浄温度は前記基板Sの表面から好ましくない半導体酸化物を蒸発させるのには十分である。また、前記洗浄温度が800 以下である約600 ~約700 の場合も満足な結果が得られた。

#### [0036]

前記洗浄温度で前記基板Sを加熱する間、または以後の洗浄工程まで前記反応チャンバ13内にキャリアガスが比較的に低い流量、約500sccm以下で注入されることができる。この場合、前記キャリアガスは水素、アルゴン、ネオン、キセノン(xenon)、クリプトンのような不活性ガスまたはこれらの組合せとすることができる。前記反応チャンバ13内に前記キャリアガスを選択的に(optionally)注入することによって、前記基板S上の酸化物から酸素を十分に除去することができ、前記基板S上の清浄な表面での好まない反応を抑制することができる。上述したように、前記反応チャンバ13内を洗浄圧力で排気しながら前記選択的なキャリアガスを注入することによって設定された洗浄条件で前記反応チャンバ13内の酸素ガスの濃度を、その飽和量の約50%以下で維持させることができる。

## [ 0 0 3 7 ]

上述したように、選択的なキャリアガスとして水素が用いられることができるが、この場合、注入される水素の量及び温度は従来の水素ベーク工程で二酸化シリコン(SiO₂)を還元させるために考慮された水素の量及び温度より少なくて低いでだろう。例えば、与えられた反応チャンバでキャリアガスとして注入される水素の流量は従来の水素ベーク工程で用いられる流量の約10%以下、さらには約3%以下とすることができる。

## [0038]

以後、前記基板 S を適切な範囲の洗浄時間の間に前記洗浄圧力及び前記洗浄温度で維持させる。(S 1 3)その結果、前記基板 S 上の汚染物質、例えば前記基板 S の露出したシリコン表面上の自然酸化膜から分解された酸素はすべて除去することができる。露出したシリコン表面の量及び特に自然酸化膜による汚染の程度による前記洗浄温度、前記洗浄圧力及び洗浄される前記基板 S の配置によって前記洗浄時間は約 1 0 秒~約 5 0 0 秒の範囲内で変化することができる。一実施例で、前記洗浄時間は、約 3 0 秒~ 1 2 0 秒、例えば約 6 0 秒とすることができ、この時間の間に十分な洗浄を行うことができる。

# [0039]

前記基板Sを前記洗浄温度及び前記洗浄圧力で前記洗浄時間の間に維持させて洗浄した後、前記反応チャンバ13内に水素ガスを注入することができる。(S15)または前記水素ガス以外に不活性ガスが注入されることができる。前記水素ガスは洗浄が完了した前記シリコン表面を後続のシリコンエピタキシャル工程により適した状態させるために注入される。その後、前記基板Sの温度がエピタキシャル工程温度として調節されることができる。この場合、洗浄が完了した後、エピタキシャル工程温度で追加的な昇温及び温度調

30

40

50

節を最小化させるために前記洗浄温度は後続のエピタキシャル工程温度に近いことが好ま しい。

[0040]

エピタキシャル層の成長に適した温度として前記基板Sを調節した後、前記露出した半導体表面上にエピタキシャル層を成長させる。(S17)前記エピタキシャル層を形成するためのエピタキシャル工程は、前記洗浄工程が実施された前記反応チャンバ13内でインサイチュで実施される。さらに詳しくは、前記反応チャンバ13内に反応ガスを注入する。この場合、前記反応ガスは形成しようとするエピタキシャル層の種類によって決められる。例えば、前記反応ガスは、SiH₄またはSiH₂ Cl₂ のようなシリコンソースガスとすることができる。また、前記反応ガスは、GeH₄ またはGeH₂ Clのようなゲルマニウムソースガスとすることができる。これに加えて、前記反応ガスは他の半導体ソースガスとすることができる。

[0041]

前記基板Sに対する半導体製造工程があらかじめ実施されない場合、すなわち、前記基板S上に導電層、絶縁層、半導体層またはこれらのパターンのような構造物が形成されない場合、前記エピタキシャル層は前記基板Sの全面に形成することができる。一方、エピタキシャル層を形成する前に、前記基板Sに対する半導体製造工程があらかじめ実施された場合には前記エピタキシャル層は露出したシリコン表面及び/またはポリシリコンゲート電極のように露出したポリシリコン表面上にだけ選択的に成長することができる。

[0042]

前記露出した表面上に形成または成長する前記エピタキシャル層は、前記露出した表面と同一物質ではないこともある。すなわち、前記反応ガスとともに前記反応チャンバ13内に適切な量の他の合金元素を注入して物理的または電気的に他の特性を有するエピタキシャル層を形成することができる。このような技術は、ひずみ格子(strainedlattice)層を形成するのに用いられることができるし、AlGaN、InGaN、AlInGaN及びAlPGaNのような三元及び四元化合物半導体層を形成するのに用いられることができる。

[0043]

上述したような洗浄及びエピタキシャル層成長工程を実施した後、第2パージ工程(S19)が実施される。前記第2パージ工程(S19)は、前記反応チャンバ13内に水素ガスまたは一つ以上の不活性ガスを注入することで実施される。また、前記第2パージ工程(S19)が実施されるうちに前記基板Sはエピタキシャル蒸着温度から冷却することができ、前記第2パージ工程(S19)中に注入される水素ガスまたは一つ以上の不活性ガスはこのような冷却工程間に発生することのある好まない反応を抑制することができる

- [0044]

- < 第 2 実施例 >

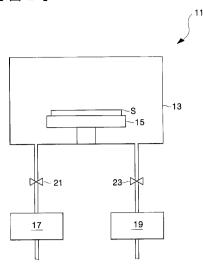

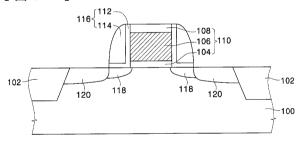

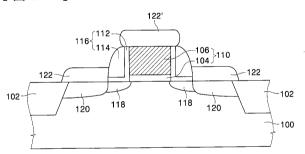

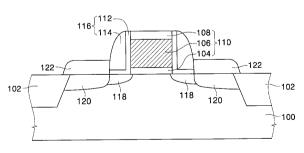

図3Aないし図3Dは、本発明の一実施例による半導体素子の製造工程を示す断面図である。

[0045]

図3Aを参照すると、半導体基板100内に活性領域を画定する素子分離膜102を形成する。前記半導体基板100はシリコン、シリコン/ゲルマニウム、シリコンカーバイドまたはゲルマニウムを含むことができる。ゲートパターン110が前記活性領域上に形成される。前記ゲートパターン110は前記半導体基板100上に積層されたゲート酸化膜104及びゲート電極106を含む。前記ゲート電極106はドーピングされたポリシリコンまたは非晶質シリコン層とすることができる。また、前記ゲート電極106は抵抗減少のためにシリサイド層を含むことができる。これに加えて、前記ゲートパターン110は前記ゲート電極106上に積層されたキャッピング層108を含むことができる。前記キャッピング層108は前記ゲート電極106の上部面を保護するために形成されて、シリコン窒化膜に形成することができる。

20

30

40

50

#### [0046]

図3 Bを参照すると、前記ゲートパターン110を形成した後、LDD(1ight1y doped drain)イオン注入とも呼ばれる初期イオン注入工程を実施して低濃度不純物領域118を形成する。すなわち、前記ゲートパターン110をイオン注入マスクとして用いて前記活性領域内に不純物イオンを注入して低濃度不純物領域118を形成する。次に、前記低濃度不純物領域118が形成された前記半導体基板100上に絶縁膜を形成する。前記絶縁膜はシリコン酸化膜及びシリコン窒化膜を順に積層させて形成することができる。その後、前記絶縁膜を異方性エッチングして前記ゲートパターン110の側壁上にゲートスペーサ116を形成する。この場合、前記ゲートスペーサ116は内部酸化膜スペーサ112及び外部窒化膜スペーサ114を具備するように形成される。

[0047]

前記ゲートスペーサ 1 1 6 を形成した後、前記ゲートパターン 1 1 0 及び前記ゲートスペーサ 1 1 6 をイオン注入マスクとして用いて前記活性領域内に不純物イオンを注入してソース / ドレイン領域 1 2 0 を形成する。前記ソース / ドレイン領域 1 2 0 は前記低濃度不純物領域 1 1 8 より高い不純物濃度を有するように形成される。前記ソース / ドレイン領域 1 2 0 を形成するためのイオン注入工程の後に通常の熱処理を実施して前記ソース / ドレイン領域 1 2 0 内の不純物イオンを活性化させる。一方、前記ソース / ドレイン領域 1 2 0 を形成するための不純物イオン注入工程は、後で説明されるエピタキシャル層を成長させた後に実施することができる。

[0048]

図3 Cを参照すると、前記ゲートパターン110及び前記ソース/ドレイン領域120を有する前記半導体基板100の露出した表面上にエピタキシャル層122を成長させる。上述したように、前記エピタキシャル層122を成長させる工程はその以前に実施される予備洗浄工程(図1のS3)を含むことができる。前記予備洗浄工程を実施することで前記半導体基板100の露出した表面上に存在する汚染物質は殆ど除去できる。

[0049]

前記予備洗浄工程(図1のS3)を実施した後、前記半導体基板100は反応チャンバ内にローディングされる。(図1のS5)次に、第1パージ工程(図1のS7)を実施した後、図1及び図2を参照して説明したようなインサイチュ洗浄工程が実施される。(図1のS9ないしS15)その結果、前記半導体基板100の露出した表面上の残存汚染物質、特に前記予備洗浄を実施した後、前記反応チャンバ内の雰囲気が不酸化雰囲気として成立される前に形成された自然酸化膜が有効に除去される。前記インサイチュ洗浄工程は、従来の水素ベーク工程で用いられた温度より低い温度を使用する。また、水素を使用する場合でも、従来の水素ベーク工程より少ない流量で用いられる。一実施例で、前記インサイチュ洗浄工程は露出した表面を有する前記半導体基板100を約50mTorr以下の圧力及び約650~約750、例えば、約700の温度で約30秒~約180秒、例えば60秒間に維持することを含むことができる。

[0050]

前記インサイチュ洗浄工程に必要となる時間は、前記半導体基板の露出した表面の面積、予備洗浄工程、予備洗浄工程及びインサイチュ洗浄工程間に半導体基板を扱う方法、反応チャンバの容積及びインサイチュ洗浄工程に適用された工程条件のような変数によって影響を受けることができる。

[0051]

前記インサイチュ洗浄工程を実施した後、前記反応チャンバ内の条件及び前記半導体基板 1 0 0 の条件、特に、温度をエピタキシャル層 1 2 2 の成長に適したように設定する。前記エピタキシャル層 1 2 2 を成長させるための条件及び露出した半導体表面の状態によって、前記エピタキシャル層 1 2 2 は前記露出した半導体表面の結晶方向によって単結晶に成長されたり、多結晶、非晶質、またはこれらの組合せによる構造を有するように成長することができる。前記エピタキシャル層 1 2 2 は、SiH₂ Cl₂ 及び / またはGeH₂ Cl₂ のような反応ガス、水素のようなキャリアガス及びHClのようなエッチングガ

スを用いて形成することができる。また、前記エピタキシャル層 1 2 2 を形成する間に前記半導体基板 1 0 0 は約 7 5 0 ~約 8 1 0 、例えば 7 8 0 の温度で維持することができる。

## [0052]

図3 Cに示すように、前記ゲートパターン110が前記キャッピング層108を含む場合、前記エピタキシャル層122は前記半導体基板100の露出した表面、すなわち前記ゲートパターン116によって露出した前記活性領域上に選択的に形成される。これとは違って、図3 Dに示すように前記ゲートパターン110が前記キャッピング層108を含まない場合、すなわち前記ゲート電極106の表面が露出する場合には、前記ゲート電極106の露出した表面上に追加エピタキシャル層122′が前記エピタキシャル層122と同時に形成することができる。前記追加エピタキシャル層122′は多結晶構造を有する前記ゲート電極106上に形成されるので、単結晶構造として成長されず、成長条件によって多結晶または非晶質構造を有するように成長される。

### [ 0 0 5 3 ]

下部の半導体基板材料によって、露出した半導体表面上に形成されるエピタキシャル層は多様な成分を有することができる。例えば、前記エピタキシャル層は実質的に純粋なシリコン、ゲルマニウム、シリコン / ゲルマニウム(Six Gei .x)、及び / またはシリコンカーバイド(Six Ci .x)とすることができる。また、前記エピタキシャル層は二元、三元、または四元化合物半導体とすることができる。以上で上述したような工程を介して形成される前記エピタキシャル層は形成中に反応チャンバ内に適切なソースガスを注入させることによって、ホウ素(boron)、燐(Phosphorous)またはアンチモン(antimony)のような不純物イオンにドーピングすることができる。

#### [0054]

前記エピタキシャル層 1 2 2 を形成した後、第 2 パージ工程を実施することができる。 (図 1 の S 1 9 )前記第 2 パージ工程は前記反応チャンバ内に水素、不活性ガスまたはこれらの混合ガスを注入して前記反応チャンバ内に残存する前記ソースガス及びエッチングガスを除去することによって、冷却中の望まない反応を防止するために実施される。

#### [0055]

## < 比較例 >

実質的に同じ過程によって用意されたシリコン基板上に、下の < 表 1 > に示すように互いに異なるエピタキシャル工程によってトランジスタ試料を製造した。

20

10

## 【表1】

| 工程パラ                                   | ラメータ     | 第1試料                                              | 第2試料  | 第3試料  |  |  |

|----------------------------------------|----------|---------------------------------------------------|-------|-------|--|--|

| 基                                      | 板        | 単結晶シリコン基板                                         |       |       |  |  |

| ゲート                                    | 絶縁膜      | SiON                                              |       |       |  |  |

| ゲート                                    | ・電極      | N型ポリシリコン膜                                         |       |       |  |  |

| 低濃度イ                                   | オン注入     | Arsenic, 4×10 <sup>14</sup> atoms/cm <sup>2</sup> |       |       |  |  |

| 予備                                     | 洗浄       | HF                                                |       |       |  |  |

|                                        | 洗浄ガス     | × (vacuum)                                        | $H_2$ | $H_2$ |  |  |

| ノン・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 温度(℃)    | 700                                               | 850   | 850   |  |  |

| インサイチュ洗浄                               | 圧力(Torr) | 10-4                                              | 5     | 5     |  |  |

|                                        | 時間(秒)    | 6 0                                               | 6 0   | 6.0   |  |  |

|                                        | 半導体ソースガス | SiH <sub>2</sub> Cl <sub>2</sub>                  |       |       |  |  |

| エピタキシャル                                | エッチングガス  | HC l                                              |       |       |  |  |

| 成長工程                                   | 運送ガス     | H <sub>2</sub>                                    | ×     |       |  |  |

|                                        | 温度 (℃)   |                                                   | 7 8 0 |       |  |  |

| ソース/ドレー                                | インイオン注入  | Arsenic, 4×10 <sup>15</sup> atoms/cm <sup>2</sup> |       |       |  |  |

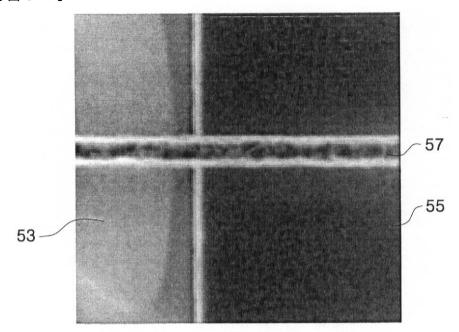

[0056]

[0057]

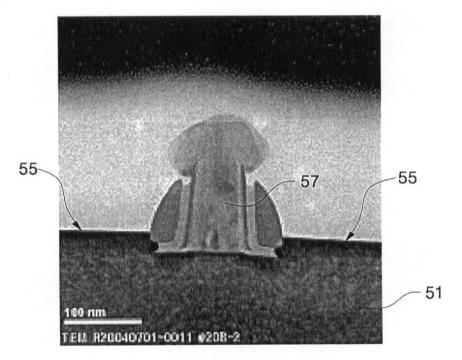

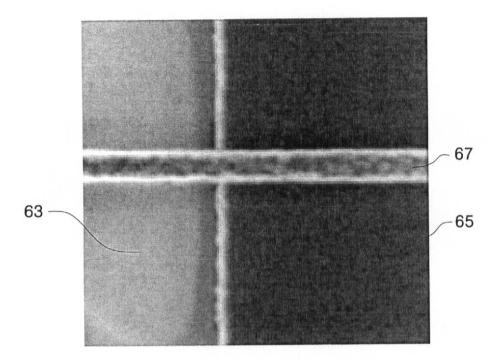

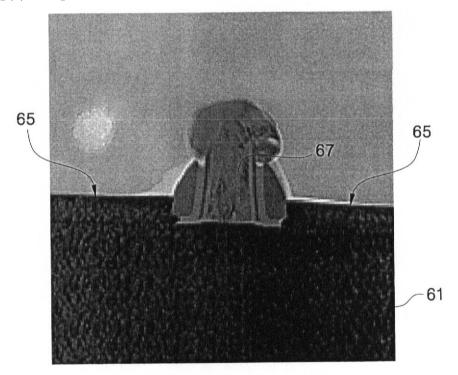

図5 A 及び図5 B は、それぞれ本発明の一実施例によってNMOSソース / ドレイン領域上に選択的に形成されたシリコンエピタキシャル層を示す走査電子顕微鏡(SEM)のイメージ及び透過電子顕微鏡(TEM)のイメージである。図5 B は、図5 A のシリコンエピタキシャル層55 上でゲート電極57を横切る方向に沿って切断した切断面を示している。一方、図6 A 及び図6 B は、それぞれ本発明の一実施例によってPMOSソース / ドレイン領域上に選択的に形成されたシリコンエピタキシャル層を示す走査電子顕微鏡(SEM)のイメージ及び透過電子顕微鏡(TEM)のイメージである。図6 A は、図6 B のシリコンエピタキシャル層65 上でゲート電極67を横切る方向に沿って切断した切断面を示している。

[0058]

図 5 A に示すように、N M O S ソース / ドレイン領域上に形成されたシリコンエピタキシャル層 5 5 は平坦な表面モルフォロジーを示した。一般的に、半導体基板の表面上に自然酸化膜のような汚染物質が除去されない場合、前記自然酸化膜のような汚染物質はエピタキシャル層の表面モルフォロジーに影響を及ぼす。すなわち、半導体基板の表面上における汚染物質の存在は、エピタキシャル層の表面モルフォロジーを悪化させる。図 5 A の結果は、本発明でのように低温でインサイチュ洗浄をする場合にも前記ソース / ドレイン領域上の自然酸化膜のような汚染物質が有効に除去することができることを示している。前記ソース / ドレイン領域上の、すなわち単結晶シリコン基板 5 1 上の汚染物質が有効に

20

10

30

40

除去されたことを、図5Bの結果からさらに確実となる。すなわち、図5Bに示したように前記単結晶シリコン基板51及び前記シリコンエピタキシャル層55は、互いに容易に仕分けできないくらいに良好な界面状態を示している。これは、前記ソース/ドレイン領域上の汚染物質が前記インサイチュ洗浄中に完全に除去されたこととして判断される。

[0059]

図6A及び図6Bに示すように、PMOSソース/ドレイン領域上に形成されたシリコンエピタキシャル層65も、上述したように平坦な表面モルフォロジーを示しており、単結晶シリコン基板61及び前記シリコンエピタキシャル層55は良好な界面状態を示した

【図面の簡単な説明】

[0060]

【図1】本発明の一実施例によるエピタキシャル層の形成方法を説明するための工程フローチャートである。

【図2】本発明の一実施例によるエピタキシャル層の形成方法に用いられることができる 反応チャンバの概路図である。

【図3A】本発明の一実施例による半導体素子の製造工程を示す断面図である。

【図3B】本発明の一実施例による半導体素子の製造工程を示す断面図である。

【図3C】本発明の一実施例による半導体素子の製造工程を示す断面図である。

【図3D】本発明の一実施例による半導体素子の製造工程を示す断面図である。

【図4】本発明の一実施例によって形成されたトランジスタとの比較例によるトランジス タのチャンネル長さとスレッショルド電圧との関係を示すグラフである。

【図 5 A 】本発明の一実施例によって N M O S ソース / ドレイン領域上に選択的に形成されたシリコンエピタキシャル層を示す走査電子顕微鏡( S E M )のイメージである。

【図 5 B】本発明の一実施例によって N M O S ソース / ドレイン領域上に選択的に形成されたシリコンエピタキシャル層を示す透過電子顕微鏡( T E M )のイメージである。

【図6A】本発明の一実施例によってPMOSソース/ドレイン領域上に選択的に形成されたシリコンエピタキシャル層を示す走査電子顕微鏡(SEM)のイメージである。

【図 6 B】本発明の一実施例によって P M O S ソース / ドレイン領域上に選択的に形成されたシリコンエピタキシャル層を示す透過電子顕微鏡( T E M )のイメージである。

【符号の説明】

[0061]

1 1: 処理装置

13:反応チャンバ

15:チャック組立体

17:高真空ポンプ

19:ラフポンプ

21、23:バルブ

1 0 0 : 半導体基板 1 0 2 : 素子分離膜

1 0 4 : ゲート酸化膜

1 0 6 : ゲート電極

108:キャッピング層

1 1 0 : ゲートパターン

1 1 2 : 内部酸化膜スペーサ

1 1 6 : ゲートスペーサ

1 1 8 : 低 濃 度 不 純 物 領 域

120:ソース/ドレイン領域

1 2 2 : エピタキシャル層

\_

40

10

20

# 【図1】

# 【図2】

【図3A】

【図3B】

【図3D】

【図3C】

【図4】

# 【図5A】

# 【図5B】

# 【図6A】

# 【図6B】

### フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 1 L 29/78 (2006.01)

(72) 発明者 申 東石

大韓民国京畿道龍仁市器興邑書川里(番地なし) 現代ホームタウン107棟1402號

(72) 発明者 李 化成

大韓民国京畿道城南市盆唐區九美洞(番地なし) カチマウル大宇アパート106棟402號

(72)発明者 上野 哲嗣

大韓民国京畿道水原市靈通區靈通洞(番地なし) ビョクジョクゴル9-ダンジアパート912棟1006號

(72)発明者 李 浩

大韓民国忠清南道天安市斗井洞(番地なし) デアアイトゥヴィル105棟904號

(72) 発明者 李 承換

大韓民国京畿道水原市靈通區靈通洞(番地なし) シンナムシル5-ダンジアパート雙龍アパート544棟1204號

F ターム(参考) 4K030 AA05 AA06 AA16 AA17 BA02 BA08 BA11 BA38 BB02 CA04

CA12 DA03 FA10 JA05 JA06 JA09 JA10 LA14 LA15

5F045 AA03 AB02 AB05 AB09 AB17 AB18 AD11 AD12 AF02 AF03

AF04 AF05 BB06 BB07 BB12 BB13 BB14 CA05 HA01

5F048 AA07 AC03 BA01 BB05 BB08 BC01 BC05 BC06 DA25 DA27

DA30

5F140 AB03 AC36 BA01 BA02 BA03 BA05 BA09 BA16 BC12 BC19

BF01 BF04 BF08 BF34 BG09 BG12 BG14 BG22 BG29 BG31

BG32 BG53 BH06 BH15 BH21 BH27 BK02 BK08 BK13 BK15

BK18 BK21 CE10