# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**G05F 1/573** (2006.01) **G05F 3/26** (2006.01)

(52) CPC특허분류

**G05F 1/573** (2013.01) **G05F 3/262** (2013.01)

(21) 출원번호

10-2016-0097746

(22) 출원일자

2016년08월01일

심사청구일자 없음

(30) 우선권주장

JP-P-2015-158562 2015년08월10일 일본(JP)

(43) 공개일자

(11) 공개번호

l자 2017년02월20일

10-2017-0018772

(71) 출원인 에스아이아이 세미컨덕터 가부시키가이샤

> 일본국 치바켄 치바시 미하마구 나카세 1쵸메 8반 지

(72) 발명자

엔도 다이키

일본국 치바켄 치바시 미하마구 나카세 1쵸메 8반 지 에스아이아이 세미컨덕터 가부시키가이샤 나이

(74) 대리인

특허법인코리아나

전체 청구항 수 : 총 6 항

# (54) 발명의 명칭 볼티지 레귤레이터

# (57) 요 약

(과제) 제한 전류와 단락 전류를 따로따로 조정할 필요가 없고, 일괄적으로 조정이 가능한 과전류 보호 회로를 구비한 볼티지 레귤레이터를 제공한다.

(해결 수단) 출력 트랜지스터의 출력 전류를 센스하는 트랜지스터로부터 공급되는 전류를 분배하고, 그 분배된 전류에 의해 출력 트랜지스터의 게이트 전압을 제어하여 출력 전류를 제한하는 출력 전류 제한 회로를 구비한 과전류 보호 회로에 있어서, 출력 전류를 센스하는 트랜지스터로부터 분배되는 전류를 상기 출력 트랜지스터가 출력하는 전압에 따라 변화시켜, 그 분배의 비가 구성하는 소자의 사이즈비로 결정되도록 구성한다.

#### 대 표 도

# 명 세 서

# 청구범위

# 청구항 1

출력 트랜지스터와,

상기 출력 트랜지스터가 출력하는 전압을 분압한 분압 전압과 기준 전압의 차를 증폭시켜 출력하여, 상기 출력 트랜지스터의 게이트를 제어하는 제 1 오차 증폭 회로와.

상기 출력 트랜지스터에 과전류가 흐른 것을 검출하고, 상기 출력 트랜지스터의 전류를 제한하는 과전류 보호 회로를 구비한 볼티지 레귤레이터로서,

상기 과전류 보호 회로는,

상기 제 1 오차 증폭 회로의 출력 전압으로 제어되고, 상기 출력 트랜지스터의 출력 전류를 센스하는 제 1 트랜 지스터와,

소스를 접지하고, 게이트와 드레인을 상기 제 1 트랜지스터의 드레인에 접속한 제 2 트랜지스터와,

드레인을 상기 제 1 트랜지스터의 드레인에 접속한 제 3 트랜지스터와,

상기 제 3 트랜지스터의 소스에 접속된 제 1 저항과,

소스를 접지하고, 게이트를 상기 제 2 트랜지스터의 게이트와 드레인에 접속하고, 드레인을 상기 제 1 저항을 개재하여 상기 제 3 트랜지스터의 소스에 접속한 제 4 트랜지스터와,

소스를 접지하고, 게이트를 상기 제 2 트랜지스터의 게이트와 드레인에 접속한 제 5 트랜지스터와,

상기 출력 트랜지스터가 출력하는 전압과 상기 제 1 저항에 인가되는 전압이 동일해지도록 상기 제 3 트랜지스터의 게이트를 제어하는 전압 제어 전압원과,

상기 제 5 트랜지스터에 흐르는 전류에 비례한 전류를 출력하는 커런트 미러 회로를 구비하고,

상기 커런트 미러 회로가 출력하는 전류에 의해, 상기 출력 트랜지스터의 게이트 전압을 제어하는 출력 전류 제한 회로를 구비한 것을 특징으로 하는 볼티지 레귤레이터.

#### 청구항 2

제 1 항에 있어서,

상기 전압 제어 전압원은,

상기 출력 트랜지스터가 출력하는 전압과 상기 제 1 저항에 인가되는 전압의 차를 증폭시켜 출력하여, 상기 제 3 트랜지스터의 게이트를 제어하는 제 2 오차 증폭 회로에 의해 구성되는 것을 특징으로 하는 볼티지 레귤레이터.

#### 청구항 3

제 1 항에 있어서,

상기 전압 제어 전압원은,

소스를 상기 출력 트랜지스터의 출력에 접속하고, 게이트와 드레인을 상기 제 3 트랜지스터의 게이트에 접속하는 제 6 트랜지스터와,

상기 제 6 트랜지스터의 게이트와 드레인에 정전류를 공급하는 제 1 전류원에 의해 구성되는 것을 특징으로 하는 볼티지 레귤레이터.

# 청구항 4

제 3 항에 있어서,

상기 제 1 전류원은,

상기 제 1 오차 증폭 회로의 출력 전압으로 제어되고, 상기 출력 트랜지스터의 출력 전류를 센스하는 제 7 트랜 지스터에 의해 구성되는 것을 특징으로 하는 볼티지 레귤레이터.

#### 청구항 5

제 1 항에 있어서,

상기 커런트 미러 회로는,

소스를 전원 단자에 접속하고, 게이트와 드레인을 상기 제 5 트랜지스터의 드레인에 접속한 제 8 트랜지스터와,

소스를 전원 단자에 접속하고, 게이트를 상기 제 8 트랜지스터의 게이트와 드레인에 접속하고, 드레인으로부터 전류를 출력하는 제 9 트랜지스터에 의해 구성되는 것을 특징으로 하는 볼티지 레귤레이터.

#### 청구항 6

제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 출력 전류 제한 회로는,

상기 커런트 미러 회로의 출력 전류를 전압으로 변환하는 제 2 저항과,

소스를 접지하고, 게이트에 상기 제 2 저항에 발생하는 전압을 입력하는 제 10 트랜지스터와,

상기 제 10 트랜지스터의 드레인으로부터 출력되는 전류를 전압으로 변환하는 제 3 저항과,

소스를 전원 단자에 접속하고, 게이트에 상기 제 3 저항에 발생하는 전압을 입력하고, 드레인을 상기 출력 트랜지스터의 게이트에 접속하는 제 11 트랜지스터에 의해 구성되는 것을 특징으로 하는 볼티지 레귤레이터.

## 발명의 설명

# 기술분야

[0001] 본 발명은 볼티지 레귤레이터에 관한 것으로, 특히 과전류 보호 회로를 구비한 볼티지 레귤레이터에 관한 것이다.

# 배경기술

- [0002] 볼티지 레귤레이터의 과전류 보호 회로에는, 출력의 전류-전압 특성이 수하 (垂下) 특성이 되는 과전류 보호 회로 (수하형 과전류 보호 회로) 와 기 자 특성이 되는 과전류 보호 회로 (기 자형 과전류 보호 회로) 가 있다.

- [0003] 수하형 과전류 보호 회로는, 예를 들어, 특허문헌 1 에 나타내는 바와 같이, 볼티지 레귤레이터의 출력 트랜지스터에 흐르는 전류가 소정의 전류를 초과하지 않게 제한한다. 출력 트랜지스터에 흐르는 제한된 전류 (이하, 「제한 전류」 라고도 한다)는, 제조 공정에서 기인하여 흐트러지기 때문에, 출력 전류를 센스하는 센스트랜지스터가 흘리는 전류를 받는 저항을 복수의 저항 소자에 의해 구성하고, 이것을 트리밍함으로써 저항값을 조정하여, 제한 전류를 원하는 값으로 설정한다.

- [0004] 한편, 7 자형 과전류 보호 회로는, 볼티지 레귤레이터의 출력 단자가 접지 단자에 단락했을 때에 생기는 과대한 손실에 의한 IC 의 파손을 방지하기 위한 회로이며, 예를 들어, 특허문헌 2 에 나타내는 바와 같이, 볼티지레귤레이터의 출력 트랜지스터에 어느 값 이상의 전류가 흐르면 전류 제한을 개시하여, 출력 전압의 저하에 수반하여 출력 전류를 적극적으로 감소시킨다. 또한, 출력 단자가 접지 단자에 단락했을 때에 출력 트랜지스터에 흐르는 전류를 「단락 전류」 라고 한다. 7 자형 과전류 보호 회로에 있어서도, 상기 서술한 수하형과전류 보호 회로와 동일하게, 센스 트랜지스터가 흘리는 전류를 받는 저항을 복수의 저항 소자에 의해 구성하고, 이것을 트리밍함으로써 저항값을 조정하여, 단락 전류를 원하는 값으로 설정한다.

# 선행기술문헌

## 특허문헌

[0005] (특허문헌 0001) 일본 공개특허공보 2003-29856호

(특허문헌 0002) 일본 특허공보 평7-74976호

# 발명의 내용

### 해결하려는 과제

[0006] 종래의 볼티지 레귤레이터에 있어서, 과전류 보호 회로에 의해 수하 특성과 7 자 특성의 양방을 얻기 위해서는, 특허문헌 1 에 기재되는 바와 같은 수하형 과전류 보호 회로와 특허문헌 2 에 기재되는 바와 같은 7 자형 과전류 보호 회로를 병존시킬 필요가 생긴다. 그러나, 상기 서술한 바와 같이, 종래의 수하형 과전류 보호 회로 및 7 자형 과전류 보호 회로에서는, 제조 공정상의 편차에 대해 제한 전류 및 단락 전류를 원하는 값으로 설정하기 위해서는, 양 보호 회로 내의 조정용의 저항의 각각을 복수의 저항 소자에 의해 구성할 필요가 생기므로, 칩 사이즈가 증대된다는 과제가 있다.

[0007] 따라서, 본 발명의 목적은 상기와 같은 과제를 해결하여, 제한 전류와 단락 전류를 따로따로 조정할 필요가 없고, 일괄적으로 조정이 가능한 과전류 보호 회로를 구비한 볼티지 레귤레이터를 제공하는 것에 있다.

# 과제의 해결 수단

[0008]

상기 과제를 해결하기 위해서, 본 발명에 있어서의 볼티지 레귤레이터는, 출력 트랜지스터와, 상기 출력 트랜지스터가 출력하는 전압을 분압한 분압 전압과 기준 전압의 차를 증폭시켜 출력하여, 상기 출력 트랜지스터의 게이트를 제어하는 제 1 오차 증폭 회로와, 상기 출력 트랜지스터에 과전류가 흐른 것을 검출하고, 상기 출력 트랜지스터의 전류를 제한하는 과전류 보호 회로를 구비한 볼티지 레귤레이터로서, 상기 과전류 보호 회로는, 상기 제 1 오차 증폭 회로의 출력 전압으로 제어되고, 상기 출력 트랜지스터의 출력 전류를 센스하는 제 1 트랜지스터와, 소스를 접지하고, 게이트와 드레인을 상기 제 1 트랜지스터의 드레인에 접속한 제 2 트랜지스터와, 드레인을 상기 제 1 트랜지스터의 드레인에 접속한 제 3 트랜지스터의 소스에 접속된 제 1 저항과, 소스를 접지하고, 게이트를 상기 제 2 트랜지스터와, 상기 제 3 트랜지스터의 소스에 접속된 제 1 저항을 개재하여 상기 제 3 트랜지스터의 소스에 접속한 제 4 트랜지스터와, 소스를 접지하고, 게이트를 상기 제 2 트랜지스터의 게이트와 드레인에 접속한 제 5 트랜지스터의, 상기 출력 트랜지스터가 출력하는 전압과 상기 제 1 저항에 인가되는 전압이 동일해지도록 상기 제 3 트랜지스터의 게이트를 제어하는 전압 제어 전압원과, 상기 제 5 트랜지스터에 흐르는 전류에 비례한 전류를 출력하는 커런트 미러 회로를 구비하고, 상기 커런트 미러 회로가 출력하는 전류에 의해, 상기 출력 트랜지스터의 게이트 전압을 제어하는 출력 전류 제한 회로를 구비한 것을 특징으로 한다.

# 발명의 효과

[0009] 본 발명의 과전류 보호 회로를 구비한 볼티지 레귤레이터에 의하면, 제 2 트랜지스터와 제 4 트랜지스터의 사이 즈비에 의해 제한 전류와 단락 전류의 비를 결정하는 것이 가능해진다. 따라서, 제조 공정상의 편차에 의한 제한 전류 및 단락 전류의 변동에 대해서는, 하나의 저항을 트리밍하는 것만으로, 즉 일괄적으로 조정할 수 있고, 따라서, 칩 사이즈의 증대를 억제하는 것이 가능해진다.

#### 도면의 간단한 설명

[0010] 도 1 은, 본 발명의 제 1 실시형태의 과전류 보호 회로를 구비한 볼티지 레귤레이터의 회로도이다.

도 2 는, 본 발명의 실시형태의 과전류 보호 회로를 구비한 볼티지 레귤레이터의 출력 전류-전압 특성을 나타내는 그래프이다.

도 3 은, 본 발명의 제 2 실시형태의 과전류 보호 회로를 구비한 볼티지 레귤레이터의 회로도이다.

도 4 는, 본 발명의 제 3 실시형태의 과전류 보호 회로를 구비한 볼티지 레귤레이터의 회로도이다.

# 발명을 실시하기 위한 구체적인 내용

- [0011] 이하, 본 발명의 실시형태에 대해 도면을 참조하여 설명한다.

- [0012] [실시형태 1]

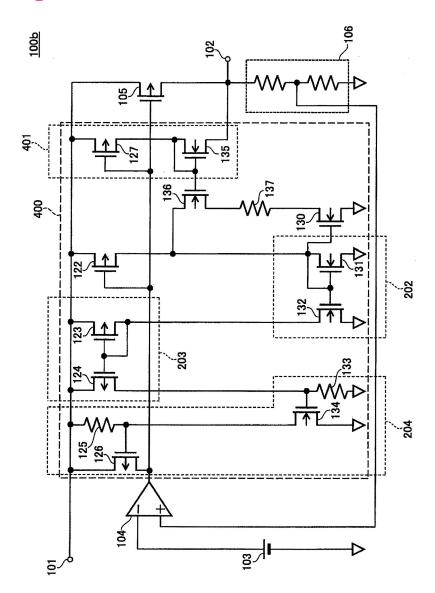

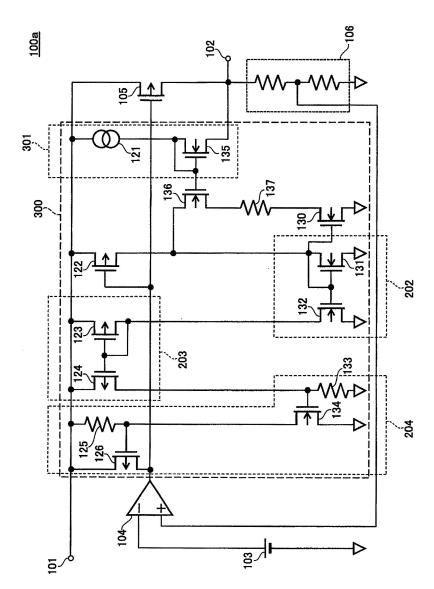

- [0013] 도 1 은, 본 발명의 제 1 실시형태의 과전류 보호 회로를 구비한 볼티지 레귤레이터의 회로도이다.

- [0014] 제 1 실시형태의 볼티지 레귤레이터는, 전원 단자 (101) 와, 출력 단자 (102) 와, 기준 전압 회로 (103) 와, 에러 앤프 (오차 증폭 회로) (104) 와, PMOS 트랜지스터 (출력 트랜지스터) (105) 와, 분압 회로 (106) 와, 과전류 보호 회로 (200) 를 갖는다.

- [0015] 출력 트랜지스터 (105) 는, 게이트가 에러 앰프 (104) 의 출력 단자에 접속되고, 소스가 전원 단자 (101) 에 접속되고, 드레인이 출력 단자 (102) 에 접속된다. 출력 단자 (102) 는 분압 회로 (106) 에 접속된다. 분압 회로 (106) 의 출력 단자는, 에러 앰프 (104) 의 비반전 입력 단자에 접속된다. 에러 앰프 (104) 의 반전 입력 단자에는, 기준 전압 회로 (103) 의 출력 단자가 접속된다.

- [0016] 이상으로부터, 에러 앰프 (104) 는, 분압 회로 (106) 의 출력 단자 전압과 기준 전압 회로 (103) 의 전압을 비교하여, 분압 회로 (106) 의 출력 단자 전압이 기준 전압 회로 (103) 의 전압과 동일해지도록 출력 트랜지스터 (105) 를 구동시킴으로써, 출력 단자 (102) 를 정전압으로 제어한다.

- [0017] 다음으로, 과전류 보호 회로 (200) 에 대해 설명한다.

- [0018] 과전류 보호 회로 (200) 는, PMOS 트랜지스터 (122, 123, 124 및 126) 와, NMOS 트랜지스터 (130, 131, 132, 134 및 136) 와, 저항 (125, 133 및 137) 과, 에러 앰프 (140) 를 구비하고 있다.

- [0019] PMOS 트랜지스터 (122) 는, 게이트가 에러 앰프 (104) 의 출력 단자에 접속되고, 소스가 전원 단자 (101) 에 접 NMOS 트랜지스터 (131) 의 게이트 및 드레인은, PMOS 트랜지스터 (122) 의 드레인에 접속되고, 소 스는 접지 단자에 접속된다. NMOS 트랜지스터 (132) 의 게이트는, NMOS 트랜지스터 (131) 의 게이트 및 드 레인에 접속되고, 소스는 접지 단자에 접속된다. PMOS 트랜지스터 (123) 의 게이트 및 드레인은, NMOS 트랜 지스터 (132) 의 드레인에 접속되고, 소스는 전원 단자 (101) 에 접속된다. PMOS 트랜지스터 (124) 의 게이 트는, PMOS 트랜지스터 (123) 의 게이트 및 드레인에 접속되고, 소스는 전원 단자 (101) 에 접속된다. (133) 은, 일단이 PMOS 트랜지스터 (124) 의 드레인에 접속되고, 타단자가 접지 단자에 접속된다. 랜지스터 (134) 의 게이트는, 저항 (133) 의 일단과 PMOS 트랜지스터 (124) 의 드레인에 접속되고, 소스가 접지 단자에 접속된다. 저항 (125) 은, 일단이 NMOS 트랜지스터 (134) 의 드레인에 접속되고, 타단이 전원 단자 PMOS 트랜지스터 (126) 는, 게이트가 저항 (125) 의 일단과 NMOS 트랜지스터 (134) 의 (101) 에 접속된다. 드레인에 접속되고, 소스가 전원 단자 (101) 에 접속되고, 드레인이 에러 앰프 (104) 의 출력 단자에 접속된다. NMOS 트랜지스터 (136) 는, 드레인이 PMOS 트랜지스터 (122) 의 드레인에 접속되고, 게이트가 에러 앰프 (140) 의 출력 단자에 접속되고, 소스가 저항 (137) 의 일단에 접속된다. 에러 앰프 (140) 는, 비반전 입력 단자가 출력 단자 (102) 에 접속되고, 반전 입력 단자가 NMOS 트랜지스터 (136) 의 소스와 저항 (137) 의 일단 저항 (137) 은, 타단이 NMOS 트랜지스터 (130) 의 드레인에 접속된다. NMOS 트랜지스터 (130) 는, 게이트가 NMOS 트랜지스터 (131) 의 게이트 및 드레인에 접속되고, 소스가 접지 단자에 접속된다.

- [0020] 또한, 에러 앰프 (140) 에 의해 전압 제어 전압원 (201) 이 구성되고, NMOS 트랜지스터 (131 및 132) 에 의해 커런트 미러 회로 (202) 가 구성되고, PMOS 트랜지스터 (123 및 124) 에 의해 커런트 미러 회로 (203) 가 구성되고, 저항 (125), PMOS 트랜지스터 (126), 저항 (133), 및 NMOS 트랜지스터 (134) 에 의해 출력 전류 제한 회로 (204) 가 구성되어 있다.

- [0021] 다음으로 과전류 보호 회로 (200) 의 동작을 설명한다. PMOS 트랜지스터 (122) 는, 게이트 및 소스를 출력 트랜지스터 (105) 와 공통으로 하고 있기 때문에, 출력 트랜지스터 (105) 가 부하에 공급하는 전류에 비례한 전류를 드레인으로부터 흘린다. PMOS 트랜지스터 (122) 의 드레인으로부터 흐르는 전류는, 병렬로 접속된 NMOS 트랜지스터 (131) 와 NMOS 트랜지스터 (136) 로 분배된다.

- [0022] 에러 앰프 (140) 는, 출력 단자 (102) 의 전압과 저항 (137) 에 발생하는 전압을 비교하여, 출력 단자 (102) 의 전압과 NMOS 트랜지스터 (136) 의 소스 전압이 동일해지도록 NMOS 트랜지스터 (136) 의 게이트 전압을 제어한다.

- [0023] 여기서, 출력 단자 (102) 에 과전류가 흐른 상태에서, 출력 단자 (102) 의 전압이 높은 경우를 생각한다. 출력 단자 (102) 의 전압이 높기 때문에, NMOS 트랜지스터 (136) 는, 전류를 흘려 소스 전압이 높아지도록 게이 트 전압을 제어한다. 저항 (137) 과 NMOS 트랜지스터 (130) 는 직렬로 접속되어 있기 때문에, NMOS 트랜지

스터 (130, 131) 로 구성되는 커런트 미러 회로에 의해, 저항 (137) 에 흐르는 전류가 결정된다. NMOS 트랜지스터 (130 과 131) 의 트랜지스터 사이즈비를 n : 1 로 하면, PMOS 트랜지스터 (122) 의 드레인으로부터 흐르는 전류는, NMOS 트랜지스터 (130 과 131) 에 n : 1 로 분배된다. 즉, 출력 전류-전압 특성은 수하 특성을 나타낸다.

- [0024] 다음으로, 출력 단자 (102) 에 흐르는 과전류에 의해, 출력 단자 (102) 의 전압이 저하되었을 경우를 생각한다. NMOS 트랜지스터 (136) 는, 소스 전압이 낮아지도록 게이트 전압을 제어한다. NMOS 트랜지스터 (130) 에 흐르는 전류는, 출력 단자 (102) 의 전압의 저하에 의해, 저항 (137) 에 인가되는 전압 (출력 단자 (102) 의 전압) 과 저항 (137) 의 저항값에 의해 제한된다. 출력 단자 (102) 가 접지 단자에 단락했을 때에 NMOS 트랜지스터 (130) 에 흐르는 전류가, NMOS 트랜지스터 (131) 에 흐르는 전류보다 충분히 작아 무시할 수 있을 것으로 가정하면, PMOS 트랜지스터 (122) 로부터 NMOS 트랜지스터 (131) 로 흐르는 전류의 분배의 비는, n + 1 로 증가한다. NMOS 트랜지스터 (130) 에 흐르는 전류의 감소는, 저항 (137) 의 저항값과 출력 단자 (102) 의 전압에 동일한 저항 (137) 에 인가되는 전압의 저하에 의한 변화이기 때문에, 출력 단자 (102) 의 전압에 대해 선형의 변화가 된다. 즉, 출력 전류-전압 특성은 기자 특성을 나타낸다.

- [0025] NMOS 트랜지스터 (131) 에 흐르는 전류는, 커런트 미러 회로 (202) 와 커런트 미러 회로 (203) 에 의해, PMOS 트랜지스터 (122) 에 흐르는 전류에 비례한 전류로서 저항 (133) 에 인가된다. 저항 (133) 에 발생한 전압은, 저항 (125) 및 NMOS 트랜지스터 (134) 에 의해 구성되는 소스 접지 증폭 회로에 의해 증폭되고, PMOS 트랜지스터 (126) 를 구동시켜 출력 트랜지스터 (105) 에 흐르는 전류를 제한한다.

- [0026] 과전류 보호 회로 (200) 가 출력 트랜지스터 (105) 에 흐르는 전류를 제한하고 있을 때에 저항 (133) 에 발생하 는 전압은, 출력 단자 (102) 의 전압에 상관없이 일정하다. 여기서, 설명을 간략화하기 위해서 PMOS 트랜지 스터 (123, 124) 및 NMOS 트랜지스터 (131, 132) 의 트랜지스터 사이즈비가 동일한 것으로 가정한다. (133) 에 흐르는 전류는, 커런트 미러 회로 (202 및 203) 에 의해 공급되기 때문에, 과전류 보호 회로 (200) 가 출력 트랜지스터 (105) 에 흐르는 전류를 제한하고 있을 때에 NMOS 트랜지스터 (131) 에 흐르는 전류도 일정하 NMOS 트랜지스터 (131) 에 흐르는 전류는, PMOS 트랜지스터 (122) 의 드레인으로부터 흐르는 전류로부 그 분배는 출력 단자 (102) 가 접지 단자에 단락되어 있는 경우와 출력 단자 (102) 의 터 분배된 전류이다. 전압이 높은 경우에서는, n + 1 : 1 이 된다. 과전류 보호 회로 (200) 가 출력 트랜지스터 (105) 에 흐르는 전류를 제한하고 있을 때의 NMOS 트랜지스터 (131) 에 흐르는 전류는 일정하기 때문에, PMOS 트랜지스터 (122) 의 드레인으로부터 흐르는 전류는, 출력 단자 (102) 가 접지 단자에 단락되어 있는 경우와 출력 단자 (102) 의 전압이 높은 경우에서는, 1:n+1이 된다. PMOS 트랜지스터 (122) 는 출력 트랜지스터 (105) 에 흐르는 전류에 비례한 전류이기 때문에, 출력 트랜지스터 (105) 에 흐르는 제한된 전류는, 출력 단자 (102) 가 접지 단 자에 단락되어 있는 경우와 출력 단자 (102) 의 전압이 높은 경우에서는, 1 : n + 1 이 된다.

- [0027] 이상으로부터, 과전류 보호 회로 (200) 는, 구성 소자의 사이즈비, 즉, NMOS 트랜지스터 (130 과 131) 의 사이즈비에 의해 제한 전류와 단락 전류의 비가 결정되기 때문에, 그들 값의 조정은 일괄적으로 실시하는 것이 가능해진다.

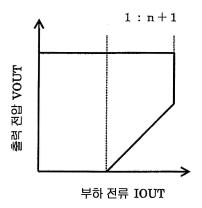

- [0028] 도 2 는, 본 실시형태의 볼티지 레귤레이터 (100) 의 출력 전류 (부하 전류) (IOUT) 와 출력 전압 (VOUT) 의 관계를 나타내는 그래프이다. 출력 트랜지스터 (105) 가 흘리는 부하 전류 (IOUT) 는, 출력 단자 (102) 의 전압인 출력 전압 (VOUT) 의 저하에 따라 감소하고, 출력 단자 (102) 가 접지 단자에 단락했을 때에 흐르는 단락전류와 제한 전류의 비는, 1 : n + 1 과, 구성 소자의 사이즈비로 결정될 수 있다.

- [0029] 또, 제조 공정상의 편차에 대한 제한 전류 및 단락 전류의 조정에 대해서는, 출력 전류 제한 회로 (204) 내의 저항 (133) 의 저항값만을 트리밍에 의해 조정하면 된다. 따라서, 종래는, 수하형 과전류 보호 회로와 기자형 과전류 보호 회로 각각으로 조정 가능한 저항이 필요, 즉 2 개의 조정 가능한 저항이 필요했던 것에 대해, 본 실시형태에 의하면, 하나의 조정 가능한 저항이 있으면 제조 공정상의 편차에 대한 제한 전류 및 단락 전류의 조정이 가능하다. 따라서, 칩 사이즈의 증대를 억제하는 것이 가능해진다.

- [0030] [실시형태 2]

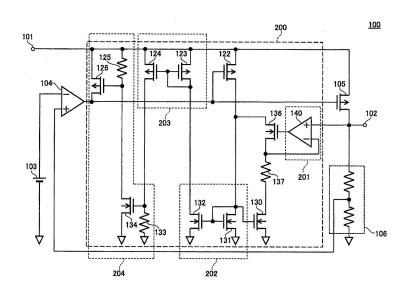

- [0031] 도 3 은, 본 발명의 제 2 실시형태의 과전류 보호 회로 (300) 를 구비한 볼티지 레귤레이터 (100a) 의 회로도이다.

- [0032] 제 2 실시형태의 과전류 보호 회로 (300) 는, 제 1 실시형태에 있어서의 NMOS 트랜지스터 (136) 에 접속하는 에러 앤프 (140) 로 구성된 전압 제어 전압원 (201) 을, 전류원 (121) 과 NMOS 트랜지스터 (135) 로 구성된 전압

제어 전압원 (301) 으로 치환하여 구성하고 있다. 그 밖의 구성은, 도 1 에 나타내는 과전류 보호 회로 (200) 와 동일하기 때문에, 동일한 구성 요소에는 동일한 부호를 부여하고, 중복되는 설명은 적절히 생략한다.

- [0033] 전류원 (121) 은, 일단이 전원 단자 (101) 에 접속되고, 타단이 NMOS 트랜지스터 (135) 의 드레인 및 게이트에 접속된다. NMOS 트랜지스터 (135) 의 소스는, 출력 단자 (102) 에 접속된다. NMOS 트랜지스터 (136) 의 게이트는, NMOS 트랜지스터 (135) 의 게이트 및 드레인에 접속된다.

- [0034] 다음으로 과전류 보호 회로 (300) 의 동작을 설명한다. NMOS 트랜지스터 (136) 의 게이트에는, 전원 단자 (101) 와 출력 단자 (102) 사이에 접속되어 있는, 전류원 (121) 과 NMOS 트랜지스터 (135) 에 의해 분압된 전압이 인가된다. NMOS 트랜지스터 (135) 는, 게이트와 드레인이 단락되어 있기 때문에, NMOS 트랜지스터 (136)의 게이트에는, 출력 단자 (102) 보다 NMOS 트랜지스터 (135)의 임계값 전압분만큼 높은 전압이 인가된다. 또, NMOS 트랜지스터 (136)의 소스에 접속된 저항 (137)에는, NMOS 트랜지스터 (136)의 게이트에 인가되는 전압보다, NMOS 트랜지스터 (136)의 임계값 전압분만큼 낮은 전압이 인가된다. 그 때문에, NMOS 트랜지스터 (135 및 136)가 동일 구조의 소자인 경우에는, 저항 (137)에는 출력 단자 (102)에 동일한 전압이 인가된다. 그 밖의 동작은, 본 발명의 제 1 실시형태의 과전류 보호 회로 (200)와 동일하다.

- [0035] [실시형태 3]

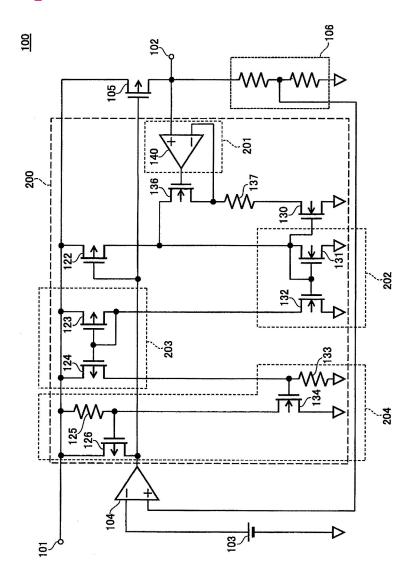

- [0036] 도 4 는, 본 발명의 제 3 실시형태의 과전류 보호 회로 (400) 를 구비한 볼티지 레귤레이터 (100b) 의 회로도이다.

- [0037] 제 3 실시형태의 과전류 보호 회로 (400) 는, 제 2 실시형태에 있어서의 전류원 (121) 과 NMOS 트랜지스터 (135) 로 구성된 전압 제어 전압원 (301) 을, 전류원 (121) 을 PMOS 트랜지스터 (127) 로 치환한 전압 제어 전압원 (401) 으로 구성하고 있다. 그 밖의 구성은, 도 1 에 나타내는 과전류 보호 회로 (100) 와 동일하기 때문에, 동일한 구성 요소에는 동일한 부호를 부여하고, 중복되는 설명은 적절히 생략한다.

- [0038] PMOS 트랜지스터 (127) 는, 게이트가 출력 트랜지스터 (105) 의 게이트에 접속되고, 소스가 전원 단자 (101) 에 접속되고, 드레인이 NMOS 트랜지스터 (135) 의 게이트 및 드레인에 접속된다.

- [0039] 다음으로 과전류 보호 회로 (400) 의 동작을 설명한다. PMOS 트랜지스터 (127) 는, 게이트 및 소스를 출력 트랜지스터 (105) 와 공통으로 하고 있기 때문에, 출력 트랜지스터 (105) 가 부하에 공급하는 전류에 비례한 전류를 드레인으로부터 흘린다. 그 때문에, 출력 트랜지스터 (105) 가 부하에 전류를 공급할 필요가 없는 경부하 구동시에 있어서의 전원 단자 (101) 와 출력 단자 (102) 사이에 접속된 소자가 흘리는 전류에서 기인하는 출력 단자 (102) 의 전압의 상승을 억제할 수 있다. 그 밖의 동작은, 본 발명의 제 1 및 제 2 실시형태의 과전류 보호 회로 (200) 및 과전류 보호 회로 (300) 와 동일하다.

- [0040] 제 2 및 제 3 실시형태에 의한 볼티지 레귤레이터의 출력 전류 (부하 전류) (IOUT) 와 출력 전압 (VOUT) 의 관계는, 도 2 에 나타내는 그래프와 동일해진다.

- [0041] 따라서, 제 2 및 제 3 실시형태의 볼티지 레귤레이터 (100a 및 100b) 에 있어서도, 제 1 실시형태의 볼티지 레귤레이터 (100) 에 의해 얻어지는 상기 서술한 효과와 동일한 효과가 얻어진다.

#### 부호의 설명

[0042] 100, 100a, 100b 볼티지 레귤레이터

101 전원 단자

102 출력 단자

103 기준 전압 회로

104. 140 에러 앰프

105 출력 트랜지스터 (PMOS 트랜지스터)

106 분압 회로

121 전류원

122, 123, 124, 126, 127 PMOS 트랜지스터

125, 133, 137 저항

130, 131, 132, 134, 135, 136 NMOS 트랜지스터

200, 300, 400 과전류 보호 회로

201, 301, 401 전압 제어 전압원

202, 203 커런트 미러 회로

204 출력 전류 제한 회로

# 도면

# 도면1

# 도면2

# 도면3

# 도면4