## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

H01L 21/20 (2006.01) H01L 21/205 (2006.01) H01L 21/28 (2006.01) H01L 21/336 (2006.01)

(21) 출원번호 10-2014-0092027

(22) 출원일자 **2014년07월21일** 심사청구일자 **2019년06월28일**

(65) 공개번호 10-2016-0011301

(43) 공개일자 2016년02월01일

(56) 선행기술조사문헌 US20020109456 A1 (뒷면에 계속) (45) 공고일자 2020년10월29일

(11) 등록번호 10-2171023

(24) 등록일자 2020년10월22일

(73) 특허권자

### 삼성전자주식회사

경기도 수워시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 박홍범

경기도 성남시 분당구 수내로 54 2421호 ( 수내동,보보스쉐르빌)

#### 서동찬

경기도 용인시 수지구 성복1로164번길 20 101동 802호 (성복동,버들치마을성복자이1차아파트)

#### 이관흠

경기도 수원시 영통구 영통로 498 129동 1103호 (영통동,황골마을1단지아파트)

(74) 대리인

특허법인씨엔에스

전체 청구항 수 : 총 10 항

심사관 : 박부식

### (54) 발명의 명칭 반도체 소자 제조방법

#### (57) 요 약

본 발명의 일 실시예는, 반도체 기판의 활성 영역 상에 게이트 전극 구조를 형성하는 단계와, 상기 활성 영역 중 상기 게이트 전극 구조 양측에 위치한 영역에 리세스를 형성하는 단계와, 비활성 기체 플라즈마를 이용하여 상기 리세스를 전처리하는 단계와, 전처리된 상기 리세스에 소스 및 드레인을 위한 에피택결을 성장시키는 단계와, 상기 소스 및 드레인을 위한 에피택결 각각에 소스 전극 구조 및 드레인 전극 구조를 형성하는 단계를 포함하는 반도체 소자 제조방법을 제공한다.

리세스 후 플라즈마 처리와 별도로 또는 병행하여, 콘택홀을 형성하기 위한 식각공정 후에 재성장 전에 식각된 표면을 플라즈마로 처리할 수 있다.

#### 대 표 도 - 도3

(56) 선행기술조사문헌

US20060057810 A1\*

US20080146034 A1

US20110003450 A1

US20110230027 A1

US20140191298 A1\*

KR1020110105575 A\*

KR1020070064346 A\*

\*는 심사관에 의하여 인용된 문헌

### 명 세 서

### 청구범위

#### 청구항 1

반도체 기판의 활성 영역 상에 게이트 전극 구조를 형성하는 단계;

상기 활성 영역 중 상기 게이트 전극 구조 양측에 위치한 영역에 리세스를 형성하는 단계;

비활성 기체 플라즈마를 이용하여 상기 리세스를 전처리하는 단계;

전처리된 상기 리세스에 소스 및 드레인을 위한 에피택셜을 성장시키는 단계; 및

상기 소스 및 드레인을 위한 에피택셜 각각에 소스 전극 구조 및 드레인 전극 구조를 형성하는 단계를 포함하고,

상기 리세스를 전처리하는 단계는, 800kW ~4000kW 범위의 파워를 인가하여 상기 비활성 기체 플라즈마를 발생 시키는 단계를 포함하고, 상기 비활성 기체는 Ar 및 Xe 중 적어도 하나를 포함하는 반도체 소자 제조방법.

### 청구항 2

제1항에 있어서

상기 반도체 기판의 활성 영역은 실리콘 또는 실리콘 게르마늄을 포함하며,

상기 에피택셜은 p형 불순물로 도프된 실리콘 게르마늄을 포함하는 것을 특징으로 하는 반도체 소자 제조방법.

#### 청구항 3

반도체 기판의 활성 영역 상에 게이트 전극 구조를 형성하는 단계;

상기 활성 영역 중 상기 게이트 전극 구조 양측에 위치한 영역에 리세스를 형성하는 단계;

상기 리세스에 제1 에피택셜을 성장시키는 단계;

상기 반도체 기판 상에 층간 절연막을 형성하는 단계;

상기 층간 절연막에 상기 제1 에피택셜에 연결되도록 콘택홀을 형성하는 단계; 및

상기 제1 에피택셜에서 상기 콘택홀에 의해 노출된 영역을 비활성 기체 플라즈마를 이용하여 전처리하는 단계;

전처리된 상기 제1 에피택셜의 노출된 영역에 제2 에피택셜을 재성장시키는 단계; 및

상기 제2 에피택셜에 소스 전극 구조와 드레인 전극 구조를 형성하는 단계를 포함하고,

상기 제1 및 제2 에피택셜은 실리콘 게르마늄을 포함하는 반도체 소자 제조방법.

#### 청구항 4

제3항에 있어서

상기 반도체 기판의 활성 영역은 실리콘 또는 실리콘 게르마늄을 포함하며,

상기 제1 및 제2 에피택셜은 p형 불순물로 도프된 실리콘 게르마늄을 포함하는 것을 특징으로 하는 반도체 소자 제조방법.

#### 청구항 5

제3항에 있어서

상기 제1 에피택셜은  $Si_{1-x}Ge_x$ 이며, 상기 제2 에피택셜은  $Si_{1-y}Ge_y$ 이며, 여기서, 상기 제2 에피택셜의 게르마늄 함량(v)이 상기 제1 에피택셜의 게르마늄 함량(x)보다 큰 것을 특징으로 하는 반도체 소자 제조방법.

### 청구항 6

제3항에 있어서.

상기 리세스를 형성하는 단계와 상기 제1 에피택셜을 성장시키는 단계 사이에, 비활성 기체 플라즈마를 이용하여 상기 리세스를 전처리하는 단계를 더 포함하는 것을 특징으로 하는 반도체 소자 제조방법.

### 청구항 7

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 비활성 기체는 Ar 및 Xe 중 적어도 하나를 포함하는 것을 특징으로 하는 반도체 소자 제조방법.

### 청구항 8

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 리세스를 형성하는 단계 후에 상기 리세스의 표면에 잔유물이 존재하며, 상기 전처리하는 단계 전에 상기 잔유물을 세정하는 공정을 더 포함하는 것을 특징으로 하는 반도체 소자 제조방법.

### 청구항 9

제1항 내지 제6항 중 어느 한 항에 있어서,

상기 활성 영역은 상면과 대향하는 두 측면을 갖는 활성 핀(active fin) 구조로 제공되며,

상기 게이트 전극 구조는 상기 활성 핀의 상면과 두 측면에 접하며 상기 활성 핀과 교차하는 것을 특징으로 하는 반도체 소자 제조방법.

#### 청구항 10

실리콘 또는 실리콘 게르마늄 반도체의 일 영역을 식각하는 단계;

상기 식각된 영역을 비활성 기체 플라즈마에 노출시킴으로써 상기 식각된 영역의 표면을 전처리하는 단계; 및 상기 전처리된 표면에 실리콘 게르마늄 에피택셜층을 성장시키는 단계를 포함하고,

상기 식각된 영역의 표면을 전처리하는 단계는, 800kW ~4000kW 범위의 파워를 인가하여 상기 비활성 기체 플라즈마를 발생시키는 단계를 포함하고, 상기 비활성 기체는 Ar 및 Xe 중 적어도 하나를 포함하는 선택적 에피택셜성장방법.

### 발명의 설명

### 기 술 분 야

[0001] 본 발명은 전계효과 트랜지스터와 같은 반도체 소자에 관한 것이다.

### 배경기술

- [0002] 반도체 제조공정에서, 식각된 표면에 선택적 에피택셜 성장공정이 적용될 경우에, 원하는 에피택셜 성장이 이루어지 않는 문제가 있었다. 이러한 문제는 다양한 반도체 소자를 제조하는데 장애요인으로 작용되어 왔다.

- [0003] 한편, 고집적화, 고성능화의 요구로 인해 CMOS(Complementary Metal Oxide Silicon) 전계 효과 트랜지스터의 크기는 지속적으로 감소해왔다. 하지만, 이에 따른 단채널 효과의 심화로 인해 트랜지스터의 크기 감소에 따른 성능 향상이 어려워지고 있다. 성능 개선을 위해서 채널 영역에서 캐리어 이동도를 향상시키는 연구가활발히 진행되고 있다.

### 발명의 내용

### 해결하려는 과제

[0004] 당 기술 분야에서는 에피택셜의 선택적 성장 또는 재성장할 때에 반도체의 오염된 표면을 전처리하여 그 표면에 서 고품질의 에피택셜을 성장시킬 수 있는 반도체 소자의 제조방법이 요구되고 있다.

### 과제의 해결 수단

- [0005] 본 발명의 일 실시예는, 반도체 기판의 활성 영역 상에 게이트 전극 구조를 형성하는 단계와, 상기 활성 영역 중 상기 게이트 전극 구조 양측에 위치한 영역에 리세스를 형성하는 단계와, 비활성 기체 플라즈마를 이용하여 상기 리세스를 전처리하는 단계와, 전처리된 상기 리세스에 소스 및 드레인을 위한 에피택셜을 성장시키는 단계와, 상기 소스 및 드레인을 위한 에피택셜 각각에 소스 전극 구조 및 드레인 전극 구조를 형성하는 단계를 포함하는 반도체 소자 제조방법을 제공한다.

- [0006] 상기 반도체 기판의 활성 영역은 실리콘 또는 실리콘 게르마늄을 포함할 수 있다. 상기 에피택셜은 실리콘 게르마늄 에피택셜을 포함할 수 있다. 실리콘 게르마늄 에피택셜은 p형 불순물로 도프될 수 있다.

- [0007] 상기 비활성 기체는 Ar 및 Xe 중 적어도 하나를 포함할 수 있다. 상기 비활성 기체 플라즈마는 800kW ~ 4000kW 범위의 파워를 인가함으로써 발생될 수 있다. 이러한 리세스를 전처리하는 단계는, 10s ~ 300s 범위의 시간 동안 실시될 수 있다.

- [0008] 상기 리세스를 형성하는 단계 후에 상기 리세스의 표면에 잔유물이 존재하며, 상기 전처리하는 단계 전에 상기 잔유물을 세정하는 공정을 더 포함할 수 있다.

- [0009] 상기 전처리 단계 후에, 전처리된 상기 리세스의 표면을 산화 또는 질화 시키는 단계와, 상기 산화 또는 질화된 표면을 세정하는 단계를 더 포함할 수 있다.

- [0010] 특정 예에서, 상기 활성 영역은 상면과 대향하는 두 측면을 갖는 활성 핀(active fin) 구조로 제공되며,상기 게이트 전극 구조는 상기 활성 핀의 상면과 두 측면에 접하며 상기 활성 핀과 교차할 수 있다.

- [0011] 본 발명의 일 실시예는, 반도체 기판의 활성 영역 상에 게이트 전극 구조를 형성하는 단계와, 상기 활성 영역 중 상기 게이트 전극 구조 양측에 위치한 영역에 리세스를 형성하는 단계와, 상기 리세스에 제1 에피택설을 성장시키는 단계와, 상기 반도체 기판 상에 충간 절연막을 형성하는 단계와, 상기 충간 절연막에 상기 제1 에피택설에 연결되도록 콘택홀을 형성하는 단계와, 상기 콘택홀에 의해 노출된 상기 제1 에피택셜 영역을 비활성 기체

플라즈마를 이용하여 전처리하는 단계와, 전처리된 상기 제1 에피택셜 영역에 제2 에피택셜을 재성장시키는 단계와, 상기 제2 에피택셜에 소스 전극 구조와 드레인 전극 구조를 형성하는 단계를 포함하는 반도체 소자 제조 방법을 제공한다.

- [0012] 상기 반도체 기판의 활성 영역은 실리콘 또는 실리콘 게르마늄을 포함할 수 있다. 상기 에피택셜 또는 상기 제1 및 제2 에피택셜 중 적어도 하나는 실리콘 게르마늄 에피택셜을 포함할 수 있다. 실리콘 게르마늄 에피택셜은 p 형 불순물로 도프될 수 있다.

- [0013] 상기 제1 에피택셜은 Si<sub>1-x</sub>Ge<sub>x</sub>이며, 상기 제2 에피택셜은 Si<sub>1-y</sub>Ge<sub>y</sub>이며, 여기서, 상기 제2 에피택셜의 게르마늄 함 량(y)이 상기 제1 에피택셜의 게르마늄 함량(x)보다 클 수 있다.

- [0014] 상기 리세스를 형성하는 단계와 상기 제1 에피택셜을 성장시키는 단계 사이에, 비활성 기체 플라즈마를 이용하여 상기 리세스를 전처리하는 단계를 더 포함할 수 있다.

- [0015] 본 발명의 일 실시예는, 실리콘 또는 실리콘 게르마늄 반도체의 일 영역을 식각하는 단계와, 상기 식각된 영역을 비활성 기체 플라즈마에 노출시킴으로써 상기 식각된 영역의 표면을 전처리하는 단계와, 상기 전처리된 표면에 실리콘 게르마늄 에피택셜층을 성장시키는 단계를 포함할 수 있다.

- [0016] 상기한 과제의 해결수단은, 본 발명의 특징을 모두 열거한 것은 아니다. 본 발명의 다양한 특징과 그에 따른 장점과 효과는 아래의 구체적인 실시형태를 참조하여 보다 상세하게 이해될 수 있을 것이다.

#### 발명의 효과

- [0017] 선택적 에피택셜 성장 또는 재성장을 적용할 표면을 비활성 기체 플라즈마를 이용하여 처리함으로써 불순물을 제거하거나 격자를 큐어링할 수 있다.

- [0018] 예를 들어, 실리콘 게르마늄(SiGe)인 경우에, 식각시에 격자 손상과 함께 잔유물로 인해 그 표면에 불순물이 높은 농도로 흡착될 수 있다. 아르곤(Ar) 또는 제논(Xe)과 같은 비활성 기체의 플라즈마로 표면 처리함으로써 불순물의 효과적인 제거와 격자 큐어링을 도모할 수 있다. 실리콘 게르마늄을 스트레서(stressor)로 이용한 전계효과 트랜지스터에서 유익하게 사용될 수 있다.

#### 도면의 간단한 설명

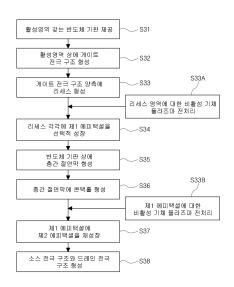

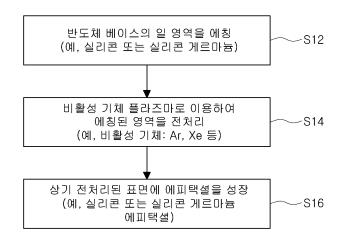

[0019] 도1은 본 발명의 일 실시예에 따른 에피택셜 성장방법을 설명하기 위한 공정 순서도이다.

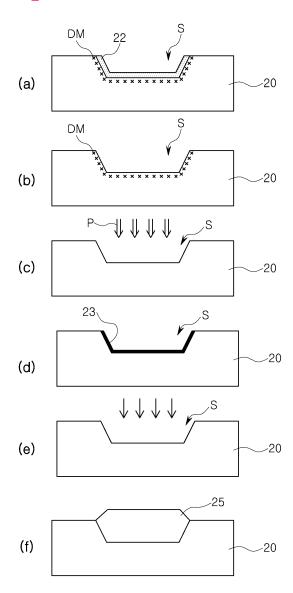

도2a 내지 도2e는 본 발명의 일 실시예에 따른 선택적 에피택셜 성장방법의 주요 공정을 나타내는 단면도이다.

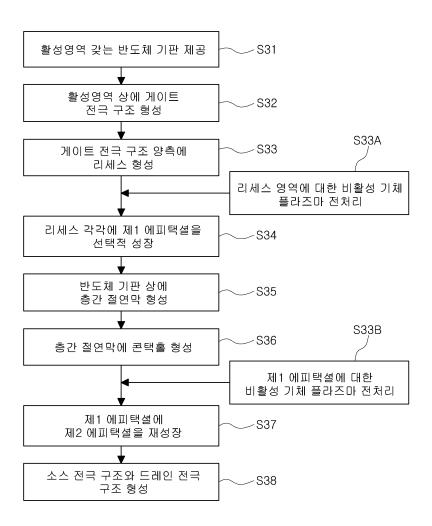

도3은 본 발명의 일 실시예에 따른 반도체 소자의 제조방법을 설명하기 위한 공정 순서도이다.

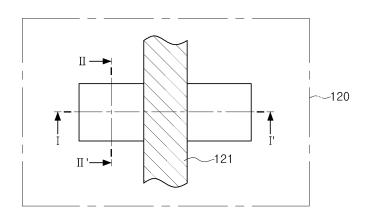

도4는 본 발명의 일 실시예에 따른 반도체 소자를 나타내는 평면도이다.

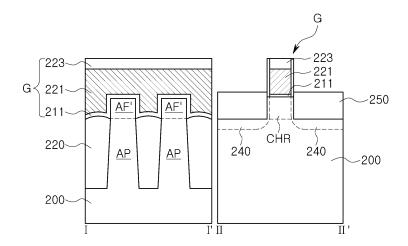

도5 내지 도12는 본 발명의 일 실시예에 따른 반도체 소자의 제조 방법의 주요공정을 나타내는 단면도로서, 도4에 도시된 반도체 소자를 I-I'선 및 II-II'선을 따라 절개한 단면도이다.

도13 내지 도18은 본 발명의 다른 실시예에 따른 반도체 소자의 제조 방법의 주요공정을 나타내는 단면도로서, 도4에 도시된 반도체 소자를 I-I'선 및 II-II'선을 따라 절개한 단면도이다.

도19a 내지 도33a는 본 발명의 일 실시예에 따른 반도체 소자의 제조 방법의 주요 공정을 나타내는 개략 사시도이다.

도19b 내지 도33b는, 각각 도19a 내지 도33a에 도시된 반도체 소자의 단면도이다.

도34는 본 발명의 일 실시예에 따른 반도체 소자를 나타내는 개략 사시도이다.

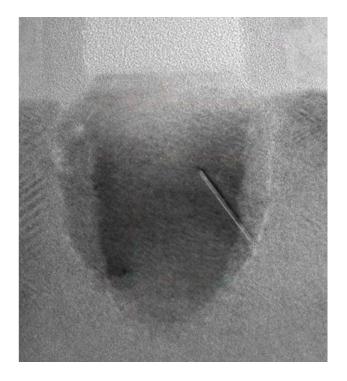

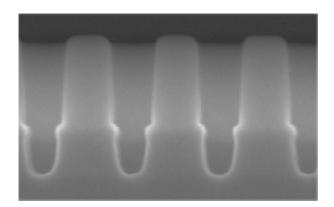

도35a 내지 도35c는 서로 다른 공정 조건에 의한 실험예로서, 리세스 식각 후의 SiGe 선택적 성장 결과를 나타 내는 TEM 사진이다.

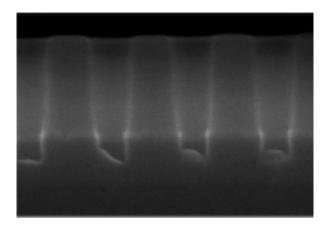

도36a 및 도36b는 서로 다른 공정 조건에 의한 실험예로서, 콘택 식각 후의 SiGe 선택적 성장 결과를 나타내는 TEM 사진이다.

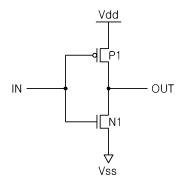

도37은 본 발명의 일 실시예에 따른 반도체 소자가 채용될 수 있는 인버터의 회로도이다.

도38는 본 발명의 일 실시예에 따른 반도체 소자가 채용될 수 있는 SRAM 셀의 회로도이다.

도39 및 도40는 각각 본 발명의 일 실시예에 따른 반도체 소자가 채용될 수 있는 전자 장치 및 저장 장치를 나타낸 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0020] 본 실시예들은 다른 형태로 변형되거나 여러 실시예가 서로 조합될 수 있으며, 본 발명의 범위가 이하 설명하는 실시예로 한정되는 것은 아니다. 또한, 본 실시예들은 당해 기술분야에서 평균적인 지식을 가진 자에게 본 발명을 더욱 완전하게 설명하기 위해서 제공되는 것이다. 예를 들어, 도면에서의 요소들의 형상 및 크기 등은 보다 명확한 설명을 위해 과장될 수 있으며, 도면 상의 동일한 부호로 표시되는 요소는 동일한 요소이다. 본 명세서에서, '상부', '상면', '하면', '측면' 등의 용어는 도면을 기준으로 한 것이며, 실제로는 소자가 배치되는 방향에 따라 달라질 수 있을 것이다.

- [0021] 한편, 본 명세서에서 사용되는 "일 실시예(one example)"라는 표현은 서로 동일한 실시예를 의미하지 않으며, 각각 서로 다른 고유한 특징을 강조하여 설명하기 위해서 제공되는 것이다. 그러나, 아래 설명에서 제시된 실시 예들은 다른 실시예의 특징과 결합되어 구현되는 것을 배제하지 않는다. 예를 들어, 특정한 실시예에서 설명된 사항이 다른 실시예에서 설명되어 있지 않더라도, 다른 실시예에서 그 사항과 반대되거나 모순되는 설명이 없는 한, 다른 실시예에 관련된 설명으로 이해될 수 있다.

- [0022] 도1은 본 발명의 일 실시예에 따른 선택적 에피택셜 성장방법(selective epitaxial growth: SEG)을 설명하기 위한 공정 순서도이다.

- [0023] 도1을 참조하면, 본 방법은 반도체 베이스의 일 영역을 식각하는 단계(S12)로부터 시작될 수 있다.

- [0024] 상기 반도체 베이스는 에피택셜 성장을 위한 단결정일 수 있다. 예를 들어, 상기 반도체 베이스는 실리콘(Si) 또는 실리콘 게르마늄(SiGe)일 수 있다. 특정 기능을 실시하기 위한 반도체 소자를 제조하기 위해서 반도체 베이스의 특정 영역을 선택적으로 식각할 수 있다. 선택적 식각은 건식 식각(dry etching) 또는 습식 식각(wet etching)으로 실시될 수 있다. 에천트와 반응결과물로 인한 불순물이 식각된 영역의 표면에 잔류할 수 있다. 또한, 식각 과정에서 결정표면에 어택이 가해지므로, 격자 손상(lattice damage)이 발생될 수 있다.

- [0025] 이어, 비활성 기체 플라즈마를 이용하여 상기 식각된 영역의 표면을 전처리한다(S14).

- [0026] 본 공정은 챔버 내에서 비활성 기체 플라즈마를 여기시키고, 식각된 영역의 표면을 비활성 기체 플라즈마에 노출시키는 과정으로 실시될 수 있다. 본 공정에서 사용되는 플라즈마 소소는 He, Ar 및 Xe과 같은 비활성 기체일수 있으며, 필요에 따라 N<sub>2</sub> 또는 H<sub>2</sub>와 같은 다른 소스가 혼합되어 사용될 수 있다. 본 공정은 에피택셜 성장 전에 채용되어 식각된 영역의 표면으로부터 불순물을 제거하고 손상된 격자를 큐어링할 수 있다.

- [0027] 다음으로, 전처리된 표면에 에피택셜층을 선택적으로 성장시킬 수 있다(S16). 본 에피택셜층의 성장은, 결정 방향성이 획보되고 불순물이 제거된 면에서 이루어지므로, 고품질의 에피택셜층이 성장될 수 있다.

- [0028] 본 선택적 에피택셜 성장방법은 다양한 형태로 변경되어 실시될 수 있다. 예를 들어, 다른 세정공정 및/또는 다른 큐어링 공정과 결합되어 플라즈마 처리에 의한 효과를 더욱 향상시킬 수 있다. 이러한 실시예로서 본 선택적 에피택셜 성장방법의 다른 실시예가 도2a 내지 도2f에 도시되어 있다.

- [0029] 도2a에 도시된 바와 같이, 반도체 베이스(20)의 일 영역(S)을 식각할 수 있다.

- [0030] 상기 식각된 영역(S)은 후속 공정에서 선택적 에피택셜 성장 영역을 정의할 수 있다. 상기 반도체 베이스(20)는 실리콘 또는 실리콘 게르마늄일 수 있다. 본 선택적 식각에 사용되는 에천트와 그 반응 결과물인 잔유물(22)이 표면에 잔류할 수 있다. 일부 불순물은 상기 식각된 영역(S)의 표면에 흡착될 뿐 아니라 인접한 내부까지 고용되어 표면 영역(DM)에 잔류할 수 있다. 또한, 이러한 표면 영역(DM)은 식각과정에서 물리적 또는 화학적 어택이 가해지므로, 격자 손상(lattice damage)이 발생될 수 있다.

- [0031] 도2b에 도시된 바와 같이, 상기 잔유물(22)이 제거되도록 상기 식각된 영역(S)을 세정할 수 있다.

- [0032] 앞선 공정에 의해 상기 식각된 영역(S)의 표면에 잔유물이 존재할 수 있다. 본 공정은 SiCoNi 같은 식각가스를 이용한 건식 식각 또는 HF 에천트를 이용한 습식 세정에 의해 실시될 수 있다. 상기 잔유물(22)이 제거된 후에 도, 상기 식각된 영역에는 C, N, 0와 같은 불순물이 잔류할 수 있다. 하지만, 그 손상된 표면 영역(DM)에 흡착되거나 고용된 불순물은 통상의 세정공정에 의해 제거되지 않을 수 있다. 또한, 세정 후에도 격자가 손상된 표면 영역(DM)은 큐어링되지 않은 채 격자가 손상된 상태로 남아 있을 수 있다.

- [0033] 도2c에 도시된 바와 같이, 비활성 기체 플라즈마를 이용하여 상기 식각된 영역(S)의 표면을 전처리할 수 있다.

- [0034] 통상적으로 열처리 공정에 의해 결정성을 향상시키기 위한 큐어링이 실시되나, 고온의 열처리 공정이 적용하기 어려울 수 있다. 예를 들어, 실리콘 게르마늄과 같이 녹는점이 낮은 물질(예, SiGe)을 반도체 베이스(21)로 사용하는 경우나, 다른 주변 요소가 고온 환경에 취약한 경우에, 고온의 열처리 공정으로 격자 손상을 큐어링할수 없다.

- [0035] 이러한 문제를 해결하기 위해서, 상기 식각된 영역(S)에 비활성 기체 플라즈마를 이용한 표면 처리공정을 적용한다. 이러한 플라즈마 표면처리는, 공정 챔버 내에서 비활성 기체 플라즈마를 여기시키고, 식각된 영역의 표면을 비활성 기체 플라즈마에 노출시킴으로써 실시될 수 있다. 이러한 플라즈마 처리에 의해 상기 표면 영역(DM)에서 손상된 격자의 큐어링과 함께 불순물의 효과적인 제거가 이루어질 수 있다. 본 공정에서 사용되는 플라즈마 소소는 He, Ar 및 Xe과 같은 비활성 기체일 수 있다.

- [0036] 도2d 및 도2e에 도시된 바와 같이, 전처리된 영역(S)의 표면에서 손상된 격자를 추가적으로 큐어링하기 위해서 산화 또는 질화 처리를 적용할 수 있다. 본 산화 또는 질화 처리에 의해 형성된 산화막 또는 질화막(23)은 간단한 세정공정(예, HF 에천트를 이용한 세정공정)을 통해서 제거될 수 있다.

- [0037] 도2f에 도시된 바와 같이, 전처리된 영역(S)에 에피택셜층(25)을 선택적으로 성장시킬 수 있다.

- [0038] 식각된 영역(S)은 상기 플라즈마 처리에 의해서 불순물이 제거되고 결정 방향성이 회복되어 선택적 에피택셜 성장 공정이 원활하게 이루어질 수 있다. 상기 에피택셜층(25)은 상기 반도체 베이스(21)와 동일한 물질일 수 있다. 예를 들어, 상기 반도체 베이스(21) 및 에피택셜층(25)은 모두 실리콘 게르마늄일 수 있다. 이와 달리, 상기 에피택셜층(25)은 상기 반도체 베이스(21)와 다른 물질일 수 있다. 예를 들어, 실리콘인 반도체 베이스(21)에 에피택셜층(25)으로서 실리콘 게르마늄을 성장시킬 수 있다.

- [0039] 상술된 플라즈마 전처리에 이용한 선택적 에피택셜 성장(SEG)공정은 SEG 공정이 채용되는 다양한 반도체 소자의 제조공정에 유익하게 적용될 수 있다. 예를 들어, 전계효과 트랜지스터(Feild Effect Transistor: FET) 제조공 정에 채용될 수 있다.

- [0040] 전계효과 트랜지스터는 소정의 바이어스 전압을 인가함에 따라, 게이트 전극 아래의 반도체 기판에 채널 영역이 형성될 수 있다. 채널 영역을 통해 다수 캐리어(major carrier)가 이동하며, 캐리어의 이동도(mobility)에 따라 전계효과 트랜지스터의 동작 특성이 결정될 수 있다.

- [0041] 캐리어의 이동도를 향상시키는 방법으로는 채널 영역에 물리적인 스트레스를 가하여 채널 영역의 에너지 밴드 구조를 변경시키는 방법이 있다. 예를 들어, 다수 캐리어가 정공인 PMOS 트랜지스터의 경우, 채널 영역에 압축 응력(compressive stress)을 가하여 정공의 이동도를 향상시킬 수 있다.

- [0042] 구체적으로, 채널 영역의 양측, 즉 소스 영역과 드레인 영역에 반도체 기판(특히, 활성 영역)의 격자보다 큰 격자를 갖는 반도체 물질을 성장시킴으로써 채널 영역에 압축 응력을 인가할 수 있다. 이러한 구조를 구현하기 위해서 선택적 에피택셜 성장(SEG)공정이 적용될 수 있다.

- [0043] 도3은 본 발명의 일 실시예로서 전계효과 트랜지스터의 제조공정을 설명하기 위한 순서도이다. 반도체 소자의 일 예로서 전계효과 트랜지스터 제조방법에서 플라즈마를 이용한 전처리가 적용될 수 있는 시점을 도3을 참조하여 설명하기로 한다.

- [0044] 도3을 참조하면, 본 제조방법은 반도체 기판의 활성 영역을 제공하는 단계(S31)로 시작될 수 있다. 활성영역은 실리콘 또는 실리콘 게르마늄일 수 있다. P-MOSFET인 경우에, 상기 활성 영역은 n형 웰로 제공될 수 있다.

- [0045] 상기 반도체 기판의 활성 영역 상에 게이트 전국 구조를 형성할 수 있다(S32). 필요한 경우에, 게이트 전국 구조를 이용하여 소스와 드레인을 정의하는 불순물 영역을 형성할 수 있다. P-MOSFET인 경우에, 상기 불순물 영역은 보론(B)과 같은 p형 불순물로 도프된 영역일 수 있다.

- [0046] 이어, 상기 활성 영역 중 상기 게이트 전국 구조 양측에 위치한 영역에 리세스를 형성할 수 있다(S33). 불순물 영역을 미리 형성하는 경우에는 리세스는 불순물 영역보다 낮은 깊이로 형성될 수 있다.

- [0047] 다음으로, 상기 리세스에 제1 에피택셜을 성장시킬 수 있다(S34). 제1 에피택셜은 불순물로 도프된 영역일 수 있다. P-MOSFET인 경우에, 제1 에피택셜은 보론(B)과 같은 p형 불순물이 도프된 에피택셜일 수 있다. 상기 제1 에피택셜은 실리콘 게르마늄일 수 있다. 실리콘 게르마늄은 채널 영역에 압축응력을 가하기 위한 스트레서로 작용할 수 있다.

- [0048] 이어, 상기 활성 영역을 덮도록 상기 반도체 기판 상에 충간 절연막을 형성하고(S35), 상기 충간 절연막에 상기 제1 에피택셜에 연결되도록 콘택홀을 형성할 수 있다(S36). 이어 콘택홀을 통해서 상기 제1 에피택셜 영역에 제2 에피택셜을 재성장시킬 수 있다(S37). 제1 에피택셜이 제1 게르마늄 농도를 갖는 실리콘 에피택셜인 경우에, 제2 에피택셜은 제2 게르마늄 농도를 갖는 실리콘 에피택셜일 수 있다. 다음으로, 상기 제2 에피택셜에 소스 전 극 구조와 드레인 전극 구조를 형성할 수 있다(S388).

- [0049] 도3에 나타난 전계효과 트랜지스터의 제조방법에서, 선택적 에피택셜 성장(SEG) 전의 플라즈마 처리는 크게 두시점, 즉 리세스 형성을 식각공정 후 및/또는 콘택홀을 위한 식각공정 후에 채용될 수 있다. 구체적으로, 첫번 째로는, 리세스를 형성하는 공정(S33) 후 그리고 제1 에피택셜을 선택적 성장(S34)하기 전에, 리세스 영역에 비활성 기체 플라즈마를 이용하여 표면 처리할 수 있다(S33A). 두번째로는, 콘택홀을 형성한 공정(S36) 후 그리고 제2 에피택셜을 선택적 성장(S37)하기 전에, 콘택홀에 의해 노출된 상기 제1 에피택셜 영역을 비활성 기체 플라즈마를 이용하여 전처리할 수 있다(S33B). 일 실시예(도5-12 또는 도13-18)에서는, 상기한 두 종의 플라즈마 처리공정 중 하나의 공정만이 채용될 수 있으며, 다른 실시예(도19a-도34)에서는 하나의 제조공정에서도 두 종의 플라즈마 처리 공정이 함께 채용될 수 있다.

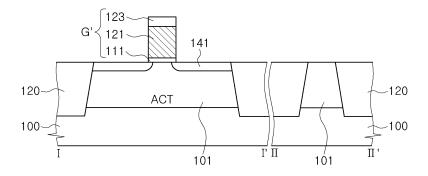

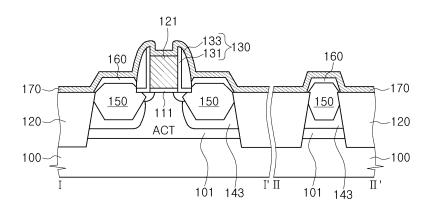

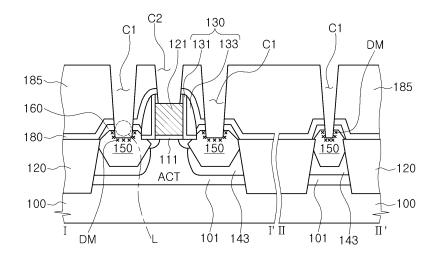

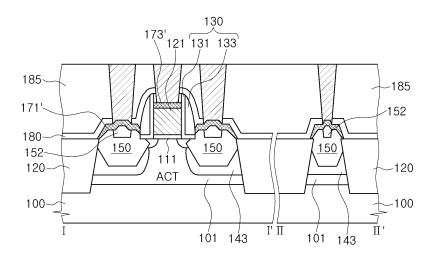

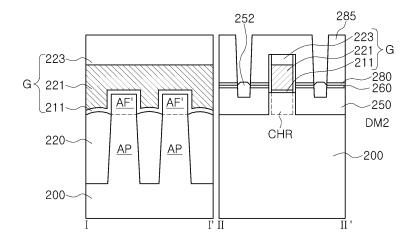

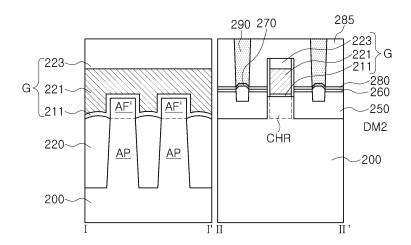

- [0050] 도4는 본 발명의 일 실시예에 따른 반도체 소자를 나타내는 평면도이며, 도5 내지 도12는 본 발명의 일 실시예에 따른 반도체 소자의 제조 방법의 주요공정을 나타내는 단면도로서, 도4에 도시된 반도체 소자를 I-I'선 및 Ⅱ-Ⅱ'선을 따라 절개한 단면도이다.

- [0051] 도4와 함께, 도5를 참조하면, 상기 반도체 기판(100)의 활성 영역(ACT) 상에 게이트 전극구조(G')를 형성할 수 있다.

- [0052] 본 실시예에서 채용된 반도체 기판(100)은 단결정 실리콘 기판일 수 있다. 예를 들어, 상기 반도체 기판(10)은 (100) 면을 갖는 실리콘 기판일 수 있다. 이와 달리, 상기 반도체 기판(100)은 실리콘-온-인슐레이터(silicon on insulator: SOI) 기판, 게르마늄(Ge) 기판, 게르마늄-온-인슐레이터(germanium on insulator: GOI) 기판,

실리콘-게르마늄 기판일 수 있다.

- [0053] 상기 활성 영역(ACT, 101)은 실리콘 또는 실리콘 게르마늄일 수 있다. 상기 활성 영역(ACT, 101)은 소자 분리막 (120)에 의해 형성될 수 있다. 상기 소자 분리막(120)은 반도체 기판(100)에 트렌치를 형성하고 트렌치 내에 절 연 물질을 매립함으로써 형성될 수 있다. 트렌치 내에는 충전된 절연 물질은 갭 필(gap fill) 특성이 우수한 절 연물질일 수 있다. 예를 들어, 이러한 절연물질은 BPSG(boron-phosphor silicate glass), HDP(High Density Plasma) 산화, USG(Undoped Silicate Glass) 또는 TOSZ(Tonen SilaZene) 물질일 수 있다.

- [0054] 반도체 기판(100)은 MOS 트랜지스터들을 형성하기 위해 불순물이 도핑된 웰 영역을 포함할 수 있다. 일 실시예 에 따르면, 반도체 기판(100)은 PMOS 트랜지스터들을 형성하기 위한 n형 웰을 포함할 수 있다.

- [0055] 본 단계에서는, 게이트 전극구조(G')는 활성 영역(ACT, 101) 상에 순차적으로 배치된 게이트 절연막(111), 게이트 전극(121) 및 캡핑막(123)을 포함할 수 있다. 상기 게이트 절연막(111)은 실리콘 산화막, 실리콘 질화막, 실리콘 산질화막 및 고유전막들 중의 적어도 하나를 포함할 수 있다. 상기 고유전막은 실리콘 산화막보다 높은 유전 상수를 갖는 절연성 물질들을 의미하며, 탄탈륨 산화막, 티타늄 산화막, 하프늄 산화막, 지르코늄 산화막, 알루미늄 산화막, 이트륨 산화막, 니오븀 산화막, 세슘 산화막, 인듐 산화막, 이리듐 산화막, BST(barium strontium titanate)막 및 PZT(zirconate titanate)막을 포함할 수 있다. 상기 게이트 절연막(111)은 단일 막일 수도 있으나, 필요에 따라 복수의 막들로 구성될 수 있다.

- [0056] 상기 게이트 전극(121)은 게이트 절연막(111) 상에 배치되며, 활성 영역을 가로지르도록 형성될 수 있다. 예를 들어, 상기 게이트 전극(121)은 불순물이 도프된 폴리실리콘(poly-Si)막으로 형성될 수 있다. 본 실시예와 같이, PMOS 트랜지스터인 경우에는, 게이트 전극(121)은 p형 불순물이 도프된 폴리실리콘막을 포함할 수 있다. 이와 달리, 상기 게이트 전극(121)은 상대적으로 비저항이 낮고, 일함수가 높은 도전 물질로 형성될 수 있다. 예를 들어, 상기 게이트 전극(121)은 일함수가 높은 도전 물질로서, 텅스텐(W) 또는 몰리브덴(Mo)과 같은 금속, 티타늄질화물, 탄탈늄질화물, 텅스텐질화물 및 티타늄알루미늄질화물과 같은 도전성 금속화합물 중 적어도 어느하나로 형성될 수 있다.

- [0057] 추가적으로, 도5에 도시된 바와 같이, 게이트 전극구조(G') 양측의 활성 영역(ACT, 101)에 저농도 불순물 영역 (141)을 형성할 수 있다. 본 실시예와 같이 PMOS 트랜지스터인 경우에는, 상기 저농도 불순물 영역(141)은 보론 (B)과 같은 p형 불순물로 도프될 수 있다. 상기 저농도 불순물 영역(141)은 스페이서(도6의 130)가 없는 게이트 전극구조(G')를 마스크를 이용하는 이온 주입 공정으로 형성될 수 있다. 저농도 불순물 영역(141)의 일부 영역은 불순물 확산에 의해 게이트 전극 구조(G)의 하부로 연장될 수 있다. 본 단계에서 형성된 저농도 불순물 영역은 후속 공정에서 형성될 고농도 불순물 영역(도6의 143)과 함께 소스 및 드레인 영역을 위한 불순물영역으로 제공될 수 있다.

- [0058] 필요에 따라, 상기 저농도 불순물 영역(141)을 형성한 후에, 할로 이온 주입 공정을 실시하여 채널 불순물 영역 (미도시)을 형성할 수 있다. 여기서, 채널 불순물 영역은 소오스/드레인 영역의 도전형과 반대되는 n형의 불순물(예를 들어, 비소(As)을 이온 주입하여 형성될 수 있다. 이러한 채널 불순물 영역은 게이트 전극(121) 아래의 활성 영역(ACT)의 캐리어 농도를 증가시켜, 펀치 쓰루우(punch through) 현상을 방지할 수 있다.

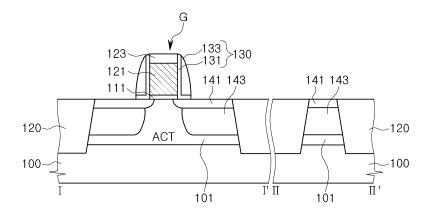

- [0059] 이어, 도6에 도시된 바와 같이, 도5에 도시된 게이트 전극 구조(G')의 양측벽에 스페이서(130)를 형성하여 원하는 게이트 전극 구조(G)를 얻을 수 있다.

- [0060] 상기 스페이서(130)는 복수의 스페이서(131,132)로 제공될 수 있으며, 식각 선택성을 갖는 절연 물질들이 번갈 아 적층된 구조를 가질 수 있다.

- [0061] 구체적으로, 본 실시예에서, 상기 스페이서(130)는 게이트 전극(121)이 형성된 반도체 기판(100)의 전면에 절연 막을 콘포멀하게 증착한 후, 에치백(etch back) 공정과 같은 전면 이방성 식각 공정을 실시하여 형성될 수 있다. 보다 구체적으로 설명하면, 게이트 전극(121)이 형성된 반도체 기판(100)의 전면에 실리콘 산화막 및 실리콘 질화막을 순서대로 컨포멀하게(conformally) 형성할 수 있다. 상기 실리콘 산화막은 화학기상증착(CVD) 또는 열산화공정으로 형성될 수 있다. 이러한 실리콘 산화막은 게이트 전극(121)의 측벽에 발생된 식각 손상을 큐어링(curing)할 수 있다.

- [0062] 이어, 차례로 적충된 실리콘 산화막 및 실리콘 질화막을 에치 백함으로써, 게이트 전극(121) 양측벽에 L자 형태의 제1 스페이서(131)와 그 위에 배치된 제2 스페이서(133)를 갖는 이중 스페이서(130)가 형성될 수 있다. 이로

써, 원하는 게이트 전국 구조(G)가 형성될 수 있다. 본 실시예와 같이, 이중 스페이서(130)를 구비함으로써, 반도체 소자의 고집적화에 따라 소스/드레인 영역 간의 거리인 채널 길이가 감소되는 단채널 효과(short channel effect)를 해소할 수 있다.

- [0063] 상기 이중 스페이서(130)를 형성한 후, 게이트 전극 구조(G) 양측의 반도체 기판(100) 내에 고농도 불순물 영역 (143)을 형성할 수 있다. 상기 고농도 불순물 영역(143)은 스페이서(130)를 구비한 게이트 전극구조(G)를 이온 주입 마스크로 이용하여 P형 불순물, 예를 들어 붕소(B)를 주입하여 형성될 수 있다. 여기서, 고농도 불순물 영역(143)은 후속 공정에서 형성될 리세스(도7의 "R")의 깊이보다 깊게 형성될 수 있다. 상기 고농도 불순물 영역 (143)의 일부도 스페이서(130) 아래로 확산될 수도 있다.

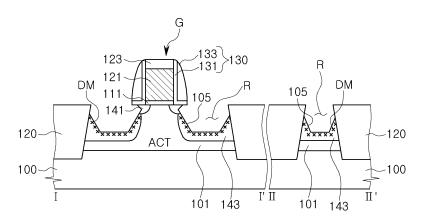

- [0064] 이어, 도7에 도시된 바와 같이, 게이트 전극 구조(G) 양측의 활성 영역(ACT)을 선택적으로 식각하여 리세스(R)을 형성할 수 있다.

- [0065] 상기 리세스(R)는 게이트 전극 구조(G)를 식각 마스크로 이용하여 이방성 및/또는 등방성 식각하여 형성될 수 있다. 본 실시예에서, 리세스(R)는 게이트 전극 양측에 각각 제공되며, 반도체 기판(100)의 표면과 평행한 바닥 면과 반도체 기판(100)의 표면에 대해 경사를 갖는 측면들에 의해 정의될 수 있다. 또한, 리세스 (R)은 게이트 전극(121)과 소자 분리막(120) 사이의 반도체 기판(100)에 형성될 때, 리세스 영역(R)은 소자 분리막(120)의 측 벽을 노출시킬 수도 있다.

- [0066] 상기 반도체 기판(100)이 (100) 면을 가질 경우, 리세스(R)의 바닥면은 (100)면을 가질 수 있으며, 게이트 전극 구조(G)에 인접한 측면은 (111) 면 (110) 면 및 (311) 면을 가질 수 있다. 본 실시예와 같이, 리세스(R)은 게이 트 전극 구조(G) 하부로 연장될 수도 있다.

- [0067] 리세스(R)은 저농도 및 고농도 불순물 영역(141,143)을 노출시킬 수 있다. 반면에, 리세스(R)는 n웰 또는 반도체 기판(100)을 노출시키지 않을 수 있다. 예를 들어, 반도체 기판(100)의 표면으로부터 리세스(R)의 깊이는 약 300~1000Å일 수 있다.

- [0068] 앞서 설명한 바와 같이, 리세스(R)는 게이트 전극 구조(G)를 식각 마스크로 이용하여 반도체 기판(100)(특히, 활성 영역(ACT))을 식각함으로써 얻어질 수 있다.

- [0069] 구체적인 예에서, 상기 게이트 전극 구조(G)와 함께 소자 분리막(120)을 식각 마스크로 이용하여 활성 영역 (ACT)에 등방성 또는 이방성 건식 식각 공정을 실시하여 트렌치를 형성할 수 있다. 이때, 에천트로서 HCl, Cl<sub>2</sub> 및 H<sub>2</sub>가 이용될 수 있다. 이방성 식각 공정에 의해 형성된 트렌치는 리세스 영역(R)의 깊이보다 얕게 형성될 수 있다. 이어, 트렌치에 식각액을 공급하여 등방성 식각을 적용함으로써 리세스(R)의 바닥면 및 측면들이 특정 결정면으로 제공될 수 있다. 보다 상세하게, 등방성 식각 공정의 식각액으로서, 유기 알칼리 에천트(수산화테트라메틸암모늄: TMAH) 또는 수산화암모늄(NH4OH)이 이용될 수 있다. 등방성 식각 공정에 의해 트렌치가 확장되어리시스 영역(R)이 형성될 수 있다. 즉, 등방성 식각 공정은 수직 방향뿐만 아니라 수평 방향으로 반도체 기판(100)을 식각할 수 있으며, 이 과정에서, 리세스(R)의 일부가 스페이서(130) 하부의 반도체 기판(100)이 식각될 수 있다.

- [0070] 한편, 실리콘으로 이루어진 반도체 기판(100)을 습식 식각할 때, 실리콘의 결정면 및 결정 방향에 따라 식각 속도가 다르게 나타난다. 구체적으로, 실리콘의 결정면(plane)에 따라 식각 속도가 다르게 나타날 수 있다. 예를 들어, 수산화암모늄(NH4OH)을 이용하여 실리콘 기판을 등방성 식각할 때, 실리콘 기판은 (111) 면에서 식각 속도가 가장 느리고, (100) 면에서 식각 속도가 가장 빠른 특성을 갖는다. 따라서, 수산화암모늄(NH4OH)을 이용하여 등방성 식각 공정을 진행하는 경우, 식각 속도가 가장 느린 (111) 면이 리세스(R)의 측면을 정의할 수 있으며, 리세스(R)는 스페이서(130) 하부에서 (111) 면을 갖는 두 개의 측면들에 의해 뾰족한 쐐기 형상을 가질 수 있다.

- [0071] 이와 달리, 리세스(R)은 CVE(Chemical Vapor Etching)와 같은 이방성 건식 식각 공정을 실시하여 형성될 수 있다. 다. 식각 가스로서 HCl 및 H<sub>2</sub>를가 사용될 수 있다.

- [0072] 상술된 이방성 및/또는 등방성 식각 공정에 의해 리세스(R)는 그 표면뿐만 아니라, 그와 인접한 내부 영역까지 에천트로 인한 불순물로 오염되고, 결정이 손상될 수 있다. 이와 같이, 식각공정에 의해 오염되고 손상된 표면 영역(DM)은 리세스(R) 형성공정이 완료한 후에 세정공정이 적용될 수 있다. 예를 들어, SiCoNi 같은 식각가스를

이용한 건식 식각 또는 HF 또는  $O_3$  및 HF를 이용한 습식 세정공정이 사용될 수 있다. 하지만, 이러한 세정공정에 의해서 리세스(R)의 표면 상에 존재한 산화막과 같은 잔유물층은 제거되어도, C, N, O와 같은 불순물 원소는 표면에 흡착되거나 고용되어 잔류할 수 있으며, 이러한 세정공정에 의해 효과적으로 제거되지 않을 수 있다. 특히, 세정 후에도 격자가 손상된 표면영역(DM)이 효과적으로 큐어링되지 않는다. 이러한 불순물 원소의 잔류와 격자 손상은 후속 에피택셜 성장을 실시하는데 큰 장애요인이 될 수 있으므로, 도8에 도시된 플라즈마를 이용한 전처리 공정이 요구된다.

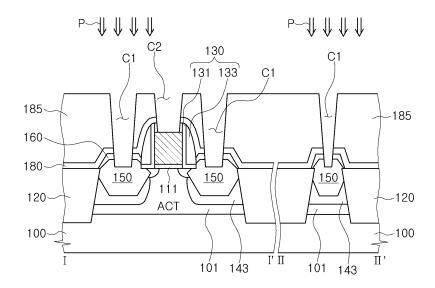

- [0073] 다음으로, 도8에 도시된 바와 같이, 비활성 기체 플라즈마(P)를 이용하여 상기 리세스(R)를 전처리할 수 있다.

- [0074] 본 공정은 공정 챔버 내에서 소정의 압력에서 파워를 인가하여 비활성 기체소스로부터 플라즈마를 여기시키고, 여기된 플라즈마에 리세스를 노출시킴으로써 실시될 수 있다. 비활성 기체 플라즈마 처리는 저온에서 실시될 수 있으며, 손상된 표면에 높은 에너지를 제공할 수 있다. 따라서, 통상의 세정 공정에서 제거되지 않는 표면에 흡착/고용되었던 불순물 원소가 효과적으로 제거될 수 있을 뿐만 아니라, 손상된 격자를 효과적으로 큐어링할 수 있다. 본 공정에서 사용되는 플라즈마 소소는 He, Ar 및 Xe과 같은 비활성 기체일 수 있다. 필요에 따라, H<sub>2</sub> 및 /또는 N<sub>2</sub>도 사용될 수 있다. 특정한 예에서는, 원자사이즈가 작은 소스(He,H<sub>2</sub> 또는 N<sub>2</sub>)보다는 원자사이즈가 큰 Ar 또는 Xe이 플라즈마 처리 과정에서 더 깊은 영역까지 영향을 줄 수 있으므로, 더 큰 효과를 기대할 수 있다. Ar 또는 Xe과 같은 플라즈마 소스는 SiGe과 같은 반도체의 경우에 유용하게 사용될 수 있다.

- [0075] 구체적으로, 비활성 기체 플라즈마는 800kW ~ 4000kW 범위의 파워를 인가하여 전처리에 사용되는 플라즈마를 발생시킬 수 있다. 파워수단으로는 RF 파워 외에도 직류 또는 교류 파워가 사용될 수 있다. 플라즈마를 이용한 처리는 비교적 저온(600℃이하)에서 실시될 수 있다. 특정 예에서는 500℃이하에서 실시될 수 있다. 이에 한정되지는 않으나, 플라즈마를 이용한 처리는 0.1~10 torr의 압력 조건에서 실시될 수 있으며, 전처리 시간은 10s~300s 범위의 시간 동안 실시될 수 있다.

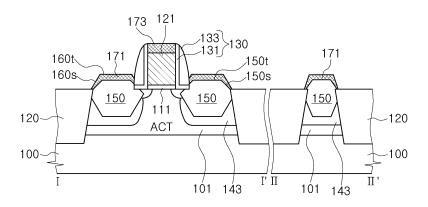

- [0076] 이어, 도9에 도시된 바와 같이, 선택적 에피택셜 성장(Selective Epitaxial Growth; SEG) 공정을 실시하여, 리세스(R) 내에 SiGe 에피택셜(150)을 형성할 수 있다.

- [0077] SiGe 에피택셜(150)은 선택적 에피택셜 성장 공정에 의해, 리세스(R)에 노출된 영역에서만 선택적으로 성장될수 있다. 앞선 공정에서 플라즈마를 이용한 전처리에 의해서 상기 리세스(R)는 결정성장에 유리한 표면을 가질수 있으므로, 본 성장공정에서 원하는 품질의 에피택셜을 성장시킬 수 있다.

- [0078] 본 실시예와 같이, PMOS 트랜지스터의 경우에는 앞서 설명한 바와 같이, 채널영역에 압축 응력을 인가하기 위해서, 상기 반도체 기판(100)의 실리콘보다 격자 상수가 큰 SiGe 에피택셜(150)이 형성될 수 있다. 상기 SiGe 에피택셜(150)은 반도체 기판(100)의 노출된 영역에 성장되므로, 반도체 기판(100)의 실리콘과 동일한 결정구조를 가질 수 있다.

- [0079] 예를 들어, 실리콘 게르마늄(Si<sub>1-x</sub>Ge<sub>x</sub>, 0<x<1)으로 형성될 수 있다. Ge 결정의 격자상수는 Si 결정의 격자상수 보다 크므로, 실리콘 결정의 격자 내에서 Si 원자가 Ge 원자로 치환될수록 Si<sub>1-x</sub>Ge<sub>x</sub>(0<x<1)격자가 더 커질 수 있다. SiGe 에피택셜(150)이 리세스(R)에 성장되면, PMOS 트랜지스터의 채널 영역에 압축 응력을 발생시키고, Ge 의 농도가 증가할수록 에피택셜(150)의 격자가 커지므로 채널영역에 가해지는 압축 응력은 증가될 수 있다.

- [0080] 본 실시예에서, SiGe 에피택셜(150)은 하부 영역에서보다 상부 영역에서 Ge의 농도가 클 수 있다. SiGe 에피택셜(150)의 하부영역은 실리콘으로 이루어진 반도체 기판(100) 간의 격자 부정합을 최소화하면서 원하는 수준의고농도를 상부영역에서 얻을 수 있다. 이와 같이, SiGe 에피택셜(150)은 저농도의 하부영역과 고농도의 상부영역을 포함할 수 있다. 예를 들어, 하부영역은 약 20 내지 50mm의 두께를 가질 수 있으며, 하부영역의 Ge 농도는 10 내지 30%일 수 있다. 상부영역은 약 40 내지 60mm의 두께를 가질 수 있으며, 상부영역의 Ge 농도는 20 내지50%일 수 있다. 특정 예에서, SiGe 에피택셜(150)의 Ge 농도는 하부에서 상부로 점차 증가하는 구배(gradient)를 가질 수 있다.

- [0081] 상기 SiGe 에피택셜층(150)은 고상 에피택시(SPE: Solid Phase Epitaxy), 기상 에피택시(VPE: Vapor Phase

Epitaxy) 및 액상 에피택시(LPE: Liquid Phase Epitaxy) 방법 중 어느 하나로 성장될 수 있다. 예를 들어,, 기상 에피택시 방법으로는 화학기상증착법(Chemical Vapor Deposition; CVD), 감압화학기상증착법(Reduced Pressure Chemical Vapor Deposition; RPCVD) 또는 고진공화학기상증착법(Ultra High Vacuum Chemical Vapor Deposition)이 이용될 수 있다.

- [0082] SiGe 에피택셜(150)의 선택적 성장 공정은 실리콘 소스 가스 및 게르마늄 소스 가스과 함께 선택적 식각 가스를 동시에 공급하여 실시될 수 있다. 선택적 식각 가스는 실리콘 소스 가스와 공급되어 산화막 또는 질화막인 소자 분리막(120)에서는 SiGe 에피택셜(150)이 형성되지 않고 실리콘(Si)이 노출된 리세스 영역에서만 SiGe 에피택셜 충(150)이 선택적으로 성장될 수 있다.

- [0083] 실리콘 소스 가스로는 모노클로실레인(SiH3Cl), DCS(DiChloroSilane), TCS(TriChloroSilane), HCS(HexaChloroSilane), SiH₄, Si₂H₆ 또는 이들의 조합이 사용될 수 있다. 게르마늄 소스 가스로는 GeH₄, Ge₂H₄, GeH₃Cl, Ge₂H₂Cl₂, Ge₃HCl₃ 또는 그 조합이 사용될 수 있다. 선택적 식각 가스는 HCl, Cl₂ 또는 이들의 조합이 사용될 수 있다. 선택적 에피택셜 성장 과정에서, 상기한 실리콘 및 게르마늄 소스 가스들이 반도체 기판(100)의 표면에 컨포멀하게 공급될 수 있도록, 캐리어 가스를 이용할 수 있다. 상기 캐리어 가스는 수소 가스, 헬륨 가스, 질소가스 및 아르곤 가스 중 적어도 어느 하나일 수 있다. 이에 한정되지는 않으나, SiGe 에피택셜(150)의 성장 공정은 약 550℃ 이상의 온도 및 수 mTorr 이상의 압력에서 실시될 수 있다. 또한, SiGe 에피택셜층(150)의 의 성장 속도는 실리콘 소스 가스와 게르마늄 소스 가스의 비율에 따라 변화할 수 있다.

- [0084] 본 실시예와 같이, 선택적 에피택셜 성장 공정에 의해 SiGe 에피택셜층(150)은 스페이서(130) 하부의 쐐기 형상의 리세스 영역(R)을 채울 수 있으며, 이로써 채널 영역에 가해지는 압축 응력을 더욱 증가시킬 수 있다. SiGe 에피택셜층(150)은 반도체 기판(100)의 표면 위로 융기(elevated)될 수 있다. SiGe 에피택셜(150)의 두께가 증가될수록 채널 영역에 가해지는 압축 응력이 더욱 증가될 수 있다. 예를 들어, SiGe 에피택셜층(150)의 융기된 높이는 약 10mm 내지 40mm 범위일 수 있다.

- [0085] 상기 SiGe 에피택셜(150)은 특정 도전형 불순물으로 도프된 에피택셜일 수 있다. 본 실시예에서, 특정 도전형 불순물은 보론(B)과 같은 p형 불순물일 수 있다. SiGe 에피택셜(150)의 불순물 도핑은 에피택셜 성장과정에서 인-시츄(insitu)로 p형 불순물을 도핑하는 방식으로 실시될 수 있다. 이와 달리, 선택적 에피택셜 성장 후에 상기 SiGe 에피택셜(150)에 p형 불순물을 이온 주입함으로써 실시될 수도 있다. 이와 같이, p형 불순물이 도핑된 SiGe 에피택셜(150)은 저농도 및 고농도 불순물 영역들(141, 143)과 함께 소스/드레인 영역으로 제공될 수 있다.

- [0086] 본 실시예에서는, SiGe 에피택셜(150)이 반도체 기판(100)의 표면 위로 융기된 것을 예시하였으나, SiGe 에피택 셜(150)은 상기 반도체 기판(100)의 표면보다 아래에 위치할 수도 있다.

- [0087] 추가적으로, 도9에 도시된 바와 같이, SiGe 에피택셜층(150) 상에 실리콘 캡핑층(160)을 형성할 수 있다. 실리콘 캡핑층(160)은 SiGe 에피택셜(150)의 상면을 덮을 수 있다. 예를 들어, 실리콘 캡핑층(160)의 두께는 약 10 내지 30㎜일 수 있다. 실리콘 캡핑층(160)은 후속공정에서 실리사이드막을 형성하는데 사용되며, 실리사이드 형성과정에서, 실리사이드막이 SiGe 에피택셜(150) 계면으로 침투하여 반도체 기판(100)과 반응하는 것을 방지할수 있다. 상기 실리콘 캡핑층(160)은 SiGe 에피택셜(150)과 유사한 선택적 에피택셜 성장공정으로 형성될 수 있다.

- [0088] 다음으로, 도10 및 도11에 도시된 바와 같이, 실리콘 캡핑층(160)을 형성한 후에 게이트 전극(121) 및 SiGe 에 피택셜(150) 상에 실리사이드막(171, 173)을 형성할 수 있다.

- [0089] 실리사이드막들(171, 173)은 실리콘 원소 및 금속 원소를 포함할 수 있다. 예를 들어, 코발트 실리사이드막, 티타늄 실리사이드막, 니켈 실리사이드막 또는 텅스텐 실리사이드막 중 어느 하나일 수 있다. 실리사이드막들 (171, 173)은 실리콘 원소 및 금속 원소의 함량이 90% 이상일 수 있다. 예를 들어, 실리사이드막(171,173)은 코발트 및 티타늄보다 낮은 온도에서 실리콘과 반응하는 니켈을 함유하는 니켈 실리사이드(Ni<sub>x</sub>Si<sub>1-x</sub>, 0<x<1)막일 수 있다. 예를 들어, 실리사이드막(171,173)은 NiSi, NiSi<sub>2</sub>, Ni<sub>3</sub>Si<sub>2</sub>, Ni<sub>2</sub>Si, Ni<sub>31</sub>Si<sub>12</sub> 중 적어도 하나일 수 있다. 이러한 니켈 실리사이드막은 코발트 및 티타늄 실리사이드들보다 낮은 비저항을 가질 수 있다. 니켈 실리사이드 막은 실리콘 캡핑층(160)과 니켈막이 반응하여 형성될 수 있다.

- [0090] 상기 실리사이드막(171,173)은 자기정렬적 실리사이드화 공정(self-aligned silicidation)을 이용하여 형성될

수 있다. 즉, 실리콘 상에 금속막을 형성하고, 금속과 실리콘을 반응시키는 열처리 공정을 실시한 후에 실리콘과 반응하지 않은 잔류 금속을 제거하는 과정으로 실시될 수 있다.

- [0091] 구체적으로 설명하면, 도10에 도시된 바와 같이, 우선, 게이트 전극(121) 상의 캡핑층(123)을 제거하는 후에, 게이트 전극(121) 및 SiGe 에피택셜(150)과 실리콘 캡핑층(160)이 형성된 반도체 기판(100) 상에 금속막(170)을 컨포멀하게 형성한다. 상기 금속막(170)은 게이트 전극(121)의 상면 및 Si 에피택셜층(160)의 표면을 덮을 수 있다. 여기서, 금속막(170)은 코발트, 티타늄, 니켈, 텅스텐 및 몰리브덴과 같은 고융점 금속(refractory metal) 물질을 포함할 수 있다. 본 실시예에서는, 금속막(170)은 니켈막일 수 있으며, 니켈막은 순수 니켈 또는 니켈 합금일 수 있다. 니켈 합금은 탄탈륨(Ta), 지르코늄(Zr), 타이타늄(Ti), 하프니움(Hf), 텅스텐(W), 코발트 (Co), 백금(Pt), 몰리브데늄(Mo), 팔라디움(Pd), 바나디움(V) 및 니오비움(Nb)에서 선택된 적어도 어느 하나를 함유할 수 있다.

- [0092] 이어, 열처리 공정을 실시하여, 실리콘 캡층(160) 및 게이트 전극(121)의 실리콘과 금속 물질을 반응시킬 수 있다. 이러한 열처리 공정은 고속 열처리(rapid thermal process: RTP) 장치 또는 로(furnace)에 의해 실시될 수 있다 열처리 온도는 약 250 내지 800℃ 범위일 수 있다.

- [0093] 이러한 열처리에 의해서 실리콘 캡핑층(160) 및 게이트 전극(121)의 실리콘이 소모되면서 그 자리에 실리사이드 막(171,173)이 형성될 수 있다. 이어, 실리사이드화되지 않은 미반응 금속막을 제거함으로써, 도11에 도시된 바와 같이, SiGe 에피택셜층(150)과 게이트 전극(121) 상에 실리사이드막(171,173)을 제공할 수 있다.

- [0094] 미반응 금속막을 제거하는 공정은 습식 식각 공정이 사용될 수 있으며, 실리사이드와 높은 선택성을 갖도록 황산(H<sub>2</sub>SO<sub>4</sub>)과 과산화수소(H<sub>2</sub>O<sub>2</sub>)의 혼합 용액이 사용될 수 있다.

- [0095] 실리사이드막(171,173)을 형성할 때, 금속막이 SiGe 에피택셜(150)과 반응하여 게르마늄을 함유한 실리사이드막이 형성될 수 있다. 이러한 Ge 함유 실리사이드막은 소스/드레인 영역에서의 콘택 저항이 증가하는 것을 억제할 수 있다.

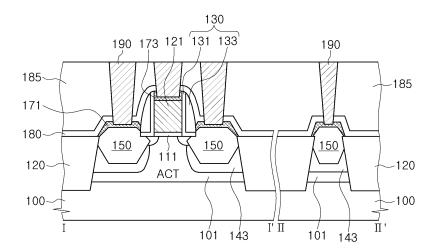

- [0096] 다음으로, 도12에 도시된 바와 같이, 실리사이드막(171,173)들을 형성한 후, 실리사이드막(171,173)과 연결되는 콘택 플러그(190)들이 형성될 수 있다.

- [0097] 본 공정은 반도체 기판(100) 전체 상면에 층간 절연막(185)(ILD; Inter-Layer Dielectric)을 형성하는 공정으로 시작될 수 있다. 구체적으로, 층간 절연막(185)으로는 TEOS(Tetra Ethyl Ortho Silicate), USG(Undoped Silicate Glass), PSG(PhosphoSilicate Glass), BSG(Borosilicate Glass), BPSG(BoroPhosphoSilicate Glass), FSG(Fluoride Silicate Glass), SOG(Spin On Glass), TOSZ(Tonen SilaZene) 또는 그 조합이 사용될 수 있다. 층간 절연막(185)은 CVD 및 스핀 코팅(spin coating) 등을 이용하여 형성될 수 있다. 필요에 따라, 층간 절연막(185)을 형성한 후에는 평탄화 공정이 실시될 수 있다. 한편, 층간 절연막(185)을 형성하기 전에, 반도체 기판(10) 상에 형성된 구조물들의 표면을 따라컨포말하게 식각 정지막(180)이 형성될 수 있다. 예를 들어, 식각 정지막(180)은 실리콘 질화막 또는 실리콘 산질화막일 수 있다.

- [0098] 이어, 상기 층간 절연막(185)을 형성한 후에는 실리사이드막(171)을 노출시키는 콘택홀들을 형성하고, 콘택홀 내에 도전 물질을 매립하여 콘택 플러그(190)들을 형성할수 있다. 콘택 플러그(190)들은 비저항이 낮은 금속 물질로 형성될 수 있다. 예를 들어, 콘택 플러그(190)는 코발트, 티타늄, 니켈, 텅스텐 또는 몰리브덴등의 금속막과, 티타늄질화막, 탄탈늄질화막, 텅스텐질화막 및 티타늄알루미늄질화막등의 도전성 금속질화막 중에서 선택된적어도 어느 하나로 형성될 수 있다.

- [0099] 콘택 플러그(190)를 형성하기 전에, 콘택홀 내의 측벽에 금속 원소의 확산을 방지하기 위한 금속 배리어막이 형성될 수 있다. 금속 배리어막은 텅스텐질화막(WN), 탄탈늄질화막(TiN) 또는 티타늄질화막(TaN) 등의 도전성 금속 질화막으로 이루어질 수 있다. 본 실시예에서는, 콘택 플러그(190)들이 게이트 실리사이드막(173)과 소스 및 드레인 실리사이드막(171) 각각에 연결된 것을 예시하였으나, 콘택 플러그(190)들의 연결은 다양한 형태로 변형될 수 있다.

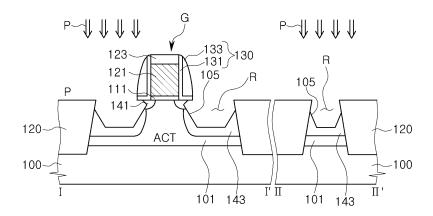

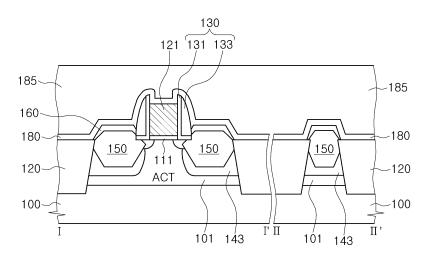

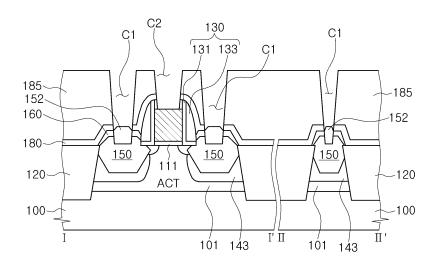

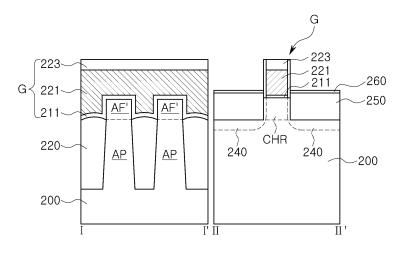

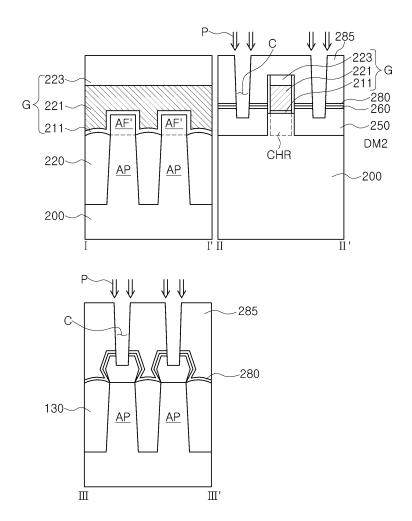

- [0100] 앞선 실시예에서는, 리세스 형성 후에 플라즈마 전처리를 적용한 예를 설명하였으나, 콘택홀 형성과정에서 제거 되는 에피택셜을 보상하기 위해서 적용되는 에피택셜의 재성장공정에도 유익하게 적용될 수 있다. 이러한 선택

적 에피택셜 재성장공정의 예는 도13 내지 도18에 도시되어 있다.

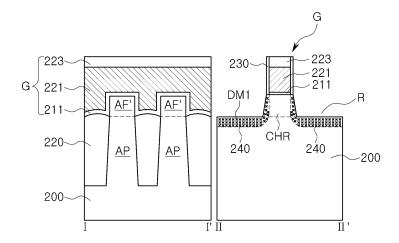

- [0101] 도13 내지 도18은 각각 도4에 도시된 반도체 소자를 I I '선 및 Ⅱ-Ⅱ'선을 따라 절개한 단면도로 이해될 수 있다. 또한, 도13에 도시된 공정은 도9에 도시된 공정에 후속되는 공정으로 이해될 수 있다.

- [0102] 도13에 도시된 바와 같이, 도9에 도시된 반도체 기판(100) 전체 상면에 식각정지막(180)과 충간절연막(185)을 형성할 수 있다.

- [0103] 상기 식각 정지막(180)은 실리콘 질화막 또는 실리콘 산질화막일 수 있다. 상기 식각 정지막(180)은 CVD 공정을 이용하여 반도체 기판(100) 상에 형성된 구조물들의 표면을 따라 컨포멀하게 형성될 수 있다. 상기 식각 정지막(180)을 형성하기 전에, 상기 게이트 전극(121) 상의 캠핑층(123)이 제거될 수 있다. 상기 층간 절연막(185)은 앞서 설명한 바와 같이, 단차 도포성이 우수한 절연물질을 이용하여 형성될 수 있다. 예를 들어, 03-TEOS, USG, PSG, BSG, BPSG, FSG, SOG, TOSZ 또는 그 조합일 수 있다. 상기 층간 절연막(185)은 CVD 및 스핀 코팅(spin coating) 등을 이용하여 형성될 수 있다. 필요에 따라, 층간 절연막(185)을 형성한 후에는 평탄화 공정이 실시될 수 있다.

- [0104] 이어, 도14에 도시된 바와 같이, 충간 절연막(185)에 실리콘 캡핑충(160)을 노출시키는 콘택홀(C1)들을 형성할 수 있다. 동일한 공정에서 게이트 전극(121)을 노출시키는 콘택홀(C2)을 함께 형성할 수도 있다.

- [0105] 본 콘택홀 형성과정에서, 도14에 도시된 바와 같이 SiGe 에피택셜(150)의 일부 영역까지 함께 제거될 수 있다. 모든 셀에서 콘택홀(C1)과 소스 및 드레인 영역의 연결을 충분히 보장하기 위해서 SiGe 에피택셜(150)의 일부 영역이 불가피하게 제거될 수 있다. SiGe 에피택셜(150)의 부분적 제거로 인해, 채널 영역에 인가되는 압축 응력은 감소될 수 있다. 특히, 부분적으로 제거되는 영역(L)은 고농도인 에피택셜(150)의 상부 영역이므로, 압축 응력의 감소는 정공의 이동도 개선효과를 크게 저감시킬 수 있다.

- [0106] 이러한 압축 응력 감소를 보상하기 위해서, 추가적으로 SiGe 에피택셜의 재성장이 요구될 수 있지만, 콘택홀 형성과정에서, SiGe 에피택셜(150)은 식각공정에 노출된 손상 영역(DM)을 가지므로, 선택적 에피택셜 재성장을 위해서 도15에 도시된 바와 같이 플라즈마(P)를 이용한 표면처리공정이 실시될 수 있다. 이러한 플라즈마(P)를 이용한 표면처리는 손상된 영역(DM)에 높은 에너지를 제공하므로, 통상의 세정 공정에서 제거되지 않는 표면에 흡착/고용되었던 불순물 원소가 효과적으로 제거될 수 있을 뿐만 아니라, 손상된 격자를 효과적으로 큐어링할 수 있다. 여기서 사용되는 플라즈마 소소는 He, Ar 및 Xe과 같은 비활성 기체일 수 있다. 본 공정에서 처리된 영역과 같이, SiGe 에피택셜(150)인 경우에는 비교적 원자사이즈가 큰 Ar 또는 Xe이 효과적으로 사용될 수 있다. 구체적인 공정 조건은 앞선 실시예에서 제시된 조건 범위에서 적절히 선택되어 사용될 수 있다.

- [0107] 이어, 도16에 도시된 바와 같이, 콘택홀(C1)에 노출된 SiGe 에피택셜(150)의 영역에 SiGe 에피택셜 재성장층 (152)을 형성할 수 있다.

- [0108] 선택적 에피택셜 성장공정을 이용하여 충간 절연막(185)의 표면에는 성장을 억제하고, SiGe 에피택셜(150)의 노출영역에 SiGe 에피택셜 재성장충(152)을 선택적으로 형성할 수 있다. 이러한 재성장충(152)은 플라즈마 처리에 의해 큐어링된 표면 상에 성장되므로, 고품질의 결정을 가질 수 있다.

- [0109] SiGe 에피택셜 재성장층(152)은 앞선 공정에서의 SiGe 에피택셜(150)의 부분적 제거로 인해 감소된 압축 응력을 보상하기 위해서 도입될 수 있다. 따라서, 상기 SiGe 에피택셜 재성장층(152)은 고농도의 Ge을 함유할 수 있다. 상기 SiGe 에피택셜(150)은 Si<sub>1-x</sub>Ge<sub>x</sub>이고, 상기 SiGe 에피택셜 재성장층(152)은 Si<sub>1-y</sub>Ge<sub>y</sub>일 때에, 상기 SiGe 에피택셜 재성장층(152)의 게르마늄 함량(x)보다 클 수 있다.

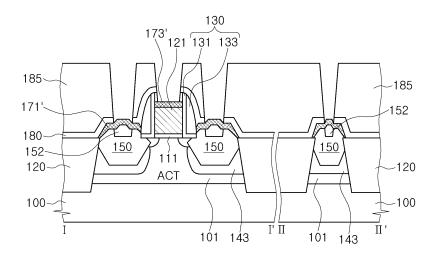

- [0110] 이어, 도17에 도시된 바와 같이, 콘택홀(C1,C2)에 노출된 에피택셜 영역에 실리사이드막(171',173')을 형성할 수 있다.

- [0111] 본 공정은 도11 및 도12에 설명된 공정과 유사하게 실시될 수 있다. 즉, 층간 절연막(185) 상에 금속막을 컨포 말하게 형성하고, 열처리 공정을 실시하여 실리콘 또는 실리콘 게르마늄과 금속막(170)을 반응시킴으로써 실리

사이드막들(171',173')을 형성할 수 있다. 이어, 반응하지 않은 금속막을 제거하여 도17에 도시된 형태를 얻을 수 있다.

- [0112] 열처리 공정을 실시할 때, SiGe 에피택셜 재성장층(152)의 일부영역과 함께 실리콘 캡핑층(160)이 실리사이드막 (171)을 형성할 수 있다. 물론, 본 실시예와 같이, 층간 절연막(185)에 콘택홀(C1)을 형성한 후에 실리사이드막 (171)을 형성하는 경우, 콘택홀에 노출된 SiGe 에피택셜 재성장층(152)의 상부만 금속과 반응하여 실리사이드막이 형성될 수도 있다. 또한, SiGe 에피택셜 재성장층(152)을 형성한 후에, 콘택홀(C1) 내부에 추가적인 실리콘 캡핑층을 형성하고, 이를 이용하여 실리사이드막을 형성할 수도 있다. 이 경우에, 앞선 공정에서 SiGe 에피택셜 (150) 상에 위치한 실리콘 캡핑층(160)의 형성이 생략될 수도 있다.

- [0113] 이어, 도18에 도시된 바와 같이, 충간 절연막(185)의 콘택홀(C1,C2) 내에 도전 물질을 매립하여 실리사이드막 (171',173')과 접촉하는 콘택 플러그들(190)을 형성할 수 있다.

- [0114] 앞선 실시예와 달리 다양한 전계효과 트랜지스터에 적용될 수 있다. 다른 예로서 핀(fin)구조를 갖는 전계효과 트랜지스터에도 유익하게 적용될 수 있다.

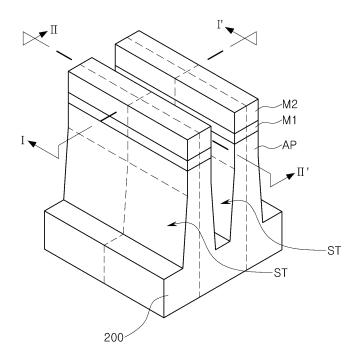

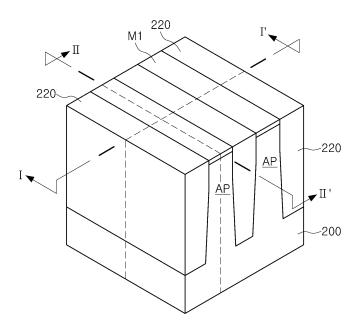

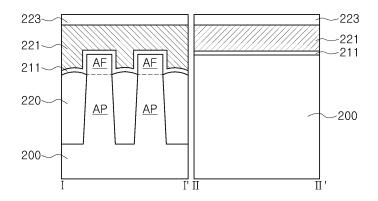

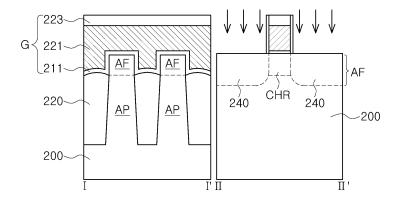

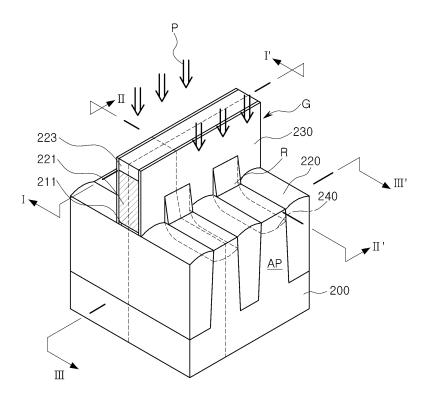

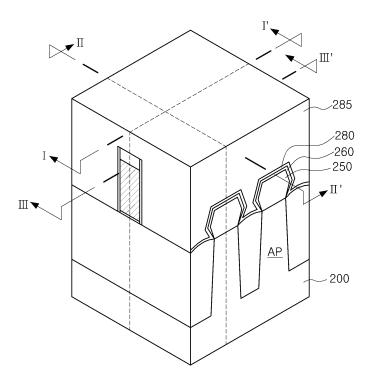

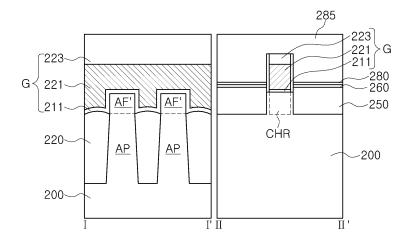

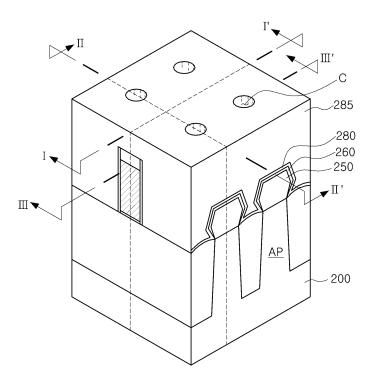

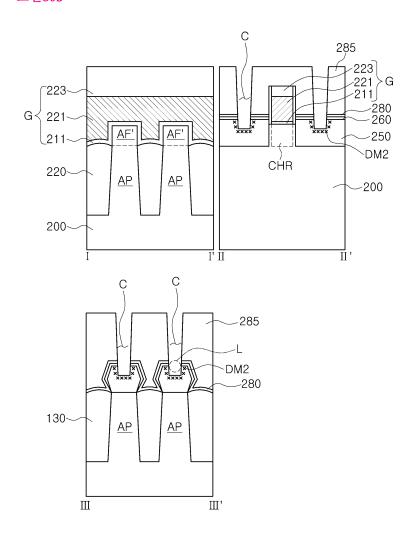

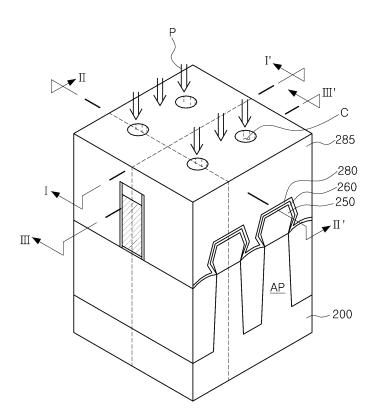

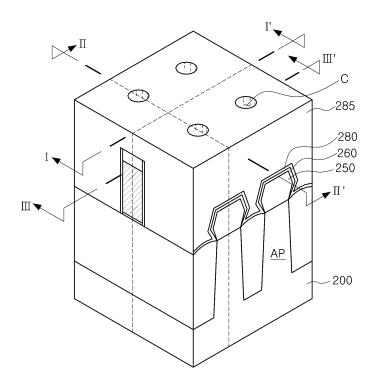

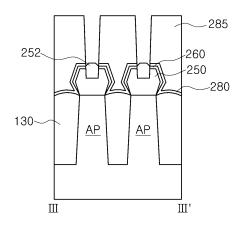

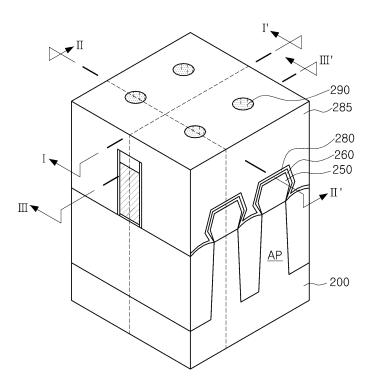

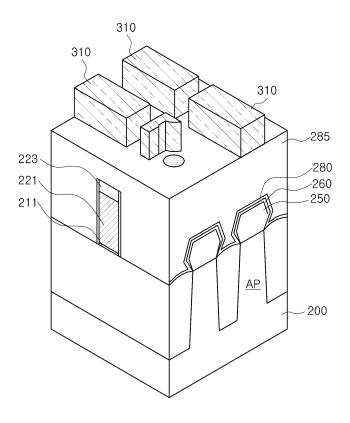

- [0115] 도19a 내지 도33a는 본 발명의 일 실시예로서, 핀구조를 갖는 전계효과 트랜지스터의 제조 방법의 주요 공정을 나타내는 개략 사시도이며, 도19b 내지 도33b는, 각각 도19a 내지 도33a에 도시된 전계효과 트랜지스터의 단면 도들이다.

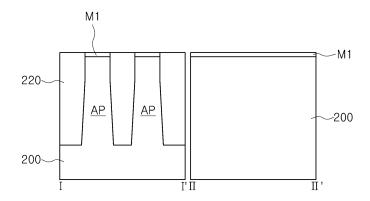

- [0116] 도19a 및 도19b에 도시된 바와 같이, 반도체 기판(100)을 패터닝하여 활성 패턴들(AP)을 정의하는 소자분리용 트렌치들(ST)을 형성할 수 있다.

- [0117] 상기 반도체 기판(200)은 벌크 실리콘 기판일 수 있으나, 이에 한정되지 않으며,실리콘 게르마늄 기판, 게르마늄 기판, SOI 기판 등일 수 있다. 상기 소자분리 트렌치(ST)의 형성공정은 상기 반도체 기판(200) 상에 마스크 패턴들을 형성한 후, 이를 식각 마스크로 사용하여 상기 반도체 기판(200)에 이방성 식각을 적용하는 과정으로 실시될 수 있다. 여기서, 상기 마스크 패턴은, 본 실시예와 같이 서로 식각 선택성을 갖는 제1 마스크 패턴(M1) 및 제2 마스크 패턴(M2)을 포함할 수 있다. 본 공정에서는 실질적으로 제2 마스크 패턴(M2)이 식각 마스크로 사용되고, 트렌치 형성 후에는 제거될 수 있다. 상기 소자분리 트렌치(ST)는 이에 한정되지 않으나 5이상의 종형 비를 갖도록 형성될 수 있다. 도시된 바와 같이, 상기 소자분리 트렌치(ST)는 아래로 갈수록 좁아지므로, 상기 활성 패턴(AP)은 위로 갈수록 좁아지는 형상을 가질 수 있다.

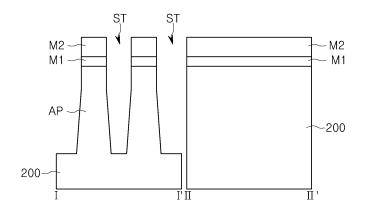

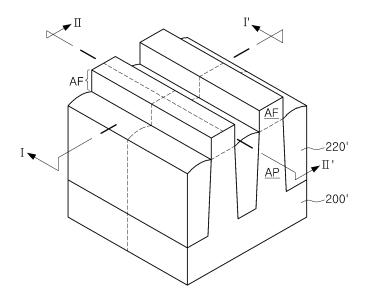

- [0118] 도20a 및 도20b를 참조하면, 상기 소자분리 트렌치들(ST)을 충전하는 소자 분리영역(220)을 형성한다. 상기 소자 분리영역(220)은 상기 소자분리 트렌치들(ST)을 절연물질로 충전한 후에 이를 평탄화하여 상기 마스크 패턴 (M1)의 상부면을 노출시킴으로써 얻어질 수 있다.

- [0119] 도21a 및 도21b를 참조하면, 상기 활성 패턴들(AP)의 상부영역들(이하, 활성 핀들(AF))을 노출시킨다.

- [0120] 상기 활성 핀들(AF)의 노출 공정은, 제1 마스크 패턴(M1)을 식각 마스크로 이용하는 습식 식각 공정으로 실시될 수 있다. 습식 식각 공정에 의해 상기 소자 분리영역(220')은 상부영역이 부분적으로 제거된 형태를 가질 수 있다. 그 결과, 상기 활성 패턴(AP)의 일부 영역이 노출되어 활성 핀들(AF)로 제공될 수 있다. 적절한 식각 조건을 채택하여 상기 소자분리 영역(220)이 원하는 깊이로 식각되는 동안에 상기 제1 마스크 패턴(M1)도 제거되어 상기 활성 핀들(AF)의 상부면들이 노출될 수 있다.

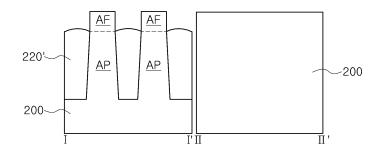

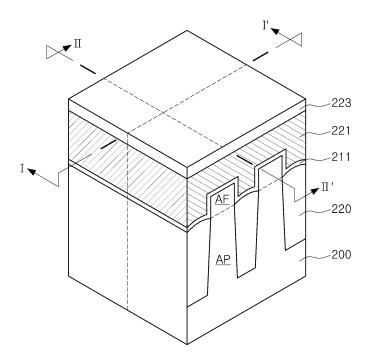

- [0121] 도22a 및 도22b를 참조하면, 상기 활성 핀들(AF)을 덮는 게이트 절연막(211)을 형성하고, 그 위에 게이트 전극 (221) 및 캠핑막(223)을 형성한다.

- [0122] 본 공정에서 형성되는 게이트 절연막(211), 게이트 전극(221) 및 캡핑막(223)은 특별히 반대되는 설명이 없는 도5에 설명된 내용과 유사한 물질로 사용될 수 있다. 특정 예에서는, 상기 게이트 절연막(211)은 원자층 증착

(ALD)로 형성한 후에 열처리하는 과정으로 형성될 수 있다. 다만, 이러한 열처리 단계는 ALD와 같은 증착공정 직후에 적용될 수도 있으나, 이와 달리, 후속 열처리 공정(예, 실리사이드 형성)에서 실시될 수 있다.

- [0123] 도23a 및 도23b를 참조하면, 게이트 절연막(211), 게이트 전극(221) 및 캡핑막(223)을 패터닝하여 게이트 전극 구조(G)를 형성하고, 게이트 전극 구조(G)된 결과물의 양 측면에 스페이서(230)를 형성할 수 있다.

- [0124] 상기 게이트 전국 구조(G)는 상기 활성 핀들(AF)을 가로지르는 형상으로 패터닝하여 형성될 수 있다. 이에 따라, 도23b에 도시된 바와 같이, 채널 영역(CHR) 및 소스/드레인 영역들(SR,DR)이 상기 활성 핀들(AF)에 각각 정의될 수 있다. 구체적으로, 상기 채널 영역(CHR)은 상기 게이트 전국 구조(G) 아래에 위치하는 상기 활성 핀(AF)의 일 영역이며, 상기 소스/드레인 영역들(SR,DR)은 상기 게이트 전국구조(G)의 양측에 위치하며 상기 채널 영역(CHR)에 의해 수평적으로 분리된 상기 활성 핀(AF)의 다른 영역들로 정의될 수 있다.

- [0125] 상기 게이트 전극 구조(G)의 형성공정은 상기 희생 게이트 패턴(160)의 양측에 위치하는 상기 활성 핀(AF)의 일부 영역(즉, 상기 소스/드레인 영역들(SR,DR))을 노출시키는 공정으로 실시될 수 있다. 구체적인 예에서, 상기 게이트 절연막(211)을 식각 정지막으로 사용하여 상기 게이트 전극(222) 및 캠핑막(223)을 이방적으로 식각하고, 게이트 절연막(211)의 노출된 부분에 이방성 식각공정을 적용하여 상기 소스/드레인 영역들(SR,DR)을 노출시킬 수 있다.

- [0126] 상기 게이트 전극 구조(G)의 양 측벽들 상에 스페이서(230)를 형성할 수 있다. 상기 게이트 스페이서(230) 형성 공정은 상기 게이트 전극구조(G)에 스페이서를 위한 막을 형성한 후, 상기 막을 이방성 식각함으로써 실시될 수 있다.

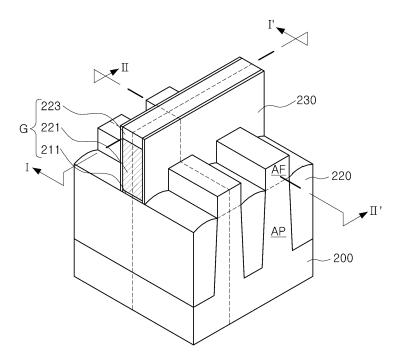

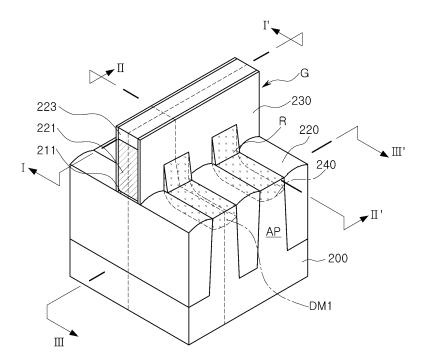

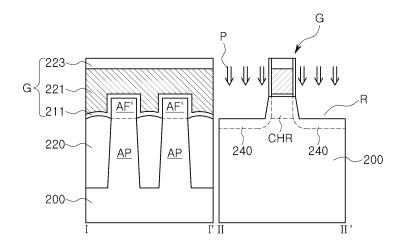

- [0127] 도24a 및 도24b를 참조하면, 상기 스페이서(230)를 형성한 후, 게이트 전극 구조(G) 양측의 활성 핀(AF)의 영역 들, 즉 소스 영역(SR) 및 드레인 영역(DR)에 불순물 영역(140)을 형성할 수 있다. 상기 불순물 영역(140)은 스페이서(230)를 구비한 게이트 전극구조(G)를 이온 주입 마스크로 이용하여 p형 불순물, 예를 들어 붕소(B)를 주입하여 형성될 수 있다.

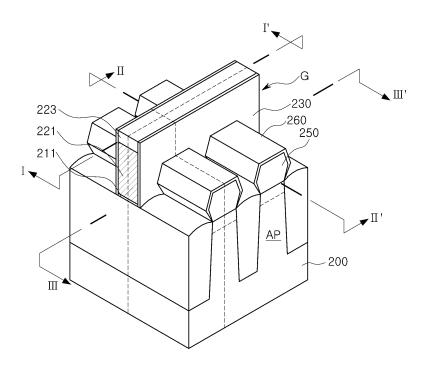

- [0128] 다음으로, 도25a 및 도25b에 도시된 바와 같이, 게이트 전극 구조(G) 양측의 활성 핀(AF)영역들을 선택적으로 식각하여 리세스(R)를 형성할 수 있다.

- [0129] 상기 리세스(R)는 게이트 전극 구조(G)를 식각 마스크로 이용하여 이방성 및/또는 등방성 식각하여 형성될 수 있다. 본 실시예에서, 리세스(R)는 게이트 전극 구조(G) 양측에 각각 제공될 수 있다. 구체적인 예에서, 상기 게이트 전극 구조(G)와 함께 소자 분리막(220)을 식각 마스크로 이용하여 활성 핀(ACT)의 소스 및 드레인 영역 (SR,DR)에 등방성 또는 이방성 건식 식각 공정을 실시하여 원하는 리세스보다 낮은 깊이로 트렌치를 형성할 수 있다. 이어, 트렌치에 식각액을 공급하여 등방성 식각을 적용함으로써 리세스(R)의 바닥면 및 측면들이 특정 결정면으로 제공될 수 있다.

- [0130] 이러한 식각 공정에 의해 리세스(R)는 그 표면뿐만 아니라, 그와 인접한 내부 영역까지 에천트로 인한 불순물로 오염되고, 결정이 손상될 수 있다. 이와 같이, 식각공정에 의해 오염되고 손상된 표면영역(DM1)은 리세스(R) 형 성공정이 완료한 후에 세정공정이 적용될 수 있으나, 통상의 세정공정으로는 흡착/고용된 불순물 원소의 제거와 손상된 격자의 큐어링을 기대할 수 없다. 이러한 문제를 개선하기 위해서, 도8에 도시된 플라즈마를 이용한 전처리 공정이 요구된다.

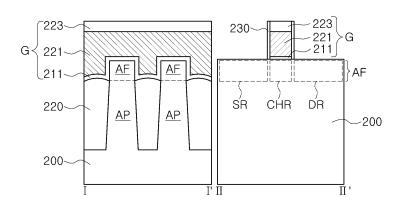

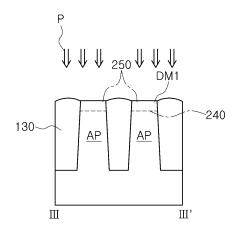

- [0131] 이어, 도26a 및 도26b에 도시된 바와 같이, 비활성 기체 플라즈마(P)를 이용하여 상기 리세스(R)를 전처리할 수 있다.

- [0132] 이러한 비활성 기체 플라즈마 처리공정에 의해서, 손상된 영역(DM1)에 흡착/고용되었던 불순물 원소가 효과적으로 제거될 수 있을 뿐만 아니라, 손상된 격자가 효과적으로 큐어링될 수 있다. 본 공정에서 사용되는 플라즈마소소는 He, Ar 및 Xe과 같은 비활성 기체일 수 있다. 특정한 예에서는, Ar 또는 Xe과 같은 플라즈마소스를 이용하여 더욱 효과적인 큐어링을 기대할 수 있다.

- [0133] 구체적으로, 비활성 기체 플라즈마는 800kW ~ 4000kW 범위의 파워를 인가하여 전처리에 사용되는 플라즈마를 발생시킬 수 있으며, 플라즈마를 이용한 처리는 비교적 저온(600℃이하)에서 실시될 수 있다. 예를 들어, 500℃이하에서 실시될 수 있다. 이에 한정되지는 않으나, 플라즈마를 이용한 처리는 0.1~10 torr의 압력 조건에서 실시될 수 있으며, 전처리 시간은 10s ~ 300s 범위의 시간 동안 실시될 수 있다.

- [0134] 이어, 도27a 및 도27c에 도시된 바와 같이, 선택적 에피택셜 성장(SEG) 공정을 실시하여, 리세스(R)에 제1 SiGe 에피택셜(250)을 형성할 수 있다.

- [0135] 제1 SiGe 에피택셜(250)은 선택적 에피택셜 성장 공정에 의해, 리세스(R)에 노출된 영역에서만 선택적으로 성장될 수 있다. 앞선 공정에서 플라즈마를 이용한 전처리에 의해서 상기 리세스(R)는 결정성장에 유리한 표면을 가질 수 있으므로, 본 성장공정에서 원하는 품질의 에피택셜을 성장시킬 수 있다. 특별히 반대되는 설명이 없는 한, 앞선 실시예의 SiGe 에피택셜 형성공정(도9 및 관련 설명)이 여기에 참고로 결합될 수 있다.

- [0136] 본 실시예와 같이, PMOS 트랜지스터인 경우에, 제1 SiGe 에피택셜(250)이 리세스(R)에 성장되면, 채널 영역에 압축 응력을 발생시킬 수 있다. Ge의 농도가 증가할수록 제1 에피택셜(250)의 격자가 커지므로 채널영역에 가해 지는 압축 응력은 증가될 수 있다.

- [0137] 본 실시예에서, 제1 SiGe 에피택셜(150)은 하부 영역에서보다 상부 영역에서 Ge의 농도가 클 수 있다. 예를 들어, 하부영역은 약 20 내지 50mm의 두께를 가질 수 있으며, 하부영역의 Ge 농도는 10 내지 30%일 수 있다. 상부 영역은 약 40 내지 60mm의 두께를 가질 수 있으며, 상부영역의 Ge 농도는 20 내지 50%일 수 있다.

- [0138] 상기 제1 SiGe 에피택셜(250)은 p형 불순물으로 도프된 에피택셜일 수 있다. 본 실시예에서, 제1 SiGe 에피택셜 (250)의 도핑공정은 에피택셜 성장과정에서 인-시츄(insitu)로 p형 불순물을 도핑하거나, 선택적 에피택셜 성장 후에 이온 주입함으로써 실시될 수도 있다. 이와 같이, p형 불순물이 도핑된 제1 SiGe 에피택셜(250)은 불순물 영역들(240)과 함께 소스/드레인 영역으로 제공될 수 있다.

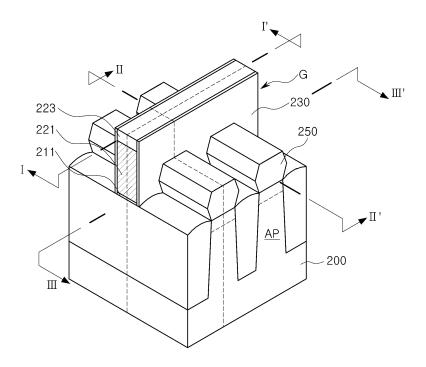

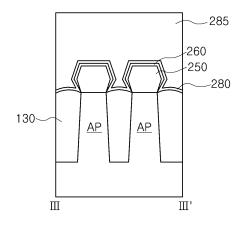

- [0139] 다음으로, 도28a 및 도28b에 도시된 바와 같이, 제1 SiGe 에피택셜(250) 상에 실리콘 캡핑층(260)을 형성할 수 있다. 실리콘 캡핑층(260)은 제1 SiGe 에피택셜(250)의 표면을 덮을 수 있다. 실리콘 캡핑층(260)의 두께는 제1 SiGe 에피택셜(250)의 결정면에 따라 상이할 수 있다. 실리콘 캡핑층(260)은 후속공정에서 실리사이드막을 형성하는데 사용될 수 있다.

- [0140] 이어, 도29a 및 도29b에 도시된 바와 같이, 반도체 기판(200) 전체 상면에 식각정지막(280)과 층간절연막(285)을 형성할 수 있다.

- [0141] 상기 식각 정지막(280)은 실리콘 질화막 또는 실리콘 산질화막일 수 있다. 상기 식각 정지막(280)은 반도체 기판(200) 상에 형성된 구조물들의 표면을 따라 컨포멀하게 형성될 수 있다. 상기 식각 정지막(280)을 형성하기전에, 상기 게이트 전극(221) 상의 캡핑층(223)이 제거될 수 있다. 상기 층간 절연막(285)은 단차 도포성이 우수한 절연물질을 이용하여 형성될 수 있다. 필요에 따라, 층간 절연막(185)을 형성한 후에는 평탄화 공정이 실시될 수 있다.

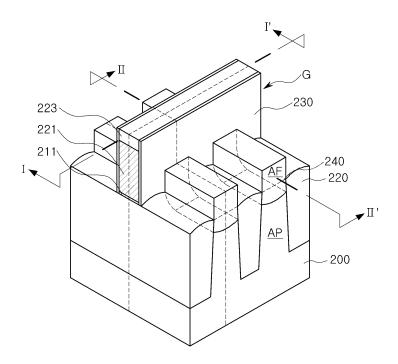

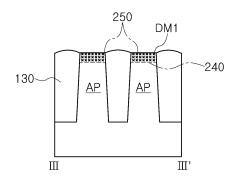

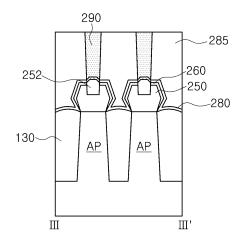

- [0142] 다음으로, 도30a 및 도30b에 도시된 바와 같이, 층간 절연막(285)에 실리콘 캠핑층(260)을 노출시키는 콘택홀 (C)들을 형성할 수 있다.

- [0143] 본 콘택홀 형성과정에서, 제1 SiGe 에피택셜(250)의 일부 영역까지 함께 제거될 수 있다. 부분적으로 제거되는 영역(L)은 고농도인 제1 SiGe 에피택셜(250)의 상부 영역이므로, 압축 응력의 감소는 정공의 이동도 개선효과를 크게 저감시킬 수 있다.

- [0144] 이러한 압축 응력 감소를 보상하기 위해서, 추가적으로 선택적 에피택셜 성장 성장 공정을 적용할 수 있다. 이에 앞서, 도31a 및 도31b에 도시된 바와 같이, 콘택홀(C) 형성을 위한 식각공정에 의해 손상 영역(DM2)에 플라즈마(P)를 이용한 표면처리공정이 적용될 수 있다. 본 플라즈마 처리 공정에서, 플라즈마 소스는 콘택홀(C)을 통해서 손상영역에 도달할 수 있다. 본 공정을 통해서, 흡착/고용된 불순물이 제거될 수 있으며, 손상된 격자도

효과적으로 큐어링될 수 있다. 여기서 사용되는 플라즈마 소소는 He, Ar 및 Xe과 같은 비활성 기체일 수 있다. 본 실시예와 같이, 상기 제1 SiGe 에피택셜(250)의 표면인 경우에는 플라즈마 소스로서 비교적 원자사이즈가 큰 Ar 또는 Xe이 사용될 수 있다. 구체적인 공정 조건은 앞선 실시예에서 제시된 조건 범위에서 적절히 선택되어 사용될 수 있다.

- [0145] 이어, 도32a 및 도32b에 도시된 바와 같이, 콘택홀(C)에 노출된 제1 SiGe 에피택셜(250)의 영역에 제2 SiGe 에 피택셜(252)을 형성할 수 있다.

- [0146] 본 선택적 에피택셜 성장공정에서는, 실리콘 및 게르마늄 소스와 함께 선택적 식각가스를 공급함으로써 충간 절 연막(285)의 표면에는 성장을 억제하고, 제1 SiGe 에피택셜(250)의 노출영역에 제2 SiGe 에피택셜(252)을 성장시킬 수 있다.

- [0147] 제2 SiGe 에피택셜(252)은 앞선 공정에서의 제1 SiGe 에피택셜(250)의 부분적 제거로 인해 감소된 압축 응력을 보상할 수 있다. 이를 위해서, 상기 제1 SiGe 에피택셜(252)은 고농도의 Ge을 함유할 수 있다. 상기 제1 SiGe 에피택셜(250)은 Si<sub>1-x</sub>Ge<sub>x</sub>이고, 상기 제2 SiGe 에피택셜(252)은 Si<sub>1-y</sub>Ge<sub>y</sub>일 때에, 상기 제2 SiGe 에피택셜(252)의 게르마늄 함량(y)이 상기 제1 SiGe 에피택셜(250)의 게르마늄 함량(x)보다 클 수 있다.

- [0148] 다음으로, 도33a 및 도33b에 도시된 바와 같이, 콘택홀(C)에 노출된 에피택셜 영역에 실리사이드막(270)을 형성하고, 콘택홀(C) 내에 도전 물질을 매립하여 실리사이드막(270)과 접촉하는 콘택 플러그들(290)을 형성할 수 있다.

- [0149] 본 공정에서는, 층간 절연막(285) 상에 금속막을 컨포말하게 형성하고, 열처리 공정을 실시하여 상기 금속막을 실리콘 또는 실리콘 게르마늄과 반응시킴으로써 실리사이드막들(270)을 형성할 수 있다. 이어, 반응하지 않은 금속막을 제거할 수 있다. 본 실시예와 같이, 열처리 공정에서, 제2 SiGe 에피택셜(252)의 일부 영역과 함께 실리콘 캠핑층(260)이 실리사이드막(270)을 형성할 수 있다. 본 실시예와 달리, 제2 SiGe 에피택셜(252)을 형성한 후에, 콘택홀(C) 내부에 추가적인 실리콘 캠핑층을 형성하고, 이를 이용하여 실리사이드막을 형성할 수도 있다. 이 경우에, 앞선 공정에서 제1 SiGe 에피택셜(250) 상에 위치한 실리콘 캠핑층(260)의 형성이 생략될 수도 있다. 다음으로, 도34에 도시된 바와 같이, 상기 실리사이드(270) 및 콘택 플러그(290)를 통해서 소스/드레인 영역에 연결된 배선 구조체(310)를 형성할 수 있다.

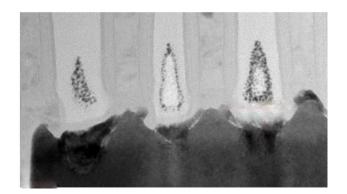

- [0150] 선택적 에피택셜 성장 전에 플라즈마 전처리를 적용함으로써 개선되는 효과를 확인하기 위해서 몇가지 실험을 실시하였다.

- [0151] 실험예1: 리세스 형성 후 SEG 공정

- [0152] SiGe 활성 핀에 리세스를 형성한 후(도25a 및 도25b 참조)에, 샘플에 따라 아래 표1에 제시된 다른 조건으로 플라즈마를 발생시켜 표면 처리를 실시하였다(도26a 및 도26b 참조). 표면 처리된 리세스 영역에 동일한 공정조건으로 SiGe을 선택적으로 성장시켰다(도27a 및 도27b 참조).

| 12 | 1 |

|----|---|

|    |   |

| [0153] | 구분  | 플라즈마  | 파워   | 압력     | 결과물 사진 | SiGe 에피성장 |

|--------|-----|-------|------|--------|--------|-----------|

|        |     | 소스    | (kW) | (Torr) |        | 평가        |

|        | 샘플1 | $N_2$ | 2000 | 1      | 도35a   | Bad       |

|        | 샘플2 | Ar    | 2000 | 1      | 도35b   | Good      |

|        | 샘플3 | Ar    | 1200 | 5      | 도35c   | Better    |

- [0154] 상기한 표1에 나타난 바와 같이, Ar 플라즈마를 이용하여 처리된 샘플 2 및 3에서 샘플1과 달리 SiGe의 성장이 이루어졌으며, 특히 샘플3에서 리세스의 전체 표면에서 SiGe 성장이 진행되는 것을 확인할 수 있었다.

- [0155]

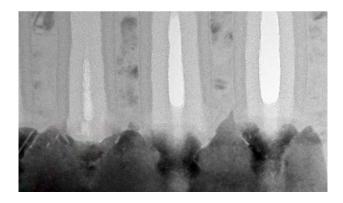

#### [0156] 실험예2: 콘택 홀 형성 후 SEG 공정

- [0157] 2개의 샘플(A 및 B)을 플라즈마 처리 여부를 제외하고 동일한 조건으로 제조하였다. 우선, 층간 절연막에 SiGe 에피택셜까지 연장되는 콘택홀을 형성하였다. 콘택홀 형성과정에서 SiGe 에피택셜의 일부 영역이 함께 제거되었다. 이어, 샘플A는 플라즈마 처리를 적용하지 않고, 샘플B는 샘플3과 동일한 플라즈마 처리 조건을 적용하였다. 다음으로, 콘택홀에 노출된 SiGe 에피택셜 영역에 동일한 공정조건으로 SiGe 에피택셜을 추가적으로 성장시켰다.

- [0158] 샘플 A 및 B에 대한 추가적인 SiGe 에피택셜 성장 결과는 도36a 및 도36b에서 확인할 수 있다. 도36a에 나타난 바와 같이, 샘플A는 콘택홀 형성과정에서 불순물로 오염되고 격자가 손상되어 정상적인 에피택셜 성장이 거의 이루어지지 않는 것을 확인할 수 있다. 이에 반하여,샘플B는 SiGe 에피택셜 성장이 이루어지는 것을 확인할 수 있었다. 이러한 결과는 Ar 플라즈마 처리로 인하여 식각된 표면에 불순물이 제거되고 손상된 격자가 큐어링된 것을 보여준다.

- [0159] 도37은 본 발명의 실시예에 따른 반도체 소자를 포함하는 CMOS 인버터(inverter)의 회로도이다.

- [0160] 도37을 참조하면, CMOS 인버터는 PMOS 트랜지스터(P1)와 NMOS 트랜지스터(N1)로 구성될 수 있다. PMOS 트랜지스터(P1)는 상술한 본 발명의 실시예에 따른 반도체 소자 중에 하나일 수 있다. PMOS 및 NMOS 트랜지스터들은 전원 전압 라인(Vdd)과 접지 전압 라인(Vss) 사이에 직렬로 연결되며, PMOS 및 NMOS 트랜지스터의 게이트들에는 입력 신호가 공통으로 입력될 수 있다. 그리고, PMOS 및 NMOS 트랜지스터의 드레인들에서 출력 신호가 공통으로 출력될 수 있다. 또한, PMOS 트랜지스터의 소스에는 구동전압이 인가되며, NMOS 트랜지스터의 소스에는 접지전압이 인가될 수 있다. 이러한 CMOS 인버터는 입력 신호(IN)를 인버팅하여 출력 신호(OUT)로 출력할 수 있다. 다시 말해, 인버터의 입력 신호로 로직 레벨 "1"이 입력될 때, 출력 신호로서 로직 레벨 "0"이 출력되며, 인버터의 입력 신호로 로직 레벨 "0"이 입력될 때, 출력 신호로서 로직 레벨 "1"이 출력될 수 있다.

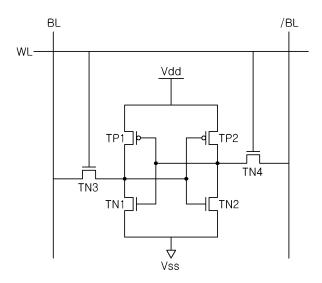

- [0161] 도38은 본 발명의 실시예에 따른 반도체 소자를 포함하는 SRAM 셀의 회로도이다.

- [0162] 도38을 참조하면, SRAM 소자에서 하나의 셀은 제1 및 제2 구동 트랜지스터(TN1, TN2), 제1 및 제2 부하 트랜지스터(TP1, TP2) 및 제1 및 제2 액세스 트랜지스터(TN3, TN4)로 구성될 수 있다. 이때, 제1 및 제2 구동 트랜지스터(TN1, TN2)의 소스는 접지 전압 라인(Vss)에 연결되며, 제1 및 제2 부하 트랜지스터(TP1, TP2)의 소스는 전원 전압 라인(Vdd)에 연결될 수 있다.

- [0163] 그리고, NMOS 트랜지스터로 이루어진 제1 구동 트랜지스터(TN1)와 PMOS 트랜지스터로 이루어진 제2 부하 트랜지스터(TP1)가 제1 인버터를 구성하며, NMOS 트랜지스터로 이루어진 제2 구동 트랜지스터(TN2)와 PMOS 트랜지스터로 이루어진 제2 부하 트랜지스터(TP2)가 제2 인버터를 구성할 수 있다. PMOS 트랜지스터로 이루어진 제1 및 제2 부하 트랜지스터(TP1, TP2)는 상술한 본 발명의 실시예에 따른 반도체 소자들 중 하나일 수 있다.

- [0164] 제1 및 제2 인버터의 출력단은 제1 액세스 트랜지스터(TN3)와 제2 액세스 트랜지스터(TN4)의 소스와 연결될 수 있다. 또한, 제1 및 제2 인버터는 하나의 래치(latch) 회로를 구성하기 위해 입력단과 출력단이 서로 교차되어 연결될 수 있다. 그리고, 제1 및 제2 액세스 트랜지스터(TN3, TN4)의 드레인은 각각 제1 및 제2 비트라인(BL, /BL)에 연결될 수 있다.

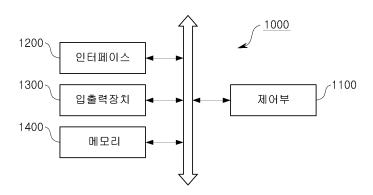

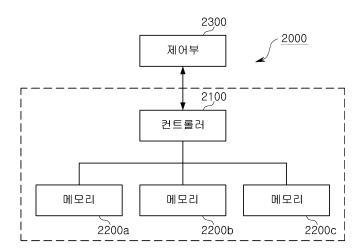

- [0165] 도39 및 도40은 본 발명의 실시예에 따른 반도체 소자를 포함하는 전자 장치 및 저장 장치를 나타낸 블록도이다.

- [0166] 도39를 참조하면, 본 발명의 일 실시예에 따른 반도체 소자를 포함하는 전자 장치(1000)는, 제어부(1100), 인터 페이스(1200), 입출력장치(1300), 메모리(1400) 등을 포함할 수 있다. 제어부(1100), 인터페이스(1200), 입출력 장치(1300), 메모리(1400) 등은 데이터가 전달되는 통로를 제공하는 버스(1500, BUS)를 통해 연결될 수 있다.

- [0167] 제어부(1100)는 적어도 하나의 마이크로프로세서, 디지털 신호 프로세서, 마이크로 컨트롤러 등과 같은 소자를 포함할 수 있다. 메모리(1400)는 다양한 방식으로 데이터를 읽고 쓸 수 있는 소자를 포함할 수 있으며, 제어부 (1100)와 메모리(1400)는 상술한 본 발명의 실시예들에 따른 반도체 소자들 중 적어도 하나를 포함할 수 있다.

- [0168] 입출력장치(1300)는 키패드, 키보드, 터치스크린 장치, 표시 장치, 오디오 입출력 모듈 등을 포함할 수 있다. 인터페이스(1200)는 통신 네트워크로 데이터를 송수신하기 위한 모듈일 수 있으며, 안테나, 유무선 트랜시버 등을 포함할 수 있다. 또한, 도39에 도시된 구성 요소 이외에, 전자 장치(1000)는 응용 칩셋, 영상 촬영 장치 등이 더 포함될 수도 있다. 도 16에 도시한 전자 장치(1000)는 그 카테고리가 제한되지 않으며, 개인 휴대용 정보단말기(PDA), 휴대용 컴퓨터, 모바일폰, 무선폰, 랩톱 컴퓨터, 메모리 카드, 휴대용 미디어 플레이어, 타블렛 PC 등 다양한 장치일 수 있다.

- [0169] 도40을 참조하면, 본 발명의 일 실시예에 따른 반도체 소자를 포함하는 저장 장치(2000)는 제어부(2300)와 통신하는 컨트롤러(2100) 및 데이터를 저장하는 메모리(2200a, 2200b, 2200c)를 포함할 수 있다. 컨트롤러(2100) 및 각 메모리(2200a, 2200b, 2200c)는 상술한 본 발명의 실시예들에 따른 반도체 소자들 중 적어도 하나를 포함할수 있다.

- [0170] 컨트롤러(2100)와 통신하는 호스트(2300)는 저장 장치(2000)가 장착되는 다양한 전자 기기일 수 있으며, 예를 들어 스마트폰, 디지털 카메라, 데스크 톱, 랩톱, 미디어 플레이어 등일 수 있다. 컨트롤러(2100)는 호스트 (2300)에서 전달되는 데이터 쓰기 또는 읽기 요청을 수신하여 메모리(2200a, 2200b, 2200c)에 데이터를 저장하거나, 메모리(2200a, 2200b, 2200c)로부터 데이터를 인출하기 위한 명령(CMD)을 생성할 수 있다.

- [0171] 이상에서 설명한 본 발명이 전술한 실시예 및 첨부된 도면에 한정되지 않으며, 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하다는 것은, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 있어 명백할 것이다.

# 도면6

### 도면9

### 도면12

### 도면15

# 도면19a

# 도면19b

# 도면20a

### 도면20b

# 도면21a

# 도면21b

## 도면22a

## 도면22b

## 도면23a

## 도면23b

# 도면24a

# 도면24b

# 도면25a

## 도면25b

# 도면26a

# 도면26b

# 도면27a

## 도면27b

# 도면28a

## 도면28b

# 도면29a

## 도면29b

# 도면30a

## 도면30b

# 도면31a

# 도면31b

# 도면32a

### 도면32b

# 도면33a

## 도면33b

도면35a

도면35b

도면35c

도면36a

도면36b

# 도면38