## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2019-12837 (P2019-12837A)

(43) 公開日 平成31年1月24日(2019.1.24)

| (51) Int.Cl. |        |                             | F I          |          |           | テーマコート    | (参考)   |

|--------------|--------|-----------------------------|--------------|----------|-----------|-----------|--------|

| HO1L         | 21/316 | (2006.01)                   | HO1L         | 21/316   | X         | 4KO29     |        |

| HO1L         | 21/363 | (2006.01)                   | HO1L         | 21/363   |           | 4KO3O     |        |

| HO1L         | 21/318 | (2006.01)                   | HO1L         | 21/318   | С         | 5F058     |        |

| HO1L         | 29/786 | (2006.01)                   | HO1L         | 29/78    | 618B      | 5F1O3     |        |

| HO1L         | 21/336 | (2006.01)                   | HO1L         | 29/78    | 619A      | 5 F 1 1 O |        |

|              |        |                             | 審査請求         | 有 請求     | 項の数 3 OL  | (全 60 頁)  | 最終頁に続く |

| (91) 中陌来县    |        | <b>焙願</b> 2018 166552 (₽201 | 18 166552) ( | 71) 中間 人 | 000152878 |           |        |

| (21) 出脚番号    | 守原2018-166552 (P2018-166552) | (71) 出題 |

|--------------|------------------------------|---------|

| (22) 出願日     | 平成30年9月6日(2018.9.6)          |         |

| (62) 分割の表示   | 特願2017-41252 (P2017-41252)   |         |

|              | の分割                          | (72) 発明 |

| 原出願日         | 平成25年3月14日 (2013.3.14)       |         |

| (31) 優先権主張番号 | 特願2012-87432 (P2012-87432)   |         |

| (32) 優先日     | 平成24年4月6日(2012.4.6)          | (72) 発明 |

| (33) 優先権主張国  | 日本国(JP)                      |         |

| (31) 優先権主張番号 | 特願2012-156492 (P2012-156492) |         |

| (32) 優先日     | 平成24年7月12日 (2012.7.12)       | (72) 発明 |

| (33) 優先権主張国  | 日本国(JP)                      |         |

|              |                              |         |

|              |                              | 1 / ->  |

(71) 出願人 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

(72) 発明者 岡崎 健一

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72)発明者 佐々木 俊成

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 横山 周平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72)発明者 羽持 貴士

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

# (54) 【発明の名称】半導体装置の作製方法

# (57)【要約】

【課題】酸化物半導体を用いた半導体装置において、酸素欠損の含有量を低減する。また

、酸化物半導体を用いた半導体装置において、電気特性 を向上させる。

【解決手段】酸化物半導体膜を有するトランジスタと、 当該トランジスタ上に形成される

保護膜とを有する半導体装置において、真空排気された 処理室内に載置された基板を18

0 以上260 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を1

00Pa以上250Pa以下とし、処理室内に設けられる電極に0.17W/cm<sup>2</sup>以上

0.5W/cm<sup>2</sup>以下の高周波電力を供給する条件により、上記保護膜として化学量論的

組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を 形成する。

【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

絶縁膜上に酸化物半導体膜を形成する工程と、

前記酸化物半導体膜上に酸化絶縁膜を形成する工程と、

前記酸化絶縁膜を形成した後、300 以上450 以下の温度で加熱処理を行う工程と、を有し、

前記酸化絶縁膜は、真空排気された処理室内に基板を配置し、前記処理室内に原料ガスとしてシリコンを含む堆積性気体及び酸化性気体を導入して、前記処理室内における圧力を100Pa以上250Pa以下とし、前記処理室内に設けられる電極に高周波電力を供給することにより形成され、

前記酸化絶縁膜の成膜温度は、前記加熱処理の温度よりも低い温度で行われ、

前記堆積性気体は、シラン、ジシラン、トリシラン、又はフッ化シランを有し、

前記酸化性気体は、酸素、オゾン、一酸化窒素、又は二酸化窒素を有することを特徴とする半導体装置の作製方法。

#### 【請求項2】

絶縁膜上に酸化物半導体膜を形成する工程と、

前記酸化物半導体膜上に酸化絶縁膜を形成する工程と、

前記酸化絶縁膜を形成した後、300 以上450 以下の温度で加熱処理を行う工程と、を有し、

前記酸化絶縁膜は、真空排気された処理室内に基板を配置し、前記処理室内に原料ガスとしてシリコンを含む堆積性気体及び酸化性気体を導入して、前記処理室内における圧力を 1 0 0 P a 以上 2 5 0 P a 以下とし、前記処理室内に設けられる電極に 0 . 1 7 W / c m <sup>2</sup> 以上 0 . 5 W / c m <sup>2</sup> 以下の高周波電力を供給することにより形成され、

前記酸化絶縁膜の成膜温度は、前記加熱処理の温度よりも低い温度で行われ、

前記堆積性気体は、シラン、ジシラン、トリシラン、又はフッ化シランを有し、

前記酸化性気体は、酸素、オゾン、一酸化窒素、又は二酸化窒素を有することを特徴とする半導体装置の作製方法。

#### 【請求項3】

請求項1又は請求項2において、

前記酸化絶縁膜は、前記酸化物半導体膜と接する領域を有することを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

# 【技術分野】

#### [00001]

本発明は、絶縁膜及び電界効果トランジスタを有する半導体装置の作製方法に関する。

#### 【背景技術】

# [0002]

液晶表示装置や発光表示装置に代表されるフラットパネルディスプレイの多くに用いられているトランジスタは、ガラス基板上に形成されたアモルファスシリコン、単結晶シリコンまたは多結晶シリコンなどのシリコン半導体によって構成されている。また、該シリコさン半導体を用いたトランジスタは、集積回路(IC)などにも利用されている。

# [0003]

近年、シリコン半導体に代わって、半導体特性を示す金属酸化物をトランジスタに用いる技術が注目されている。なお、本明細書中では、半導体特性を示す金属酸化物を酸化物半 導体とよぶことにする。

# [0004]

例えば、酸化物半導体として、酸化亜鉛、またはIn-Ga-Zn系酸化物を用いたトランジスタを作製し、該トランジスタを表示装置の画素のスイッチング素子などに用いる技術が開示されている(特許文献 1 及び特許文献 2 参照)。

#### 【先行技術文献】

30

10

20

#### 【特許文献】

[0005]

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

【発明の概要】

【発明が解決しようとする課題】

[00006]

酸化物半導体を用いたトランジスタにおいて、酸化物半導体膜に含まれる酸素欠損は、トランジスタの電気特性の不良に繋がる。例えば、膜中に酸素欠損が含まれている酸化物半導体を用いたトランジスタは、しきい値電圧がマイナス方向に変動しやすく、ノーマリーオン特性となりやすい。これは、酸化物半導体に含まれる酸素欠損に起因して電荷が生じてしまい、低抵抗化するためである。

[0007]

また、酸化物半導体膜に酸素欠陥が含まれると、経時変化や光ゲートBT(Bias-Temperature)ストレス試験により、トランジスタの電気特性、代表的にはしきい値電圧が変動してしまうという問題がある。

[00008]

そこで、本発明の一態様は、酸化物半導体を用いた半導体装置において、酸素欠損の含有量を低減することを課題の一とする。また、本発明の一態様は、酸化物半導体を用いた半導体装置において、電気特性を向上させることを課題の一とする。

【課題を解決するための手段】

[0009]

本発明の一態様は、プラズマCVD法を用いて化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を形成することを特徴とする。

[0010]

また、本発明の一態様は、酸化物半導体膜を有するトランジスタと、当該トランジスタ上に形成される保護膜とを有する半導体装置において、当該保護膜として、プラズマ C V D 法を用いて化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を形成することを特徴とする。

[0011]

また、本発明の一態様は、酸化物半導体膜を有するトランジスタと、当該トランジスタ上に形成される保護膜とを有する半導体装置において、真空排気された処理室内に載置された基板を180 以上260 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100 Pa以上250 Pa以下とし、処理室内に設けられる電極に0.17W/cm²以上0.5W/cm²以下の高周波電力を供給する条件により、上記保護膜として化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を形成することを特徴とする。

[0012]

また、本発明の一態様は、酸化物半導体膜を有するトランジスタと、当該トランジスタ上に形成される保護膜とを有する半導体装置において、真空排気された処理室内に載置された基板を180 以上260 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下とし、処理室内に設けられる電極に0.17W/cm²以上0.5W/cm²以下の高周波電力を供給する条件により、上記保護膜として化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を形成した後、加熱処理を行い、保護膜に含まれる酸素を酸化物半導体膜に拡散させることを特徴とする。

[0013]

また、本発明の一態様は、ゲート電極と、ゲート電極の一部とゲート絶縁膜を介して重なる酸化物半導体膜と、酸化物半導体膜に接する一対の電極とを有するトランジスタと、酸化物半導体膜上に設けられる保護膜と、を有し、保護膜は、電子スピン共鳴測定によるg = 2.001に現れる信号のスピン密度が1.5×10<sup>18</sup>spins/cm³未満であ

10

20

30

40

る酸化絶縁膜である。

[0014]

なお、一対の電極は、ゲート絶縁膜及び酸化物半導体膜の間に設けられる。または、一対の電極は、酸化物半導体膜及び保護膜の間に設けられる。

[0015]

また、本発明の一態様は、酸化物半導体膜と、酸化物半導体膜に接する一対の電極と、酸化物半導体膜上に設けられるゲート絶縁膜と、酸化物半導体膜の一部とゲート絶縁膜を介して重なるゲート電極とを有するトランジスタと、ゲート絶縁膜及びゲート電極を覆う保護膜と、を有し、保護膜は、電子スピン共鳴測定によるg=2.001に現れる信号のスピン密度が1.5×10<sup>18</sup> spins/cm³未満である酸化絶縁膜であることを特徴とする半導体装置である。

10

【発明の効果】

[0016]

酸化物半導体を有するトランジスタにおいて、トランジスタ上に形成される保護膜として化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を形成することで、更には当該保護膜から酸化物半導体膜に酸素を拡散させることで、酸化物半導体膜に含まれる酸素欠損量を低減することができる。このため、本発明の一態様により、優れた電気特性を有する半導体装置を作製することができる。

【図面の簡単な説明】

[0017]

20

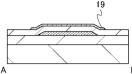

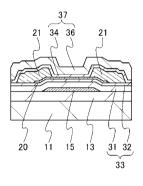

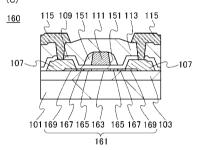

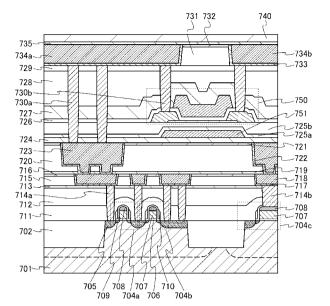

- 【図1】トランジスタの一形態を説明する上面図及び断面図である。

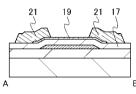

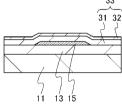

- 【 図 2 】 ト ラ ン ジ ス タ の 作 製 方 法 の 一 形 態 を 説 明 す る 断 面 図 で あ る 。

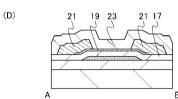

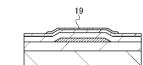

- 【図3】トランジスタの一形態を説明する断面図である。

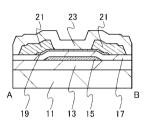

- 【 図 4 】 トランジスタの作製方法の一形態を説明する断面図である。

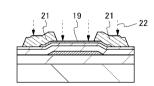

- 【図5】トランジスタの一形態を説明する上面図及び断面図である。

- 【 図 6 】 トランジスタの作製方法の一形態を説明する断面図である。

- 【図7】トランジスタの一形態を説明する上面図及び断面図である。

- 【図8】トランジスタの一形態を説明する上面図及び断面図である。

- 【図9】トランジスタの一形態を説明する断面図である。

- 【図10】トランジスタの一形態を説明する断面図である。

- 【図11】トランジスタの一形態を説明する断面図である。

- 【図12】トランジスタの一形態を説明する断面図である。

- 【図13】半導体装置の一形態を説明する断面図である。

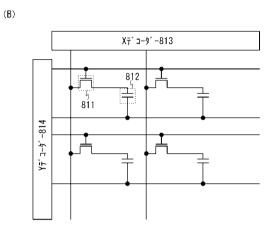

- 【図14】半導体装置の一形態を示す回路図である。

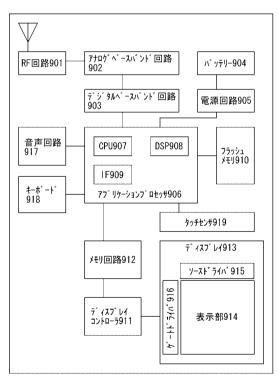

- 【図15】半導体装置の一形態を示すブロック図である。

- 【図16】半導体装置の一形態を示すブロック図である。

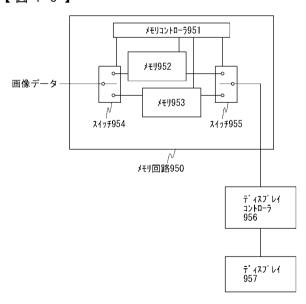

- 【図17】半導体装置の一形態を示すブロック図である。

- 【図18】作製した試料のTDS分析結果を示す図である。

- 【図19】作製した試料の酸素分子脱離量を示す図である。

- 【図20】作製した試料のTDS分析結果を示す図である。

- 【 図 2 1 】作製した試料における電力と、単位面積あたりのスピン数の関係を示す図である。

- 【図22】作製した試料におけるシラン流量と、単位面積あたりのスピン数の関係を示す図である。

- 【図23】作製した試料のCPM測定結果を示す図である。

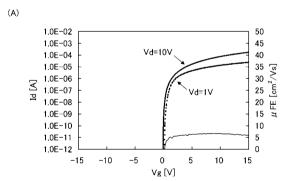

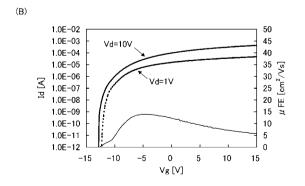

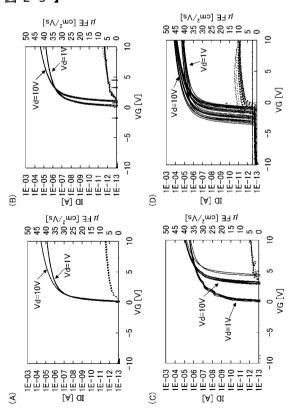

- 【図24】作製した試料の電流・電圧特性の初期特性を示す図である。

- 【図25】作製した試料の電流-電圧特性の初期特性を示す図である。

- 【図26】C-V測定用のMOS構造素子を示す図である。

- 【図27】作製した試料のC-V測定結果を示す図である。

- 【図28】作製した試料のESR測定結果を示す図である。

30

40

【図29】作製した試料の欠陥密度とヒステリシス量の関係を示す図である。

【発明を実施するための形態】

#### [0018]

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。また、以下に説明する実施の形態及び実施例において、同一部分または同様の機能を有する部分には、同一の符号または同一のハッチパターンを異なる図面間で共通して用い、その繰り返しの説明は省略する。

[0019]

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、または領域は、明 瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない

### [0020]

また、本明細書にて用いる第1、第2、第3などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

[ 0 0 2 1 ]

「ソース」や「ドレイン」の機能は、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

[0022]

本明細書において、フォトリソグラフィ工程を行った後にエッチング工程を行う場合は、 フォトリソグラフィ工程で形成したマスクはエッチング工程後に除去するものとする。

[0023]

(実施の形態1)

本実施の形態では、本発明の一態様である半導体装置、及び当該半導体装置の作製方法について図面を参照して説明する。

[0024]

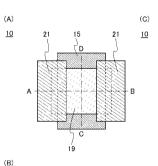

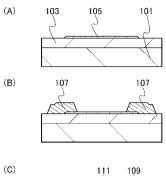

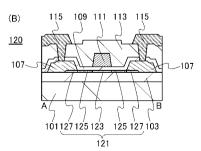

図 1 ( A )乃至図 1 ( C )に、半導体装置が有するトランジスタ 1 0 の上面図及び断面図を示す。図 1 ( A )はトランジスタ 1 0 の上面図であり、図 1 ( B )は、図 1 ( A )の一点鎖線 A - B 間の断面図であり、図 1 ( C )は、図 1 ( A )の一点鎖線 C - D 間の断面図である。なお、図 1 ( A )では、明瞭化のため、トランジスタ 1 0 の構成要素の一部(例えば、基板 1 1、下地絶縁膜 1 3、ゲート絶縁膜 1 7)、保護膜 2 3 などを省略している

[0025]

図1(B)及び図1(C)に示すトランジスタ10は、下地絶縁膜13上に形成されるゲート電極15と、下地絶縁膜13及びゲート電極15上に形成されるゲート絶縁膜17と、ゲート絶縁膜17を介して、ゲート電極15と重なる酸化物半導体膜19と、酸化物半導体膜19に接する一対の電極21と、を有する。また、ゲート絶縁膜17、酸化物半導体膜19、及び一対の電極21を覆う保護膜23を有する。

[0026]

本実施の形態に示すトランジスタ10は、保護膜23が、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜である。さらに好ましくは、保護膜23は、酸化物半導体膜19に含まれる酸素欠損量以上の酸素を含む。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜は、加熱により酸素の一部が脱離する酸化絶縁膜である。このため、加熱により酸素の一部が脱離する酸化絶縁膜を保護膜23として設けることで、加熱処理により酸化物半導体膜19に含まれる酸素欠損を補填することが可能である。この結果、酸化物半導体膜19に含まれる酸素欠損量

10

20

30

40

20

30

40

50

が低減され、しきい値電圧のマイナスシフトを抑制したトランジスタとなる。また、経時変化や光ゲートBTストレスによって、しきい値電圧の変動が少なく、優れた電気特性を有するトランジスタとなる。

#### [0027]

なお、トランジスタ10においては、保護膜23に含まれる酸素は、直接、酸化物半導体膜19に移動すると共に、ゲート絶縁膜17及び保護膜23が接する領域からゲート絶縁膜17を介して、酸化物半導体膜19に移動する。

### [0028]

また、保護膜23において、電子スピン共鳴測定によるg=2.001に現れる信号のスピン密度が1.5×10<sup>18</sup>spins/cm³未満、さらには1.0×10<sup>18</sup>spins/cm³未満、さらには1.0×10<sup>18</sup>spins/cm³以下であることが好ましい。保護膜23のスピン密度が上記範囲を満たすことで、酸化物半導体膜19及び保護膜23の界面、並びに保護膜23における欠陥を低減することが可能であり、当該領域における電子のトラップを低減することができる。この結果、トランジスタの電気特性において、異なるドレイン電圧におけるオン電流の立ち上がり電圧が略同一となる。即ち、優れた電気特性を有するトランジスタを作製することができる。なお、保護膜23の上記スピン密度は加熱処理後の値である。

### [0029]

保護膜 2 3 としては、厚さが 3 0 n m 以上 5 0 0 n m 以下、好ましくは 1 0 0 n m 以上 4 0 0 n m 以下の酸化シリコン膜、酸化窒化シリコン膜等を用いることができる。

#### [0030]

以下に、トランジスタ10の他の構成の詳細について説明する。

#### [ 0 0 3 1 ]

基板 1 1 の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板 1 1 として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板 1 1 として用いてもよい。

# [0032]

また、基板 1 1 として、可撓性基板を用い、可撓性基板上に直接、下地絶縁膜 1 3 及びトランジスタ 1 0 を形成してもよい。または、基板 1 1 と下地絶縁膜 1 3 の間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板 1 1 より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ 1 0 は耐熱性の劣る基板や可撓性の基板にも転載できる。

# [0033]

下地絶縁膜13としては、酸化シリコン、酸化窒化シリコン、窒化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム、酸化窒化アルミニウム等がある。なお、下地絶縁膜13として、窒化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム等を用いることで、基板11から酸化物半導体膜19へ、アルカリ金属、水、水素等の不純物が拡散することを抑制できる

#### [0034]

ゲート電極15は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いてもよい。また、ゲート電極15は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、チ

タン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いてもよい。

[0035]

また、ゲート電極 1 5 は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

[0036]

また、ゲート電極15とゲート絶縁膜17との間に、In-Ga-Zn系酸窒化物半導体膜、In-Sn系酸窒化物半導体膜、In-Ga系酸窒化物半導体膜、In-Zn系酸窒化物半導体膜、In-Zn系酸窒化物半導体膜、金属窒化膜(InN、ZnN等)等を設けることが好ましい。これらの膜は5eV以上、好ましくは5.5eV以上の仕事関数を有し、酸化物半導体の電子親和力よりも大きい値であるため、酸化物半導体を用いたトランジスタのしきい値電圧をプラスにすることができ、所謂ノーマリーオフ特性のスイッチング素子を実現できる。例えば、In-Ga-Zn系酸窒化物半導体膜を用いる場合、少なくとも酸化物半導体膜19より高い窒素濃度、具体的には7原子%以上のIn-Ga-Zn系酸窒化物半導体膜を用いる。

[0037]

ゲート絶縁膜17としては、例えば酸化シリコン、酸化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物、などを用いればよく、積層または単層で設ける。また、ゲート絶縁膜17において酸化物半導体膜19に接する側に、加熱により酸素が脱離する酸化絶縁膜を用いることで、酸化物半導体膜19たに加熱により酸素が脱離するにとが可能であり、電極側に、酸素、水等のブロッキング効果を有する絶縁膜を設けることができる。また、ゲート絶縁膜17のゲート電極側に、酸素、水等のブロッキング効果を有する絶縁膜を設けることで、酸化物半導体膜19からの酸素の外部への拡散と、外部から酸化物半導体膜19への水素、水の侵入を防ぐことができる。酸素、水素、水等のブロッキング効果を有する絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化質化ガリウム、酸化窒化ガリウム、酸化

[ 0 0 3 8 ]

また、ゲート絶縁膜 1 7 として、ハフニウムシリケート(HfSiO $_{\rm x}$ )、窒素が添加されたハフニウムシリケート(HfSi $_{\rm x}$ О $_{\rm y}$ N $_{\rm z}$ )、窒素が添加されたハフニウムアルミネート(HfAl $_{\rm x}$ О $_{\rm y}$ N $_{\rm z}$ )、酸化ハフニウム、酸化イットリウムなどのhigh-k材料を用いることでトランジスタのゲートリークを低減できる。

[0039]

ゲート絶縁膜17の厚さは、5 n m 以上400n m 以下、より好ましくは10n m 以上3 00n m 以下、より好ましくは50n m 以上250n m 以下とするとよい。

[0040]

酸化物半導体膜19は、少なくともインジウム(In)若しくは亜鉛(Zn)を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーの一または複数を有することが好ましい。

[0041]

スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、またはジルコニウム(Zr)等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(P

10

20

30

40

r )、ネオジム(N d )、サマリウム(S m )、ユウロピウム(E u )、ガドリニウム(G d )、テルビウム(T b )、ジスプロシウム(D y )、ホルミウム(H o )、エルビウム(E r )、ツリウム(T m )、イッテルビウム(Y b )、ルテチウム(L u )等がある

### [0042]

例えば、酸化物半導体として、酸化インジウム、酸化五ズ、酸化亜鉛、二元系金属酸化物であるIn-Zn系金属酸化物、Sn-Zn系金属酸化物、Al-Zn系金属酸化物、Zn-Mg系金属酸化物、Sn-Mg系金属酸化物、In-Mg系金属酸化物(IGZOとも表系金属酸化物、三元系金属酸化物であるIn-Sn-Zn系金属酸化物(IGZOとも表記する)、In-Al-Zn系金属酸化物、In-Sn-Zn系金属酸化物、Sn-Al-Zn系金属酸化物、In-Hf-Zn系金属酸化物、In-Ce-Zn系金属酸化物、In-Ce-Zn系金属酸化物、In-Bu-Zn系金属酸化物、In-Gd-Zn系金属酸化物、In-Sm-Zn系金属酸化物、In-Br-Zn系金属酸化物、In-Ho-Zn系金属酸化物、In-Ho-Zn系金属酸化物、In-Ho-Zn系金属酸化物、In-Br-Sh-Al-Zn系金属酸化物、In-Al-Ga-Zn系金属酸化物、In-Al-Ga-Zn系金属酸化物、In-Al-Ga-Zn系金属酸化物、In-Al-Zn系金属酸化物、In-Sn-Hf-Zn系金属酸化物、In-Sn-Hf-Zn系金属酸化物、In-Sn-Hf-Zn系金属酸化物、In-Sn-Hf-Zn系金属酸化物、In-Hf-Zn系金属酸化物、In-Hf-Zn系金属酸化物、In-Hf-Zn系金属酸化物を用いることができる。

# [0043]

なお、ここで、例えば、In-Ga-Zn系金属酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

#### [0044]

# [ 0 0 4 5 ]

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)、In:Ga:Zn=2:2:1(=2/5:2/5:1/5)、あるいはIn:Ga:Zn=3:1:2(=1/2:1/6:1/3)の原子数比のIn-Ga・Zn系金属酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn-Sn・Zn系金属酸化物やその組成の近傍の酸化物を用いるとよい。なお、金属酸化物の原子数比は、誤差として上記の原子数比のプラスマイナス20%の変動を含む。

#### [0046]

しかし、これらに限られず、必要とする半導体特性及び電気特性(電界効果移動度、 しきい値電圧等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性及び電気特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

# [0047]

例えば、In-Sn-Zn系金属酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系金属酸化物でも、バルク内欠陥密度を低くすることにより移動度を上げることができる。

# [0048]

また、酸化物半導体膜19に形成することが可能な金属酸化物は、エネルギーギャップが 2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように 10

20

30

40

20

30

40

50

、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタのオフ電流を低減することができる。

# [0049]

また、酸化物半導体膜 1 9 は、非晶質構造、単結晶構造、または多結晶構造であってもよい。

# [0050]

また、酸化物半導体膜19は、例えば非単結晶を有してもよい。非単結晶は、例えば、CAAC(CAXis Aligned Crystal)、多結晶、微結晶、非晶質部の一以上を有する。非晶質部は、微結晶、CAACよりも欠陥準位密度が高い。また、微結晶は、CAACよりも欠陥準位密度が高い。なお、CAACを有する酸化物半導体を、CAAC・OS(CAXis Aligned Crystal Oxide Semiconductor)と呼ぶ。CAAC・OSは、例えば、c軸配向し、a軸または/およびb軸はマクロに揃っていない。

# [0051]

酸化物半導体膜19は、例えば微結晶を有してもよい。なお、微結晶を有する酸化物半導体を、微結晶酸化物半導体と呼ぶ。微結晶酸化物半導体膜は、例えば、1nm以上10nm未満のサイズの微結晶(ナノ結晶ともいう。)を膜中に含む。

#### [0052]

酸化物半導体膜19は、例えば非晶質部を有してもよい。なお、非晶質部を有する酸化物 半導体を、非晶質酸化物半導体と呼ぶ。非晶質酸化物半導体膜は、例えば、原子配列が無 秩序であり、結晶成分を有さない。または、非晶質酸化物半導体膜は、例えば、完全な非 晶質であり、結晶部を有さない。

### [0053]

なお、酸化物半導体膜19が、CAAC-OS、微結晶酸化物半導体、非晶質酸化物半導体の混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-OSの領域と、を有する。また、混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、CAAC-OSの領域と、の積層構造を有してもよい。

# [0054]

なお、酸化物半導体膜19は、例えば、単結晶を有してもよい。酸化物半導体膜は、複数の結晶部を有し、当該結晶部の c 軸が被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃っていることが好ましい。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。そのような酸化物半導体膜の一例としては、 C A A C - O S 膜がある。

# [0055]

ここでCAAC-OS膜の詳細について説明する。CAAC-OS膜に結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC-OS膜に含まれる結晶部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には明確な粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

# [0056]

CAAC・OS膜に含まれる結晶部は、例えば c 軸が CAAC・OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃い、かつ a b 面に垂直な方向から見て金属原子が三角形状または六角形状に配列を有し、 c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸及び b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、80°以上10°以下、好ましくは85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-10°以上10°以下、好まし

くは・5°以上5°以下の範囲も含まれることとする。

#### [0057]

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部の結晶性が低下することもある。

### [0058]

CAAC-OS膜に含まれる結晶部の c軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃うため、CAAC-OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。また、結晶部は、成膜したとき、または成膜後に加熱処理などの結晶化処理を行ったときに形成される。従って、結晶部の c軸は、CAAC-OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃う。

#### [0059]

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

#### [0060]

また、酸化物半導体膜19は、複数の酸化物半導体膜が積層された構造でもよい。例えば、酸化物半導体膜19を、第1の酸化物半導体膜と第2の酸化物半導体膜の積層として、第1の酸化物半導体膜と第2の酸化物半導体膜に、異なる組成の金属酸化物を用いてもよい。例えば、第1の酸化物半導体膜に二元系金属酸化物乃至四元系金属酸化物の一を用い、第2の酸化物半導体膜に第1の酸化物半導体膜と異なる二元系金属酸化物乃至四元系金属酸化物を用いてもよい。

#### [0061]

また、第1の酸化物半導体膜と第2の酸化物半導体膜の構成元素を同一とし、両者の組成を異ならせてもよい。例えば、第1の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1とし、第2の酸化物半導体膜の原子数比をIn:Ga:Zn=3:1:2としてもよい。また、第1の酸化物半導体膜の原子数比をIn:Ga:Zn=1:3:2とし、第2の酸化物半導体膜の原子数比をIn:Ga:Zn=2:1:3としてもよい。なお、各酸化物半導体膜の原子数比は、誤差として上記の原子数比のプラスマイナス20%の変動を含む。

#### [0062]

この時、第1の酸化物半導体膜と第2の酸化物半導体膜のうち、ゲート電極に近い側(チャネル側)の酸化物半導体膜のInとGaの含有率をIn>Gaとするとよい。またゲート電極から遠い側(バックチャネル側)の酸化物半導体膜のInとGaの含有率をInGaとするとよい。

### [0063]

酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、より多くのs軌道が重なるため、In>Gaの組成となる酸化物はIn Gaの組成となる酸化物と比較して高い移動度を備える。また、GaはInと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、In Gaの組成となる酸化物はIn>Gaの組成となる酸化物と比較して安定した特性を備える。

# [0064]

チャネル側にIn > G a の組成となる酸化物半導体を適用し、バックチャネル側にIn G a の組成となる酸化物半導体を適用することで、トランジスタの電界効果移動度および信頼性をさらに高めることが可能となる。

# [0065]

また、第1の酸化物半導体膜と第2の酸化物半導体膜に、結晶性の異なる酸化物半導体を適用してもよい。すなわち、単結晶酸化物半導体、多結晶酸化物半導体、微結晶酸化物半

10

20

30

40

20

30

40

50

導体、非晶質酸化物半導体、または C A A C - O S を適宜組み合わせた構成としてもよい。また、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜の少なくともどちらか一方に非晶質酸化物半導体を適用すると、酸化物半導体膜 1 9 の内部応力や外部からの応力を緩和し、トランジスタの特性ばらつきが低減され、また、トランジスタの信頼性をさらに高めることが可能となる。

[0066]

酸化物半導体膜19の厚さは、1nm以上100nm以下、更に好ましくは1nm以上50nm以下、更に好ましくは1nm以上30nm以下、更に好ましくは3nm以上20nm以下とすることが好ましい。

[ 0 0 6 7 ]

酸化物半導体膜19において、アルカリ金属またはアルカリ土類金属の濃度は、1×10<sup>18</sup>atoms/cm<sup>3</sup>以下、さらに好ましくは2×10<sup>16</sup>atoms/cm<sup>3</sup>以下であることが望ましい。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流の上昇の原因となるためである

[0068]

酸化物半導体膜19には、5×10<sup>18</sup> a t o m s / c m <sup>3</sup> 以下の窒素が含まれてもよい

[0069]

一対の電極 2 1 は、導電材料として、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタングステンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、タングステン膜上にチタン膜を積層する二層構造、銅・マグネシウム・アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または窒化モリブデン膜または窒化モリブデン膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。な、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

[ 0 0 7 0 ]

なお、ここでは、一対の電極 2 1 は、酸化物半導体膜 1 9 及び保護膜 2 3 の間に設けられているが、ゲート絶縁膜 1 7 及び酸化物半導体膜 1 9 の間に一対の電極 2 1 を設けてもよい。

[0071]

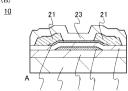

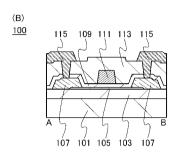

次に、図1に示すトランジスタの作製方法について、図2を用いて説明する。

[ 0 0 7 2 ]

図 2 ( A )に示すように、基板 1 1 上に下地絶縁膜 1 3 及びゲート電極 1 5 を形成し、ゲート電極 1 5 上にゲート絶縁膜 1 7 を形成する。次に、ゲート絶縁膜 1 7 上に酸化物半導体膜 1 8 を形成する。

[ 0 0 7 3 ]

下地絶縁膜13は、スパッタリング法、CVD法等により形成する。ここでは、厚さ10 0nmの酸化窒化シリコン膜をCVD法により形成する。

[0074]

ゲート電極 1 5 の形成方法を以下に示す。はじめに、スパッタリング法、 C V D 法、蒸着法等により導電膜を形成し、導電膜上にフォトリソグラフィエ程によりマスクを形成する。次に、該マスクを用いて導電膜の一部をエッチングして、ゲート電極 1 5 を形成する。この後、マスクを除去する。

[0075]

なお、ゲート電極15は、上記形成方法の代わりに、電解メッキ法、印刷法、インクジェ

20

30

40

50

ット法等で形成してもよい。

[0076]

ここでは、厚さ100nmのタングステン膜をスパッタリング法により形成する。次に、フォトリソグラフィエ程によりマスクを形成し、当該マスクを用いてタングステン膜をドライエッチングして、ゲート電極15を形成する。

[0077]

ゲート絶縁膜17は、スパッタリング法、CVD法、蒸着法等で形成する。

[0078]

ここでは、厚さ 5 0 n m の窒化シリコン膜を C V D 法により形成した後、厚さ 2 0 0 n m の酸化窒化シリコン膜を C V D 法により形成することで、ゲート絶縁膜 1 7 を形成する。

[0079]

酸化物半導体膜18は、スパッタリング法、塗布法、パルスレーザー蒸着法、レーザーア ブレーション法等により形成する。

[0800]

スパッタリング法で酸化物半導体膜18を形成する場合、プラズマを発生させるための電源装置は、RF電源装置、AC電源装置、DC電源装置等を適宜用いることができる。

[0081]

スパッタリングガスは、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲気、希ガス及び酸素の混合ガス雰囲気を適宜用いる。なお、希ガス及び酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。

[0082]

また、ターゲットは、形成する酸化物半導体膜18の組成にあわせて、適宜選択すればよい。

[0083]

なお、酸化物半導体膜18を形成する際に、例えば、スパッタリング法を用いる場合、基板温度を150 以上750 以下、好ましくは150 以上450 以下、さらに好ましくは200 以上350 以下として、酸化物半導体膜18を成膜することで、CAAC-OS膜を形成することができる。

[0084]

なお、 C A A C - O S 膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域が a - b 面から劈開し、 a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、 C A A C - O S 膜を成膜することができる。

[0085]

また、CAAC-OS膜を成膜するために、以下の条件を適用することが好ましい。

[0086]

成膜時の不純物混入を抑制することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度(水素、水、二酸化炭素および窒素など)を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80 以下、好ましくは-100 以下である成膜ガスを用いる。

[0087]

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を100 以上基板歪み点未満、好ましくは200 以上500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

[ 0 0 8 8 ]

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージ

を軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

# [0089]

スパッタリング用ターゲットの一例として、 In - Ga - Zn 系金属酸化物ターゲットについて以下に示す。

# [0090]

# [0091]

次に、図2(B)に示すように、素子分離された酸化物半導体膜19がゲート絶縁膜17上にあって、ゲート電極15の一部と重なるように形成する。酸化物半導体膜18上にフォトリソグラフィエ程によりマスクを形成した後、該マスクを用いて酸化物半導体膜18の一部をエッチングすることで、素子分離された酸化物半導体膜19を形成することができる。

# [0092]

また、酸化物半導体膜19として印刷法を用いることで、素子分離された酸化物半導体膜 19を直接的に形成することができる。

### [0093]

ここでは、スパッタリング法により、厚さ 3 5 n m の酸化物半導体膜 1 8 を形成した後、当該酸化物半導体膜 1 8 上にマスクを形成し、酸化物半導体膜 1 8 の一部を選択的にエッチングすることで、酸化物半導体膜 1 9 を形成する。こののち、マスクを除去する。

#### [0094]

次に、図2(C)に示すように、一対の電極21を形成する。

# [0095]

一対の電極 2 1 の形成方法を以下に示す。はじめに、スパッタリング法、 C V D 法、蒸着法等で導電膜を形成する。次に、該導電膜上にフォトリソグラフィエ程によりマスクを形成する。次に、該マスクを用いて導電膜をエッチングして、一対の電極 2 1 を形成する。この後、マスクを除去する。

# [0096]

ここでは、スパッタリング法により厚さ 5 0 n m のタングステン膜、厚さ 4 0 0 n m のアルミニウム膜、及び厚さ 1 0 0 n m のチタン膜を順にスパッタリング法により積層する。次に、チタン膜上にフォトリソグラフィ工程によりマスクを形成し、当該マスクを用いてタングステン膜、アルミニウム膜、及びチタン膜をドライエッチングして、一対の電極 2 1 を形成する。

### [0097]

なお、一対の電極21を形成した後、エッチング残渣を除去するため、洗浄処理をすることが好ましい。この洗浄処理を行うことで、一対の電極21の短絡を抑制することができる。当該洗浄処理は、TMAH(Tetramethylammonium Hydroxide)溶液などのアルカリ性の溶液、希フッ酸、シュウ酸、リン酸などの酸性の溶液、または水を用いて行うことができる。

# [0098]

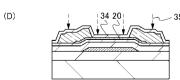

次に、図2(D)に示すように、保護膜23を形成する。

#### [0099]

保護膜 2 3 は一対の電極 2 1 を形成した後、プラズマ C V D 装置の真空排気された処理室内に載置された基板 1 1 を 1 8 0 以上 2 6 0 以下、好ましくは 1 8 0 以上 2 5 0

10

20

30

-

40

以下、さらに好ましくは 1 8 0 以上 2 3 0 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を 1 0 0 Pa以上 2 5 0 Pa以下、さらに好ましくは 1 0 0 Pa以上 2 0 0 Pa以下とし、処理室内に設けられる電極に 0 . 1 7 W / c m <sup>2</sup>以上 0 . 5 W / c m <sup>2</sup>以下、好ましくは 0 . 2 5 W / c m <sup>2</sup>以上 0 . 4 0 W / c m <sup>2</sup>以下、さらに好ましくは 0 . 2 6 W / c m <sup>2</sup>以上 0 . 3 5 W / c m <sup>2</sup>以下の高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を基板 1 1 上に形成する。

#### [0 1 0 0]

保護膜23の原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

#### [0101]

保護膜23の成膜条件として、上記圧力の処理室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、シリコンを含む堆積性気体の酸化が進むため、保護膜23中における酸素含有量が化学量論的組成よりも多くなる。一方、基板温度が、上記温度で形成された膜では、シリコンと酸素の結合力が弱いため、後の工程の加熱処理により膜中の酸素の一部が脱離する。これらの結果、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を形成することができる。即ち、加熱により酸素の一部が脱離する酸化絶縁膜を形成することができる。

### [0102]

なお、保護膜23の原料ガスとして、酸化性気体に対するシリコンを含む堆積性気体の割合を多くし、且つ高周波電力を上記パワー密度とすることで、堆積速度を速くできると共に、保護膜に含まれる酸素含有量を増加させることができる。

#### [ 0 1 0 3 ]

ここでは、保護膜23として、流量160sccmのシラン及び流量4000sccmの一酸化二窒素を原料ガスとし、処理室の圧力を200Pa、基板温度を220 とし、27.12MHzの高周波電源を用いて1500Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ400nmの酸化窒化シリコン膜を形成する。なお、プラズマCVD装置は電極面積が6000cm²である平行平板型のプラズマCVD装置であり、供給した電力を単位面積あたりの電力(電力密度)に換算すると0.25W/cm²である。

# [0104]

次に、加熱処理を行うことで、保護膜23に含まれる酸素を酸化物半導体膜19に拡散させ、酸化物半導体膜19に含まれる酸素欠損を補填することで、酸化物半導体膜19に含まれる酸素欠損量を低減することができる。また、保護膜23形成後の加熱処理により、保護膜23の電子スピン共鳴測定によるg=2.001に現れる信号のスピン密度が1.5×10<sup>18</sup>spins/cm<sup>3</sup>以下となる。該加熱処理の温度は、代表的には、150 以上基板歪み点未満、好ましくは250 以上450 以下とする。

### [0105]

なお、当該加熱処理の温度を保護膜23の成膜温度より高くすることで、保護膜23に含まれる酸素をより多く酸化物半導体膜19に拡散させ、酸化物半導体膜19に含まれる酸素欠損を補填することができる。この時の加熱処理の温度は、250 以上基板歪み点未満、好ましくは250 以上450 以下、更に好ましくは300 以上450 以下とすることができる。

# [0106]

該加熱処理は、電気炉、RTA(Rapid Thermal Anneal)装置等を用いることができる。RTA装置を用いることで、短時間に限り、基板の歪み点以上の温度で熱処理を行うことができる。そのため、保護膜23から酸化物半導体膜19への酸素拡散時間を短縮することができる。

10

20

30

20

30

40

50

#### [0107]

加熱処理は、窒素、酸素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウム等)の雰囲気下で行えばよい。

# [0108]

ここでは、窒素及び酸素雰囲気で、350、1時間の加熱処理を行い、保護膜23に含まれる酸素を酸化物半導体膜19に拡散する。本実施の形態においては、保護膜23からの固相拡散により、酸化物半導体膜19に酸素を拡散させることが可能であるため、ダメージが少なく、酸化物半導体膜19に酸素を添加することができる。

#### [0109]

以上の工程により、しきい値電圧のマイナスシフトを抑制した、優れた電気特性を有するトランジスタを作製することができる。また、経時変化や光ゲートBTストレス試験による電気特性の変動の少ない、信頼性の高いトランジスタを作製することができる。

# [0110]

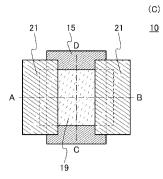

次に、図1と異なる構造のトランジスタについて、図3及び図4を用いて説明する。ここでは、トランジスタ10と比較して、酸化物半導体膜に接するように緻密で膜密度の高い膜を設ける構造について、図3を用いて説明する。

#### [0111]

図3に示すトランジスタ30は、基板11上に設けられる下地絶縁膜13と、下地絶縁膜13上に形成されるゲート電極15とを有する。また、下地絶縁膜13及びゲート電極15上に、絶縁膜31及び絶縁膜32で構成されるゲート絶縁膜33が形成され、ゲート絶縁膜33を介して、ゲート電極15と重なる酸化物半導体膜20と、酸化物半導体膜20に接する一対の電極21とを有する。また、ゲート絶縁膜33、酸化物半導体膜20、及び一対の電極21上には、絶縁膜34及び絶縁膜36で構成される保護膜37が形成される。

# [0112]

本実施の形態に示すトランジスタ30において、酸化物半導体膜20が、酸化雰囲気で発生したプラズマに曝されている。酸化雰囲気としては、酸素、オゾン、一酸化二窒素等の雰囲気がある。さらには、プラズマ処理において、平行平板型のプラズマCVD装置を用い、上部電極にバイアスを印加し、基板11が搭載される下部電極にバイアスを印加しない状態で発生させたプラズマに酸化物半導体膜を曝すことが好ましい。この結果、ダメージが少なく、且つ酸素が酸化物半導体膜20に供給されるため、酸化物半導体膜20に含まれる酸素欠損量を低減することができる。

# [0113]

また、トランジスタ30は、酸化物半導体膜20に接するように、絶縁膜32及び絶縁膜34が形成されている。絶縁膜32及び絶縁膜34は、緻密な膜であり、膜密度が高い。このため、後に形成する絶縁膜36の形成工程において、酸化物半導体膜20へのダメージ低減が可能である。

# [0114]

絶縁膜32及び絶縁膜34としては、厚さが5nm以上400nm以下、好ましくは5nm以上50nm以下、より好ましくは10nm以上30nm以下の酸化シリコン膜、酸化窒化シリコン膜等を用いることができる。

# [0115]

また、トランジスタ30上に設けられる保護膜37の一部である絶縁膜36が、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜である。さらに好ましくは、絶縁膜36は、酸化物半導体膜20に含まれる酸素欠損量以上の酸素を含む。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜は、加熱により酸素の一部が脱離する酸化絶縁膜である。このため、加熱により酸素の一部が脱離する酸化絶縁膜を保護膜37として設けることで、加熱処理により酸化物半導体膜20に酸素を拡散させることができる。加熱処理により、絶縁膜36に含まれる酸素が酸化物半導体膜20に拡散し、酸化物半

20

30

40

50

導体膜20に含まれる酸素欠損を補填することが可能である。この結果、酸化物半導体膜20に含まれる酸素欠損量が低減され、しきい値電圧のマイナスシフトが抑制されたトランジスタとなる。また、経時変化や光ゲートBTストレス試験によって、しきい値電圧の変動が少なく、優れた電気特性を有するトランジスタとなる。

[0116]

なお、トランジスタ 3 0 においては、絶縁膜 3 6 に含まれる酸素は、絶縁膜 3 1 、絶縁膜 3 2 、及び絶縁膜 3 4 の一以上を介して、酸化物半導体膜 2 0 に移動する。

[0117]

次に、図3に示すトランジスタの作製方法について、図4を用いて説明する。

[0118]

図4(A)に示すように、基板11上に実施の形態1と同様に、下地絶縁膜13及びゲート電極15を形成する。次に、ゲート絶縁膜33として機能する絶縁膜31及び絶縁膜3 2を形成する。

[0119]

絶縁膜31としては、CVD法により厚さ5nm以上400nm以下の窒化シリコン膜または窒化酸化シリコン膜を形成する。次に、絶縁膜32として、CVD法により厚さ5nm以上400nm以下の酸化シリコン膜または酸化窒化シリコン膜を形成する。なお、絶縁膜31及び絶縁膜32の厚さは、2つの絶縁膜の合計の厚さが図1に示すトランジスタ10のゲート絶縁膜17の範囲となるように、適宜選択すればよい。

[0120]

ここでは、絶縁膜31として、流量50sccmのシラン及び流量5000sccmの一酸化二窒素を原料ガスとし、処理室の圧力を60Pa、基板温度を350 とし、27.12MHzの高周波電源を用いて1500Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ50nmの窒化シリコン膜を形成する。

[0121]

絶縁膜32として、流量20sccmのシラン及び流量3000sccmの一酸化二窒素を原料ガスとし、処理室の圧力を40Pa、基板温度を350 とし、27.12MHzの高周波電源を用いて100Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ200nmの酸化窒化シリコン膜を形成する。当該条件により、緻密な膜であり、絶縁膜31よりも膜密度が高い酸化窒化シリコン膜を形成することができる。

[0122]

ここでは、ゲート絶縁膜33の厚さを厚くすることで、さらに好ましくは抵抗率が5×10<sup>13</sup>・cm以上1×10<sup>15</sup>・cm以下の窒化シリコン膜と、酸化窒化シリコン膜とを積層することで、後に形成されるトランジスタのゲート電極15と、酸化物半導体膜20または一対の電極21との間に発生する静電気破壊を抑制することができる。

[ 0 1 2 3 ]

次に、図4(B)に示すように、実施の形態1と同様に、ゲート絶縁膜33上に酸化物半 導体膜19を形成する。

[0124]

次に、図4(C)に示すように、一対の電極21を形成する。次に、酸化物半導体膜19を酸化雰囲気で発生させたプラズマに曝し、酸化物半導体膜19に酸素22を供給し、図4(D)に示す酸化物半導体膜20を形成する。酸化雰囲気としては、酸素、オゾン、一酸化二窒素等の雰囲気がある。さらに、プラズマ処理において、基板11が搭載される下部電極にバイアスを印加しない状態で発生したプラズマを酸化物半導体膜19に曝さすことが好ましい。この結果、酸化物半導体膜19にダメージを与えず、且つ酸素を供給することが可能である。

[0125]

ここでは、プラズマ C V D 装置の処理室に一酸化二窒素を導入し、処理室に設けられる上部電極に 2 7 . 1 2 M H z の高周波電源を用いて 1 5 0 W の高周波電力を供給して発生させた酸素プラズマに酸化物半導体膜 1 9 を曝す。

#### [0126]

次に、酸化物半導体膜20及び一対の電極21上に絶縁膜34を形成する。ここでは、流 量 20sccmのシラン及び流量 3000sccmの一酸化二窒素を原料ガスとし、処理 室の圧力を200Pa、基板温度を350 とし、27.12MHzの高周波電源を用い て100Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ10n mの酸化窒化シリコン膜を形成する。当該条件により、緻密な膜であり、膜密度が後の工 程で形成される絶縁膜36よりも高い酸化窒化シリコン膜を形成することができる。

### [0127]

次に、絶縁膜34に酸素35を添加してもよい。絶縁膜34に酸素35を添加する方法と しては、イオン注入法、イオンドーピング法、プラズマ処理等がある。この結果、絶縁膜 3 4 を、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜とすることがで きる。

# [ 0 1 2 8 ]

次に、図4(E)に示すように、絶縁膜34上に絶縁膜36を形成する。トランジスタ1 0上に形成された保護膜 2 3 と同様に、プラズマ C V D 装置の真空排気された処理室内に 載置された基板11を180 以上260 以下、好ましくは180 以上250 以下 、さらに好ましくは180 以上230 以下に保持し、処理室に原料ガスを導入して処 理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上 2 0 0 P a 以下とし、処理室内に設けられる電極に 0 . 1 7 W / c m <sup>2</sup> 以上 0 . 5 W / c m<sup>2</sup>以下、好ましくは 0 . 2 5 W / c m<sup>2</sup>以上 0 . 4 0 W / c m<sup>2</sup>以下、さらに好ましく は 0 . 2 6 W / c m <sup>2</sup> 以上 0 . 3 5 W / c m <sup>2</sup> 以下の高周波電力を供給する条件により、 絶 縁 膜 3 4 と し て 酸 化 シ リ コ ン 膜 ま た は 酸 化 窒 化 シ リ コ ン 膜 を 形 成 す る 。

#### [0129]

次に、トランジスタ10と同様に、加熱処理を行うことで、絶縁膜36に含まれる酸素を 酸化物半導体膜20に拡散させ、酸化物半導体膜20に含まれる酸素欠損を補填すること で、酸化物半導体膜20に含まれる酸素欠損量を低減することができる。

以上の工程により、しきい値電圧のマイナスシフトを抑制した、優れた電気特性を有する トランジスタを作製することができる。また、経時変化や光ゲートBTストレス試験によ る電気特性の変動の少ない、信頼性の高いトランジスタを作製することができる。

### [0131]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及 び方法などと適宜組み合わせて用いることができる。

# [ 0 1 3 2 ]

# (実施の形態2)

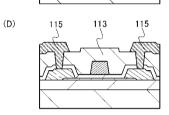

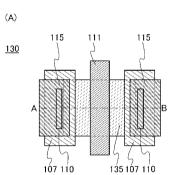

本実施の形態では、実施の形態1及と異なる構造のトランジスタについて、図5を用いて 説 明 す る 。 本 実 施 の 形 態 に 示 す ト ラ ン ジ ス タ 1 0 0 は 、 実 施 の 形 態 1 に 示 す ト ラ ン ジ ス タ と比較して、トップゲート構造のトランジスタである点が異なる。

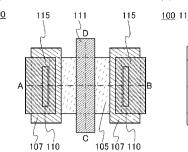

# [ 0 1 3 3 ]

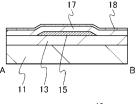

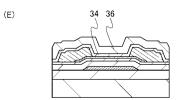

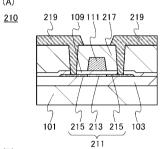

図 5 ( A )乃至図 5 ( C )に、トランジスタ 1 0 0 の上面図及び断面図を示す。図 5 ( A ) はトランジスタ100の上面図であり、図5(B)は、図5(A)の一点鎖線A-B間 の断面図であり、図 5 ( C ) は、図 5 ( A ) の一点鎖線 C - D 間の断面図である。なお、 図 5 ( A )では、明瞭化のため、トランジスタ 1 0 0 の構成要素の一部(例えば、基板 1 01、下地絶縁膜103、ゲート絶縁膜109)、保護膜113などを省略している。

#### [ 0 1 3 4 ]

図 5 ( B )及び図 5 ( C )に示すトランジスタ 1 0 0 は、下地絶縁膜 1 0 3 上に形成され る酸化物半導体膜105と、酸化物半導体膜105に接する一対の電極107と、下地絶 縁 膜 1 0 3 、 酸 化 物 半 導 体 膜 1 0 5 、 及 び 一 対 の 電 極 1 0 7 に 接 す る ゲ ー ト 絶 縁 膜 1 0 9 と、ゲート絶縁膜109を介して酸化物半導体膜105と重なるゲート電極111とを有 する。また、ゲート絶縁膜109及びゲート電極111を覆う保護膜113と、ゲート絶 10

20

30

40

縁膜 1 0 9 及び保護膜 1 1 3 の開口部 1 1 0 (図 5 ( A )参照。)において、一対の電極 1 0 7 と接する配線 1 1 5 とを有してもよい。

#### [0135]

本実施の形態に示すトランジスタ100上に設けられる保護膜113が、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜である。さらに好ましくは、保護膜113は、酸化物半導体膜105に含まれる酸素欠損量以上の酸素を含む。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜は、加熱により酸素の一部が脱離する酸化絶縁膜を保護膜113として設けることで、加熱処理により酸化物半導体膜105に酸素を拡散させ、酸化物半導体膜105に含まれる酸素欠損を補填することが可能である。この結果、酸化物半導体膜105に含まれる酸素欠損を補填することが可能である。この結果、酸化物半導体膜105に含まれる酸素欠損量が低減され、しきい値電圧のマイナスシフトを抑制したトランジスタとなる。また、経時変化や光ゲートBTストレス試験によって、しきい値電圧の変動が少なく、優れた電気特性を有するトランジスタとなる。

[0136]

なお、トランジスタ100においては、保護膜113に含まれる酸素は、下地絶縁膜10 3及びゲート絶縁膜109の一以上を介して、酸化物半導体膜105に移動する。

[0137]

また、保護膜 1 1 3 において、電子スピン共鳴測定による g = 2 . 0 0 1 に現れる信号のスピン密度が 1 .  $5 \times 10^{-1.8}$  s p i n s / c m  $^3$  k 満、好ましくは 1 .  $0 \times 10^{-1.8}$  s p i n s / c m  $^3$  以下であると、優れた電気特性を有するトランジスタとなるため好ましい。

[0138]

保護膜 1 1 3 としては、厚さが 3 0 n m 以上 5 0 0 n m 以下、好ましくは 1 0 0 n m 以上 4 0 0 n m 以下の酸化シリコン膜、酸化窒化シリコン膜等を用いることができる。

[0139]

以下に、トランジスタ100の他の構成の詳細について説明する。

[0140]

基板101は、実施の形態1に示す基板11に列挙する基板を適宜用いることができる。

[0141]

下地絶縁膜103は、加熱により酸素の一部が脱離する酸化絶縁膜を用いて形成することが好ましい。加熱により酸素の一部が脱離する酸化絶縁膜としては、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を用いることが好ましい。加熱により酸素の一部が脱離する酸化絶縁膜は、加熱処理により酸化物半導体膜に酸素を拡散させることができる。下地絶縁膜103の代表例としては、酸化シリコン、酸化室化シリコン、窒化酸化シリコン、酸化ガリウム、酸化ハフニウム、酸化イットリウム、酸化アルミニウム、酸化窒化アルミニウム等がある。

[0142]

下地絶縁膜103は、50nm以上、好ましくは200nm以上3000nm以下、好ましくは300nm以上1000nm以下とする。下地絶縁膜103を厚くすることで、下地絶縁膜103の酸素脱離量を増加させることができると共に、下地絶縁膜103及び後に形成される酸化物半導体膜との界面における界面準位を低減することが可能である。

[0143]

ここで、「加熱により酸素の一部が脱離する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の脱離量が1.0×10<sup>18</sup>atoms/cm<sup>3</sup>以上、好ましくは3.0×10<sup>20</sup>atoms/cm<sup>3</sup>以上であることをいう。

[0144]

上記構成において、加熱により酸素の一部が脱離する絶縁膜は、酸素が過剰な酸化シリコン ( S i O  $_X$  ( X > 2 ) )であってもよい。酸素が過剰な酸化シリコン ( S i O  $_X$  ( X > 2 ) )とは、シリコン原子数の 2 倍より多い酸素原子を単位体積当たりに含むものである

10

20

30

40

。単位体積当たりのシリコン原子数及び酸素原子数は、ラザフォード後方散乱法により測定した値である。

# [0145]

ここで、TDS分析にて、酸素原子に換算しての酸素の脱離量の測定方法について、以下に説明する。

# [0146]

TDS分析したときの気体の脱離量は、スペクトルの積分値に比例する。このため、絶縁膜のスペクトルの積分値と、標準試料の基準値に対する比とにより、気体の脱離量を計算することができる。標準試料の基準値とは、所定の原子を含む試料の、スペクトルの積分値に対する原子の密度の割合である。

### [0147]

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、及び絶縁膜のTDS分析結果から、絶縁膜の酸素分子の脱離量(N<sub>〇2</sub>)は、数式1で求めることができる。ここで、TDS分析で得られる質量数32で検出されるスペクトルの全てが酸素分子由来と仮定する。質量数32のものとしてCH<sub>3</sub>OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子及び質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

# [0148]

$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times ($  数式 1 )

#### [0149]

$N_{H_2}$  は、標準試料から脱離した水素分子を密度で換算した値である。  $S_{H_2}$  は、標準試料を  $T_0$   $D_1$   $S_2$  分析したときのスペクトルの積分値である。 ここで、標準試料の基準値を、  $N_{H_2}$   $I_2$  とする。  $S_{0_2}$  は、絶縁膜を  $T_0$   $I_2$   $I_3$   $I_4$   $I_4$   $I_5$   $I_4$   $I_5$   $I_4$   $I_5$   $I_4$   $I_5$   $I_$

# [0150]

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述の は酸素分子のイオン化率を含むため、酸素分子の脱離量を評価することで、酸素原子の脱離量についても見積もることができる。

# [ 0 1 5 1 ]

なお、N<sub>O2</sub>は酸素分子の脱離量である。絶縁膜においては、酸素原子に換算したときの酸素の脱離量は、酸素分子の脱離量の2倍となる。

### [0152]

下地絶縁膜103から酸化物半導体膜105に酸素が供給されることで、下地絶縁膜103及び酸化物半導体膜105の界面準位を低減できる。この結果、トランジスタの動作などに起因して生じうる電荷などが、上述の下地絶縁膜103及び酸化物半導体膜105の界面に捕獲されることを抑制することができ、電気特性の変動の少ないトランジスタを得ることができる。

# [ 0 1 5 3 ]

即ち、酸化物半導体膜105に酸素欠損が生じると、下地絶縁膜103と酸化物半導体膜105との界面において電荷が捕獲され、当該電荷がトランジスタの電気特性に影響してしまうところ、下地絶縁膜103として、加熱により酸素が脱離する絶縁膜を設けることで、酸化物半導体膜105及び下地絶縁膜103の界面準位を低減し、酸化物半導体膜105及び下地絶縁膜103の界面における電荷捕獲の影響を小さくすることができる。

# [0154]

50

10

20

30

酸化物半導体膜105は、実施の形態1に示す酸化物半導体膜19と同様に形成することができる。

[ 0 1 5 5 ]

一対の電極107は、実施の形態1に示す一対の電極21と同様に形成することができる。なお、一対の電極107において、チャネル幅方向における長さが酸化物半導体膜105より長く、更にはチャネル長方向と交差する端部を覆う構造とし、一対の電極107及び酸化物半導体膜105の接触面積を増大させることで、酸化物半導体膜105と一対の電極107との接触抵抗を低減することが可能であり、トランジスタのオン電流を高めることができる。

[0156]

なお、ここでは、一対の電極107は、酸化物半導体膜105及びゲート絶縁膜109の間に設けられているが、下地絶縁膜103及び酸化物半導体膜105の間に一対の電極107を設けてもよい。

[0157]

ゲート絶縁膜109は、実施の形態1に示すゲート絶縁膜17と同様に形成することができる。

[0158]

ゲート電極111は、実施の形態1に示すゲート電極15と同様に形成することができる

[ 0 1 5 9 ]

配線115は、一対の電極107に列挙する材料を適宜用いることができる。

[ 0 1 6 0 ]

次に、図5に示すトランジスタの作製方法について、図6を用いて説明する。

[0161]

図 6 ( A )に示すように、基板 1 0 1 上に下地絶縁膜 1 0 3 を形成する。次に、下地絶縁膜 1 0 3 上に酸化物半導体膜 1 0 5 を形成する。

[0162]

下地絶縁膜103は、スパッタリング法、CVD法等により形成する。

[0163]

下地絶縁膜103として、加熱により酸素の一部が脱離する酸化絶縁膜をスパッタリング法により形成する場合は、成膜ガス中の酸素量が高いことが好ましく、酸素、または酸素及び希ガスの混合ガス等を用いることができる。代表的には、成膜ガス中の酸素濃度を6%以上100%以下にすることが好ましい。

[0164]

また、下地絶縁膜103としてCVD法で酸化絶縁膜を形成する場合、原料ガス由来の水素または水が酸化絶縁膜中に混入される場合がある。このため、CVD法で酸化絶縁膜を形成した後、脱水素化または脱水化として、加熱処理を行うことが好ましい。

[0165]

さらに、CVD法で形成した酸化絶縁膜に、酸素を導入することで、加熱により脱離する酸素量を増加させることができる。酸化絶縁膜に酸素を導入する方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理等がある。

[0166]

ここで、酸化物半導体膜105は、実施の形態1に示す酸化物半導体膜19と同様の形成方法を適宜用いることができる。

[0167]

また、 C A A C - O S 膜に含まれる結晶部の配向を高めるためには、酸化物半導体膜の下地絶縁膜である、下地絶縁膜 1 0 3 の表面の平坦性を高めることが好ましい。代表的には、下地絶縁膜 1 0 3 の平均面粗さ(R a)を、 1 n m 以下、0 . 3 n m 以下、または 0 . 1 n m 以下とすることが好ましい。なお、本明細書等において、平均面粗さ(R a)とは

10

20

30

40

20

30

40

50

、JISB0601:2001(ISO4287:1997)で定義されている算術平均粗さを、曲面に対して適用できるよう三次元に拡張したものであり、基準面から指定面までの偏差の絶対値を平均した値で表現される。また、平坦化処理としては、化学的機械的研磨(Chemical Mechanical Polishing:CMP)処理、ドライエッチング処理、真空のチャンバーに不活性ガス、例えばアルゴンガスを導入し、被処理面を陰極とする電界をかけて、表面の微細な凹凸を平坦化するプラズマ処理(いわゆる逆スパッタ)等の一または複数を適用することができる。

[0168]

次に、加熱処理を行うことが好ましい。当該加熱処理により、下地絶縁膜103に含まれる酸素の一部を、下地絶縁膜103及び酸化物半導体膜105の界面近傍に拡散させることができる。この結果、下地絶縁膜103及び酸化物半導体膜105の界面近傍における界面準位を低減することができる。

[0169]

加熱処理の温度は、代表的には、150 以上基板歪み点未満、好ましくは250 以上450 以下、更に好ましくは300 以上450 以下とする。

[0170]

加熱処理は、ヘリウム、ネオン、アルゴン、キセノン、クリプトン等の希ガス、または窒素を含む不活性ガス雰囲気で行う。または、不活性ガス雰囲気で加熱した後、酸素雰囲気で加熱してもよい。なお、上記不活性雰囲気及び酸素雰囲気に水素、水などが含まれないことが好ましい。処理時間は3分~24時間とする。

[0171]

なお、後に酸化物半導体膜105となる酸化物半導体膜を下地絶縁膜103上に形成し、上記加熱処理を行った後、該酸化物半導体膜の一部をエッチングして、酸化物半導体膜105を形成してもよい。当該工程により、下地絶縁膜103に含まれる酸素において、より多くの酸素を下地絶縁膜103及び酸化物半導体膜105の界面近傍に拡散させることができる。

[0172]

次に、図6(B)に示すように、一対の電極107を形成する。一対の電極107は実施の形態1に示す一対の電極21と同様の形成方法を適宜用いることができる。または、印刷法またはインクジェット法により一対の電極107を形成することができる。

[0173]

次に、図 6 ( C )に示すように、ゲート絶縁膜 1 0 9 を形成した後、ゲート絶縁膜 1 0 9 上にゲート電極 1 1 1 を形成する。

[0174]

ゲート絶縁膜109は、実施の形態1に示すゲート絶縁膜17と同様の形成方法を適宜用いることができる。

[0175]

また、 C A A C - O S 膜は、被形成面または表面に沿って酸素が移動しやすい。このため、素子分離した酸化物半導体膜 1 0 5 の側面から酸素の脱離が生じやすく、酸素欠損が形成されやすい。しかしながら、酸化物半導体膜 1 0 5 上に加熱により酸素の一部が脱離する酸化絶縁膜と、当該酸化絶縁膜上に金属酸化膜とをゲート絶縁膜 1 0 9 として設けることにより、酸化物半導体膜 1 0 5 の側面からの酸素脱離を抑制することが可能である。この結果、酸化物半導体膜 1 0 5 の側面の導電性の上昇を抑制することを抑制することができる。

[0176]

ゲート電極111は、実施の形態1に示すゲート電極15の形成方法を適宜用いることができる。

[0177]

ここで、露光装置の解像限界以下の幅にまで微細化されたゲート電極の形成方法の一例について説明する。ゲート電極111の形成に用いるマスクに対してスリミング処理を行い

、より微細な構造のマスクとすることが好ましい。スリミング処理としては、例えば、酸素ラジカルなどを用いるアッシング処理を適用することができる。ただし、スリミング処理を適用することができる。ただし、スリミング処理であれば、アッシング処理以外の方法を用いてもよい。また、スリミング処理によって形成されるマスクによって、トランジスタのチャネル長が決定されることになるため、制御性の良好な処理を適用することが好ましい。スリミング処理の結果、フォトリソグラフィ法などによって形成されたマスクを、露光装置の解像限界以下、好ましくは、1/2以下、より好ましくは1/3以下の幅にまで微細化することが可能である。例えば、形成されたマスクの幅は、20nm以上2000nm以下、好ましくは50nm以上350nm以下を達成することができる。また、スリミングしたマスクを後退させながら、導電膜をエッチングすることで、露光装置の解像限界以下の幅にまで微細化されたゲート電極11を形成することができる。

[0178]

次に、図 6 ( D )に示すように、ゲート絶縁膜 1 0 9 及びゲート電極 1 1 1 上に保護膜 1 1 3 を形成した後、一対の電極 1 0 7 に接続する配線 1 1 5 を形成する。

[0179]

保護膜113は、実施の形態1に示す保護膜23と同様に、プラズマCVD装置の真空排気された処理室内に載置された基板101を180 以上260 以下、好ましくは180 以上230 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられる電極に0.17W/cm²以上0.5W/cm²以下、好ましくは0.25W/cm²以上0.40W/cm²以下、さらに好ましくは0.26W/cm²以上0.35W/cm²以下の高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成する。

[0180]

保護膜113の成膜条件として、上記圧力において上記パワー密度の高周波電力を供給することで、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜を形成することができる。

[0181]

次に、実施の形態1と同様に、加熱処理を行うことで、保護膜113に含まれる酸素を酸化物半導体膜105に拡散させ、酸化物半導体膜105に含まれる酸素欠損を補填することで、酸化物半導体膜105に含まれる酸素欠損量を低減することができる。また、保護膜113形成後の加熱処理により、保護膜113の電子スピン共鳴測定によるg=2.001に現れる信号のスピン密度が1.5×10<sup>18</sup>spins/cm<sup>3</sup>未満、好ましくは1.0×10<sup>18</sup>spins/cm<sup>3</sup>以下となる。該加熱処理の温度は、代表的には、150 以上基板歪み点未満、好ましくは250 以上450 以下、更に好ましくは300 以上450 以下とする。

[0182]

配線115は、スパッタリング法、CVD法、蒸着法等で導電膜を形成した後、該導電膜上にマスクを形成して導電膜をエッチングして形成する。導電膜上に形成するマスクは、印刷法、インクジェット法、フォトリソグラフィ法を適宜用いることができる。この後マスクを除去する。また、配線115をデュアルダマシン法で形成してもよい。

[0183]

以上の工程により、しきい値電圧のマイナスシフトを抑制した、優れた電気特性を有するトランジスタを作製することができる。また、経時変化や光ゲートBTストレス試験による電気特性の変動の少ない、信頼性の高いトランジスタを作製することができる。

[0184]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及び方法などと適宜組み合わせて用いることができる。

[0185]

10

20

30

40

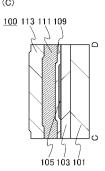

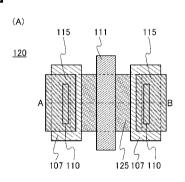

#### (実施の形態3)

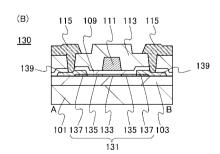

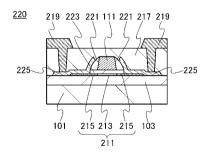

本実施の形態では、実施の形態 1 及び実施の形態 2 と異なる構造のトランジスタについて、図 7 を用いて説明する。本実施の形態に示すトランジスタ 1 2 0 は、実施の形態 2 に示すトランジスタ 1 0 0 と比較して、酸化物半導体膜にドーパントが添加されている点が異なる。

# [0186]

図7(A)及び図7(B)に、トランジスタ120の上面図及び断面図を示す。図7(A)はトランジスタ120の上面図であり、図7(B)は、図7(A)の一点鎖線A-B間の断面図である。なお、図7(A)では、明瞭化のため、トランジスタ120の構成要素の一部(例えば、基板101、下地絶縁膜103、ゲート絶縁膜109)、保護膜113などを省略している。

#### [0187]

図7(B)に示すトランジスタ120は、下地絶縁膜103上に形成される酸化物半導体膜121と、酸化物半導体膜121に接する一対の電極107と、下地絶縁膜103、酸化物半導体膜121、及び一対の電極107に接するゲート絶縁膜109と、ゲート絶縁膜109を介して酸化物半導体膜121と重なるゲート電極111とを有する。また、ゲート絶縁膜109及びゲート電極111を覆う保護膜113を有する。また、ゲート絶縁膜109及び保護膜113の開口部110(図7(A)参照。)において、一対の電極107と接する配線115とを有してもよい。

### [0188]

本実施の形態に示すトランジスタ120は、酸化物半導体膜121において、ゲート電極111とゲート絶縁膜109を介して重なる第1の領域123と、ドーパントが添加された第2の領域125と、一対の電極107と接する第3の領域127とを有する。なお、第1の領域123及び第3の領域127には、ドーパントが添加されていない。第1の領域123を挟むように対となる第2の領域125が設けられる。また、第1の領域123及び第2の領域125を間に挟むように対となる第3の領域127が設けられる。

#### [0189]

第1の領域123は、トランジスタ120においてチャネル領域として機能する。第3の領域127において一対の電極107と接する領域は、一対の電極107によって酸素の一部が一対の電極107に拡散し、酸素欠損ができ、n型化する。このため、第3の領域127の一部はソース領域及びドレイン領域として機能する。第2の領域は、ドーパントが添加され、導電率が高いため、低抵抗領域として機能し、チャネル領域と、ソース領域及びドレイン領域との間の抵抗を低減することができる。このため、実施の形態1に示すトランジスタ100と比較して、トランジスタ120のオン電流及び電界効果移動度を高めることができる。

# [0190]

第2の領域125に添加されるドーパントとしては、ホウ素、窒素、リン、及びヒ素の少なくとも一以上がある。または、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの少なくとも一以上がある。なお、ドーパントとして、ホウ素、窒素、リン、及びヒ素の一以上と、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノンの一以上とが適宜組み合わされて含まれていてもよい。

#### [0191]

また、第 2 の領域 1 2 5 に含まれるドーパントの濃度は、  $5 \times 10^{-18}$  a t o m s / c m  $^3$  以上  $1 \times 10^{-22}$  a t o m s / c m  $^3$  以下、好ましくは  $5 \times 10^{-18}$  a t o m s / c m  $^3$  以上  $5 \times 10^{-19}$  a t o m s / c m  $^3$  未満とする。

# [0192]

第2の領域125はドーパントを含むため、キャリア密度または欠陥を増加させることができる。このため、ドーパントを含まない第1の領域123及び第3の領域127と比較して導電性を高めることができる。なお、ドーパント濃度を増加させすぎると、ドーパントがキャリアの移動を阻害することになり、第2の領域125の導電性を低下させること

10

20

30

40

になる。

[0193]

第 2 の領域 1 2 5 は、導電率が 0 . 1 S / c m 以上 1 0 0 0 S / c m 以下、好ましくは 1 0 S / c m 以上 1 0 0 0 S / c m 以下とすることが好ましい。

[0194]

次に、本実施の形態に示すトランジスタ120の作製方法について、図6及び図7を用いて説明する。

[0195]

実施の形態 1 と同様に、図 6 ( A ) 乃至図 6 ( C ) の工程を経て、基板 1 0 1 上に下地絶縁膜 1 0 3 を形成し、下地絶縁膜 1 0 3 上に酸化物半導体膜 1 2 1 を形成し、酸化物半導体膜 1 2 1 上に一対の電極 1 0 7 を形成する。次に、酸化物半導体膜 1 2 1 及び一対の電極 1 0 7 上にゲート絶縁膜 1 0 9 を形成し、ゲート絶縁膜 1 0 9 を介して、酸化物半導体膜 1 2 1 の一部と重なるように、ゲート電極 1 1 1 を形成する。

[0196]

次に、一対の電極107及びゲート電極111をマスクとして、酸化物半導体膜121に ドーパントを添加する。酸化物半導体膜121にドーパントを添加する方法として、イオ ンドーピング法またはイオンインプランテーション法を用いることができる。

[0197]

また、上記酸化物半導体膜121へのドーパントの添加は、酸化物半導体膜121を覆って、ゲート絶縁膜109が形成されている状態を示したが、酸化物半導体膜121が露出している状態でドーパントの添加を行ってもよい。

[0198]

さらに、上記ドーパントの添加はイオンドーピング法またはイオンインプランテーション法などによる注入以外の方法でも行うことができる。例えば、添加する元素を含むガス雰囲気にてプラズマを発生させて、酸化物半導体膜121に対してプラズマ処理を行うことによって、ドーパントを添加することができる。上記プラズマを発生させる装置としては、ドライエッチング装置、プラズマCVD装置などを用いることができる。

[0199]

なお、ドーパントの添加処理は、基板101を加熱しながら行ってもよい。

[0200]

ここでは、イオンインプランテーション法により、リンを酸化物半導体膜 1 2 1 に添加する。

[0201]

この後、加熱処理を行う。当該加熱処理の温度は、代表的には、150 以上450 以下、好ましくは250 以上325 以下とする。または、250 から325 まで徐々に温度上昇させながら加熱してもよい。

[0202]

当該加熱処理により、第2の領域125の導電率を高めることができる。なお、当該加熱 処理において、第1の領域123、第2の領域125,及び第3の領域127は、多結晶 構造、非晶質構造、またはCAAC-OSとなる。

[ 0 2 0 3 ]

こののち、実施の形態1と同様に、保護膜113を形成し、加熱処理して保護膜113に含まれる酸素を酸化物半導体膜121に拡散させ、酸化物半導体膜121の酸素欠損を低減した後、配線115を形成して、図7に示すトランジスタ120を形成することができる。

[0204]

本実施の形態に示すトランジスタ120は、酸化物半導体膜121において、チャネル領域となる第1の領域123と、ソース領域及びドレイン領域として機能する第3の領域127の間に、低抵抗領域である第2の領域125を有する。このため、実施の形態2に示すトランジスタ100と比較して、チャネル領域と、ソース領域及びドレイン領域との間

10

20

30

40

20

30

40

50

の抵抗を低減することが可能であり、オン電流を高めたトランジスタを作製することができる。また、トランジスタ120上に保護膜113を設けることで、しきい値電圧のマイナスシフトを抑制した、優れた電気特性を有するトランジスタを作製することができる。また、経時変化や光ゲートBTストレス試験による電気特性の変動の少ない、信頼性の高いトランジスタを作製することができる。

[0205]

なお、トランジスタ120においては、保護膜113に含まれる酸素は、下地絶縁膜10 3及びゲート絶縁膜109の一以上を介して、酸化物半導体膜121に移動する。

[0206]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及 び方法などと適宜組み合わせて用いることができる。

[0207]

(実施の形態4)

本実施の形態では、実施の形態 1 乃至実施の形態 3 と異なる構造のトランジスタについて、図 8 を用いて説明する。本実施の形態に示すトランジスタ 1 3 0 は、他の実施の形態に示すトランジスタと比較して、酸化物半導体膜の構造が異なり、チャネル領域と、ソース領域及びドレイン領域との間に、電界緩和領域を有する。

[0208]

図8(A)及び図8(B)に、トランジスタ130の上面図及び断面図を示す。図8(A)はトランジスタ130の上面図であり、図8(B)は、図8(A)の一点鎖線A-B間の断面図である。なお、図8(A)では、明瞭化のため、トランジスタ130の構成要素の一部(例えば、基板101、下地絶縁膜103、ゲート絶縁膜109)、保護膜113などを省略している。

[0209]

図8(B)に示すトランジスタ130は、基板101上に設けられる下地絶縁膜103と、下地絶縁膜103上に形成される酸化物半導体膜131と、酸化物半導体膜131に接する一対の電極139と、下地絶縁膜103、酸化物半導体膜131、及び一対の電極139に接するゲート絶縁膜109と、ゲート絶縁膜109を介して酸化物半導体膜131と重なるゲート電極111とを有する。また、ゲート絶縁膜109及びゲート電極111を覆う保護膜113を有する。また、ゲート絶縁膜109及び保護膜113の開口部110において、一対の電極139と接する配線115とを有してもよい。

[ 0 2 1 0 ]

本実施の形態に示すトランジスタ130は、酸化物半導体膜131において、ゲート電極111とゲート絶縁膜109を介して重なる第1の領域133と、ドーパントが添加された第2の領域135と、一対の電極139と接し、且つドーパントが添加された第3の領域137とを有する。なお、第1の領域133には、ドーパントが添加されていない。第1の領域133を挟むように対となる第2の領域135が設けられる。また、第1の領域133及び第2の領域135を間に挟むように対となる第3の領域137が設けられる。

[ 0 2 1 1 ]

第2の領域135及び第3の領域137に添加されるドーパントとしては、実施の形態3 に示す第2の領域125と同様のドーパントを適宜用いることができる。

[0212]

また、第2の領域135及び第3の領域137に含まれるドーパントの濃度及び導電率は、実施の形態3に示す第2の領域125と同様のドーパントの濃度とすることができる。なお、本実施の形態においては、第2の領域135より第3の領域137の方がドーパントの濃度及び導電率が高い。

[0213]

第1の領域133は、トランジスタ130においてチャネル領域として機能する。第2の領域135は、電界緩和領域として機能する。第3の領域137において一対の電極13 9と接する領域は、一対の電極139の材料によっては酸素の一部が一対の電極139に 拡散し、酸素欠損ができ、n型化する。また、第3の領域137にはドーパントが添加され、導電率が高いため、実施の形態2に示すトランジスタ120と比較して、第3の領域137及び一対の電極139のコンタクト抵抗をさらに低減することができる。このため、実施の形態2に示すトランジスタと比較して、トランジスタ130は、オン電流及び電界効果移動度を高めることができる。

# [0214]

なお、一対の電極139は、第3の領域137にドーパントを添加させるために、膜厚を薄くすることが好ましく、代表的には、10nm以上100nm以下、好ましくは20nm以上50nm以下とする。

# [0215]

次に、本実施の形態に示すトランジスタ130の作製方法について、図6及び図8を用いて説明する。

#### [0216]

実施の形態 2 と同様に、図 6 ( A )乃至図 6 ( C )の工程を経て、基板 1 0 1 上に下地絶縁膜 1 0 3 を形成し、下地絶縁膜 1 0 3 上に酸化物半導体膜 1 3 1 を形成し、酸化物半導体膜 1 3 1 上に一対の電極 1 3 9 (図 8 ( B )参照。)を形成する。次に、酸化物半導体膜 1 3 1 及び一対の電極 1 3 9 上にゲート絶縁膜 1 0 9 を形成し、ゲート絶縁膜 1 0 9 を 介して、酸化物半導体膜 1 3 1 の一部と重なるように、ゲート電極 1 1 1 を形成する。

### [0217]

次に、ゲート電極111をマスクとして、酸化物半導体膜131にドーパントを添加する。ドーパントの添加方法は、実施の形態2に示す方法を適宜用いることができる。なお、本実施の形態では、第2の領域135と共に、第3の領域137にもドーパントを添加する。さらに、第2の領域135より第3の領域137の方がドーパントの濃度が高い。このため、ドーパント濃度のプロファイルのピークが第3の領域137となるように、添加方法の条件を適宜用いる。このとき、第3の領域137は一対の電極139と重なるが、第2の領域135は、一対の電極139と重ならない。このため、第2の領域135では、ドーパント濃度のプロファイルのピークが下地絶縁膜103となるため、第2の領域135におけるドーパントの濃度は、第3の領域137より低くなる。

# [0218]

この後、加熱処理を行う。当該加熱処理の温度は、代表的には、150 以上450 以下、好ましくは250 以上325 以下とする。または、250 から325 まで徐々に温度上昇させながら加熱してもよい。

#### [ 0 2 1 9 ]

当該加熱処理により、第2の領域135及び第3の領域137の導電率を高めることができる。なお、当該加熱処理において、第1の領域133、第2の領域135、及び第3の領域137は、多結晶構造、非晶質構造、またはCAAC-OSとなる。

#### [ 0 2 2 0 ]

こののち、実施の形態 2 と同様に、保護膜 1 1 3 を形成し、加熱処理して保護膜 1 1 3 に含まれる酸素を酸化物半導体膜 1 3 1 に拡散させ、酸素欠損量を低減させた後、配線 1 1 5 を形成して、図 8 に示すトランジスタ 1 3 0 を形成することができる。

# [ 0 2 2 1 ]

本実施の形態に示すトランジスタ130は、酸化物半導体膜131において、チャネル領域となる第1の領域133と、ソース領域及びドレイン領域として機能する第3の領域137の間に、電界緩和領域として機能する第2の領域135を有する。このため、実施の形態2に示すトランジスタ100と比較して、トランジスタの劣化を抑制することができる。また、一対の電極139と接する第3の領域137にドーパントが含まれるため、一対の電極139及び第3の領域137の接触抵抗をさらに低減することが可能であり、オン電流を高めたトランジスタを作製することができる。また、トランジスタ130上に保護膜113を設けることで、しきい値電圧のマイナスシフトを抑制した、優れた電気特性を有するトランジスタを作製することができる。また、経時変化や光ゲートBTストレス

10

20

30

40

試験による電気特性の変動の少ない、信頼性の高いトランジスタを作製することができる

# [0222]

なお、トランジスタ130においては、保護膜113に含まれる酸素は、下地絶縁膜10 3及びゲート絶縁膜109の一以上を介して、酸化物半導体膜131に移動する。

#### [ 0 2 2 3 ]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及び方法などと適宜組み合わせて用いることができる。

## [0224]

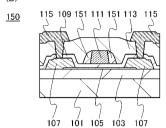

(実施の形態5)

本実施の形態では、実施の形態 2 乃至実施の形態 4 に適用可能なトランジスタの構造について、図 9 を用いて説明する。

#### [0225]

本実施の形態に示すトランジスタは、ゲート電極 1 1 1 の側面に接するサイドウォール絶縁膜を有することを特徴とする。ここでは、実施の形態 2 に示すトランジスタを用いて説明する。

### [0226]

図9(A)に示すトランジスタ140は、下地絶縁膜103上に形成される酸化物半導体膜105と、酸化物半導体膜105に接する一対の電極107と、下地絶縁膜103、酸化物半導体膜105、及び一対の電極107に接するゲート絶縁膜109と、ゲート絶縁膜109を介して酸化物半導体膜105と重なるゲート電極111とを有する。また、ゲート電極111の側面に接するサイドウォール絶縁膜141を有する。ゲート絶縁膜109、ゲート電極111、及びサイドウォール絶縁膜141を覆う保護膜113を有する。また、ゲート絶縁膜109及び保護膜113の開口部において、一対の電極107と接する配線115とを有してもよい。

### [0227]

サイドウォール絶縁膜141の端部は一対の電極107と重なり、一対の電極107及びゲート電極111の間を充填するように設けられている。一対の電極107及びゲート電極111の間の凹凸を緩和することができる。このため、保護膜113の被覆率を高めることが可能である。

### [0228]

図 9 ( B ) に示すトランジスタ 1 5 0 は、トランジスタ 1 4 0 と比較して、ゲート電極 1 1 1 の側面に接するサイドウォール絶縁膜 1 5 1 の形状が異なる。具体的には、サイドウォール絶縁膜 1 5 1 の端部は、一対の電極 1 0 7 と重ならず、ゲート電極 1 1 1 及び一対の電極 1 0 7 の間に位置する。

#### [0229]

図 9 ( C )に示すトランジスタ 1 6 0 は、図 9 ( B )に示すトランジスタ 1 5 0 と比較して、酸化物半導体膜 1 6 1 にドーパントが添加されている点が異なる。

# [0230]

酸化物半導体膜161において、ゲート電極111とゲート絶縁膜109を介して重なる第1の領域163と、ドーパントが添加され、且つサイドウォール絶縁膜151と重なる第2の領域165と、ドーパントが添加された第3の領域167と、一対の電極107と接する第4の領域169とを有する。なお、第1の領域163及び第4の領域169には、ドーパントが添加されていない。第1の領域163を挟むように対となる第2の領域165が設けられる。また、第1の領域163及び第2の領域165を間に挟むように対となる第3の領域167が設けられる。また、第1の領域163乃至第3の領域167を間に挟むように対となる第4の領域169が設けられる。

#### [0231]

第1の領域163は、トランジスタ160においてチャネル領域として機能する。

# [0232]

50

10

20

30

20

30

40

50

第2の領域165及び第3の領域167は、ドーパントが添加され、導電率が高いため、低抵抗領域として機能し、チャネル領域と、ソース領域及びドレイン領域との間の抵抗を低減することができる。また、第2の領域165は第3の領域167よりドーパントの濃度及び導電率が低いため、電界緩和領域として機能する。このため、トランジスタ160の劣化を低減することができる。

[ 0 2 3 3 ]

第2の領域165及び第3の領域167に添加されるドーパントとしては、実施の形態3 に示す第2の領域125と同様のドーパントを適宜用いることができる。

[0234]

また、第2の領域165及び第3の領域167に含まれるドーパントの濃度、及び導電率は、実施の形態3に示す第2の領域125と同様のドーパントの濃度とすることができる。なお、本実施の形態においては、第2の領域165より第3の領域167の方がドーパントの濃度及び導電率が高い。

[ 0 2 3 5 ]

第4の領域169において一対の電極107と接する領域は、一対の電極107によっては酸素の一部が一対の電極107に拡散し、酸素欠損ができ、n型化する。この結果、第4の領域169の一部はソース領域及びドレイン領域として機能する。

[0236]

本実施の形態に示すトランジスタ160は、酸化物半導体膜161において、第1の領域163を挟むように、低抵抗領域である第2の領域165及び第3の領域167を有する。このため、チャネル領域と、ソース領域及びドレイン領域との間の抵抗を低減することが可能であり、オン電流を高めたトランジスタを作製することができる。

[0237]

また、トランジスタ140、150、160上に保護膜113を設けることで、しきい値電圧のマイナスシフトを抑制した、優れた電気特性を有するトランジスタを作製することができる。また、経時変化や光ゲートBTストレス試験による電気特性の変動の少ない、信頼性の高いトランジスタを作製することができる。

[0238]

なお、トランジスタ140、150、160においては、保護膜113に含まれる酸素は、下地絶縁膜103、ゲート絶縁膜109の一以上を介して、酸化物半導体膜に移動する

[0239]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及 び方法などと適宜組み合わせて用いることができる。

[0240]

(実施の形態6)

本実施の形態では、実施の形態 2 乃至実施の形態 5 と異なる構造のトランジスタについて、図 1 0 を用いて説明する。本実施の形態に示すトランジスタは、実施の形態 2 乃至実施の形態 5 と比較して、一対の電極及びゲート電極がゲート絶縁膜を介して重なっている点が異なる。

[0241]

図10に示すトランジスタ170は、下地絶縁膜103上に形成される酸化物半導体膜105と、酸化物半導体膜105に接する一対の電極107と、下地絶縁膜103、酸化物半導体膜105、及び一対の電極107に接するゲート絶縁膜109と、ゲート絶縁膜109を介して酸化物半導体膜105と重なるゲート電極171とを有する。また、ゲート絶縁膜109及びゲート電極171を覆う保護膜113を有する。また、ゲート絶縁膜109及び保護膜113の開口部において、一対の電極107と接する配線115とを有してもよい。

[0242]

本実施の形態に示すトランジスタ170は、一対の電極107及びゲート電極171がゲ

20

30

40

50

ート絶縁膜109を介して重なっている。このため、酸化物半導体膜105において、ゲート絶縁膜109を介してゲート電極171と対向する領域がチャネル領域として機能し、一対の電極107と接する領域がソース領域及びドレイン領域として機能する。即ち、チャネル領域と、ソース領域及びドレイン領域とが接している。チャネル領域と、ソース領域及びドレイン領域との間に抵抗となる領域がないため、実施の形態2乃至実施の形態5に示すトランジスタと比較して、オン電流及び電界効果移動度が高い。

[ 0 2 4 3 ]

また、トランジスタ170上に保護膜113を設けることで、しきい値電圧のマイナスシフトを抑制した、優れた電気特性を有するトランジスタを作製することができる。また、経時変化や光ゲートBTストレス試験による電気特性の変動の少ない、信頼性の高いトランジスタを作製することができる。

[0244]

なお、トランジスタ 1 7 0 においては、保護膜 1 1 3 に含まれる酸素は、下地絶縁膜 1 0 3、ゲート絶縁膜 1 0 9 の一以上を介して、酸化物半導体膜 1 0 5 に移動する。

[ 0 2 4 5 ]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及び方法などと適宜組み合わせて用いることができる。

[0246]

(実施の形態7)

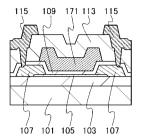

本実施の形態では、実施の形態 1 乃至実施の形態 6 と異なる構造のトランジスタについて、図 1 1 を用いて説明する。

[0247]

図11(A)に示すトランジスタ210は、下地絶縁膜103上に形成される酸化物半導体膜211と、下地絶縁膜103及び酸化物半導体膜211に接するゲート絶縁膜109と、ゲート絶縁膜109を介して酸化物半導体膜211と重なるゲート電極111とを有する。また、ゲート絶縁膜109及びゲート電極111を覆う保護膜217と、ゲート絶縁膜109及び保護膜217の開口部において、酸化物半導体膜211と接する配線219を有する。

[0248]

本実施の形態に示すトランジスタ210は、酸化物半導体膜211は、ゲート電極111 とゲート絶縁膜109を介して重なる第1の領域213と、ドーパントが添加された第2の領域215とを有する。なお、第1の領域213には、ドーパントが添加されていない。また、第1の領域213を挟むように対となる第2の領域215が設けられる。

[0249]

第 1 の領域 2 1 3 は、トランジスタ 2 1 0 においてチャネル領域として機能する。第 2 の領域 2 1 5 はソース領域及びドレイン領域として機能する。

[0250]

第2の領域215に添加されるドーパントとしては、実施の形態3に示す第2の領域12 5と同様のドーパントを適宜用いることができる。

[0251]

また、第2の領域215に含まれるドーパントの濃度及び導電率は、実施の形態3に示す 第2の領域125と同様のドーパントの濃度とすることができる。

[0252]

図11(B)に示すトランジスタ220は、下地絶縁膜103上に設けられる酸化物半導体膜211と、酸化物半導体膜211に接する、ソース電極及びドレイン電極として機能する一対の電極225と、酸化物半導体膜211の少なくとも一部と接するゲート絶縁膜223と、ゲート絶縁膜223上であって、且つ酸化物半導体膜211と重畳するゲート電極111とを有する。

[ 0 2 5 3 ]

また、ゲート電極111の側面に接するサイドウォール絶縁膜221を有する。また、下

地絶縁膜103、ゲート電極111、サイドウォール絶縁膜221、及び一対の電極22 5上に保護膜217を有する。また、保護膜217の開口部において、酸化物半導体膜2 11と接する配線219を有する。

#### [ 0 2 5 4 ]

図 1 1 ( B ) に示すトランジスタにおいて、酸化物半導体膜 2 1 1 は、ゲート電極 1 1 1 とゲート絶縁膜 2 2 3 を介して重なる第 1 の領域 2 1 3 と、ドーパントが添加された第 2 の領域 2 1 5 とを有する。なお、第 1 の領域 2 1 3 には、ドーパントが添加されていない。第 1 の領域 2 1 5 が設けられる。

## [0255]

トランジスタの一対の電極225の端部が、サイドウォール絶縁膜221上に位置し、更に酸化物半導体膜211において、一対の電極225が、ドーパントを含む一対の第2の領域215の露出部を全て覆っている。このため、チャネル長方向におけるソース・ドレイン間の距離(より正確には、一対の電極225と接する酸化物半導体膜211の間の距離)を、サイドウォール絶縁膜221の幅で制御することができる。つまりマスクを用いてパターンを形成するのが困難な微細なデバイスにおいて、酸化物半導体膜211と接する一対の電極225のチャネル側の端部を、マスクを用いずに形成させることができる。また、マスクを使用しないため、複数のトランジスタにおける加工ばらつきを低減することができる。

#### [0256]

本実施の形態に示すトランジスタ210、220上に設けられる保護膜217は、実施の形態1に示す保護膜23と同様に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜である。さらに好ましくは、保護膜217は、酸化物半導体膜211に含まれる酸素欠損量以上の酸素を含む。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜は、加熱により酸素の一部が脱離する酸化絶縁膜である。このため、加熱により酸素の一部が脱離する酸化絶縁膜である。このため、加熱により酸素の一部が脱離する酸化絶縁膜として設けることで、加熱処理により酸化物半導体膜に酸素を拡散させ、酸化物半導体膜211に含まれる酸素欠損を補填することが可能である。この結果、酸化物半導体膜211に含まれる酸素欠損量が低減され、しきい値電圧のマイナスシフトを抑制したトランジスタとなる。また、経時変化や光ゲートBTストレス試験によって、しきい値電圧の変動が少なく、優れた電気特性を有するトランジスタとなる。

### [0257]

また、保護膜 2 1 7 において、電子スピン共鳴測定による g = 2 . 0 0 1 に現れる信号のスピン密度が 1 .  $5 \times 10^{-1.8}$  s p i n s / c m  $^3$  未満、好ましくは 1 .  $0 \times 10^{-1.8}$  s p i n s / c m  $^3$  以下であると、優れた電気特性を有するトランジスタとなるため好ましい。

# [0258]

なお、トランジスタ220においては、保護膜217に含まれる酸素は、下地絶縁膜10 3、ゲート絶縁膜223、及びサイドウォール絶縁膜221の一以上を介して、酸化物半 導体膜211に移動する。

### [0259]

なお、本実施の形態に示す構成及び方法などは、他の実施の形態及び実施例に示す構成及 び方法などと適宜組み合わせて用いることができる。

# [0260]

# (実施の形態8)

本実施の形態では、実施の形態1乃至実施の形態7と異なる構造のトランジスタについて、図12を用いて説明する。本実施の形態に示すトランジスタは、酸化物半導体膜を介して対向する複数のゲート電極を有することを特徴とする。なお、本実施の形態では、実施の形態6に示すトランジスタを用いて説明するが、適宜他の実施の形態と組み合わせることができる。

# [0261]

10

20

30

図12に示すトランジスタ230は、基板101上に設けられるゲート電極231と、ゲート電極231を覆う絶縁膜233を有する。また、絶縁膜233上に形成される酸化物半導体膜105と、酸化物半導体膜105に接する一対の電極107と、絶縁膜233、酸化物半導体膜105、及び一対の電極107に接するゲート絶縁膜109と、ゲート絶縁膜109を介して酸化物半導体膜105と重なるゲート電極171とを有する。また、ゲート絶縁膜109及びゲート電極171を覆う保護膜113を有する。また、ゲート絶縁膜109及び保護膜113の開口部において、一対の電極107と接する配線115とを有してもよい。

## [0262]

ゲート電極 2 3 1 は、実施の形態 1 に示すゲート電極 1 5 と同様に形成することができる。なお、ゲート電極 2 3 1 は、後に形成される絶縁膜 2 3 3 の被覆性を高めるために、側面がテーパ形状であることが好ましく、基板 1 0 1 とゲート電極 2 3 1 の側面のなす角度は、 2 0 度以上 7 0 度以下、好ましくは 3 0 度以上 6 0 度以下とする。

# [0263]

絶縁膜233は、実施の形態2に示す下地絶縁膜103と同様に形成することができる。なお、後に、絶縁膜233上に酸化物半導体膜105を形成するため、絶縁膜233の表面は平坦であることが好ましい。このため、後に絶縁膜233となる絶縁膜を基板101及びゲート電極231上に形成した後、当該絶縁膜を平坦化処理して、表面の凹凸が少ない絶縁膜233を形成する。

# [0264]

本実施の形態に示すトランジスタ230は、酸化物半導体膜105を介して対向するゲート電極231及びゲート電極171を有する。ゲート電極231とゲート電極171に異なる電位を印加することで、トランジスタ230のしきい値電圧を制御し、好ましくは、しきい値電圧をプラスシフトさせることができる。

#### [ 0 2 6 5 ]

本実施の形態に示すトランジスタ230上に保護膜113が設けられる。保護膜113は、実施の形態1に示す保護膜23と同様に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜である。さらに好ましくは、保護膜113は、酸化物半導体膜105に含まれる酸素欠損量以上の酸素を含む。この結果、酸化物半導体膜105に含まれる酸素欠損量が低減され、しきい値電圧のマイナスシフトを抑制したトランジスタとなる。また、経時変化や光ゲートBTストレス試験によって、しきい値電圧の変動が少なく、優れた電気特性を有するトランジスタとなる。

#### [0266]

# (実施の形態9)

本実施の形態では、実施の形態 1 乃至実施の形態 8 に示すトランジスタにおいて、酸化物半導体膜中に含まれる水素濃度を低減したトランジスタの作製方法について説明する。ここでは、代表的に実施の形態 1 及び実施の形態 2 を用いて説明するが、適宜他の実施の形態と組み合わせることができる。なお、本実施の形態に示す工程の一以上と、実施の形態 1 及び実施の形態 2 に示すトランジスタの作製工程とが組み合わさればよく、全て組み合わせる必要はない。

# [ 0 2 6 7 ]

実施の形態 1 に示す酸化物半導体膜 1 9 及び実施の形態 2 に示す酸化物半導体膜 1 0 5 において、水素濃度を  $5 \times 10^{-19}$  a toms / c m  $^3$  未満、好ましくは  $5 \times 10^{-18}$  a toms / c m  $^3$  未満、より好ましくは  $1 \times 10^{-18}$  a toms / c m  $^3$  以下、より好ましくは  $5 \times 10^{-17}$  a toms / c m  $^3$  以下、さらに好ましくは  $1 \times 10^{-16}$  a toms / c m  $^3$  以下とすることが好ましい。

### [0268]

酸化物半導体膜19、105に含まれる水素は、金属原子と結合する酸素と反応して水となると共に、酸素が脱離した格子(あるいは酸素が脱離した部分)には欠損が形成されてしまう。また、水素が酸素と結合することで、キャリアである電子が生じてしまう。これ

10

20

30

40

20

30

40

50

らのため、酸化物半導体膜の成膜工程において、水素を含む不純物を極めて減らすことにより、酸化物半導体膜の水素濃度を低減することが可能である。このため、水素をできるだけ除去し、高純度化させた酸化物半導体膜をチャネル領域とすることにより、しきい値電圧のマイナスシフトを低減することができ、またトランジスタのソース及びドレインにおけるリーク電流を、代表的には、チャネル幅あたりのオフ電流を数 y Α / μ m ~ 数 z Α / μ m にまで低減することが可能であり、トランジスタの電気特性を向上させることができる。

### [0269]

酸化物半導体膜19中の水素濃度を低減する第1の方法として、酸化物半導体膜19を形成する前に、加熱処理またはプラズマ処理により、基板11、下地絶縁膜13、ゲート電極15、ゲート絶縁膜17それぞれに含まれる水素または水を脱離させる方法がある。この結果、後の加熱処理において、基板11乃至ゲート絶縁膜17に付着または含有する水素若しくは水が、酸化物半導体膜19中に拡散することを防ぐことができる。なお、加熱処理は、不活性雰囲気、減圧雰囲気または乾燥空気雰囲気にて、100 以上基板の歪み点未満の温度で行う。また、プラズマ処理は、希ガス、酸素、窒素または酸化窒素(亜酸化窒素、一酸化二窒素、二酸化窒素等)を用いる。なお、実施の形態2乃至実施の形態8においては、酸化物半導体膜105を形成する前に、加熱処理またはプラズマ処理により、基板101及び下地絶縁膜103それぞれに含まれる水素または水を脱離させる。

### [0270]

酸化物半導体膜19、105中の水素濃度を低減する第2の方法として、酸化物半導体膜をスパッタリング装置で成膜する前に、スパッタリング装置にダミー基板を搬入し、ダミー基板上に酸化物半導体膜を成膜して、ターゲット表面、または防着板に付着した水素、水等を取り除く方法がある。この結果、酸化物半導体膜中への水素または水等の混入を低減することが可能である。

#### [ 0 2 7 1 ]

酸化物半導体膜19、105中の水素濃度を低減する第3の方法として、酸化物半導体膜を形成する際に、例えば、スパッタリング法を用いる場合、基板温度を150 以上750 以下、好ましくは150 以上450 以下、さらに好ましくは200 以上350 以下として、酸化物半導体膜を成膜する方法がある。この方法により、酸化物半導体膜中への水素または水等の混入を低減することが可能である。

### [0272]

ここで、酸化物半導体膜 1 9、 1 0 5 中に含まれる水素濃度を低減することが可能なスパッタリング装置について、以下に詳細を説明する。

# [0273]

酸化物半導体膜を成膜する処理室は、リークレートを1×10<sup>・10</sup>Pa・m<sup>3</sup>/秒以下とすることが好ましく、それによりスパッタリング法により成膜する際、膜中への水素または水等の混入を低減することができる。

### [0274]

また、スパッタリング装置の処理室の排気として、ドライポンプ等の粗引きポンプと、スパッタイオンポンプ、ターボ分子ポンプ及びクライオポンプ等の高真空ポンプとを適宜組み合わせて行うとよい。ターボ分子ポンプは大きいサイズの分子の排気が優れる一方、水素及び水の排気能力が低い。さらに、水素の排気能力の高いスパッタイオンポンプまたは水の排気能力の高いクライオポンプを組み合わせることが有効となる。

# [0275]

処理室の内側に存在する吸着物は、内壁に吸着しているために処理室の圧力に影響しないが、処理室を排気した際のガス放出の原因となる。そのため、リークレートと排気速度に相関はないが、排気能力の高いポンプを用いて、処理室に存在する吸着物をできる限り脱離し、予め排気しておくことが重要である。なお、吸着物の脱離を促すために、処理室をベーキングしてもよい。ベーキングすることで吸着物の脱離速度を10倍程度大きくすることができる。ベーキングは100以上450以下で行えばよい。このとき、不活性

ガスを導入しながら吸着物の除去を行うと、排気するだけでは脱離しにくい水などの脱離 速度をさらに大きくすることができる。

#### [0276]

このように、酸化物半導体膜の成膜工程において、処理室の圧力、処理室のリークレートなどにおいて、不純物の混入を極力抑えることによって、酸化物半導体膜に含まれる水素または水等の混入を低減することができる。

#### [ 0 2 7 7 ]

酸化物半導体膜19、105中の水素濃度を低減する第4の方法として、原料ガスに水素を含む不純物が除去された高純度ガスを用いる方法がある。この結果、酸化物半導体膜中への水素または水等の混入を低減することが可能である。

[0278]

酸化物半導体膜19、105中の水素濃度を低減する第5の方法として、酸化物半導体膜を形成した後、加熱処理を行う方法がある。当該加熱処理により、酸化物半導体膜の脱水素化または脱水化をすることができる。

#### [0279]

加熱処理の温度は、代表的には、150 以上基板歪み点未満、好ましくは250 以上 450 以下、更に好ましくは300 以上450 以下とする。

# [ 0 2 8 0 ]

加熱処理は、ヘリウム、ネオン、アルゴン、キセノン、クリプトン等の希ガス、または窒素を含む不活性ガス雰囲気で行う。または、不活性ガス雰囲気で加熱した後、酸素雰囲気で加熱してもよい。なお、上記不活性雰囲気及び酸素雰囲気に水素、水などが含まれないことが好ましい。処理時間は3分~24時間とする。

[0281]

なお、図2(B)及び図6(A)に示すように、素子分離した酸化物半導体膜19、105を形成した後、上記脱水素化または脱水化のための加熱処理を行ってもよい。このような工程を経ることで、脱水素化または脱水化のための加熱処理において、ゲート絶縁膜17または下地絶縁膜103に含まれる水素または水等を効率よく放出させることができる

# [0282]

また、脱水化または脱水素化のための加熱処理は、複数回行ってもよく、他の加熱処理と兼ねてもよい。

[0283]

以上の酸化物半導体膜中の水素濃度を低減する第1の方法乃至第5の方法の一以上を実施の形態1乃至実施の形態8に示すトランジスタの作製方法に組み合わせることで、水素または水等をできるだけ除去し、高純度化させた酸化物半導体膜をチャネル領域に有するトランジスタを作製することができる。この結果、しきい値電圧のマイナスシフトを低減することができ、またトランジスタのソース及びドレインにおけるリーク電流を、代表的には、チャネル幅あたりのオフ電流を数yA/μm~数zA/μmにまで低減することが可能であり、トランジスタの電気特性を向上させることができる。以上のことから、本実施の形態により、しきい値のマイナスシフトが低減され、リーク電流が低く、電気特性を有するトランジスタを作製することができる。

[0284]

(実施の形態10)

本実施の形態では、下部に第1の半導体材料を用いたトランジスタを有し、上部に第2の 半導体材料を用いたトランジスタを有する半導体装置であって、第1の半導体材料を用い たトランジスタに半導体基板を用いた構造を、図13を用いて説明する。

#### [ 0 2 8 5 ]

図13は、下部に第1の半導体材料を用いたトランジスタを有し、上部に第2の半導体材料を用いたトランジスタを有する半導体装置の断面構成を示す一例である。ここで、第1の半導体材料と第2の半導体材料とは異なる材料を用いる。例えば、第1の半導体材料を

10

20

30

40

20

30

40

50

酸化物半導体以外の半導体材料とし、第2の半導体材料を酸化物半導体とすることができる。酸化物半導体以外の材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体または多結晶半導体を用いることが好ましい。単結晶半導体を用いたトランジスタは、チャネル幅あたりのオフ電流が数 y A /  $\mu$  m ~ 数 z A /  $\mu$  m 程度と十分低い特性を利用した回路に用いることができる。これらのことから、図13に示す半導体装置を用いて、例えば低消費電力の論理回路を構成することもできる。なお、第1の半導体材料として、有機半導体材料などを用いてもよい。

# [0286]

トランジスタ704a、トランジスタ704b及びトランジスタ704cはそれぞれ、nチャネル型トランジスタ(NMOSFET)またはpチャネル型トランジスタ(PMOSFET)も用いることができる。ここでは、トランジスタ704a及びトランジスタ704bとしてpチャネル型のトランジスタを示し、トランジスタ704cとしてnチャネル型のトランジスタを示す。図13に示す例においては、トランジスタ704a及びトランジスタ704bは、STI(Sha11ow Trench Iso1ation)702によって他の素子と絶縁分離されている。一方、トランジスタ704cは、STI702によってトランジスタ704a及び704bと絶縁分離されている。STI702を用いることにより、LOCOSによる素子分離法で発生した素子分離部のバーズビークを抑制することができ、素子分離部の縮小等が可能となる。一方で、トランジスタの構造の微細化が要求されない半導体装置においてはSTI702の形成は必ずしも必要ではなく、LOCOS等の素子分離手段を用いることもできる。

### [0287]

図13におけるトランジスタ704a、トランジスタ704b及びトランジスタ704cは、それぞれ基板701中に設けられたチャネル領域と、チャネル領域を挟むように設けられたが一ト絶縁膜706と、ゲート絶縁膜706上にチャネル領域と重畳するように設けられたゲート電極707、708とを有する。ゲート電極は加工精度を高めるための第1の材料からなるゲート電極707と、配線として低抵抗化を目的とした第2の材料からなるゲート電極707と、配線として低抵抗化を目的とした第2の材料からなるゲート電極708を積層した構造とすることができるが、この構造に限らず、適宜要求される仕様に応じて材料、積層数、形状等を調整することができる。なお、図において、明示的にはソース電極やドレイン電極を有しない場合があるが、便宜上このような状態を含めてトランジスタとよぶ場合がある。

# [0288]

また、基板701中に設けられた不純物領域705には、コンタクトプラグ714aが接続されている。ここでコンタクトプラグ714aは、トランジスタ704a等のソース電極やドレイン電極としても機能する。また、不純物領域705とチャネル領域の間には、不純物領域705と異なる不純物領域が設けられている。該不純物領域は、導入された不純物の濃度によって、LDD領域やエクステンション領域としてチャネル領域近傍の電界分布を制御する機能を果たす。ゲート電極707、708の側壁には絶縁膜709を介してサイドウォール絶縁膜710を有する。絶縁膜709やサイドウォール絶縁膜710を用いることで、LDD領域やエクステンション領域を形成することができる。

# [0289]

また、トランジスタ704a、トランジスタ704b及びトランジスタ704cは、絶縁膜711により被覆されている。絶縁膜711には保護膜としての機能を持たせることができ、外部からチャネル領域への不純物の侵入を防止することができる。また、絶縁膜711をCVD法による窒化シリコン等の材料とすることで、チャネル領域に単結晶シリコンを用いた場合には加熱処理によって、単結晶シリコンの水素化を行うことができる。また、絶縁膜711に引張応力または圧縮応力を有する絶縁膜を用いることで、チャネル領域を構成する半導体材料に歪みを与えることができる。nチャネル型のトランジスタの場

20

30

40

50

合にはチャネル領域となるシリコン材料に引張応力を、 p チャネル型のトランジスタの場合にはチャネル領域となるシリコン材料に圧縮応力を付加することで、各トランジスタの移動度を向上させることができる。

[0290]

ここでは、図13におけるトランジスタ750は、実施の形態6に示すトランジスタ17 0と同様の構造を有する。さらに、トランジスタ750の下地絶縁膜は、絶縁膜725a 、絶縁膜725bの2層構造であり、下地絶縁膜を介して、トランジスタ750の酸化物 半導体膜と対向するゲート電極751を有する。絶縁膜725aは、水素、水、及び酸素 のブロッキング効果を有する絶縁膜で形成することが好ましく、酸化物半導体膜からの酸 素の外部への拡散と、外部から酸化物半導体膜への水素、水の侵入を防ぐことができる。 酸素、水素、水等のブロッキング効果を有する絶縁膜としては、代表的には酸化アルミニ ウム膜で形成する。絶縁膜725bは、実施の形態2に示す下地絶縁膜103を適宜用い ることができる。

[0291]

なお、トランジスタ750としてここでは実施の形態6に示すトランジスタ170を用いて説明したが、実施の形態1乃至実施の形態9で示したトランジスタを適宜用いることができる。

[0292]

第2の半導体材料を用いたトランジスタ750は、必要な回路構成に応じて下層のトランジスタ704a等の第1の半導体材料を用いたトランジスタと電気的に接続する。図13においては、一例としてトランジスタ750のソースまたはドレインがトランジスタ704aのソースまたはドレインと電気的に接続している構成を示している。

[0293]

第2の半導体材料を用いたトランジスタ750のソースまたはドレインの一方は、トランジスタ750のゲート絶縁膜726、絶縁膜727、絶縁膜728、絶縁膜729を貫通するコンタクトプラグ730bを介して、トランジスタ750よりも上方に形成された配線734aと接続する。ゲート絶縁膜726及び絶縁膜727は、実施の形態1乃至実施の形態9で示した構造、材料を適宜用いることができる。

[0294]

配線734aは、絶縁膜731中に埋め込まれている。配線734aは、例えば銅、アルミニウム等の低抵抗な導電性材料を用いることが好ましい。低抵抗な導電性材料を用いることが好ましい。低抵抗な導電性材料を用いることで、配線734aを伝播する信号のRC遅延を低減することができる。配線734aに銅を用いる場合には、銅のチャネル領域への拡散を防止するため、バリア膜733を形成する。バリア膜として、例えば窒化タンタル、窒化タンタルとタンタルとの積層、窒化チタン、窒化チタンとチタンとの積層等による膜を用いることができるが、配線材料の拡散防止機能、及び配線材料や下地膜等との密着性が確保される程度においてこれらの材料からなる膜に限られない。バリア膜733は配線734aとは別個の層として形成してもよく、バリア膜となる材料を配線材料中に含有させ、加熱処理によって絶縁膜731に設けられた開口の内壁に析出させて形成しても良い。

[0295]

絶縁膜731には、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、BPSG(Borophosphosilicate glass)、PSG(Phosphorussilicate Glass)、炭素を添加した酸化シリコン(SiOC)、フッ素を添加した酸化シリコン(SiOF)、Si(OC<sub>2</sub>H<sub>5</sub>) 4 を原料とした酸化シリコンであるTEOS(Tetraethyl orthosilicate)、HSQ(Hydrogen Silsesauioxane)、MSQ(Methyl Silsesauioxane)、MSQ(Methyl Silsesauioxane)、OSG(Organo Silicate Glass)、有機ポリマー系の材料等の絶縁体を用いることができる。特に半導体装置の微細化を進める場合には、配線間の寄生容量が顕著になり信号遅延が増大するため酸化シリコンの比誘電率(km4.0~4.5)では高く、kが3.0以下の材料を用いることが好ましい。また該

20

30

40

50

絶縁膜に配線を埋め込んだ後にCMP処理を行うため、絶縁膜には機械的強度が要求される。この機械的強度が確保できる限りにおいて、これらを多孔質(ポーラス)化させて低誘電率化することができる。絶縁膜731は、スパッタリング法、CVD法、スピンコート法(Spin On Glass:SOGともいう)を含む塗布法等により形成する。

[0296]

絶縁膜731上には、絶縁膜732を設けても良い。絶縁膜732は、配線材料を絶縁膜731中に埋め込んだ後、CMP等による平坦化処理を行う際のエッチングストッパとして機能する。

[0297]

配線734a上には、バリア膜735が設けられており、バリア膜735上に保護膜74 0が設けられている。バリア膜735は銅等の配線材料の拡散を防止することを目的とした膜である。バリア膜735は、配線734aの上面のみに限らず、絶縁膜731、73 2上に形成してもよい。バリア膜735は、窒化シリコンやSiC、SiBON等の絶縁 性材料で形成することができる。

[0298]

[0299]

配線723は、既述した配線734a、734bと同様にバリア膜722、724により被覆され、絶縁膜720中に埋め込まれて設けられている。図13に示すように、配線723は上部の配線部分と、下部のビアホール部分から構成される。下部のビアホール部分は下層の配線718と接続する。該構造の配線723はいわゆるデュアルダマシン法等により形成することができる。また、上下層の配線間の接続はデュアルダマシン法によらず、コンタクトプラグを用いて接続してもよい。絶縁膜720上には、CMP等による平坦化処理を行う際のエッチングストッパとして機能する絶縁膜721を設けてもよい。

[0300]

配線723が電気的に接続する配線718についても、既述したトランジスタ750の上層の配線層と同様の構成により形成することができる。シリコン等の第1の半導体材料をチャネル領域に用いたトランジスタ704aは、絶縁膜711、絶縁膜712、絶縁膜713を貫通するコンタクトプラグ714aを介して配線718と接続する。シリコン等の第1の半導体材料をチャネル領域に用いたトランジスタ704cのゲート電極は、絶縁膜711、絶縁膜712、絶縁膜713を貫通するコンタクトプラグ714bを介して配線718と接続する。配線718は、既述した配線734a、734bと同様にバリア膜717、719により被覆され、絶縁膜715中に埋め込まれて設けられている。絶縁膜715上には、CMP等による平坦化処理を行う際のエッチングストッパとして機能する絶縁膜716を設けてもよい。

[0301]

以上のように、半導体装置の下部に設けられた第1の半導体材料を用いたトランジスタ7 04aは、複数のコンタクトプラグ及び複数の配線を介して、上部に設けられた第2の半 導体材料を用いたトランジスタ750と電気的に接続する。半導体装置を以上のような構 成とすることで、高速動作性能を有する第1の半導体材料を用いたトランジスタと、オフ電流が極めて小さい第2の半導体材料を用いたトランジスタとを組み合わせ、低消費電力化が可能な高速動作の論理回路を有する半導体装置を作製することができる。

#### [0302]

このような半導体装置は、既述の構成に限らず、発明の趣旨を逸脱しない範囲において、任意に変更が可能である。例えば、説明においては第1の半導体材料を用いたトランジスタの間の配線層は2層として説明したが、これを1層あるいは3層以上とすることもでき、また配線を用いることなく、コンタクトプラグのみによって両トランジスタを直接接続することもできる。この場合、例えばシリコン貫通電極(Through Silicon Via:TSV)技術を用いることもできる。また、配線は銅等の材料を絶縁膜中に埋め込むことで形成する場合について説明したが、例えばバリア膜、配線材料層、及びバリア膜の三層構造としてフォトリソグラフィエ程により配線パターンに加工したものを用いてもよい。

#### [0303]

特に、銅配線を第1の半導体材料を用いたトランジスタ704a、704bと第2の半導体材料を用いたトランジスタ750との間の階層に形成する場合には、第2の半導体材料を用いたトランジスタ750の製造工程において付加する熱処理の影響を十分考慮する必要がある。換言すれば、第2の半導体材料を用いたトランジスタ750の製造工程において付加する熱処理の温度を配線材料の性質に適合するように留意する必要がある。例えば、トランジスタ750の構成部材に対して高温で熱処理を行った場合、銅配線では熱応力が発生し、これに起因したストレスマイグレーションなどの不都合が生じるためである。

#### [0304]

### (実施の形態11)

先 の 実 施 の 形 態 で 示 し た 半 導 体 装 置 の 一 例 と し て は 、 中 央 演 算 処 理 装 置 、 マ イ ク ロ プ ロ セ ッ サ 、 マ イ ク ロ コ ン ピ ュ ー タ 、 記 憶 装 置 、 イ メ ー ジ セ ン サ 、 電 気 光 学 装 置 、 発 光 表 示 装 置 等がある。また、該半導体装置をさまざまな電子機器に適用することができる。電子機器 としては、例えば、表示装置、照明装置、パーソナルコンピュータ、ワードプロセッサ、 画像再生装置、ポータブルCDプレーヤ、ラジオ、テープレコーダ、ヘッドホンステレオ 、ステレオ、時計、コードレス電話子機、トランシーバ、携帯無線機、携帯電話、スマー トフォン、電子書籍、自動車電話、携帯型ゲーム機、電卓、携帯情報端末、電子手帳、電 子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、高周波 加 熱 装 置 、 電 気 炊 飯 器 、 電 気 洗 濯 機 、 電 気 掃 除 機 、 温 水 器 、 扇 風 機 、 毛 髪 乾 燥 機 、 エ ア コ ン デ ィ シ ョ ナ ー 、 加 湿 器 、 除 湿 器 、 空 調 設 備 、 食 器 洗 浄 器 、 食 器 乾 燥 器 、 衣 類 乾 燥 器 、 布 団 乾 燥 器 、 電 気 冷 蔵 庫 、 電 気 冷 凍 庫 、 電 気 冷 凍 冷 蔵 庫 、 D N A 保 存 用 冷 凍 庫 、 懐 中 電 灯 、 工具、煙感知器、医療機器、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレー タ、産業用ロボット、電力貯蔵システム、電気自動車、ハイブリッド車、プラグインハイ ブリッド車、装軌車両、原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、船 舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇 宙船等がある。本実施の形態では、先の実施の形態で示した半導体装置を、携帯電話、ス マートフォン、電子書籍などの携帯機器に応用した場合の例を図14乃至図17を用いて 説明する。

#### [0305]

携帯電話、スマートフォン、電子書籍などの携帯機器においては、画像データの一時記憶などにSRAMまたはDRAMが使用されている。SRAMまたはDRAMが使用される理由としてはフラッシュメモリでは応答が遅く、画像処理では不向きであるためである。一方で、SRAMまたはDRAMを画像データの一時記憶に用いた場合、以下の特徴がある。

### [0306]

通常のSRAMは、図14(A)に示すように1つのメモリセルがトランジスタ801~ 806の6個のトランジスタで構成されており、それをXデコーダー807、Yデコーダ 10

20

30

40

10

20

30

40

50

- 8 0 8 にて駆動している。トランジスタ 8 0 3 とトランジスタ 8 0 5 、トランジスタ 8 0 4 とトランジスタ 8 0 6 はインバータを構成し、高速駆動を可能としている。しかし 1 つのメモリセルが 6 トランジスタで構成されているため、セル面積が大きいという欠点がある。デザインルールの最小寸法を F としたときに S R A M のメモリセル面積は通常 1 0 0 ~ 1 5 0 F <sup>2</sup> である。このため S R A M はビットあたりの単価が各種メモリの中で最も高い。

[0307]

それに対して、 D R A M はメモリセルが図 1 4 ( B ) に示すようにトランジスタ 8 1 1 、保持容量 8 1 2 によって構成され、それを X デコーダー 8 1 3 、 Y デコーダー 8 1 4 にて駆動している。 1 つのセルが 1 トランジスタ及び 1 容量の構成になっており、面積が小さい。 D R A M のメモリセル面積は通常 1 0 F <sup>2</sup> 以下である。ただし、 D R A M は常にリフレッシュが必要であり、書き換えをおこなわない場合でも電力を消費する。

[0308]

しかしながら、トランジスタ811に先の実施の形態で説明した、オフ電流の低いトランジスタを用いることで、保持容量812の電荷を長時間保持することが可能であり頻繁なリフレッシュは不要である。したがって、メモリセル面積が縮小され、且つ消費電力を低減することができる。

[0309]

[0310]

図16に、ディスプレイのメモリ回路950に先の実施の形態で説明した半導体装置を使用した例を示す。図16に示すメモリ回路950は、メモリ952、メモリ953、スイッチ954、スイッチ955及びメモリコントローラ951により構成されている。また、メモリ回路は、信号線から入力された画像データ(入力画像データ)、メモリ952、及びメモリ953に記憶されたデータ(記憶画像データ)を読み出し、及び制御を行うディスプレイコントローラ956と、ディスプレイコントローラ956からの信号により表示するディスプレイ957が接続されている。

[0311]

まず、ある画像データがアプリケーションプロセッサ(図示しない)によって、形成される(入力画像データA)。入力画像データAは、スイッチ954を介してメモリ952に記憶される。そしてメモリ952に記憶された画像データ(記憶画像データA)は、スイッチ955、及びディスプレイコントローラ956を介してディスプレイ957に送られ、表示される。

[0312]

入力画像データAに変更が無い場合、記憶画像データAは、通常30~60Hz程度の周期でメモリ952からスイッチ955を介して、ディスプレイコントローラ956から読み出される。

[0313]

次に、例えばユーザーが画面を書き換える操作をしたとき(すなわち、入力画像データAに変更が有る場合)、アプリケーションプロセッサは新たな画像データ(入力画像データB)を形成する。入力画像データBはスイッチ954を介してメモリ953に記憶される。この間も定期的にメモリ952からスイッチ955を介して記憶画像データAは読み出されている。メモリ953に新たな画像データ(記憶画像データB)が記憶し終わると、ディスプレイ957の次のフレームより、記憶画像データBは読み出され、スイッチ95 及びディスプレイコントローラ956を介して、ディスプレイ957に記憶画像データBが送られ、表示がおこなわれる。この読み出しはさらに次に新たな画像データがメモリ952に記憶されるまで継続される。

[0314]

このようにメモリ952及びメモリ953は交互に画像データの書き込みと、画像データの読み出しを行うことによって、ディスプレイ957の表示をおこなう。なお、メモリ952及びメモリ953はそれぞれ別のメモリには限定されず、1つのメモリを分割して使用してもよい。先の実施の形態で説明した半導体装置をメモリ952及びメモリ953に採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

[0315]

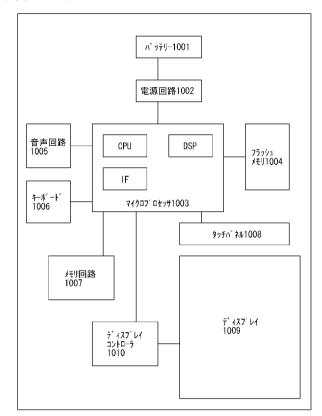

図 1 7 に電子書籍のブロック図を示す。図 1 7 はバッテリー 1 0 0 1、電源回路 1 0 0 2 、マイクロプロセッサ 1 0 0 3、フラッシュメモリ 1 0 0 4、音声回路 1 0 0 5、キーボード 1 0 0 6、メモリ回路 1 0 0 7、タッチパネル 1 0 0 8、ディスプレイ 1 0 0 9、ディスプレイコントローラ 1 0 1 0 によって構成される。

[0316]

ここでは、図17のメモリ回路1007に先の実施の形態で説明した半導体装置を使用することができる。メモリ回路1007の役割は書籍の内容を一時的に保持する機能を持つ。機能の例としては、ユーザーがハイライト機能を使用する場合などがある。ユーザーが電子書籍を読んでいるときに、特定の箇所にマーキングをしたい場合がある。このマーキング機能をハイライト機能と言い、表示の色を変える、アンダーラインを引く、文字を太くする、文字の書体を変えるなどによって、周囲との違いを示すことである。ユーザーが指定した箇所の情報を記憶し、保持する機能である。この情報を長期に保存する場合にはフラッシュメモリ1004にコピーしても良い。このような場合においても、先の実施の形態で説明した半導体装置を採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

[0317]

以上のように、本実施の形態に示す携帯機器には、先の実施の形態に係る半導体装置が搭載されている。このため、読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を低減した携帯機器が実現される。

[0318]

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【実施例1】

[0319]

本実施例では、実施の形態 1 に示す保護膜 2 3 の作製方法を用いて形成した酸化窒化シリコン膜の特性について説明する。具体的には、該作製方法で形成した酸化窒化シリコン膜に含まれる酸素量の T D S 分析(昇温脱離ガス分析)の結果を用いて説明する。

[0320]

まず、作製した試料について説明する。作製した試料は、実施の形態 1 に示す保護膜 2 3 の条件を用いてシリコンウェハ上に厚さ 4 0 0 n m の酸化窒化シリコン膜を形成した構造の試料である。

[0321]

10

20

30

40

シリコンウェハをプラズマ C V D 装置の処理室内に設置し、処理室内に原料ガスであるシランを 1 6 0 s c c m、原料ガスである一酸化二窒素を 4 0 0 0 s c c m供給し、処理室内の圧力を 2 0 0 P a に制御し、 2 7 . 1 2 M H z の高周波電源を用いて 1 5 0 0 W の電力を供給して酸化窒化シリコン膜を形成した。また、酸化窒化シリコン膜を形成する際の基板温度は 2 2 0 とした。なお、本実施例で用いたプラズマ C V D 装置は電極面積が 6 0 0 0 c m 2 である平行平板型のプラズマ C V D 装置であり、供給した電力を単位面積あたりの電力(電力密度)に換算すると 0 . 2 5 W / c m 2 である。

#### [0322]

上記した方法で作製した試料を試料A1とする。

### [0323]

また、比較例として、試料 A 1 の作製に用いたプラズマ C V D 装置を用いて、シリコンウェハ上に酸化窒化シリコン膜を形成した試料 A 2 を作製した。試料 A 2 の酸化窒化シリコン膜は、処理室内にシランを 3 0 s c c m、一酸化二窒素を 4 0 0 0 s c c m供給し、処理室内の圧力を 2 0 0 P a に制御し、 2 7 . 1 2 M H z の高周波電源を用いて 1 5 0 W の電力を供給することで形成した。なお、試料 A 2 の酸化窒化シリコン膜を形成する際に供給した電力は、単位面積あたりの電力(電力密度)に換算すると 0 . 0 2 5 W / c m 2 である。

### [0324]

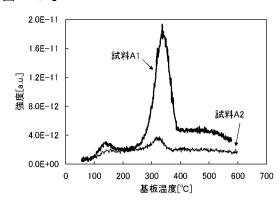

次に、試料 A 1 及び試料 A 2 について T D S 分析を行った。 T D S 分析の結果を図 1 8 に示す。図 1 8 の横軸は試料 A 1 及び試料 A 2 の基板温度を表し、縦軸は T D S スペクトルのピーク強度を表す。

#### [ 0 3 2 5 ]

TDS分析において、基板温度300 以上400 以下の領域に見られるピークは、分析した試料(本実施例では試料A1または試料A2)に含まれる酸素(詳細には酸素原子または酸素分子)が外部に脱離することで現れるピークである。なお、外部に脱離する酸素の総量は該ピークの積分値に相当する。また、酸化窒化シリコン膜において、化学量論的組成よりも多くの酸素を有する場合、過剰な酸素は脱離しやすく、外部に脱離しやすいと考えられる。それゆえ、該ピーク強度の強弱によって酸化窒化シリコン膜に含まれる酸素量を評価できる。

### [0326]

図 1 8 より、酸素が外部に脱離することで現れるピークは、試料 A 2 よりも試料 A 1 の強度が大きいと確認できた。従って、試料 A 1 の酸化窒化シリコン膜に含まれる酸素量は試料 A 2 の酸化窒化シリコン膜に含まれる酸素量より多いことが確認できた。

### [0327]

続いて、実施の形態1に示す保護膜23の作製方法において、絶縁膜を形成する際に供給する電力の影響について説明する。

## [0328]

まず、作製した試料について説明する。作製した試料は、試料 A 1 と同じ構造であり、絶縁膜として酸化窒化シリコン膜を形成する際に供給する電力を 1 0 0 0 W ( 0 . 1 7 W / c m <sup>2</sup> )、または 2 0 0 0 W ( 0 . 3 3 W / c m <sup>2</sup> )とした試料である。なお、酸化窒化シリコン膜を形成する際の他の条件は試料 A 1 と同じである。

#### [0329]

ここでは、供給する電力を 1 0 0 0 W ( 0 . 1 7 W / c m <sup>2</sup> ) とした試料を試料 A 3 とし、供給する電力を 2 0 0 0 W ( 0 . 3 3 W / c m <sup>2</sup> ) とした試料を試料 A 4 とする。

#### [0330]

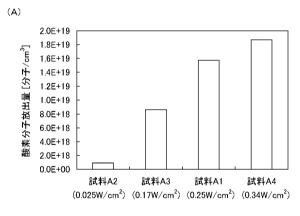

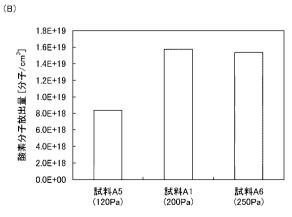

試料A3及び試料A4についてTDS分析を行った。TDS分析より得られる酸素量に関する説明は上記の通りである。TDS分析より得られた試料A1、試料A3、試料A4、及び試料A2の各試料に含まれる酸素量を図19(A)に示した。

#### [ 0 3 3 1 ]

図 1 9 ( A ) より、酸化窒化シリコン膜を形成する際に供給する電力を大きくするにつれ

10

20

30

40

て、作製した試料に含まれる酸素量が増加することを確認した。

#### [0332]

続いて、実施の形態 1 に示す保護膜 2 3 の作製方法において、絶縁膜を形成する際に制御する圧力の影響について説明する。

#### [0333]

まず、作製した試料について説明する。作製した試料は、試料 A 1 と同じ構造であり、酸化窒化シリコン膜を形成する際に制御する圧力を 1 2 0 P a 、または 2 5 0 P a とした試料である。なお、酸化窒化シリコン膜を形成する際の他の条件は試料 A 1 と同じである。

#### [0334]

ここでは、制御する圧力を120Paとした試料を試料A5とし、制御する圧力を250 Paとした試料を試料A6とする。

#### [0335]

試料A5及び試料A6についてTDS分析を行った。TDS分析より得られる酸素量に関する説明は上記の通りである。TDS分析より得られた試料A1、試料A5及び試料A6の各試料に含まれる酸素量を図19(B)に示した。

#### [0336]

図 1 9 (B)より、酸化窒化シリコン膜を形成する際に制御する圧力を高くすることで、作製した試料に含まれる酸素量が増加することを確認した。

#### [ 0 3 3 7 ]

以上より、実施の形態1に示す保護膜23の作製方法を用いて酸化窒化シリコン膜を形成することで、化学量論的組成よりの多くの酸素を有する酸化窒化シリコン膜を形成できることが確認できた。該酸化窒化シリコン膜は加熱されることで酸素の一部が脱離するため、該酸化窒化シリコン膜をトランジスタの保護膜として用いることで、該酸素をトランジスタの酸化物半導体膜に拡散させることができる。この結果、優れた電気特性を有するトランジスタを作製できることができる。

#### 【実施例2】

### [0338]

本実施例では、実施の形態 1 に示す保護膜 2 3 の作製方法を用いて形成した酸化窒化シリコン膜の特性について、実施例 1 とは異なる構造の試料を T D S 分析した結果を用いて説明する。

#### [0339]

本実施例で作製した試料は、シリコンウェハ上に厚さ 5 0 n m の窒化シリコン膜を形成し、該窒化シリコン膜上に厚さ 2 0 0 n m の酸化窒化シリコン膜を形成した積層構造の試料である。

## [0340]

シリコンウェハをプラズマ C V D 装置の処理室内に設置し、処理室内に50 s c c m のシラン、5000s c c m の窒素を供給し、処理室内の圧力を60 P a に制御し、27.12 M H z の高周波電源を用いて150 W の電力を供給して窒化シリコン膜を形成した。また、窒化シリコン膜を形成する際の基板温度は350 とした。なお、本実施例で用いたプラズマ C V D 装置は実施例1と同様であり、電力密度に換算すると0.25 W / c m 2 である。

#### [ 0 3 4 1 ]

続いて、160sccmのシラン、4000sccmの一酸化二窒素を処理室内に供給し、処理室内の圧力を200Paに制御し、27.12MHzの高周波電源を用いて1500W(0.25W/cm²)の電力を供給して、窒化シリコン膜上に酸化窒化シリコン膜を形成した。また、当該酸化窒化シリコン膜を形成する際の基板温度は220 とした。このようにして作製した試料を試料B1とする。

#### [ 0 3 4 2 ]

また、上記室化シリコン膜上に100sccmのシラン、3000sccmの一酸化二窒素を処理室内に供給し、処理室内の圧力を40Paに制御し、27.12MHzの高周波

10

20

30

40

電源を用いて1500W(0.25W/cm²)の電力を供給して、窒化シリコン膜上に酸化窒化シリコン膜を形成した試料を試料B2とする。また、当該酸化窒化シリコン膜を形成する際の基板温度は350 とした。

#### [ 0 3 4 3 ]

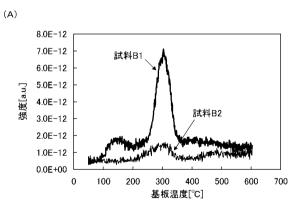

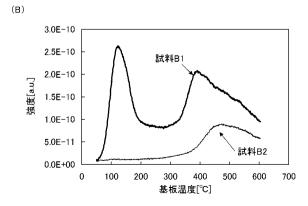

試料B1及び試料B2についてTDS分析を行った。TDS分析の結果を図20に示す。本実施例におけるTDS分析は実施例1と同様に行った。図20(A)及び図20(B)において、横軸は試料B1及び試料B2の基板温度を表し、縦軸はTDSスペクトルのピーク強度を表す。

#### [0344]

図20(A)は、試料B1及び試料B2において外部に脱離する酸素量に対応する結果を表し、図20(B)は、試料B1及び試料B2において外部に脱離する水の量に対応する結果を表している。なお、実施例1と同様に図20(A)及び図20(B)のピーク強度の強弱によって試料B1または試料B2の酸化窒化シリコン膜に含まれる酸素量、及び水の量を評価できる。

#### [ 0 3 4 5 ]

図 2 0 ( A ) より、酸素が外部に脱離することで現れるピークは試料 B 2 よりも試料 B 1 のほうが大きいと確認できた。従って、試料 B 1 の酸化窒化シリコン膜に含まれる酸素量は試料 B 2 の酸化窒化シリコン膜に含まれる酸素量より多いことが確認できた。

#### [0346]

このことから、基板温度を180 以上250 以下とする実施の形態1に示す保護膜23の作製方法を用いて酸化窒化シリコン膜を形成することで、化学量論的組成よりの多くの酸素を有する酸化窒化シリコン膜を形成できることが確認できた。

#### [0347]

なお、図20(B)より、水が外部に脱離することで現れるピークは試料B2よりも試料B1のほうが大きいと確認された。なお、基板温度が100 付近に現れるピークは、吸着水の脱離を示すピークである。このことから、試料B1は、試料B2と比較して、粗な膜であり、水を吸着しやすいことがわかる。以上のことから、試料B1の酸化窒化シリコン膜に含まれる水の量は試料B2の酸化窒化シリコン膜に含まれる水の量より多いといえる。これは、試料B1の酸化窒化シリコン膜を形成する際のシランの流量が試料B2の酸化窒化シリコン膜を形成する際のシランの流量が試料B1の方が低いことが理由と推察される。

## 【実施例3】

#### [0348]

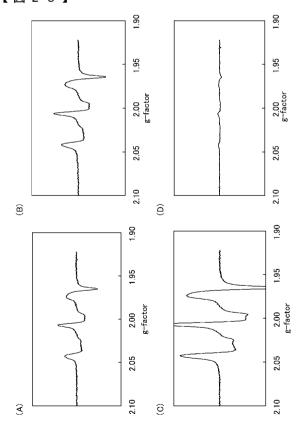

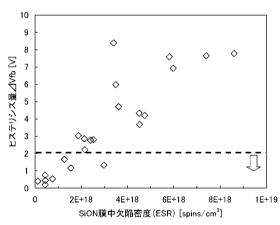

本実施例では、酸化物半導体膜上に酸化窒化シリコン膜を形成する際に、酸化物半導体膜に生じる欠陥量について説明する。具体的には、酸化物半導体膜上に酸化窒化シリコン膜を形成した試料のESR測定結果、及びCPM(Constant photocurrent method)測定結果を用いて説明する。

#### [0349]

はじめに、ESR測定結果について説明する。まず、作製した試料について説明する。作製した試料は、石英基板上に厚さ100nmの酸化物半導体膜を形成し、該酸化物半導体膜上に厚さ400nmの酸化窒化シリコン膜を形成した積層構造の試料である。

#### [0350]

石英基板上にスパッタリング法を用いてCAAC-OS膜であるIGZO膜を形成した。該IGZO膜は、スパッタリングターゲットをIn:Ga:Zn=1:1:1(原子数比)のターゲットとし、スパッタリングガスとして50sccmのArと50sccmの酸素をスパッタリング装置の処理室内に供給し、処理室内の圧力を0.6Paに制御し、5kWの直流電力を供給して形成した。なお、IGZO膜を形成する際の基板温度は170とした。また、該IGZO膜を形成した後、窒素雰囲気で第1の加熱処理を行い、続けて窒素及び酸素を含む雰囲気で第2の加熱処理を行った。加熱処理の温度は共に350とし、加熱処理を行った時間は第1の加熱処理及び第2の加熱処理共に1時間とした。

10

20

30

40

#### [0351]

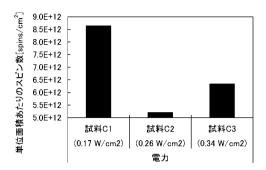

次に、IGZO膜を形成した石英基板をプラズマCVD装置の処理室内に設置し、処理室内に原料ガスであるシランを160sccm、原料ガスである一酸化二窒素を4000sccm供給し、処理室内の圧力を120Paに制御し、27.12MHzの高周波電源で電力を供給して酸化窒化シリコン膜を形成した。なお、該プラズマCVD装置は6000cm²である平行平板型のプラズマCVD装置である。供給する電力(電力密度)は1000W(0.17W/cm²)、1500W(0.25W/cm²)、2000W(0.33W/cm²)の3条件とし、それぞれを試料C1、試料C2、試料C3をする。

## [0352]

そして、試料 C 1 乃至試料 C 3 について E S R 測定を行った。 E S R 測定は下記の条件で行った。測定温度は室温(2 5 )とし、9 . 2 G H z の高周波電力(マイクロ波パワー)は2 0 m W とし、磁場の向きは作製した試料の酸化窒化シリコン膜の表面と平行とし、I G Z O 膜の酸素欠損に由来する g = 1 . 9 3 に現れる信号の、単位面積あたりのスピン数の検出下限を1 . 0 × 1 0 <sup>1 2</sup> s p i n s / c m <sup>2</sup> とした。

#### [0353]

ESR測定の結果を図21に示す。図21は酸化窒化シリコン膜を形成する際に供給する電力と、酸化物半導体膜中のg=1.93に現れる信号の単位面積あたりのスピン数との関係を表した図である。単位面積あたりのスピン数が小さいほど酸化物半導体膜に含まれる酸素欠損は少ないといえる。

## [ 0 3 5 4 ]

図21より、試料C1と比較して、試料C2及び試料C3の単位面積あたりのスピン数が低減していると確認できた。従って、酸化物半導体膜上に酸化窒化シリコン膜を形成する際、実施の形態1に示す保護膜23の作製方法を用いて酸化窒化シリコン膜を形成することで、該酸化窒化シリコン膜を形成したときに生じる酸化物半導体膜中の酸素欠損をさらに低減することができる。

#### [0355]

また、酸化窒化シリコン膜を形成する際の電力を 1 5 0 0 W ( 0 . 2 5 W / c m <sup>2</sup> ) と一定にし、シランの流量を 1 2 0 s c c m または 2 0 0 s c c m として酸化窒化シリコン膜を形成した試料を作製した。シランの流量が 1 2 0 s c c m である試料を試料 C 4 とし、シランの流量が 2 0 0 s c c m である試料を試料 C 5 とする。

#### [0356]

試料 C 2、 試料 C 4 及び試料 C 5 についても上記と同様条件で E S R 測定を行った。結果を図 2 2 に示す。図 2 2 は酸化窒化シリコン膜を形成する際に供給するシランの流量と、酸化物半導体膜中のg = 1 . 9 3 に現れる信号の単位面積あたりのスピン数との関係を表した図である。

## [0357]

図 2 2 より、酸化窒化シリコン膜を形成する際にシランの流量を増大すると、単位面積あたりのスピン数が低減する傾向にあると確認できた。従って、酸化物半導体膜上に酸化窒化シリコン膜を形成する際、シランの流量を増大して形成することによって、該酸化窒化シリコン膜を形成したときに生じる酸化物半導体膜中の酸素欠損をさらに低減することができる。

#### [0358]

次に、試料 C 2 、試料 C 4 、及び試料 C 5 を 3 0 0 で加熱処理を行った後、 E S R 測定を行った。この結果、試料 C 2 、試料 C 4 、及び試料 C 5 における I G Z 0 膜の酸素欠損に由来する g = 1 . 9 3 に現れる信号の単位面積あたりのスピン数は、検出下限(1 . 0 × 1 0  $^{1}$  2 s p i n s / c m  $^{2}$  ) 以下であった。

#### [0359]

以上のことから、酸化物半導体膜上に実施の形態 1 に示す保護膜 2 3 の作製方法を用いて酸化窒化シリコン膜を形成した後、加熱処理することで、酸化物半導体膜に含まれる酸素欠損を低減できることがわかった。

10

20

30

40

[0360]

次に、CPMの測定結果について説明する。まず、作製した試料について説明する。

[0361]

まず、基板としてガラス基板を用い、基板上に酸化物半導体膜を形成した。

[0362]

酸化物半導体膜としては、CAAC-OS膜であるIGZO膜をスパッタリング法で形成し、フォトリソグラフィエ程により該IGZO膜上にマスクを形成し、該マスクを用いて該IGZO膜の一部をエッチングした。その後、エッチングされたIGZO膜に加熱処理を行い、酸化物半導体膜を形成した。なお、本実施例では厚さ100nmのIGZO膜を形成した。

[0363]

IGZO膜は、スパッタリングターゲットをIn:Ga:Zn=1:1:1(原子数比)のターゲットとし、スパッタリングガスとして50sccmのArと50sccmの酸素をスパッタリング装置の処理室内に供給し、処理室内の圧力を0.7Paに制御し、5kWの直流電力を供給して形成した。なお、IGZO膜を形成する際の基板温度を170とした。

[0364]

エッチングされたIGZO膜に行った加熱処理は、窒素雰囲気で行う第1の加熱処理と、第1の加熱処理の後、続けて窒素及び酸素雰囲気で行う第2の加熱処理とした。第1の加熱処理及び第2の加熱処理の温度は共に450 とし、処理時間は第1の加熱処理及び第2の加熱処理共に1時間とした。

[0365]

次に、酸化物半導体膜に接する一対の電極を形成した。

[0366]

酸化物半導体膜上に導電膜を形成し、フォトリソグラフィエ程により該導電膜上にマスクを形成し、該マスクを用いて該導電膜の一部をエッチングし、一対の電極を形成した。なお、該導電膜は、厚さ100nmのチタン膜上に厚さ400nmのアルミニウム膜を形成し、該アルミニウム膜上に厚さ100nmのチタン膜を形成した。

[0367]

次に、加熱処理を行った。当該加熱処理は、温度を300 とし、酸素及び窒素を含む雰囲気で1時間行った。

[0368]

次に、酸化物半導体膜、及び一対の電極上に絶縁膜を形成した。

[0369]

絶縁膜は、実施の形態1に示す保護膜23の作製方法を用いて酸化窒化シリコン膜を形成した。具体的には、160sccmのシラン、4000sccmの一酸化二窒素をプラズマCVD装置の処理室に供給し、処理室の圧力を200Paに制御し、27.12MHzの高周波電源を用いて1500W(0.25W/cm²)の電力を供給して、厚さ400nmの酸化窒化シリコン膜を形成した。また、絶縁膜を形成する際の基板温度は220とした。

[0370]

絶縁膜を形成した後、ここまでの工程で得られた構成に加熱処理を行った。当該加熱処理 は、温度を300 とし、酸素及び窒素を含む雰囲気で1時間行った。

[0371]

以上の工程により、得られた試料を試料て6とする。

[0372]

ここで、比較例となる試料の作製工程について説明する。比較例となる試料(以下、試料 C 7 とする。)は、上記試料 C 6 の絶縁膜を下記のようにして形成したトランジスタであり、他の工程は全て同じである。試料 C 7 の絶縁膜は、3 0 s c c m のシラン、4 0 0 0 s c c m の一酸化二窒素をプラズマ C V D 装置の処理室に供給し、処理室の圧力を 2 0 0

10

20

30

40

Paに制御し、27.12MHzの高周波電源を用いて150W(0.025W/cm<sup>2</sup>)の電力を供給して、厚さ400nmの酸化窒化シリコン膜を形成した。また、絶縁膜を 形成する際の基板温度は220 とした。

[0373]

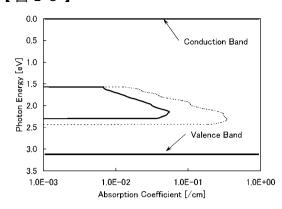

次に、試料C6及び試料C7のCPM測定を行った。CPM測定は、試料に設けられた一対の電極の間に電圧を印加した状態で光電流値が一定となるように試料面に照射する光量を調整し、照射光量から吸光係数を測定する方法である。CPM測定においては、試料に欠陥があるとき、欠陥の存在する準位に応じたエネルギー(波長より換算)における吸光係数が増加する。この吸光係数の増加分に定数を掛けることにより、試料の欠陥密度を評価することができる。

[0374]

試料 C 6 及び試料 C 7 それぞれを C P M 測定して得られた吸収係数からバンドテイル起因の吸収係数を除いた吸収係数、即ち欠陥に起因する吸収係数を図 2 3 に示す。図 2 3 において、横軸は吸収係数を表し、縦軸は光エネルギーを表す。なお、図 2 3 の縦軸において、酸化物半導体膜の伝導帯の下端を 0 e V とし、価電子帯の上端を 3 . 1 5 e V とする。また、図 2 3 において、各曲線は吸収係数と光エネルギーの関係を示す曲線であり、欠陥準位に相当する。実線で示す曲線は試料 C 6 の欠陥準位に相当し、破線で示す曲線は試料 C 7 の欠陥準位に相当する。試料 C 6 における欠陥準位による吸収係数は 1 . 0 0 × 1 0 · 2 / c mであった。

[0375]

図23より、試料C7と比較して試料C6の欠陥準位が少ないことが分かる。

[0376]

以上のことから酸化物半導体膜上に酸化窒化シリコン膜を形成する際、シランの流量を増大させると共に、供給電力を増大させることによって、該酸化窒化シリコン膜を形成したときに生じる酸化物半導体膜中の酸素欠損をさらに低減することができる。

[0377]

以上より、酸化物半導体膜を有するトランジスタ上に保護膜として酸化窒化シリコン膜を 形成する際、実施の形態 1 に示す保護膜 2 3 の作製方法を用いて酸化窒化シリコン膜を形 成することで、優れた電気特性を有するトランジスタを作製することができる。

【実施例4】

[0378]

本実施例は、本発明の一態様である半導体装置の電気特性について説明する。具体的には 本発明の一態様であるトランジスタの電流 - 電圧特性の結果を用いて説明する。

[0379]

はじめに、トランジスタの作製工程について説明する。本実施例では図4を参照して説明 する。

[0380]

まず、基板11としてガラス基板を用い、基板11上にゲート電極15を形成した。

[0381]

スパッタリング法で厚さ100nmのタングステン膜を形成し、フォトリソグラフィ工程により該タングステン膜上にマスクを形成し、該マスクを用いて該タングステン膜の一部をエッチングし、ゲート電極15を形成した。

[0382]

次に、ゲート電極 1 5 上に絶縁膜 3 1 及び絶縁膜 3 2 で構成されるゲート絶縁膜 3 3 を形成した。

[0383]

絶縁膜3 1 として厚さ5 0 n m の窒化シリコン膜を形成し、絶縁膜3 2 として厚さ2 0 0 n m の酸化窒化シリコン膜を形成した。該窒化シリコン膜は、シラン 5 0 s c c m 、窒素5 0 0 0 s c c mをプラズマ C V D 装置の処理室に供給し、処理室内の圧力を 6 0 P a に

10

20

30

30

40

制御し、27.12MHzの高周波電源を用いて150Wの電力を供給して形成した。該酸化窒化シリコン膜は、シラン20sccm、一酸化二窒素3000sccmをプラズマCVD装置の処理室に供給し、処理室内の圧力を40Paに制御し、27.12MHzの高周波電源を用いて100Wの電力を供給して形成した。なお、該窒化シリコン膜及び該酸化窒化シリコン膜は、基板温度を350 として形成した。

[ 0 3 8 4 ]

ここまでの工程で得られた構成は図4(A)を参照できる。なお、図4(A)には下地絶縁膜13が図示されているが、本実施例において下地絶縁膜13は形成していない。

[0385]

次に、ゲート絶縁膜33を介してゲート電極15に重なる酸化物半導体膜19を形成した

[0386]

ここでは、酸化物半導体膜19として、CAAC-OS膜であるIGZO膜をスパッタリング法で形成した。

[0387]