(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第3794637号 (P3794637)

(45) 発行日 平成18年7月5日(2006.7.5)

(24) 登録日 平成18年4月21日 (2006.4.21)

(51) Int.C1.

F I

HO1L 27/146 HO4N 5/335 (2006.01) (2006.01) HO1L 27/14 HO4N 5/335

請求項の数 7 (全 17 頁)

(21) 出願番号 特願2003-62282 (P2003-62282) (22) 出願日 平成15年3月7日 (2003.3.7)

(65) 公開番号 特開2004-273759 (P2004-273759A) (43) 公開日 平成16年9月30日 (2004. 9. 30)

審查請求日 平成16年9月30日 (2004: 5: 30) 審查請求日 平成16年2月17日 (2004: 2: 17)

早期審查対象出願

前置審查

|(73)特許権者 000005821

Α

$\mathbf{E}$

松下電器産業株式会社

大阪府門真市大字門真1006番地

||(74)代理人 100098291

弁理士 小笠原 史朗

(72)発明者 稲垣 誠

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

|(72)発明者 松長 誠之

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

審査官 柴山 将隆

最終頁に続く

#### (54) 【発明の名称】 固体撮像装置

## (57)【特許請求の範囲】

#### 【請求項1】

入射した光信号の強度に応じた電気信号を出力する固体撮像装置であって、

半導体基板上に、入射光を光電変換し得られた信号電荷を蓄積するフォトダイオードと、前記フォトダイオードに蓄積された信号電荷をゲート電極に印加されたパルス信号に従って転送する転送トランジスタと、転送された前記信号電荷を一時的に蓄積するフローティング拡散層部と、増幅トランジスタと、前記フローティング拡散層部に蓄積された信号電荷をゲート電極に印加されたパルス信号に従ってリセットするリセットトランジスタとを含む感光セルを行および列方向の2次元状に配列した感光領域と、

前記増幅トランジスタのドレインに共通して接続される電源ラインと、

同一列に配列された前記増幅トランジスタのソースに共通して接続される複数の垂直信 号線と、

同一行に配置された前記転送トランジスタのゲート電極からなる第 1 ゲート電極群を共通接続する複数の第 1 水平信号線と、

同一行に配置された前記リセットトランジスタのゲート電極からなる第 2 ゲート電極群 を共通接続する複数の第 2 水平信号線と、を備え、

前記感光セルでは、前記フォトダイオードと、前記転送トランジスタと、前記フローティング拡散層部と、前記増幅トランジスタと、前記リセットトランジスタとが、素子分離領域に囲まれた一つの活性領域内に形成されており、

前記感光セルに含まれる前記フローティング拡散層部は、当該感光セルと列方向に隣接

する感光セルに含まれる前記増幅トランジスタのゲートに接続されており、該フローティング拡散層部に蓄積された信号電荷は該隣接する感光セルに含まれる前記増幅トランジスタで増幅され、

各前記第1水平信号線と前記第1ゲート電極群とは同一材料かつ同層で連続的に形成され、かつ各前記第2水平信号線と前記第2ゲート電極群とは同一材料かつ同層で連続的に形成されていることを特徴とする、固体撮像装置。

### 【請求項2】

前記複数の第1水平信号線と前記複数の第2水平信号線とが、同一材料で形成されており、かつ、前記フローティング拡散層部は、同じ感光セルに含まれる前記転送トランジスタのゲート電極に接続される前記第1水平信号線と、同じ感光セルに含まれる前記リセットトランジスタのゲート電極に接続される前記第2水平信号線との間に挟まれていることを特徴とする、請求項1に記載の固体撮像装置。

#### 【請求項3】

前記フローティング拡散層部と前記増幅トランジスタのゲートとを接続するために、当該フローティング拡散層部に設けられる第1のコンタクトホールと、前記増幅トランジスタと前記リセットトランジスタとの共通ドレインを前記電源ラインに接続するために、当該共通ドレインに設けられる第2のコンタクトホールと、前記増幅トランジスタのソースを前記垂直信号線に接続するために、当該ソースに設けられる第3のコンタクトホールと、前記フローティング拡散層部と前記増幅トランジスタのゲートとを接続するために、当該ゲートに設けられる第4のコンタクトホールとが、ほぼ一直線上に並んでいることを特徴とする、請求項1または2に記載の固体撮像装置。

#### 【請求項4】

前記フローティング拡散層部と前記増幅トランジスタのゲートとを接続するために、当該フローティング拡散層部に設けられる第1のコンタクトホールと、前記増幅トランジスタと前記リセットトランジスタとの共通ドレインを前記電源ラインに接続するために、当該共通ドレインに設けられる第2のコンタクトホールと、前記増幅トランジスタのソースを前記垂直信号線に接続するために、当該ソースに設けられる第3のコンタクトホールとが、ほぼ一直線上に並んでいることを特徴とする、請求項1または2に記載の固体撮像装置。

## 【請求項5】

前記フローティング拡散層部と前記増幅トランジスタのゲートとを接続する信号線と、前記電源ラインと、前記垂直信号線とが、同一の金属配線層で形成されていることを特徴とする、請求項1~4のいずれかに記載の固体撮像装置。

## 【請求項6】

前記電源ラインは、同じ列に配列された前記増幅トランジスタのドレインに共通して接続される複数の垂直電源ラインを含み、

前記フローティング拡散層部と前記増幅トランジスタのゲートとを接続する信号線は、 当該フローティング拡散層部と同じ感光セルに含まれる前記増幅トランジスタに接続され る前記垂直信号線と、当該増幅トランジスタのドレインに接続される前記垂直電源ライン との間に挟まれていることを特徴とする、請求項1~5のいずれかに記載の固体撮像装置

### 【請求項7】

前記感光セルに含まれるすべてのトランジスタが、nチャンネル型MOSトランジスタであることを特徴とする、請求項1~6のいずれかに記載の固体撮像装置。

#### 【発明の詳細な説明】

## [0001]

### 【発明の属する技術分野】

本発明は、家庭用ビデオカメラ、デジタルスチルカメラ、携帯電話用カメラなど、各種の機器に用いられるMOS型固体撮像装置に関する。

## [0002]

50

40

20

### 【従来の技術】

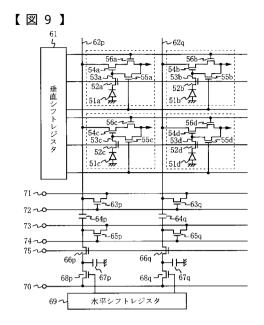

図9および図10を参照して、従来のセンサ、およびその駆動方法を説明する。図9は、従来のセンサの回路図である。図9に示すセンサは、2×2のマトリックス状に配列された感光セル(破線で囲んだ部分)を備えている。各感光セルは、フォトダイオード51、転送ゲート52、フローティング拡散層部53、増幅トランジスタ54、リセットトランジスタ55、およびアドレストランジスタ56を含み、画像を構成する一つの画素に対応する。なお、以下では、説明を簡単にするために、感光セルは2×2のマトリックス状に配列されていると仮定するが、実際には、感光セルは行および列方向にそれぞれ数十から数千個配列される。

## [0003]

図9に示すセンサの駆動方法は、以下のとおりである。 1 行目の感光セルから信号を取り出すためには、まず、 1 行目の感光セルに含まれるアドレストランジスタ5 6 a 、 5 6 b が、垂直シフトレジスタ6 1 から O N 状態に制御される。次に、リセットトランジスタ5 5 a 、 5 5 b が、同様に、垂直シフトレジスタ6 1 から O N 状態に制御される。これにより、フローティング拡散層部53 a 、 5 3 b はリセットされる。このとき、増幅トランジスタ6 3 p とによってソースホロア回路が構成され、垂直信号線62 p 上にはこのソースホロア回路の出力が現れる。同様に、増幅トランジスタ5 4 b と負荷トランジスタ63 q とによってソースホロア回路が構成され、垂直信号線62 q 上にもソースホロア回路の出力が現れる。これに青号電荷とは無関係な雑音電をある。次に、転送ゲート52 a 、 5 1 b に蓄積された信号電荷とは無関係な雑態に制定される。これにより、フォトダイオード51 a 、 5 1 b に蓄積されていた信号電荷に対応する信号電圧が現れる。

### [0004]

クランプ容量64p、64a、クランプトランジスタ65p、65a、サンプルホールドトランジスタ66p、66a、およびサンプルホールド容量67p、67aは、雑音抑圧回路を構成する。この雑音抑圧回路は、フローティング拡散層部53に信号電荷があるときの画素出力(すなわち、信号出力)と、信号電荷がないときの画素出力(すなわち、雑音出力)との差を求める。図9に示すセンサでは、主として、増幅トランジスタ54の閾値電圧のばらつきによる雑音と、リセットトランジスタ55の熱雑音であるkTC雑音とが発生する。垂直信号線62p、62a上に雑音出力が現れているときに、クランプトランジスタ65p、65aとサンプルホールドトランジスタ66p、66aとは、制御端子74、75からON状態に制御され、サンプルホールド容量67p、67aにはクランプ電圧供給端子73から雑音のないクランプ電圧が印加される。所定の時間が経過した後、クランプトランジスタ65p、65aは、制御端子74からOFF状態に制御される。

## [0005]

次に、垂直信号線62p、62 qには、雑音のない信号電圧と雑音電圧の和に等しい電圧が現れる。垂直信号線62p、62 q は雑音電圧から信号電圧と雑音電圧との和に変化し、その変化分は雑音のない信号電圧に相当する。したがって、クランプ容量64p、64 q のサンプルホールド側電圧も、雑音のない信号電圧に相当する分だけ変化する。実際に、サンプルホールド容量67p、67 q にかかる電圧は、雑音のないクランプ電圧から、垂直信号線62p、62 q の信号電圧変化分をクランプ容量とサンプルホールド容量で分圧した電圧分だけ変化する。よって、サンプルホールド容量67p、67 q にかかる電圧は、雑音のないクランプ電圧と分圧された信号電圧とであり、雑音分が除去されている。サンプルホールドトランジスタ66p、66 q が O F F 状態に制御された後、水平シフトレジスタ69によって、水平トランジスタ68p、68 q が順次選択的にON 状態に制御される。これにより、フォトダイオード51a、51bに蓄積されていた信号電荷に対応する信号が、出力端子70から順次出力される。

## [0006]

40

10

20

次に、2行目の感光セルから信号を取り出すために、2行目の感光セルについて、1行目の場合と同様の操作が行われる。これにより、フォトダイオード51 c、51 dに蓄積されていた信号電荷に対応する信号が、出力端子70から順次出力される。

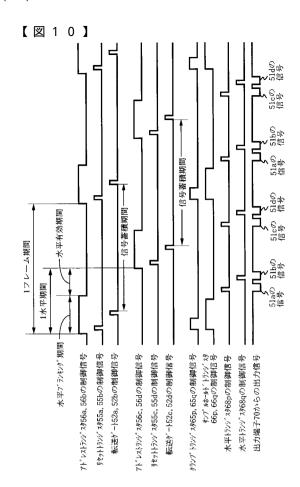

#### [0007]

以上の動作をタイミングチャートで示すと、図10のようになる。図10において、フォトダイオード51の1行分に蓄積されていた信号が最終的に出力端子70から出力される期間を水平有効期間と呼び、フォトダイオード51から信号を垂直信号線62に出力し、出力した信号の雑音を抑圧する期間を水平ブランキング期間と呼ぶ。また、水平ブランキング期間と水平有効期間とを合わせて、1水平期間と呼ぶ。1水平期間は、実際に1行分の信号を読み出すために要する時間である。センサ全体から信号を読み出すために要する時間を1フレーム期間と呼ぶ。図10に示すように、フォトダイオード51に蓄積される信号電荷の量は、転送ゲート52に印加される転送パルスの時間間隔で定まる。また、転送パルスの時間間隔は、1フレーム期間で一定である。このため、フォトダイオード51の感度は、一定になる。

#### [ 0 0 0 8 ]

図9に示すセンサでは、4個のトランジスタ(転送ゲート52、増幅トランジスタ54、リセットトランジスタ55、およびアドレストランジスタ56)によって、各感光セルが構成されている。これに対して、最近、センサの小型化のために、3個のトランジスタで各感光セルを構成したセンサが考案されている。この新しく考案されたセンサは、図9に示すセンサからアドレストランジスタ56を除去した上で、感光セルの電源を共通化した構成を有している。このセンサから信号を読み出すためには、各感光セルにパルス状の電源電圧を供給する必要がある。

### [0009]

なお、図9に示すセンサの駆動方法は、例えば、特許文献1に記載されている。また、各感光セルを3個のトランジスタで構成したセンサについて、感光セルの具体的なレイアウトを記載した文献は知られていない。

## [0010]

#### 【特許文献1】

特開平9-247537号公報

#### [0011]

#### 【発明が解決しようとする課題】

センサに限らず半導体集積回路では、回路のレイアウトは、回路の構成やデザインルールなどとともに、回路サイズを決定する要因の一つとなる。一般に、回路サイズが小さいほど、回路の歩留まりが向上し、回路のコストが低下する。したがって、所定のデザインルールに従って与えられた回路をいかにレイアウトするかは、半導体集積回路の設計における重要な技術課題の一つである。しかしながら、各感光セルを3個のトランジスタで構成したセンサについて、感光セルの具体的なレイアウトは、従来、明らかにされていなかった。

## [0012]

それ故に、本発明は、各感光セルを3個のトランジスタで構成したセンサについて、レイ 40 アウトに適した新規な回路構成を明らかにし、回路サイズの小さなセンサを提供すること を目的とする。

## [0013]

## 【課題を解決するための手段及び発明の効果】

第1の発明は、入射した光信号の強度に応じた電気信号を出力する固体撮像装置であって、半導体基板上に、入射光を光電変換し得られた信号電荷を蓄積するフォトダイオードと、フォトダイオードに蓄積された信号電荷をゲート電極に印加されたパルス信号に従って転送する転送トランジスタと、転送された信号電荷を一時的に蓄積するフローティング拡散層部と、増幅トランジスタと、フローティング拡散層部に蓄積された信号電荷をゲート電極に印加されたパルス信号に従ってリセットするリセットトランジスタとを含む感光

20

30

30

40

50

セルを行および列方向の2次元状に配列した感光領域と、増幅トランジスタのドレインに共通して接続される電源ラインと、同一列に配列された増幅トランジスタのゲート電極して接続される複数の垂直信号線と、同一行に配置された転送トランジスタのゲート電極からなる第1ゲート電極群を共通接続する複数の第1水平信号線と、同一行に配置されたリセットトランジスタのゲート電極からなる第2ゲート電極群を共通接続する複数の第2水平信号線とを備え、感光セルでは、フォトダイオードと、転送トランジスタと、フローティング拡散層部と、増幅トランジスタと、リセットトランジスタと、フローティング拡散層部と、増幅トランジスタと、リセットトランジスタとが、素子分離領域に囲まれた一つの活性領域内に形成されており、感光セルに含まれるプローティング拡散層部は、当該感光セルと列方向に隣接する感光セルに含まれる増幅トランジスタのゲートに接続されており、該フローティング拡散層部に蓄積された信号電荷は該隣接する感光セルに含まれる増幅トランジスタで増幅され、各第1水平信号線と第1ゲート電極群とは同一材料かつ同層で連続的に形成され、かつ各第2水平信号線と第2ゲート電極群とは同一材料かつ同層で連続的に形成されていることを特徴とする。

このような第1の発明によれば、固体撮像装置の機能を損なうことなく、レイアウトに適した感光セルの回路構成を得ることができる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

#### [0014]

第2の発明は、第1の発明において、上記複数の第1水平信号線と、上記複数の第2水平信号線とが、同一材料で形成されており、かつ、フローティング拡散層部は、同じ感光セルに含まれる転送トランジスタのゲート電極に接続される第1水平信号線と、同じ感光セルに含まれるリセットトランジスタのゲート電極に接続される第2水平信号線との間に挟まれていることを特徴とする。

### [0015]

このような第2の発明によれば、第1水平信号線と転送トランジスタのゲート電極、第2水平信号線とリセットトランジスタのゲート電極とが同じ材料で形成されているので、これらの信号線を配線するときに、コンタクトホールを設ける必要がなくなる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

## [0016]

第3の発明は、第1または第2の発明において、フローティング拡散層部と増幅トランジスタのゲートとを接続するために、当該フローティング拡散層部に設けられる第1のコンタクトホールと、増幅トランジスタとリセットトランジスタとの共通ドレインを電源ラインに接続するために、当該共通ドレインに設けられる第2のコンタクトホールと、増幅トランジスタのソースを垂直信号線に接続するために、当該ソースに設けられる第3のコンタクトホールと、フローティング拡散層部と増幅トランジスタのゲートとを接続するために、当該ゲートに設けられる第4のコンタクトホールとが、ほぼ一直線上に並んでいることを特徴とする。

### [0017]

第4の発明は、第1または第2の発明において、フローティング拡散層部と増幅トランジスタのゲートとを接続するために、当該フローティング拡散層部に設けられる第1のコンタクトホールと、増幅トランジスタとリセットトランジスタとの共通ドレインを電源ラインに接続するために、当該共通ドレインに設けられる第2のコンタクトホールと、増幅トランジスタのソースを垂直信号線に接続するために、当該ソースに設けられる第3のコンタクトホールとが、ほぼ一直線上に並んでいることを特徴とする。

このような第3および第4の発明によれば、感光セルのレイアウト結果において、複数のコンタクトホールをほぼ一直線上に並べることにより、これらのコンタクトホールをレイアウトするために必要な面積を小さくすることができる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

#### [0018]

第5の発明は、第1ないし第4のいずれかの発明において、フローティング拡散層部と増

20

30

40

50

幅トランジスタのゲートとを接続する信号線と、電源ラインと、垂直信号線とが、同一の 金属配線層で形成されていることを特徴とする。

このような第 5 の発明によれば、フローティング拡散層部と増幅トランジスタのゲートとを接続する信号線と、電源ラインと、垂直信号線とを同一の金属配線層で形成することにより、これらの信号線を配線するときに、コンタクトホールを設ける必要がなくなる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

### [0019]

第6の発明は、第1ないし第5のいずれかの発明において、電源ラインは、同じ列に配列された増幅トランジスタのドレインに共通して接続される複数の垂直電源ラインを含み、フローティング拡散層部と増幅トランジスタのゲートとを接続する信号線は、当該フローティング拡散層部と同じ感光セルに含まれる増幅トランジスタに接続される垂直信号線と、当該増幅トランジスタのドレインに接続される垂直電源ラインとの間に挟まれていることを特徴とする。

このような第6の発明によれば、感光セルのレイアウトパターンが単純かつ規則的になる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

#### [0020]

第7の発明は、第1ないし第6のいずれかの発明において、感光セルに含まれるすべてのトランジスタが、nチャンネル型MOSトランジスタであることを特徴とする。

#### [0021]

## 【発明の実施の形態】

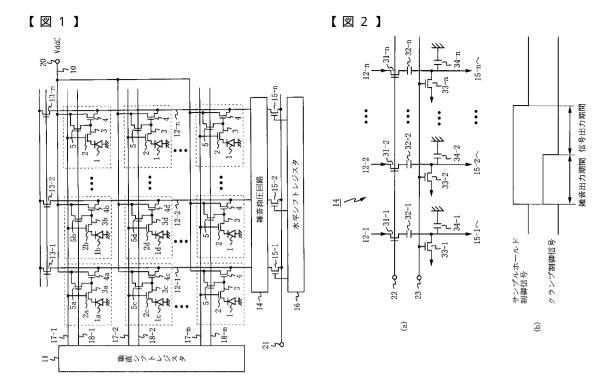

本発明の実施形態に係るセンサを説明するに先立ち、各感光セルを 3 個のトランジスタで構成したセンサの参考例を説明する。図 1 は、本発明の参考例に係るセンサの回路図である。図 1 に示すセンサは、 m × n のマトリックス状に配列された感光セル(破線で囲んだ部分)、電源ライン 1 0、垂直シフトレジスタ 1 1、 n 本の垂直信号線 1 2 - 1 ~ n、 n 個の負荷トランジスタ 1 3 - 1 ~ n、雑音抑圧回路 1 4、 n 個の水平トランジスタ 1 5 - 1 ~ n、および水平シフトレジスタ 1 6を備えている。各感光セルは、フォトダイオード 1、転送ゲート 2、フローティング拡散層部 3、増幅トランジスタ 4、およびリセットトランジスタ 5 を含み、アドレストランジスタを含まないことを特徴とする。実際のセンサにおけるmおよび n の値は、数十から数千程度である。

## [0022]

m×n個の感光セルは、半導体基板上に形成される。より詳細には、感光セルは、p型基板上、または、n型基板上のpウェル(P-well)内に形成される。各感光セルにおいて、フォトダイオード1は、入射光を光電変換し、得られた信号電荷を蓄積する。転送ゲート2は、フォトダイオード1とフローティング拡散層部3との間に設けられ、フォトダイオード1に蓄積された信号電荷をフローティング拡散層部3に転送する。フローティング拡散層部3は、フォトダイオード1から転送された信号電荷を一時的に蓄積する。増幅トランジスタ4は、フローティング拡散層部3に蓄積された信号電荷を増幅する。リセットトランジスタ5は、フローティング拡散層部3に蓄積された信号電荷を増幅する。

## [0023]

感光セルが配列された感光領域には、電源ライン 1 0 および垂直信号線 1 2 - 1 ~ nに加えて、2組のm本の信号線 1 7 - 1 ~ m、18 - 1 ~ mが配線される。電源ライン 1 0 は、増幅トランジスタ 4 のドレインに共通して接続される。本参考例では、電源ライン 1 0 は、すべての感光セルに含まれる増幅トランジスタ 4 およびリセットトランジスタ 5 のドレインに共通して接続され、電源ライン 1 0 の他端にある電源供給端子 2 0 から、すべての感光セルに対して、パルス状の電源電圧 V d d C が印加されるものとする。なお、図 1 では、すべての感光セルが 1 本の電源ライン 1 0 に接続されているが、感光セルに共通し

た電源を供給するために、電源ラインを2本以上使用してもよい。

#### [0024]

垂直信号線12-1~nは、感光セルの各列に対して設けられる。垂直信号線12~1~nは、それぞれ、同じ列に配列された感光セルに含まれる増幅トランジスタ4および負荷トランジスタ13-1~nと、雑音抑圧回路14とを接続する。信号線17-1~m、18-1~mは、垂直シフトレジスタ11の出力信号線であり、感光セルの各行に対して設けられる。信号線17-1~mは、それぞれ、同じ行に配列された感光セルに含まれる転送ゲート2のゲートを接続する。信号線18-1~mは、それぞれ、同じ行に配列された感光セルに含まれるリセットトランジスタ5のゲートを接続する。

#### [0025]

垂直シフトレジスタ11は、以下に示すように、垂直ドライバ回路として動作する。垂直シフトレジスタ11は、電源ラインVddCがハイレベルであるときに、同じ行に配列11は、電源ラインVddCがハイレベルであるときに、同じ行に配列11は、電源ラインVddCがハイレベルであるときに、転送ゲート2の駆動タイミングスタ11は、電源ライングで、同じ行に配列された感光セルに含まれるリセットトランジスタ5を同時に駆動する。負荷トランジスタ13-1~nは、それぞれ、垂直信号線12-1~nに接続され、行方向に並べて配列される。雑音抑圧回路14は、垂直信号線12-1~nに接続され、増幅トランジスタ4から出力された信号を取り込み、取り込んだ信号の雑下に接続され、増幅トランジスタ15-1~nは、行方向に並べて配列された信号を取り込み、取り込んだ信号の雑下トランジスタ15-1~nには、雑音抑圧回路14から出力されたn本の信号がそれぞれ、水平シフトレジスタ16は、水平ドライバ回路として動作する。すなわち、水平シフトレジスタ16は、水平ドライバ回路として動作する。すなわち、水平シフトレジスタ16は、水平ドライバ回路として動作する。すなわち、水平シフトレジスタ16は、水平トランジスタ15-1~nを順次選択的に動作させる。これにより、雑音抑圧回路14から出力されたn本の信号は、出力端子21から順次出力される。

### [0026]

図2は、雑音抑圧回路14の詳細を説明するための図である。雑音抑圧回路14は、図2(a)に示すように、n個のサンプルホールドトランジスタ31-1~n、n個のクランプトランジスタ33-1~n、およびn個のサンプルホールド容量34-1~nを含んでいる。雑音抑圧回路14は、図9に示した雑音抑圧回路とサンプルホールドトランジスタ31-1~nの位置が異なるが、図9に示した雑音抑圧回路とサンプルホールドトランジスタ31-1~nのゲートには、制御端子22から入力されるサンプルホールド制御信号が印加される。同様に、クランプトランジスタ33-1~nのゲートには、制御端子22から入力されるサンプルホールド制御信号が印加される。同様に、クランプトランジスタ33-1~nのゲートには、制御端子23から入力されるクランプ制御信号が印加される。これら2本の制御信号は、図2(b)に示すように変化する。2本の制御信号がともにハイレベルである期間が雑音出力期間となり、サンプルホールド制御信号がハイレベルで、クランプ制御信号がローレベルである期間が信号出力期間となる。

## [0027]

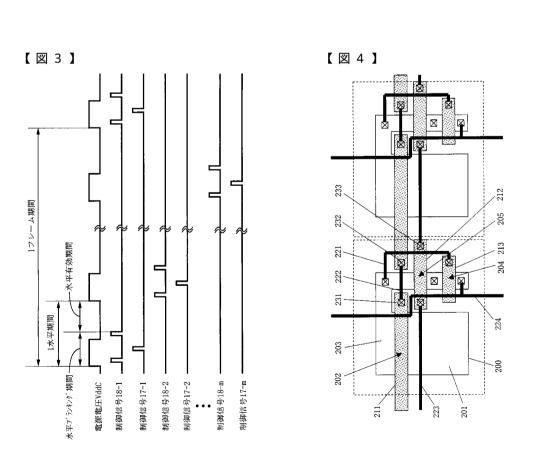

以下、図3に示すタイミングチャートを適宜参照しながら、図1に示すセンサの駆動方法を説明する。このセンサを駆動するためには、各水平期間ごとに、電源ライン10をパルス駆動するステップと、垂直シフトレジスタ11によって、m×n個のフォトダイオード1から1行分の信号を読み出すステップと、水平シフトレジスタ16によって、読み出した1行分の信号を順次出力するステップとが実行される。

## [0028]

図3に示すように、初期状態では、電源電圧VddCはローレベルである。すなわち、初期状態では、電源ライン10は駆動されていない。1行目の感光セルから信号を取り出すためには、まず、電源電圧VddCがハイレベルに制御される。これにより、すべての感光セルにおいて、転送ゲート2およびリセットトランジスタ5のドレインがハイレベルになる。次に、電源ライン10が駆動されている間に、垂直シフトレジスタ11が、信号線18-1を所定の時間だけハイレベルにする。これにより、リセットトランジスタ5a、5bを始め、1行目の感光セルに含まれるリセットトランジスタ5のゲート電位はハイレ

10

20

30

20

30

40

50

ベルとなり、これらリセットトランジスタ5はON状態となる。このとき、増幅トランジスタ4a、4bを始め、1行目の感光セルに含まれる増幅トランジスタ4も動作状態となる。同時に、フローティング拡散層部3a、3bを始め、1行目の感光セルに含まれるフローティング拡散層部3に蓄積された信号電荷をリセットしたときの雑音出力が、垂直信号線12-1~nに現れる。

#### [0029]

次に、電源ライン10が駆動されている間に、垂直シフトレジスタ11が、信号線17-1を所定の時間だけハイレベルにする。これにより、転送ゲート2a、2bを始め、1行目の感光セルに含まれる転送ゲート2のゲート電位はハイレベルとなり、これら転送ゲート2はON状態となる。このとき、フォトダイオード1a、1bを始め、1行目の感光セルに含まれるフォトダイオード1に蓄積された信号電荷は、各感光セルに含まれるフローティング拡散層部3に読み出され、読み出された信号電荷に対応した信号出力が、垂直信号線12-1~nに現れる。

### [0030]

このようにして、垂直信号線12-1~nには、雑音電圧が現れた後、信号電圧と雑音電圧との和が現れる。雑音抑圧回路14は、従来の雑音抑圧回路と同様に動作し、垂直信号線12-1~nに出力された信号の雑音を抑圧する。雑音抑圧回路14から出力されたn本の信号は、それぞれ、水平トランジスタ15-1~nに入力される。

#### [0031]

雑音抑圧回路14が動作した後、電源電圧VddCは、ローレベルに変化する。次に、電源ライン10が駆動されていない間に、垂直シフトレジスタ11が、信号線18-1を所定の時間だけハイレベルにする。これにより、フローティング拡散層部3a、3bを始め、1行目の感光セルに含まれるフローティング拡散層部3に蓄積された信号電荷は、リセットされる。また、増幅トランジスタ4a、4bを始め、1行目の感光セルに含まれる増幅トランジスタ4は、次に選択されるまで非動作状態となる。

#### [0032]

水平シフトレジスタ16は、水平トランジスタ15-1~nのゲートに接続されるn本の出力信号を出力する。水平シフトレジスタ16は、n本の出力信号を選択的にハイレベルにすることにより、水平トランジスタ15-1~nを順次選択的にON状態に制御する。これにより、フォトダイオード1a、1bを始め、1行目のフォトダイオード1に蓄積されていた信号電荷に対応する信号が、出力端子21から順次出力される。

## [0033]

次に、2行目の感光セルから信号を取り出すために、2行目の感光セルについて、1行目の場合と同様の操作が行われる。これにより、フォトダイオード1 c、1 dを始め、2行目の感光セルに蓄積されていた信号電荷に対応する信号が、出力端子21から順次出力される。以下、3行目からm行目の感光セルについても、同様の操作が行われる。なお、図3に示す水平ブランキング期間、水平有効期間、1水平期間、および1フレーム期間の定義、並びにフォトダイオード1の感度が一定になる点は、従来のセンサと同じである。

## [0034]

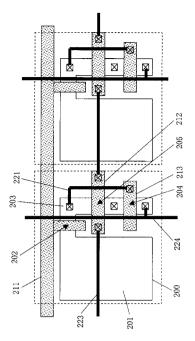

図1に示すセンサに含まれる感光セルを、特段の工夫を行わずにレイアウトすると、例えば、図4に示すレイアウトパターンが得られる。図4では、破線で囲んだ領域が、一つの感光セルに相当する。また、内部に色が塗られていない領域は活性領域200を、ハッチングされた領域はポリシリコン配線211~213を、黒い太線は金属配線221~224を、対角線を引いた正方形はコンタクトホールを表す。なお、以下に示すレイアウト図でも、図4と同じ記法を使用する。

## [0035]

活性領域200は、素子分離領域(図示せず)に囲まれた領域であり、その内部に、フォトダイオードや、各トランジスタのゲート、ソースおよびドレインなど、回路として機能する素子あるいはその電極などが形成される。図4に示すレイアウトパターンでは、各感光セルに活性領域200が一つずつ含まれている。

### [0036]

活性領域200とポリシリコン配線211~213とが重なる場所には、トランジスタが形成される。図4では、各感光セルにおいて、活性領域200とポリシリコン配線211~213とは3箇所で重なっている。これにより、各感光セルにおいて、3個のトランジスタが形成される。具体的には、活性領域200とポリシリコン配線211とが重なる場所には、転送ゲート202(図1では転送ゲート2)が形成される。活性領域200とポリシリコン配線212とが重なる場所には、リセットトランジスタ205(図1ではリセットトランジスタ5)が形成される。活性領域200とポリシリコン配線213とが重なる場所には、増幅トランジスタ204(図1では増幅トランジスタ4)が形成される。

## [0037]

活性領域 2 0 0 のうち、転送ゲート 2 0 2 からリセットトランジスタ 2 0 5 までの領域は、フローティング拡散層部 2 0 3 (図 1 ではフローティング拡散層部 3 )となる。また、活性領域 2 0 0 のうち、転送ゲート 2 0 2 を挟んでフローティング拡散層部 2 0 3 と反対側にある領域は、フォトダイオード 2 0 1 (図 1 ではフォトダイオード 1 )となる。

#### [0038]

このように形成された3個のトランジスタとフローティング拡散層部203とを所定の方法で電気的に接続すれば、図1に示す感光セルを実現できる。図4に示すレイアウトパターンでは、この接続に金属配線を使用している。具体的には、各感光セルにおいて、5種類の金属配線が使用され、図4には、そのうち4種類の金属配線221~224が示されている。金属配線221は、同じ感光セルに含まれるフローティング拡散層部203と増幅トランジスタ204のゲートとを接続する。金属配線222は、行方向に隣接して配列された感光セルに含まれるポリシリコン配線211を接続する。ポリシリコン配線211と金属配線222とによって、図1に示す信号線17が構成される。金属配線223は、行方向に隣接して配列された感光セルのポリシリコン配線212を接続する。ポリシリコン配線212と金属配線223とによって、図1に示す信号線18が構成される。金属配線224は、同じ列に配列された感光セルに含まれる増幅トランジスタ204のソースを接続する。金属配線224によって、図1に示す重信号線12が構成される。なお、図4では、図1に示す電源ライン10は、示されていない。

## [0039]

活性領域200と、ポリシリコン配線211~213と、金属配線221~224とは、 半導体製造プロセスでは、それぞれ、異なる工程で形成される。これら3種類の領域ある いは配線を電気的に接続するためには、層間を連結するためのコンタクトホールを設ける 必要がある。図4に示すレイアウトパターンでは、各感光セルについて、8個のコンタク トホールが設けられている。

## [0040]

上述したように、図4に示すレイアウトパターンでは、ポリシリコン配線211と金属配線222とによって、図1に示す信号線17が構成されている。この理由は、ポリシリコン配線211を金属配線222の部分にまで延長すると、活性領域200と延長したポリシリコン配線とに新たな重なりが生じ、この場所に不要なトランジスタが形成されてしまうからである。しかし、ポリシリコン配線211と金属配線222と用いた場合、両者を接続するために、各感光セルにおいて、2個のコンタクトホール231、232を設ける必要が生じる。これに伴い、金属配線221を配線するときには、コンタクトホール232を避けて配線する必要が生じる。さらに、コンタクトホール233は、金属配線221の金属配線223側(図4では右側)に設ける必要があるので、感光セルの水平方向のサイズが大きくなる。このように、図4に示すレイアウトパターンでは、信号線17を2種類の配線で構成しているために、感光セルの水平方向のサイズが大きくなってしまう。

### [0041]

そこで、図1に示すセンサに含まれる感光セルを、若干の工夫を行った上でレイアウトすると、例えば、図5に示すレイアウトパターンが得られる。このレイアウトパターンでは、ポリシリコン配線211のみによって、信号線17が実現されている。したがって、図

10

20

30

40

30

40

50

4に示すレイアウトパターンに含まれていたコンタクトホール231、232を削除できるので、図4に示すレイアウトパターンよりも、感光セルの水平方向のサイズを小さくすることができる。

## [0042]

しかし、図 5 に示すレイアウトパターンでは、ポリシリコン配線 2 1 2 と金属配線 2 2 3 とによって、図 1 に示す信号線 1 8 が構成されている。このため、ポリシリコン配線 2 1 2 のみによって信号線 1 8 を構成し、感光セルのサイズをさらに小さくできる可能性がある。

#### [0043]

そこで、以下では、本発明の実施形態に係るセンサについて、レイアウトに適した感光セルの新たな回路構成と、その構成を有する感光セルをレイアウトした結果とを説明する。

#### [0044]

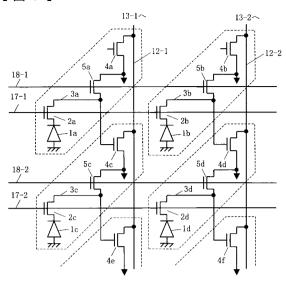

図6は、本発明の実施形態に係るセンサの回路図である。本実施形態に係るセンサは、参考例に係るセンサ(図1)と比べて、感光セルの回路構成のみが相違する。そこで、図6では、2×2のマトリックス状に配列された感光セル(破線で囲んだ部分)のみを示し、他の感光セル、および図1と同一の回路(垂直シフトレジスタ11、負荷トランジスタ13・1~n、雑音抑圧回路14、水平トランジスタ15・1~n、水平シフトレジスタ16)については、記載を省略している。

#### [0045]

本実施形態に係るセンサでは、参考例に係るセンサと同様に、各感光セルは、フォトダイオード 1、転送ゲート 2、フローティング拡散層部 3、増幅トランジスタ 4、およびリセットトランジスタ 5 を含んでいる。これら 5 個の要素の機能も、参考例に係るセンサと同様である。

#### [0046]

本実施形態に係るセンサに含まれる感光セルは、以下の点で、参考例に係るセンサに含まれる感光セルと相違する。すなわち、参考例に係るセンサでは、上述したように、各感光セルに含まれるフローティング拡散層部 3 は、同じ感光セルに含まれる増幅トランジスタ4のゲートに接続される。これに対して、本実施形態に係るセンサでは、図6に示すように、各感光セルに含まれるフローティング拡散層部 3 は、当該感光セルと列方向に隣接する感光セル(図6では、当該感光セルのすぐ下にある感光セル)に含まれる増幅トランジスタ4のゲートに接続される。例えば、図6において、左上の感光セルに含まれるフローティング拡散層部 3 a は、左下の感光セルに含まれる増幅トランジスタ4 c のゲートに接続される。同様に、左下の感光セルに含まれるフローティング拡散層部 3 c は、左下の感光セルのすぐ下にある感光セル(図6では一部のみが示されている)に含まれる増幅トランジスタ4 e のゲートに接続される。

## [0047]

このようにフローティング拡散層部3を、他の感光セルに含まれる増幅トランジスタ4のゲートに接続すると、フォトダイオード1に蓄積された信号電荷に対応した信号出力は、他の感光セルに含まれる増幅トランジスタ4の作用によって、垂直信号線12に現れることになる。このように回路構成を変更しても、他の感光セルが元の感光セルと同じ列に配列されている限り、センサ全体として見たときの動作は同じである。したがって、本実施形態に係るセンサに対して、参考例に係るセンサと同じ駆動方法(図3を参照)を適用すれば、本実施形態に係るセンサからでも、センサに入射した光信号に応じた電気信号を正しく読み出すことができる。

#### [0048]

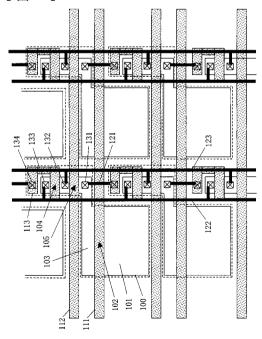

図6に示す感光セルをレイアウトすると、図7に示すレイアウトパターンが得られる。このレイアウトパターンにおいても、図4および図5に示すレイアウトパターンと同様に、各感光セルに活性領域100が一つずつ含まれている。各感光セルにおいて、活性領域100とポリシリコン配線111~113とは3箇所で重なっている。これにより、各感光セルにおいて、3個のトランジスタが形成される。具体的には、活性領域100とポリシ

20

30

40

50

リコン配線111とが重なる場所には、転送ゲート102(図6では転送ゲート2)が形成される。活性領域100とポリシリコン配線112とが重なる場所には、リセットトランジスタ105(図6ではリセットトランジスタ5)が形成される。活性領域100とポリシリコン配線113とが重なる場所には、増幅トランジスタ104(図6では増幅トランジスタ4)が形成される。

## [0049]

活性領域100のうち、転送ゲート102からリセットトランジスタ105までの領域は、フローティング拡散層部103(図6ではフローティング拡散層部3)となる。また、活性領域100のうち、転送ゲート102を挟んでフローティング拡散層部103と反対側にある領域は、フォトダイオード101(図6ではフォトダイオード1)となる。

[0050]

図7に示すレイアウトパターンでは、各感光セルにおいて、3種類の金属配線121~123が使用されている。金属配線121は、ある感光セルに含まれるフローティング拡散層部103と、当該感光セルに列方向に隣接する感光セルに含まれる増幅トランジスタ104のゲートとを接続する。金属配線122は、同じ列に配列された感光セルに含まれる増幅トランジスタ104のソースを接続する。この金属配線122によって、図1に示す垂直信号線12が構成される。金属配線123は、同じ列に配列された感光セルに含まれる増幅トランジスタ104とリセットトランジスタ105との共通ドレインを接続する。この金属配線123によって、図1に示す電源ライン10の一部(列方向に伸延する部分)が実現される。なお、図7に示すレイアウトパターンでは、図4に示すレイアウトパターンに含まれる金属配線222、223に対応した金属配線は不要である。

[0.051]

活性領域100と、ポリシリコン配線111~113と、金属配線121~113とは、 半導体製造プロセスでは、それぞれ、異なる工程で形成される。これら3種類の領域ある いは配線を電気的に接続するため、図7に示すレイアウトパターンでは、各感光セルにつ いて、4個のコンタクトホール131~134が設けられている。

[0052]

本実施形態に係るセンサに含まれる感光セルのレイアウトパターン(図7)は、参考例に係るセンサに含まれる感光セルのレイアウトパターン(図4および図5)と比べて、以高を表別に係るレイアウトパターンでは、感光領域は長方形のような特徴を有している。を考例に係るレイアウトパターンでは、感光領域は、活性領域100の形状に合わせて、2個の長方形を連結した形状(破線・101と転送ゲート102とフローティング拡散層部103の一部とを含む第1のの残余の部分と増幅トランジスタ104とリセットトランジスタ103をと含む第2の領域(図7では金属配線122の右側にある領域)とに分割した場合、大まかに言えば、の残余の部分と増幅トランジスタ104とリセットトランジスタ103の領域と、感光セルムの第1の領域と、感光セルムと行方向に隣接する感光セルBの第1の領域との間に、感光セルムと列方向に隣接する感光セルを容易に接続することがで接する感光セルに含まれる増幅トランジスタ104のゲートとを容易に接続することができる。

[0053]

また、参考例に係るレイアウトパターンでは、図1に示す信号線17または信号線18の少なくとも一方が、ポリシリコン配線と金属配線の両方によって構成されている。これに対して、本実施形態に係るレイアウトパターンでは、信号線17はポリシリコン配線111のみによって構成され、信号線18はポリシリコン配線112のみによって構成される。したがって、信号線17と信号線18とは、同じ材料で形成されていると言える。また、フローティング拡散層部103は、同じ感光セルに含まれる転送ゲート102に接続されるポリシリコン配線111と、同じ感光セルに含まれる感光セルに含まれるリセットト

30

40

50

ランジスタ105に接続されるポリシリコン配線112との間に挟まれている。このように信号線17と転送ゲート102のゲート電極、信号線18とリセットトランジスタ105のゲート電極とが同じ材料で形成されているので、これらの信号線を配線するときに、コンタクトホールを設ける必要がなくなる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

#### [0054]

また、本実施形態に係るレイアウトパターンでは、上述したように、3種類の金属配線121~123が使用され、4個のコンタクトホール131~134が設けられる。コンタクトホール131は、フローティング拡散層部103と増幅トランジスタ104のゲートとを接続するために、フローティング拡散層部103に設けられる。コンタクトホール132は、増幅トランジスタ104とリセットトランジスタ105との共通ドレインを金属配線123(図1では電源ライン10)に接続するために、当該共通ドレインに設けられる。コンタクトホール133は、増幅トランジスタ104のソースを金属配線122(図1では垂直信号線12)に接続するために、当該ソースに設けられる。コンタクトホール134は、フローティング拡散層部103と増幅トランジスタ104のゲートとを接続するために、当該ゲートと同一の活性領域内に設けられる。本実施形態に係るレイアウトパターンでは、4個のコンタクトホール131~134が、ほぼー直線上に並んでいる。これにより、4個のコンタクトホール131~134が、ほぼー直線上に並んでいる。これにより、4個のコンタクトホールをレイアウトするために必要な面積を小さくすることができる。

#### [0055]

また、フローティング拡散層部103と増幅トランジスタ104のゲートとを接続する金属配線121と、金属配線122(図1では垂直信号線12)と、金属配線123(図1では電源ライン10)とは、いずれも金属配線である。このため、これら3種類の配線は、同一の金属配線層で形成することができる。これにより、これらの信号線を配線するときに、コンタクトホールを設ける必要がなくなる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

#### [0056]

また、金属配線122と金属配線123とは、感光セルが配列された感光領域に、互いに平行に配線されており、金属配線121は、金属配線122と金属配線123との間に挟まれている。より詳細には、フローティング拡散層部103と増幅トランジスタ104のゲートとを接続する金属配線121は、当該フローティング拡散層部103と同じ感光セルに含まれる増幅トランジスタ104に接続される金属配線122と、当該増幅トランジスタ104のドレインに接続される金属配線123との間に挟まれている。これにより、感光セルのレイアウトパターンが単純かつ規則的になる。したがって、レイアウトしたときの感光セルのサイズを小さくし、センサ全体の回路サイズを小さくすることができる。

## [0057]

このように、図6に示すセンサに含まれる感光セルを、図7に示すように規則的に無理なくレイアウトすることができる。図7に示すレイアウトパターンでは、図4および図5に示すレイアウトパターンのように、フォトダイオード上に金属配線が配線されることもない。以上のことから、本実施形態によれば、各感光セルを3個のトランジスタで構成するセンサについて、レイアウトに適した新たな回路構成を採用することにより、感光セルのサイズを小さくし、センサ全体のサイズを小さくすることができる。これにより、センサの歩留まりが向上し、センサのコストが低下するという効果を奏することができる。

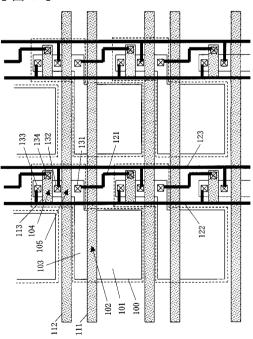

#### [0058]

図8は、図6に示す感光セルの他のレイアウトパターンを示す図である。図8に示すレイアウトパターンは、以下の点で、図7に示すレイアウトパターンと相違する。すなわち、図7に示すレイアウトパターンでは、各感光セルに含まれる4個のコンタクトホール131~134が、ほぼ一直線上に並んでいる。これに対して、図8に示すレイアウトパターンでは、各感光セルに含まれる4個のコンタクトホール131~134のうち、3個のコ

ンタクトホール 1 3 1 ~ 1 3 3 がほぼ一直線上に並んでおり、コンタクトホール 1 3 4 はこの直線外にある。センサをレイアウトする際に使用するデザインルールによっては、図8 に示すレイアウトを使用してもよい。

## [0059]

なお、本実施形態に係るセンサでは、感光セルに含まれるすべてのトランジスタが、 n チャンネル型MOSトランジスタであることが好ましい。その理由は、以下のとおりである。近年、ロジック回路の多くが C MOSを用いて製造されることに伴い、 MOS型固体撮像装置も C MOSを用いて製造される場合が多い。ロジック回路用の C MOSプロセスは複雑な多数の工程からなり、一部の工程をセンサの製造のためだけに変更することは極めて難しい。したがって、センサを製造するためには、製造プロセスの一工程に、センサに固有の工程を追加する必要がある。この場合、 p 型不純物であるボロンは質量が軽く動きやすいため、半導体内部で小さく作るのが難しいことを考慮すると、センサに固有の工程では、 N M O S のみを使用することが有利である。

## [0060]

以上に示すように、本発明の実施形態に係るセンサによれば、レイアウトに適した新規な 回路構成を採用することにより、感光セルのサイズを小さくし、センサ全体のサイズを小 さくすることができる。

#### 【図面の簡単な説明】

- 【図1】本発明の参考例に係るセンサの回路図

- 【図2】 本発明の実施形態に係るセンサの雑音抑圧回路の詳細を示す図

- 【図3】 本発明の実施形態に係るセンサの駆動方法を示すタイミングチャート

- 【図4】本発明の参考例に係るセンサのレイアウト図

- 【図5】本発明の参考例に係るセンサの他のレイアウト図

- 【図6】本発明の実施形態に係るセンサの回路図

- 【図7】本発明の実施形態に係るセンサのレイアウト図

- 【図8】本発明の実施形態に係るセンサの他のレイアウト図

- 【図9】従来のセンサの回路図

- 【図10】従来のセンサの駆動方法を示すタイミングチャート

## 【符号の説明】

- 1、101...フォトダイオード

- 2、102…転送ゲート

- 3、103...フローティング拡散層部

- 4、104…増幅トランジスタ

- 5、105…リセットトランジスタ

- 10…電源ライン

- 11…垂直シフトレジスタ

- 12...垂直信号線

- 13…負荷トランジスタ

- 14...雑音抑圧回路

- 15…水平トランジスタ

- 16…水平シフトレジスタ

- 100...活性領域

- 1 1 1 ~ 1 1 3 ... ポリシリコン配線

- 1 2 1 ~ 1 2 3 ... 金属配線

- 131~134...コンタクトホール

10

20

30

40

【図5】

【図6】

【図7】

【図8】

## フロントページの続き

## (56)参考文献 特開2003-046864(JP,A)

特開平11-274443(JP,A)

特開平11-195776(JP,A)

特開2002-190987(JP,A)

特開2001-94086(JP,A)

特開2001-189441(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 27/146

H04N 5/335