**UK Patent**

GE

(11) 2580740

$^{(13)}B$

45) Date of B Publication

03.11.2021

## (54) Title of the Invention: Graphics processing systems

(51) INT CL: G06T 15/00 (2011.01)

(21) Application No: 1914295.9

(22) Date of Filing: **03.10.2019**

(30) Priority Data:

(31) **16153359** (32) **05.10.2018** (33) **US**

(43) Date of A Publication 29.07.2020

(56) Documents Cited:

KR 201646293 A US 6421058 B2 US 5805868 A US 20050108469 A1

(58) Field of Search:

As for published application 2580740 A viz: INT CL **G06T** updated as appropriate

Additional Fields

Other: WPI, EPODOC

(72) Inventor(s):

Frode Heggelund Andreas Due Engh-Halstvedt Christian Vik Grøvdal

(73) Proprietor(s):

ARM Limited (Incorporated in the United Kingdom) 110 Fulbourn Road, Cambridge, Cambridgeshire, CB1 9NJ, United Kingdom

(74) Agent and/or Address for Service:

Dehns

St. Bride's House, 10 Salisbury Square, LONDON, EC4Y 8JD, United Kingdom

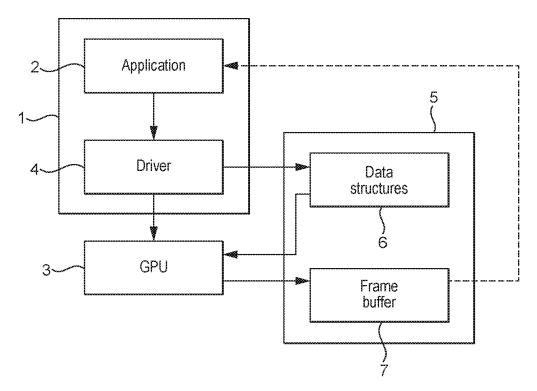

FIG. 1

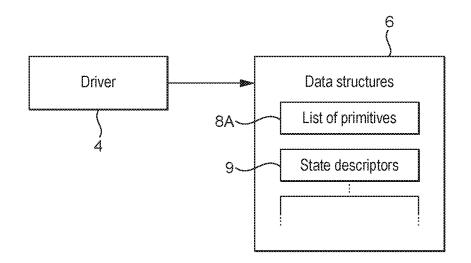

FIG. 2

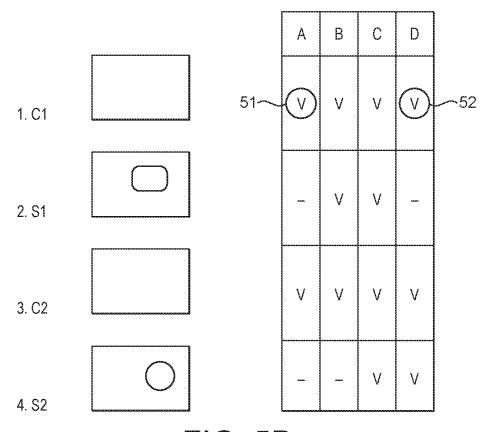

| < | 1. Clear stencil buffer 2. Draw stencil mask for object 1 3. Draw object 1 masked with S1 4. Clear stencil buffer 5. Draw stencil mask for object 2 | (C1)<br>(S1)<br>(O1)<br>(C2)<br>(S2) |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|   | 6. Draw object 2 masked with S2                                                                                                                     | (02)                                 |

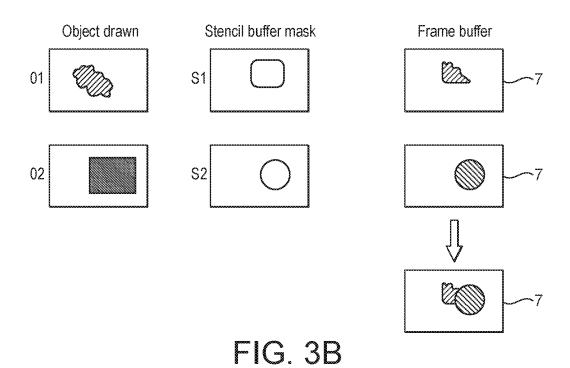

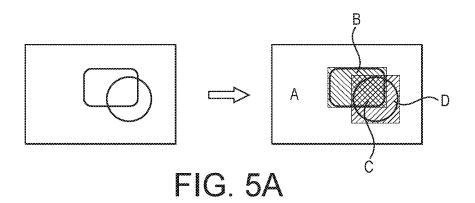

FIG. 3A

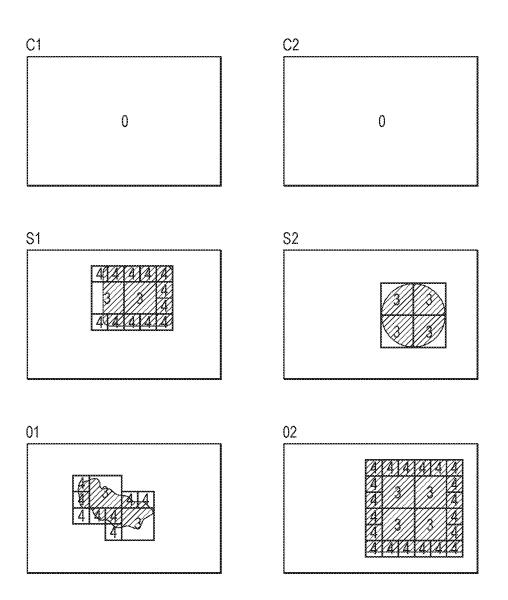

FIG. 4

FIG. 5B

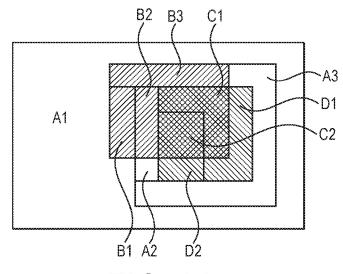

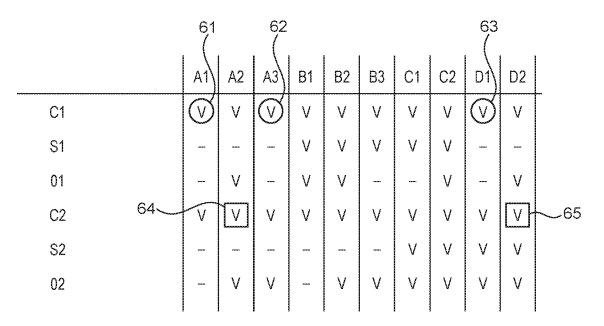

FIG. 6A

FIG. 6B

FIG. 7

## **Graphics Processing Systems**

5

The present invention relates to graphics processing systems, and in particular to tile-based graphics processing systems.

Graphics processing is normally carried out by first splitting the scene to be displayed into a number of similar basic components or "primitives", which primitives are then subjected to the desired graphics processing operations. The graphics "primitives" are usually in the form of simple polygons, such as triangles.

10

Each primitive is at this stage defined by and represented as a set of vertices. Each vertex for a primitive has associated with it a set of data (such as position, colour, texture and other attributes data) representing the vertex. This data is then used, e.g., when rasterising and rendering the primitive(s) to which the vertex relates in order to generate the desired render output of the graphics processing system.

Once primitives and their vertices have been generated and defined, they can be processed by the graphics processing system, in order, e.g., to display the frame.

20

15

This process basically involves determining which sampling points of an array of sampling points covering the output area to be processed are covered by a primitive, and then determining the appearance each sampling point should have (e.g. in terms of its colour, etc.) to represent the primitive at that sampling point. These processes are commonly referred to as rasterising and rendering, respectively.

25

The rasterising process determines the sample positions that should be used for a primitive (i.e. the (x, y) positions of the sample points to be used to represent the primitive in the output, e.g. scene to be displayed). This is typically done using the positions of the vertices of a primitive.

30

The rendering process then derives the data, such as red, green and blue (RGB) colour values and an "Alpha" (transparency) value, necessary to represent the primitive at the sample points (i.e. "shades" each sample point). This can involve, as is known in the art, applying textures, blending sample point data values, etc..

(In graphics literature, the term "rasterisation" is sometimes used to mean both primitive conversion to sample positions and rendering. However, herein "rasterisation" will be used to refer to converting primitive data to sampling point addresses only.)

5

These processes are typically carried out by testing sets of one, or of more than one, sampling point, and then generating for each set of sampling points found to include a sample point that is inside (covered by) the primitive in question (being tested), a discrete graphical entity usually referred to as a "fragment" on which the graphics processing operations (such as rendering) are carried out. Covered sampling points are thus, in effect, processed as fragments that will be used to render the primitive at the sampling points in question. The "fragments" are the graphical entities that pass through the rendering process (the rendering pipeline). Each fragment that is generated and processed may, e.g., represent a single sampling point or a set of plural sampling points, depending upon how the graphics processing system is configured.

15

20

10

(A "fragment" is therefore effectively (has associated with it) a set of primitive data as interpolated to a given output space sample point or points of a primitive. It may also include per-primitive and other state data that is required to shade the primitive at the sample point (fragment position) in question. Each graphics fragment may typically be the same size and location as a "pixel" of the output (e.g. output frame) (since as the pixels are the singularities in the final display, there may be a one-to-one mapping between the "fragments" the graphics processor operates on (renders) and the pixels of a display). However, it can be the case that there is not a one-to-one correspondence between a fragment and a display pixel, for example where particular forms of post-processing, such as downsampling, are carried out on the rendered image prior to displaying the final image.)

25

(It is also the case that as multiple fragments, e.g. from different overlapping primitives, at a given location may affect each other (e.g. due to transparency and/or blending), the final pixel output may depend upon plural or all fragments at that pixel location.)

30

(Correspondingly, there may be a one-to-one correspondence between the sampling points and the pixels of a display, but more typically there may not be a one-to-one correspondence between sampling points and display pixels, as downsampling may be carried out on the rendered sample values to generate the

output pixel values for displaying the final image. Similarly, where multiple sampling point values, e.g. from different overlapping primitives, at a given location affect each other (e.g. due to transparency and/or blending), the final pixel output will also depend upon plural overlapping sample values at that pixel location.)

5

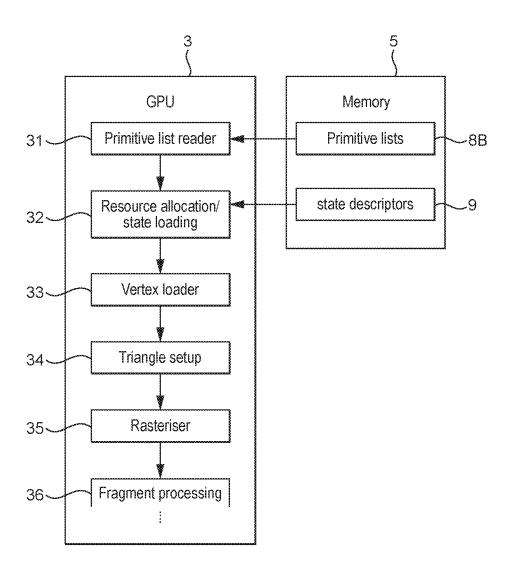

Figure 1 shows a typical computer graphics processing system, comprising a host processor (CPU) 1, a graphics processing unit (GPU) 3, and a memory 5 for storing data required by and/or generated by the host processor 1 and graphics processor 3.

10

When an application 2 that is executing on the host processor 1 requires graphics processing from the graphics processor 3, such as a frame to be displayed, the application 2 will send appropriate commands and data to a driver 4 for the graphics processor 3 that is running on the host processor 1.

15

The driver 4 will then send appropriate commands and data to the graphics processor 3 to cause it to generate the render output required by the application 2. The driver 4 sends commands and data to the graphics processor 3 by writing to data structures 6 in the memory 5, which data structures 6 are then read by the graphics processor 3.

20

The commands and data provided by the driver 4 will include commands to "draw" primitives to be rendered for the render output to be generated by the graphics processor 3, together with associated vertex data representing the vertices to be used for the primitives for the render output.

25

The commands sent to the graphics processor 3 cause the graphics processor 3 to read and process the vertex data to generate the render output. The graphics processor 3 will typically use the vertex data for a primitive to rasterise the primitive to one or more fragments each (potentially) applying to a region (area) of the render output. The fragments will then be rendered.

The completed render output (e.g. frame) may be written in a frame buffer 7 in the memory 5, from where it may be provided for display on a display device, such as a screen or printer.

30

Some graphics processing systems use so-called "tile-based" rendering. In tile-based rendering, the two-dimensional render output (i.e. the output of the rendering process, such as an output frame to be displayed) is rendered as a plurality of smaller area sub-regions, usually referred to as "tiles". The tiles are each rendered separately (typically one-after-another). The rendered tiles are then recombined to provide the complete render output (e.g. frame for display). In such

arrangements, the render output is typically divided (by area) into regularly-sized and shaped rendering tiles (they are usually e.g., squares or rectangles).

Other terms that are commonly used for "tiling" and "tile-based" rendering include "chunking" (the rendering tiles are referred to as "chunks") and "bucket" rendering. The terms "tile" and "tiling" will be used hereinafter for convenience, but it should be understood that these terms are intended to encompass all alternative and equivalent terms and techniques.

The advantage of such tile-based rendering is that primitives that do not appear in a given tile do not have to be processed for that tile, and therefore can be ignored when the tile is processed. This can allow the overall amount of graphics processing necessary for a given render output to be reduced.

The Applicants have recognised that it may be desirable to perform a graphics processing operation for the entirety of a render output (e.g. frame) being generated. For example, when performing a stencil operation it may be desirable to first clear the stencil buffer for the entire render output (frame).

The Applicants further believe that there remains scope for improvements to performing graphics processing operations for an entire render output, particularly in the case of tile-based graphics processing systems.

According to a first aspect of the present invention, there is provided a method of operating a graphics processing system comprising a graphics processor, the method comprising:

when it is desired to perform a graphics processing operation for the entirety of the area of a render output that is being generated by the graphics processor:

issuing, to the graphics processor, a command to draw a primitive that occupies the entirety of the area of the render output and to perform the graphics processing operation for the primitive, and in response to which command, the graphics processor will determine the vertices for the primitive from the area of the render output; and the graphics processor in response to the command:

determining the vertices for the primitive to be drawn in response to the command from the area of the render output;

drawing the primitive using the determined vertices so as to occupy the entirety of the area of the render output; and

performing the graphics processing operation defined for the command for the primitive.

20

5

10

15

25

30

According to a second aspect of the present invention, there is provided a graphics processing system comprising command issuing circuitry and a graphics processor;

wherein the command issuing circuitry is configured to:

5

when it is desired to perform a graphics processing operation for the entirety of the area of a render output that is being generated by the graphics processor:

issue, to the graphics processor, a command to draw a primitive that occupies the entirety of the area of the render output and to perform the graphics processing operation for the primitive, and in response to which command, the graphics processor will determine the vertices for the primitive from the area of the render output; and

the graphics processor is configured to, in response to a command to draw a primitive that occupies the entirety of the area of the render output and to perform a graphics processing operation for the primitive:

15

10

determine the vertices for the primitive to be drawn in response to the command from the area of the render output;

draw the primitive using the determined vertices so as to occupy the entirety of the area of the render output; and

perform the graphics processing operation defined for the command for the primitive.

20

The present invention is concerned with performing graphics processing operations for the entirety of the area of a render output being generated (rendered). Thus, the present invention is concerned with performing "full-frame" graphics processing operations, that affect the entire area of the frame being rendered.

25

In the present invention such a "full-frame" graphics processing operation is triggered by issuing a specific, "full-frame", command to the graphics processor which instructs the graphics processor to draw a primitive occupying (covering) the entirety of the area of the render output being rendered, a "full-frame" primitive, and to perform the graphics processing for the so-drawn "full-frame" primitive (and so for the entirety of the area of the render output (frame) being generated).

30

Furthermore, in the present invention, the graphics processor is configured to, in response to receiving the "full-frame" command, determine the vertices for the "full-frame" primitive from the area of the render output (frame), and draw the "full-frame" primitive using the so-determined vertices.

This means that the vertices for the "full-frame" primitive do not need to be (and are not) explicitly specified in the command and any associated data sent to the graphics processor, but are instead, in effect, "implicit" to the "full-frame" command itself.

5

Thus, in the present invention, instead of, e.g., the graphics processor determining vertices to use for the "full-frame" primitive from vertex data that is supplied to the graphics processor by a host processor, and that is, e.g., stored in, and read by the graphics processor from, memory, the graphics processor determines the vertices from (based on) the area of the render output.

10

Thus, for example, where the render output is a frame to be displayed, the graphics processor can determine the vertices for the "full-frame" primitive from the area of the frame. For example, where (as will typically be the case) the frame is a rectangular or square area, the vertices for the "full-frame" primitive may (be determined by the graphics processor to) correspond to the four corners of the frame.

15

The Applicants have recognised that since the vertices of a "full-frame" primitive occupying the entirety of the area of the render output (frame) being generated should correspond to the vertices (corners) of the render output (frame) being generated, a command to the graphics processor to draw such a "full-frame" primitive does not need to "explicitly" define or refer to vertex positions for the "full-frame" primitive in order for the graphics processor to be able to draw the "full-frame" primitive.

25

20

Thus, the "full-frame" command of the present invention does not refer explicitly to vertex data. Correspondingly, issuing the "full-frame" command to draw the "full-frame" primitive to the graphics processor should be (and preferably is) performed without writing vertex data associated with (and defining the vertices of) the "full-frame" primitive to (the) memory. Correspondingly, the graphics processor, in response to the "full-frame" command, determines the vertex positions for the "full-frame" primitive from (based on) the area of the render output (frame) rather than from explicitly indicated vertex data (read from (the) memory).

30

The present invention accordingly allows the performance of a graphics processing operation for the entirety of a render output without the need to read (and without reading) vertex data from memory. Accordingly, the requirements for reading and writing vertex data where a "full-frame" operation is to be performed

can be avoided, and moreover, generation of the vertex data in the first place can be avoided.

The present invention can thus reduce memory traffic (bandwidth) and usage, and accordingly power usage, when performing graphics processing operations for an entire render output. This is generally beneficial, but may be particularly advantageous for graphics processors that are to be used in low power and portable devices.

It will be appreciated, therefore, that the present invention provides an improved graphics processing system. Moreover, and as will be become apparent from the following, the present invention becomes particularly advantageous in the context of a tile-based graphics processing system.

The graphics processor may be any suitable and desired processor, e.g. and preferably a graphics processing unit (GPU). The graphics processor should be operable to process graphics processing commands (including the "full-frame" command) (and data) to generate (render) a render output (frame).

In a preferred embodiment, the graphics processor is a tile-based graphics processor (and the graphics processing system is a tile-based graphics processing system), and the render output (area) is accordingly divided into plural rendering tiles for rendering purposes (is processed on a tile-by-tile basis (by the graphics processor)).

The render output can be any suitable and desired render output to be generated (rendered) by the graphics processor. The render output to be generated (rendered) by the graphics processor may typically be a frame intended for display on a display device, such as a screen or printer, but may also, for example, comprise intermediate data intended for use in later rendering passes (also known as a "render to texture" output), etc..

The render output will typically be represented as a rectangular array of data elements (pixels), e.g. representing an image, wherein generating (rendering) the render output includes the graphics processor determining the colour (or greyscale) value to be used for each data element (pixel) of the render output (frame).

The tiles that the render output may be divided into for rendering purposes can be any suitable and desired such tiles. The size and shape of the rendering tiles may normally be dictated by the tile configuration that the graphics processor is configured to use and handle.

15

10

5

25

20

The rendering tiles are preferably all the same size and shape (i.e. regularly-sized and shaped tiles are preferably used), although this is not essential. The tiles are preferably square or rectangular. The size and number of tiles can be selected as desired. In a preferred arrangement, each tile is  $16 \times 16$ , or  $32 \times 32$  data elements (pixels) in size (with the render output then being divided into however many such tiles as are required for the render output size and shape that is being used).

Graphics processing commands (including the "full-frame" command) (and data) may be issued to the graphics processor in any suitable and desired manner.

10

5

In a preferred embodiment, the graphics processing system includes a, e.g. host, processor which issues graphics processing commands (including the "full-frame" command) (and data) to the graphics processor. The, e.g. host, processor can be any suitable and desired processor, such as and preferably a central processing unit (CPU), of the graphics processing system.

15

In a preferred embodiment, the, e.g. host, processor of the graphics processing system generates the graphics processing commands (including the "full-frame" command) (and data) for the graphics processor in response to instructions from an application executing on the processor. This is preferably done by a driver for the graphics processor that is executing on the, e.g. host, processor.

20

In a preferred embodiment, graphics processing commands (including the "full-frame" command) (and data) are written to memory, e.g. by the driver, and the graphics processor then reads the graphics processing commands (including the "full-frame" command) (and data) therefrom.

25

The memory can be any suitable and desired storage. The memory may be an on-chip memory (i.e. on the same chip as the, e.g. host, processor and/or CPU and/or the graphics processor) or it may be an external (main) memory (i.e. not on the same chip as the, e.g. host, processor and/or the graphics processor). Where the memory is an external memory, it may be connected to the, e.g. host, processor and/or to the graphics processor by a suitable interconnect.

30

The "full-frame" command is issued to the graphics processor when it is desired to perform a graphics processing operation for the entirety of the area of the render output. According to a preferred embodiment, the, e.g. host, processor (e.g. the driver for the graphics processor) recognises when a graphics processing operation for the entirety of the area of the render output is to be performed (e.g. when the application has so requested), and when it is recognised that a graphics

processing operation for the entirety of the area of the render output is to be performed, issues a "full-frame" command to the graphics processor accordingly.

The "full-frame" command that is issued to the graphics processor is a command that triggers the graphics processor to draw a primitive occupying the entirety of the area of the render output, and to perform a graphics processing operation for that "full-frame" primitive.

The "full-frame" command will typically be included in a sequence of plural graphics processing commands issued to the graphics processor to cause the graphics processor to generate (render) a desired render output (e.g. frame). The sequence of plural graphics processing commands issued to the graphics processor to generate (render) the render output may include one or more instances of a "full-frame" command.

Thus, in a preferred embodiment, a sequence of plural graphics processing commands that includes one or more instances of a "full-frame" command to draw (one or more instances of) a "full-frame" primitive occupying the entire area of the render output is issued to the graphics processor to generate (render) the render output, together with one or more other commands to draw one or more other primitives. The one or more other primitives will typically not occupy the entire area of the render output, but may each occupy some but not all of the area of the render output.

To facilitate the rendering operation, the graphics processing commands (and data) to be processed for the render output (including any "full-frame" commands) may be organised into distinct draw calls, wherein the draw calls for the render output are processed in turn to generate the render output.

As discussed above, the data associated with a (and each) command to draw a primitive issued to the graphics processor (other than a "full-frame" command in the manner of the present invention) will typically also include vertex data defining the vertices of the respective primitive to draw. In contrast, (each instance of) a "full-frame" command should not be (and preferably is not) associated with vertex data defining the vertices of the "full-frame" primitive.

The "full-frame" command of the present invention triggers the graphics processor to draw a "full-frame" primitive. The command can indicate this is any suitable and desired manner, such as by having a particular command identifier that the graphics processor interprets accordingly. For example, the driver for the

20

25

5

10

15

graphics processor can generate an appropriate "full-frame" job descriptor and issue that descriptor for processing by the graphics processor.

As well as indicating a "full-frame" primitive operation, the "full-frame" command also triggers the graphics processor to perform a desired graphics processing operation for the entirety of the render output (for the "full-frame" primitive).

This can be done in any suitable and desired manner. In a preferred embodiment, the graphics processing operation is indicated by configuration (state) data that is associated with the "full-frame" command, such as, and preferably, a draw call descriptor (DCD) for the draw call being processed.

Thus, in a preferred embodiment, a (and each) command is associated with configuration data (state data) for configuring the graphics processor to perform the desired graphics processing operation for the (respective) "full-frame" primitive.

Preferably, the configuration data (state data) (for a "full-frame" command) is issued to the graphics processor by the, e.g. host, processor (along with the respective command(s)), preferably by the e.g. driver for the graphics processor running on the, e.g. host, processor writing the configuration data (state data) to (the) memory, with the graphics processor then reading the configuration data (state data) from the memory.

The configuration data (state data) may be associated with a "full-frame" command in any suitable and desired manner. In a particularly preferred embodiment, (each instance of) the "full-frame" command comprises information indicative of the (respective) configuration data (state data) (stored in (the) memory). For example, and in a preferred embodiment, (each instance of) the "full-frame" command includes an index or pointer indicative of (respective) configuration data (state data) (e.g. stored in (the) memory).

Thus, in a preferred embodiment, the graphics processor reads the "full-frame" command (from (the) memory), then reads configuration data (state data) (from (the) memory) according to information indicative of the location of the configuration data (state data) included in the read "full-frame" command, and then performs the graphics processing operation for the "full-frame" primitive according to the read configuration data.

The "full-frame" primitive that the "full-frame" command instructs the graphics processor to draw occupies the entirety of the area of the render output (e.g. frame) (occupies the entirety of the area corresponding to each data element

15

10

5

20

25

30

(sampling position) of the render output), but can otherwise be any suitable and desired primitive. This may depend, e.g., upon the shape and configuration of the render output that is being generated.

Where (as will typically be the case) the render output (frame) corresponds to a rectangular (including square) area, the "full-frame" primitive will be (and is preferably) defined by four vertices: one vertex at each of the four corners of the rectangle (e.g. square). Other arrangements would be possible.

Drawing the "full-frame" primitive can be performed in any suitable and desired manner which includes the graphics processor determining the vertices for the "full-frame" primitive from the area of the render output (frame). The vertices for the "full-frame" primitive are determined by the graphics processor from the area (the (two-dimensional) size (and position)) of the render output (e.g. frame), but can otherwise be determined in any suitable and desired manner.

The graphics processor may explicitly determine the vertices for the "full-frame" primitive, e.g. by assessing the area (the (two-dimensional) size (and position)) of the render output (frame), and assigning vertices to appropriate extremities (vertices) of the render output, e.g. one vertex at each of the four corners of the render output. Where the render output is a frame to be displayed, the graphics processor may assess the area of the frame based on the defined area of the frame buffer that is storing the frame.

In a preferred embodiment, the graphics processor reads width and height values of the render output (target) (e.g. frame), preferably from a descriptor (state information) for the render output (e.g. a "Frame Buffer Descriptor"), e.g. stored in (the) memory, and then determines the vertices for the "full-frame" primitive (and draws the "full-frame" primitive) using the read width and height values. For example, and preferably, the graphics processor sets the coordinates of one vertex of the "full-frame" at one corner of the render output (frame), and determines the coordinates of other vertices of the "full-frame" primitive by adding or subtracting width and/or height values as appropriate.

Once the vertices for the "full-frame" primitive have been determined, the graphics processor draws the "full-frame" primitive and performs the graphics processing operation for the primitive. This can be done in any suitable and desired manner.

In a preferred embodiment, the "full-frame" primitive is first subjected to a triangle (primitive) set up operation (preferably in a triangle set up unit) that uses

10

5

15

20

25

30

the determined vertices for the full-frame primitive to generate barycentric functions for varying interpolation, and, optionally, and preferably, a set of edge functions for the primitive. In a preferred embodiment, both barycentric functions and edge functions are generated, although the edge functions need not be generated from the vertices, if desired, as because the "full-frame" primitive edge completely covers the render output, edge functions may not strictly be needed, or can be anything that covers the entire frame as the area outside the frame will not be subdivided anyway.

The triangle set up process (triangle set up unit) is preferably able to run a respective, different, triangle set up process (program) for each specific primitive type, so, accordingly, in a preferred embodiment, a distinct triangle set up process (program) is defined for a "full-frame" primitive that is executed in response to receiving a "full-frame" command (primitive) for processing.

The graphics processing and processor preferably then rasterises the "full-frame" primitive to graphics fragments, and then performs the graphics processing operation for the graphics fragments.

The (rasteriser of the) graphics processor, should, and preferably does rasterise the "full-frame" primitive to generate graphics fragments covering the entire of the area of the render output.

In a preferred embodiment, the (rasteriser of the) graphics processor is configured to perform so-called "hierarchical" rasterisation. Thus, in a preferred embodiment, the (rasteriser of the) graphics processor is configured to rasterise primitives, including a "full-frame" primitive, by testing larger patches of the render output to be generated against the primitive to be rasterised, to determine if the primitive covers (at least in part) any smaller patches of the render output that the larger patch encompasses. If the primitive does cover (at least in part) any smaller patches of the render output that the larger patch encompasses, then the larger patch is sub-divided into those smaller patches, and the process is then repeated for each smaller patch of the render output that was found to be at least partially covered by the primitive.

In this way, the rasterisation process operates to iteratively test the primitive against progressively smaller patches of the render output. A fragment or fragments is then generated for rendering for patches of sampling points found to be covered at least in part by the primitive in question.

20

15

5

10

30

In such an arrangement, a "full-frame" primitive of the present invention can be handled in the same way, but in a preferred embodiment, where hierarchical rasterisation is used, the rasteriser generates fragments for the "full frame" primitive in respect of the largest tested patch immediately without subdividing that patch into smaller patches (for testing) (since it is known that the "full frame" primitive will cover all of the render output area.

The graphics processing operation that the "full-frame" command instructs the graphics processor to perform for the "full-frame" primitive occupying the entirety of the area of the render output can be any suitable and desired graphics processing operation.

The graphics processing operation should be an operation that it is desired to perform for the entirety of the area of the render output. Thus, the graphics processing operation should be a graphics processing operation that has (or at least has the potential to have) an effect in respect of the entire area of the render output.

The graphics processing operation can (directly) affect (e.g. write to) data elements values of the render output. Alternatively, the graphics processing operation can affect data values associated with the render output, but which are not the render output itself, such as depth values and/or stencil values and/or other values that the graphics processor uses to generate the render output. (In such embodiments, the graphics processing operation accordingly will indirectly affect the render output.)

In a preferred embodiment, the graphics processing operation is a graphics processing operation for the entire area of the render output, which if repeated, would produce the same result (in respect of each data element of the entire render output) as performing only a single instance of the graphics processing operation. In other words, performing the graphics processing operation two or more times in a row would produce the same output result as performing the graphics processing operation only a single time.

In a preferred embodiment, the graphics processing operation is an operation that sets the value for each data element for a target area corresponding to the entire area of the render output to a respective selected, preferably predetermined, value. The graphics processing operation may set the data elements for the target area to different values to each other, or may set each data

30

5

10

15

20

element for the target area to the same value (as the value for each other data element).

The graphics processing operation may be an operation which sets data values for the render output. For example, and in an embodiment, the graphics processing operation may set each data element value of the render output, for example by writing (drawing) to each data element of the render output. In one such embodiment, the graphics processing operation is a so-called "blitting" operation, in which an image is drawn across the entire render output (frame). In another embodiment, the graphic processing operation is a "clear to image" or "clear to pattern" operation in which the entire render output (frame) is cleared to a background image or pattern.

Alternatively, and in an embodiment, the graphics processing operation sets data values associated with the render output, but which are not the render output itself, in respect of the entire area of the render output (for all data elements (positions) in the render output). For example, the graphics processing operation is preferably an operation which sets depth values and/or stencil values and/or other values that the graphics processor uses to generate the render output. (In such embodiments, the graphics processing operation accordingly will indirectly affect the render output.)

Thus, in an embodiment, the graphics processing operation that is performed for the "full-frame" primitive is an operation which affects (e.g. sets) depth and/or stencil and/or other values that the graphics processor uses to generate the render output for an area corresponding to the entire area of the render output.

In one such embodiment, the graphics processing operation is a "clear" operation in which depth and/or stencil values and/or other values that the graphics processor uses to generate the render output are cleared for an area corresponding to the entire area of the render output (e.g. each corresponding data element value is set to a data value which indicates that the data element is "cleared", such as zero or "NaN").

Thus, according to a preferred embodiment, the graphics processing system comprises a depth buffer for storing depth data and/or a stencil buffer for storing stencil data (in (the) memory). The depth buffer may store depth data for an area corresponding to the entirety of the area of the render output. Similarly, the stencil buffer may store stencil data for an area corresponding to the entirety of the area of

15

10

5

20

30

25

the render output. The graphics processing (e.g. clear) operation may accordingly affect (clear) the entirety of the depth and/or stencil buffer.

It will be appreciated that in a tile-based graphics processing system, the depth buffer may typically store depth data for an area corresponding to a single, or a few, rendering tiles (only). Similarly, the stencil buffer may typically store stencil data for an area corresponding to a single, or a few rendering tiles (only). In these embodiments, therefore, the graphics processing (e.g. clear) operation may affect (clear) the entirety of the depth and/or stencil buffer in respect of each rendering tile that the render output has been divided into.

10

5

In another preferred embodiment, the graphics processing operation is a background loading operation, in which a background image or pattern for the entire render output is loaded. In this case, it may be unnecessary to repeat loading the same background image or pattern in respect of some rendering tiles, for example in the case that "clear to background" graphics processing operations are being performed.

15

In another preferred embodiment, the graphics processing operation is a graphics processing operation for the entire area of the render output, which if repeated, would produce an undesired result. In other words, performing the graphics processing operation two or more times in a row would produce an undesired result, whereas performing the graphics processing operation only once produces a desired result.

20

25

For example, and preferably, the graphics processing operation is a "full-frame" filtering or other operation which it is desired to perform only once in respect of previously drawn data. For example, where some rendering tiles of a filtered render output are overwritten and others are not, it may be desired to re-apply the "full-frame" filter operation to the overwritten rendering tiles, but not to the other tiles to which the filter has already been applied.

30

As already mentioned, in a tile-based graphics processing system, the graphics processing operation is performed on a tile-by-tile basis. Thus the present invention, in this case will comprise the graphics processor processing the "full-frame" command (and performing the graphics processing operation) on a tile-by-tile basis.

UI

In a preferred embodiment, tile-by-tile processing is achieved by the use of so-called "primitive lists". Thus, in a preferred embodiment, the graphics processing system (e.g. the host processor and/or driver for the graphics processor and/or

graphics processor) is operable to arrange graphics processing commands (to draw primitives) (including the "full-frame" command) (and data) for processing (in respect of a (or each) draw call) into lists representing different sub-regions of the render output. Each such "primitive list" should indicate to the graphics processor the graphics processing commands (primitives) that are to be processed for a respective sub-region (e.g. for a respective draw call).

The individual primitive lists and the commands (primitives) in them can be arranged in any desired and suitable fashion and include any desired and suitable data. The commands (primitives) are preferably listed (ordered) in each primitive list in the desired processing order (first to last).

The primitive lists may be prepared for any suitable and desired sub-regions of the render output. The (and each) sub-region may, e.g., correspond to a single rendering tile, or to a set of plural rendering tiles, as desired.

In one embodiment, primitive lists are prepared for (only) a single set of sub-regions of the render output area, with each sub-region in the set of sub-regions corresponding to the same size and shape sub-region of the render output. In a preferred such arrangement, each sub-region corresponds to a respective one of the rendering tiles that the render output has been divided into. Thus, in this case, each rendering tile will have a primitive list that is exclusive to that rendering tile prepared for it.

In another preferred embodiment, primitive lists are prepared for two or more different sets of sub-regions of the render output, wherein each different set of sub-regions comprises different sized sub-regions to the sub-regions in the other sets of render output sub-regions for which primitive lists can be prepared.

In this case, each render output sub-region preferably comprises a group of one or more contiguous rendering tiles. Preferably, the render output sub-regions are rectangular (including squares). Preferably, the render output sub-regions in a given set of render output sub-regions all have the same size, and preferably also the same shape, as each other (i.e. preferably cover the same number of rendering tiles).

Each set of sub-regions preferably comprises sufficient sub-regions to cover (and covers) the entire render output (frame), i.e. encompass all the individual rendering tiles that the render output is divided into.

In a preferred embodiment, the sets of sub-regions comprise one set of sub-regions in which each sub-region of the set corresponds to a respective single

10

5

20

15

25

30

rendering tile (that are one (1x1) rendering tile in size), and one or more (and preferably more than one) sets of sub-regions in which each sub-region of the set corresponds to (encompasses) more than one rendering tile.

In a particularly preferred arrangement, the sets of render output sub-regions for which primitive lists can be prepared are arranged in a hierarchical fashion, i.e. such that the number of sub-regions in each set progressively changes as one moves through the sets of sub-regions. The sets of sub-regions are most preferably arranged such that they effectively form a pyramidal structure as one progresses up the sets. The render output area and/or number of rendering tiles included in the sub-regions preferably progressively increases as one moves up the sets of sub-regions from lowest set (which may, e.g., be, and in one preferred embodiment is, a base, single rendering tile sub-region set).

In a preferred embodiment, the sets of sub-regions layering hierarchy is arranged such that primitive lists can, in effect, be prepared for the entire render output, for the render output area divided into four sub-regions, for the render output area divided into 16 sub-regions, for the render output area divided into 64 sub-regions, and so on, e.g., and preferably, down to its division into the individual rendering tiles.

The graphics processing commands (primitives) (in respect of a (or each) draw call) may be arranged (e.g. by the driver for the graphics processor and/or the graphics processor) into primitive lists representing different sub-regions of the render output in any suitable and desired manner.

A (and each) command to draw a primitive will typically be placed into primitive lists by processing vertex data associated with (and defining the vertices of) the primitive to determine which sub-region(s) of the render output the primitive (potentially) falls within, e.g. using exact binning, or bounding box binning.

Thus, any "full-frame" commands to draw a "full-frame" primitive could be placed into primitive lists by (e.g. the driver) processing a set of any vertices defined for the "full-frame" primitive.

However, in a preferred embodiment, "full-frame" commands to draw a "full-frame" primitive are placed into primitive lists by the graphics processing system (e.g. the driver) recognising that the "full-frame" command applies to the entire area of the render output, and when a "full-frame" command that applies to the entire area of the render output is recognised, listing the "full-frame" command in one or more primitive lists corresponding to (that encompass) the entire area of the render

20

15

5

10

25

35

output (without reading (and processing) vertex data associated with (and defining the vertices of) the "full-frame" primitive). Thus, a "full-frame" command to draw a "full-frame" primitive is preferably listed in the primitive lists without needing to read (and without reading) (and process) vertex data associated with (and defining the vertices of) the "full-frame" primitive.

Thus, in the case where primitive lists are prepared for (only) a single set of sub-regions of the render output area, a "full-frame" command should be, and is preferably, included in each primitive list, i.e. each sub-region that the render output has been divided into.

10

15

5

In the case where primitive lists are prepared for plural sets of sub-regions (in a "hierarchical" fashion), a "full-frame" command is preferably listed at the "highest" level of the hierarchy and in all the lists at that level of the hierarchy (so as to encompass the entire render output area). For example, where one of the sets of sub-regions contains a single sub-region that encompasses the entire render output (which will accordingly be at the "highest" level of the hierarchy), a "full-frame" command is preferably listed (once) in the primitive list for that single sub-region encompassing the entire render output.

20

Once all the commands (including any "full-frame" commands) have been placed into primitive lists and primitive lists have been prepared for the render output sub-regions, the rendering tiles are preferably then processed and rendered, using the primitive lists to determine which commands (and primitives) need to be processed for each tile. Preferably, the graphics processor comprises a primitive list reading unit (circuit) configured to read the primitive lists and determine which commands to process for a rendering tile.

25

Preferably, each rendering tile is processed and rendered separately, i.e. the separate, individual tiles are rendered one-by-one (i.e. on at tile-by-tile basis). This rendering can be carried out in any desired manner, for example, by rendering the individual tiles in succession or in a parallel fashion, and storing the output for each tile, e.g., in the frame buffer (in (the) memory), e.g. for display.

30

35

Thus the present invention preferably comprises, once the primitive lists have been prepared, processing the commands (including any "full-frame" commands) to generate the render output, on a tile-by-tile basis, (the primitive list reading circuit) using the primitive lists to determine which commands to process for each tile to be rendered (to determine which primitives should be rendered for which tiles).

As will be discussed further below, the Applicants have recognised that when performing a graphics processing operation for the entire area of a render output that is being generated on a tile-by-tile basis, it may be the case that that processing operation performed in respect of one or more of the tiles that the render output has been divided into does not in fact need to be performed.

For example, and as will be discussed further below, in the case of a stencil buffer clear operation which clears the entire stencil buffer for the entirety of the area of the render output, it may not be necessary to perform the clear operation in respect of tiles for which no stencil buffer write operations have been performed since the previous stencil buffer clear operation was performed.

Thus, in a preferred embodiment, where the graphics processor is a tile-based graphics processor, the method comprises (and the graphics processor is correspondingly configured to) determining whether processing (executing) the "full-frame" command for a tile of the render output being processed would cause the graphics processor to perform an unnecessary graphics processing operation for that tile of the render output, and when it is determined that processing the "full-frame" command for the tile would cause the graphics processor to perform an unnecessary graphics processing operation for the tile, omitting processing (executing) the "full-frame" command for the tile. This is preferably done for plural, and preferably for each, of the rendering tiles that are being processed to generate the render output (that the render output has been divided into for rendering purposes).

Thus, according to an embodiment of the present invention, the graphics processor is a tile-based graphics processor, in which a render output of the graphics processor is divided into plural rendering tiles for rendering purposes, and each rendering tile is generated by the graphics processor processing graphics processing commands for the respective rendering tile; and the method comprises:

the graphics processor, when generating a rendering tile, in response to the graphics processing command to draw a primitive that occupies the entirety of the area of the render output and to perform a graphics processing operation for the primitive to be processed for the rendering tile:

15

10

5

20

25

determining whether it is unnecessary to process the graphics processing command for the rendering tile; and

when it is determined that processing the graphics processing command for the rendering tile is unnecessary, omitting processing the graphics processing command for the rendering tile.

According to an embodiment of the present invention, the graphics processor is a tile-based graphics processor, in which a render output of the graphics processor is divided into plural rendering tiles for rendering purposes; and the graphics processor comprises:

rendering circuitry configured to generate each rendering tile by processing graphics processing commands for the respective rendering tile; and

command omitting circuitry configured to, when the graphics processor is generating a rendering tile, in response to a graphics processing command to draw a primitive that occupies the entirety of the area of the render output and to perform a graphics processing operation for the primitive to be processed for the rendering tile:

determine whether it is unnecessary to process the graphics processing command for the rendering tile; and

when it is determined that processing the graphics processing command for the rendering tile is unnecessary, cause the rendering circuitry of the graphics processor to omit processing the graphics processing command for the rendering tile.

As will be appreciated by those skilled in the art, these embodiments of the present invention can and preferably do include one or more, and preferably all, of the preferred and optional features of the present invention described herein, as appropriate.

In these embodiments, it will be appreciated the (rendering circuit of the) graphics processor processes (renders) the "full-frame" command for the rendering tile when it is not determined that processing the "full-frame" command for the rendering tile is unnecessary (when it is determined that processing the "full-frame" command for the rendering tile is necessary).

In this case, the (rendering circuit of the) graphics processor, in respect of the rendering tile it is generating, draws the "full-frame" primitive and performs the "full-frame" graphics processing operation for the "full-

10

5

15

20

30

frame" primitive in the manner as described above. The graphics processor also determines the vertices to use for the "full-frame" primitive from the area of the render output as described above. Instances of a "full-frame" determined as being unnecessary to process (render) for a rendering tile, however, are not processed (rendered) by the (rendering circuit of the) graphics processor for the rendering tile.

Thus, a "full-frame" graphics processing command should be, and preferably is, processed (rendered) in respect of those rendering tiles where it is not determined (it is other than) to be unnecessary to do so (where it is determined to be necessary to do so), but not in respect of those rendering tiles where it is determined to be unnecessary to do so.

Thus, in these embodiments, the total number of graphics processing operations required to perform a graphics processing operation for the entire area of a render output in a tile-based graphics processing system may be reduced. These embodiments accordingly can reduce processing, and accordingly power usage, for graphics processing operations that are to be performed for an entire render output.

The graphics processing operation may be any suitable and desired "full-frame" graphics processing operation (e.g., and preferably, as described above). In a particularly preferred embodiment, the "full-frame" command is a command to draw a "full-frame" primitive and to perform a "full-frame" graphics processing operation for the "full-frame" primitive that sets each data element corresponding to the entire area of the render output to a respective selected, preferably predetermined value. The operation may set data element values for the render output (frame), or for data element values associated with the render output (such as depth and/or stencil values and/or other values).

Thus, the graphics processing operation is preferably an operation which, when repeated, produces the same result (in respect of each data element) for the entire render output, such as, and preferably, a "full-frame" clear operation, to e.g. clear depth values and/or stencil values for the entire render output.

Where the graphics processing operation is a graphics processing operation which if repeated, would produce an undesired result, or the same result as performing only a single instance of the graphics processing operation, the (command omitting circuit of the) graphics processor preferably identifies

15

5

10

20

25

appropriate opportunities to omit repeating the "full-frame" graphics processing operation for a rendering tile.

Thus, according to a preferred embodiment, determining whether it is unnecessary to process the "full-frame" graphics processing command for the rendering tile comprises determining whether processing the "full-frame" graphics processing command for the rendering tile would cause the graphics processor to unnecessarily or undesirably repeat the graphics processing operation for the rendering tile. In this case, it is determined that it is unnecessary to process the "full-frame" graphics processing command for the rendering tile when it is determined that processing the "full-frame" graphics processing command for the rendering tile would cause the graphics processor to unnecessarily or undesirably repeat the graphics processing operation for the rendering tile.

The Applicants have recognised that it may be undesirable or unnecessary to repeat a graphics processing command which affects each data element corresponding to the entire area of a render output in respect of one or more rendering tiles. For example, it may be unnecessary to repeatedly perform a clear operation to set each data element to a value indicating that the data element is "cleared", e.g. zero or "NaN" for a rendering tile.

For example, it may be desired to perform a series of plural stencil operations, each including a stencil clear operation for the entire area of the render output. In a tile-based graphics processing system, each such stencil operation will typically be performed by first clearing the entire stencil buffer for the particular tile that is being processed to a "cleared" state. Then, if the particular tile corresponds to an area of the render output that it is desired to stencil, writing stencil data to the stencil buffer.

If, however, the particular tile that is being processed does not correspond to an area of the render output that it is desired to stencil, then stencil data will not be written to the stencil buffer, and so the stencil buffer will remain unchanged and in the "cleared" state. In a subsequent stencil operation for that tile, therefore, clearing the stencil buffer will be unnecessary, since the stencil buffer will already be in the "cleared" state. Similarly, in the case of a depth clear operation for the entirety of the render output, or a "blitting" operation for the entirety of the render output, some tiles may undergo unnecessary graphics processing operations.

The Applicants have accordingly recognised that in a tile-based graphics processing system which is repeatedly performing a graphics processing operation

15

5

10

25

20

35

that, for example, sets each data element for a target area corresponding to the entire render output to a respective selected (predetermined) value (such as a stencil clear operation), repeatedly performing such an operation will have the same effect as performing the operation only once, for rendering tiles where other commands affecting the selected (predetermined) values are not processed by the graphics processor in between. Accordingly, some rendering tiles (e.g. those tiles which correspond to areas which it is not desired to stencil) may undergo a large number of unnecessary graphics processing operations (e.g. clear operations).

Accordingly, in the present embodiments, such unnecessary operations are identified and omitted such that the number of "full-frame" commands processed (executed) by the graphics processor may be significantly reduced.

The graphics processor, (the command omitting circuit) may determine whether processing the "full-frame" graphics processing command for the rendering tile would cause the graphics processor to unnecessarily or undesirably repeat the graphics processing operation for the rendering tile in any suitable and desired manner.

In a preferred embodiment, the graphics processor determines whether another (repeated) instance of the "full-frame" command is to be, or has been, processed for the rendering tile. (and can be omitted).

20

25

30

35

5

10

15

Thus, in a preferred embodiment, determining whether it is unnecessary to process the graphics processing command for the rendering tile comprises determining whether a repeated instance of the command is to be processed for the rendering tile, wherein the command and the repeated instance of the command are to be processed for the rendering tile without an intermediate command in response to which the graphics processor will set a data element for the rendering tile to a value other than the respective selected value; and determining that it is unnecessary to process the graphics processing command for the rendering tile when it is determined that a repeated instance of the command is to be processed for the rendering tile, wherein the command and the repeated instance of the command are to be processed for the rendering tile without an intermediate command in response to which the graphics processor will set a data element for the rendering tile to a value other than the respective selected value.

This operation may be achieved in any suitable and desired manner. In a preferred embodiment, the graphics processor comprises primitive list reading circuitry (e.g., and preferably, as described above) (wherein the primitive list reading

circuit comprises the command omitting circuit), and the primitive list reading circuit, in response to reading the "full-frame" graphics processing command in a primitive list for the rendering tile, determines whether a repeated instance of the "full-frame" command is to be processed for the rendering tile.

5

Preferably, the (command omitting circuit of the) graphics processor (e.g. primitive list reading circuit) does this by determining whether the next command to be processed for the rendering tile (which affects (writes to) data elements for the rendering tile) is a repeated instance of the "full-frame" command.

10

It is then determined that processing the "full-frame" graphics processing command for the rendering tile would cause the graphics processor to unnecessarily or undesirably repeat the graphics processing operation for the rendering tile (and so processing the "full-frame" command is unnecessary) when it is determined that the next command to be processed for the rendering tile (which affects (writes to) data elements for the rendering tile) is a repeated instance of the "full-frame" command.

15

Preferably, the graphics processor (e.g. primitive list reading circuit) only considers whether the next or previous command, immediately following or preceding the "full-frame" command, for the rendering tile is a repeated instance of the "full-frame" command (i.e. the graphics processor (e.g. primitive list reading circuit) preferably determines whether the "full-frame" command is one of consecutive repeated instances of the "full-frame" command to be processed for the rendering tile (in the primitive list(s) for the rendering tile).

25

20

However, it would also be possible for the graphics processor (e.g. primitive list reading circuit) to, in effect, "ignore" any commands in between repeated instances of the "full-frame" command which, e.g., and preferably, do not affect (e.g. write to) data elements for the rendering tile (and so, e.g., consider whether the next command to be processed for the rendering tile which does affect (e.g. write to) data elements for the rendering tile, is a repeated instance of the "full-frame" command).

30

35

(Similarly, it will be appreciated that the graphics processor (e.g. primitive list reading circuit) could determine that a "full-frame" graphics processing command is unnecessary to process when it is determined that the "full-frame" command itself is a repeated instance of an e.g. previous "full-frame" command.)

Thus, in a preferred embodiment, the graphics processor determines whether the "full-frame" graphics processing command is one of consecutive

(repeated) instances of the "full-frame" graphics processing command to be processed for the rendering tile; and determines that it is unnecessary to process the "full-frame" graphics processing command for the rendering tile when it is determined that the "full-frame" graphics processing command is one of consecutive (repeated) instances of the "full-frame" graphics processing command to be processed for the rendering tile.

5

10

15

20

25

30

The (command omitting circuit of the) primitive list reading circuit may identify that the next (or previous) command to be processed for the rendering tile is a repeated instance of the "full-frame" command in any suitable and desired manner.

In a preferred embodiment, the primitive list reading circuit, upon reading a "full-frame" command from a primitive list for the rendering tile, "holds back" the "full-frame" command, and before the graphics processor processes the "full-frame" command, the primitive list reading circuit determines the next command to be processed for the rendering tile (by reading the primitive list(s) for the rendering tile). The primitive list reading circuit then preferably determines whether the next command to be processed for the rendering tile is a second (repeated) instance of the "full-frame" command.

The (command omitting circuit of the) primitive list reading circuit may determine whether the next command to be processed for the rendering tile is a second (repeated) instance of the "full-frame" command in any suitable and desired manner.

In a preferred embodiment, the graphics processing system is configured such that each instance of the "full-frame" command comprises the same configuration data (state data) indicating data (e.g. an index or pointer) as each other instance of the "full-frame" command (indicative of the same configuration data (state data)).

Thus, in a particularly preferred embodiment, repeated instances of a "full-frame" command are identified by comparing configuration data (state data) indicating data (e.g. indexes or pointers, such as, and preferably, an index for a draw call descriptor) included in the commands. If the configuration data (state data) indicating data, e.g. (e.g. draw call descriptor) indexes, for the commands are the same, then the commands can be, and are preferably, taken to be the same (and vice-versa).

Thus, the (command omitting circuit of the) primitive list reading circuit preferably determines whether the next command to be processed for the rendering tile is a second (repeated) instance of the "full-frame" command by comparing the configuration data (state data) indicating data (e.g. indexes or pointers) included in the commands. In this case, it is determined that the next command to be processed for the rendering tile is a second (repeated) instance of the "full-frame" command when the configuration data (state data) indicating data (e.g. index or pointer) for the next command is the same as the configuration data (state data) indicating data (e.g. index or pointer) for the (first) "full-frame" command.

10

15

5

Then, when it is determined that the next command to be processed for the rendering tile is a second (repeated) instance of the "full-frame" command, the primitive list reading circuit preferably causes the graphics processor to omit processing one of the repeated instances of the "full-frame" command. This may be achieved by the primitive list reading circuit passing (only) a single instance of the "full-frame" command to subsequent stages of the graphics processor, such as the rasteriser, for processing. Preferably, the second (repeated) instance of the "full-frame" command, in effect, "overwrites" the first instance of the "full-frame" command.

20

In this way, identified repeated instances of a "full-frame" command may, in effect, be "coalesced" into a single "full-frame" command for subsequent processing by the e.g. rasteriser of the graphics processor, so that only a single instance of the repeated "full-frame" command (i.e. the "coalesced" command) is processed for the rendering tile.

25

If, however, the next command to be processed for the rendering tile is not a second instance of the "full-frame" command (if the next command is a different command), the primitive list reading circuit then preferably causes the graphics processor to process both the first instance of the "full-frame" command and (then) the next command. Thus, the primitive list reading circuit may pass both commands to subsequent stages of the graphics processor, such as the rasteriser, for processing.

30

Where the (rasteriser of the) graphics processor processes only a single instance of repeated instances of a "full-frame" command, then the graphics processor preferably loads configuration data (state data) for only a single instance of the "full-frame" command.

Thus, a particularly preferred embodiment comprises the graphics processor reading (loading) configuration data (state data) (from (the) memory) for only one of unnecessarily or undesirably repeated instances of a "full-frame" command, and then processing (only) a single instance of the "full-frame" command according to the read configuration data (state data).

Thus in the present embodiment, the primitive list reader is able to identify repeated instances of the "full-frame" command before the graphics processor reads (loads) configuration data (state data) for the repeated instances of the "full-frame" command. This can avoid the need to read (load) configuration data in respect of unnecessarily or undesirably repeated instances of the "full-frame" command, thereby reducing bandwidth requirements. Thus, the present embodiment can further reduce memory traffic (bandwidth) and usage, and accordingly power usage, for graphics processing operations for an entire render output.

15

10

5

Additionally or alternatively, in a preferred embodiment, the graphics processor reads configuration data (state data) (from (the) memory) according to information indicative (e.g. an index or pointer) of the (location of) configuration data (state data) included in a "full-frame" command, processes the "full-frame" command according to the read configuration data (state data), and then processes one or more other instances of the "full-frame" command according to the read configuration data (state data).

25

20

The Applicants have furthermore recognised that where plural instances of a "full-frame" command are to be processed, then it may be advantageous to only read configuration data (state data) associated with the "full-frame" command for (only) one of the plural instances of the "full-frame" command to be processed, rather than for each of the plural instances of the "full-frame" command to be processed.

30

This means that the overall bandwidth consumed can be reduced as compared to reading configuration data (state data) for each of the plural instances of the "full-frame" command. Thus, the present embodiment can further reduce memory traffic (bandwidth) and usage, and accordingly power usage, for graphics processing operations for an entire render output.

Additionally or alternatively, in a preferred embodiment, where the "full-frame" command is a command to draw a "full-frame" primitive and to perform a "full-frame" graphics processing operation for the "full-frame" primitive that sets

each data element corresponding to the entire area of the render output to a respective selected, preferably predetermined value, determining whether it is unnecessary to process the "full-frame" graphics processing command for the rendering tile comprises determining whether each data element for the rendering tile is (already) set to the respective selected value; and determining that it is unnecessary to process the "full-frame" command for the rendering tile when it is determined that each data element for the rendering tile is (already) set to the respective selected value.

This operation may be achieved as desired. However, in a preferred embodiment, the graphics processor comprises a rasteriser (e.g., and preferably, as described above) (and the rasteriser comprises the command omitting circuit), and the rasteriser, before rasterising (processing) the "full-frame" primitive for the rendering tile, determines whether each data element for the rendering tile is (already) set to the respective selected value. The rasteriser then omits processing (omits rasterising (generating fragments for)) the "full-frame" primitive for the rendering tile when it is determined that each data element for the rendering tile is (already) set to the respective selected value.

For example, and in a preferred embodiment, where the graphics processing operation is a "full-frame" clear operation to be performed for a "full-frame" primitive in respect of a rendering tile, the rasteriser determines whether the rendering tile is already cleared, and if the rendering tile is already cleared, omits rasterising the "full-frame" primitive for the rendering tile.

In a particularly preferred embodiment, the rasteriser is configured to perform so-called "hierarchical" rasterisation (e.g., and preferably, as described above), and the rasteriser of the graphics processor is configured to, in response to the "full-frame" command to draw the "full-frame" primitive covering the entire area of the render output to be processed for the rendering tile, test the "full-frame" primitive against a patch covering the entire area of the render output being generated to determine if each data element for the rendering tile is (already) set to the respective selected value. If it is determined that each data element for the rendering tile is (already) set to the respective selected value, then the patch is preferably not subdivided, and preferably no fragments are generated for the patch.

In this way, fragments are not generated for the "full-frame" primitive in respect of the rendering tile, and so processing (rendering) of the "full-frame" command is stopped ("skipped over") for that rendering tile.

35

5

10

15

20

25

In another preferred embodiment, where the "full-frame" command is a command to perform a "full-frame" clear operation (to clear, e.g., stencil values and/or depth values), the (command omitting circuit of the (primitive list reading circuit of the)) graphics processor identifies whether any other graphics processing commands (in the primitive list(s)) are to be processed for the rendering tile following the "full-frame" command which could (or will) affect (e.g. draw to) data values corresponding to the rendering tile.

5

10

15

20

25

30

35

Thus, in this case, determining whether it is unnecessary to process the "full-frame" clear command for the rendering tile preferably comprises determining whether other commands (in the primitive list(s)) are to be processed for the rendering tile following the "full-frame" clear command (which e.g. affect (draw to) or use data values corresponding to the rendering tile).

In this case, it is determined that processing the "full-frame" clear command for the rendering tile is unnecessary when it is determined that no other commands following the "full-frame" clear command (which affect (draw to) or use data values corresponding to the rendering tile) are to be processed for the rendering tile.

The Applicants have recognised that in the case of a "full-frame" clear operation, it may not be necessary to perform the clear operation for a rendering tile if there are no other commands to process for that rendering tile following the clear operation to generate the render output and/or if the data values for the rendering tile are not subsequently used.

Although the present invention has been described above with particular reference to a single rendering tile, it will be appreciated that the present invention can be, and preferably is, applied to plural and preferably to each rendering tile that is generated by the graphics processor to form the render output (frame). Similarly, although the present invention has been described above with particular reference to generating a single render out (e.g. frame), it will be appreciated that the present invention can be, and preferably is, applied to each of plural render outputs (frames) in a sequence of render outputs (frames) being generated by the graphics processor.

The present invention can be implemented in any suitable system, such as a suitably configured micro-processor based system. In an embodiment, the present invention is implemented in a computer and/or micro-processor based system. The present invention is preferably implemented in a portable device, such as, and preferably, a mobile phone or tablet.

The present invention is applicable to any form or configuration of graphics processor, such as graphics processors having a "pipelined" arrangement (in which case the graphics processor comprises a rendering pipeline).

The graphics processing system and/or graphics processor may also comprise, and/or be in communication and/or associated with, one or more memories and/or memory devices that store the data described herein, and/or the output data generated by the graphics processing system or graphics processor, and/or software for performing the processes described herein.

5

10

15

20

25

30

The various functions of the present invention can be carried out in any desired and suitable manner. For example, the functions of the present invention can be implemented in hardware or software, as desired. Thus, for example, unless otherwise indicated, the various functional elements, stages, and "means" of the present invention may comprise a suitable processor or processors, controller or controllers, functional units, circuitry, circuits, processing logic, microprocessor arrangements, etc., that are operable to perform the various functions, etc., such as appropriately dedicated hardware elements (processing circuit(s)/circuitry) and/or programmable hardware elements (processing circuit(s)/circuitry) that can be programmed to operate in the desired manner.

It should also be noted here that, as will be appreciated by those skilled in the art, the various functions, etc., of the present invention may be duplicated and/or carried out in parallel on a given processor. Equally, the various processing stages may share processing circuits/circuitry, etc., if desired.

Furthermore, any one or more or all of the processing stages of the present invention may be embodied as processing stage circuit/circuitry, e.g., in the form of one or more fixed-function units (hardware) (processing circuits), and/or in the form of programmable processing circuits that can be programmed to perform the desired operation. Equally, any one or more of the processing stages and processing stage circuits/circuitry of the present invention may be provided as a separate circuit element to any one or more of the other processing stages or processing stage circuits, and/or any one or more or all of the processing stages and processing stage circuits may be at least partially formed of shared processing circuits.

Subject to any hardware necessary to carry out the specific functions discussed above, the components of the graphics processing system can otherwise

include any one or more or all of the usual functional units, etc., that such components include.