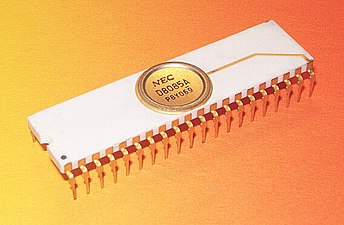

Intel 8085

An Intel P8085AH-2 processor variant with black plastic and silver pins | |

| General information | |

|---|---|

| Launched | March 1976 |

| Discontinued | 2000[1] |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 3, 5 and 6 MHz |

| Data width | 8 bits |

| Address width | 16 bits |

| Architecture and classification | |

| Technology node | 3 μm |

| Instruction set | 8085 |

| Physical specifications | |

| Transistors |

|

| Package |

|

| Socket | |

| History | |

| Predecessor | Intel 8080 |

| Successor | Intel 8086 |

| Support status | |

| Unsupported | |

The Intel 8085 ("eighty-eighty-five") is an 8-bit microprocessor produced by Intel and introduced in March 1976.[2] It is the last 8-bit microprocessor developed by Intel.

It is software-binary compatible with the more-famous Intel 8080 with only two minor instructions officially ( 10 more undocumented instructions exist, see undocumented instructions) added to support its added interrupt and serial input/output features. However, it requires less support circuitry, allowing simpler and less expensive microcomputer systems to be built.

The "5" in the part number highlighted the fact that the 8085 uses a single +5-volt (V) power supply by using depletion-mode transistors, rather than requiring the +5 V, −5 V and +12 V supplies needed by the 8080. This capability matched that of the competing Z80, a popular 8080-derived CPU introduced the year before. These processors could be used in computers running the CP/M operating system.

The 8085 is supplied in a 40-pin DIP package. To maximise the functions on the available pins, the 8085 uses a multiplexed address/data (AD0-AD7) bus. However, an 8085 circuit requires an 8-bit address latch, so Intel manufactured several support chips with an address latch built in. These include the 8755, with an address latch, 2 KB of EPROM and 16 I/O pins, and the 8155 with 256 bytes of RAM, 22 I/O pins and a 14-bit programmable timer/counter. The multiplexed address/data bus reduced the number of PCB tracks between the 8085 and such memory and I/O chips.

Both the 8080 and the 8085 were eclipsed by the Zilog Z80 for desktop computers, which took over most of the CP/M computer market, as well as a share of the booming home-computer market in the early-to-mid-1980s.

The 8085 had a long life as a controller, no doubt thanks to its built-in serial I/O and five prioritized interrupts, arguably microcontroller-like features that the Z80 CPU did not have. Once designed into such products as the DECtape II controller and the VT102 video terminal in the late 1970s, the 8085 served for new production throughout the lifetime of those products. This was typically longer than the product life of desktop computers.

Description

[edit]

The 8085 is a conventional von Neumann design based on the Intel 8080. Unlike the 8080 it does not multiplex state signals onto the data bus, but the 8-bit data bus is instead multiplexed with the lower eight bits of the 16-bit address bus to limit the number of pins to 40. State signals are provided by dedicated bus control signal pins and two dedicated bus state ID pins named S0 and S1. Pin 40 is used for the power supply (+5 V) and pin 20 for ground. Pin 39 is used as the Hold pin.

The Intel 8085 processor was designed using nMOS circuitry, with later "H" versions implemented in Intel's enhanced nMOS process known as HMOS II ("High-performance MOS"), which was originally developed for fast static RAM products.[3] Unlike the 8080, the 8085 requires only a single 5-volt power supply, similar to its competing processors. The 8085 contains approximately 6,500 transistors.[4]

The 8085 incorporates the functions of the 8224 (clock generator) and the 8228 (system controller) on chip, increasing the level of integration. A downside compared to similar contemporary designs (such as the Z80) is the fact that the buses require demultiplexing; however, address latches in the Intel 8155, 8355, and 8755 memory chips allow a direct interface, so an 8085 along with these chips is almost a complete system.

The 8085 has extensions to support new interrupts, with three maskable vectored interrupts (RST 7.5, RST 6.5 and RST 5.5), one non-maskable interrupt (TRAP), and one externally serviced interrupt (INTR). Each of these five interrupts has a separate pin on the processor, a feature which permits simple systems to avoid the cost of a separate interrupt controller. The RST 7.5 interrupt is edge triggered (latched), while RST 5.5 and 6.5 are level-sensitive. All interrupts except TRAP are enabled by the EI instruction and disabled by the DI instruction. In addition, the SIM (Set Interrupt Mask) and RIM (Read Interrupt Mask) instructions, the only official instructions of the 8085 that are not from the 8080 design, allow each of the three maskable RST interrupts to be individually masked. All three are masked after a normal CPU reset. SIM and RIM also allow the global interrupt mask state and the three independent RST interrupt mask states to be read, the pending-interrupt states of those same three interrupts to be read, the RST 7.5 trigger-latch flip-flop to be reset (cancelling the pending interrupt without servicing it), and serial data to be sent and received via the SOD and SID pins, respectively, all under program control and independently of each other.

SIM and RIM each execute in four clock cycles (T states), making it possible to sample SID and/or toggle SOD considerably faster than it is possible to toggle or sample a signal via any I/O or memory-mapped port, e.g. one of the port of an 8155. (In this way, SID can be compared to the SO ["Set Overflow"] pin of the 6502 CPU contemporary to the 8085.)

Like the 8080, the 8085 can accommodate slower memories through externally generated wait states (pin 35, READY), and has provisions for Direct Memory Access (DMA) using HOLD and HLDA signals (pins 39 and 38). An improvement over the 8080 is that the 8085 can itself drive a piezoelectric crystal directly connected to it, and a built-in clock generator generates the internal high-amplitude two-phase clock signals at half the crystal frequency (a 6.14 MHz crystal would yield a 3.07 MHz clock, for instance). The internal clock is available on an output pin, to drive peripheral devices or other CPUs in lock-step synchrony with the CPU from which the signal is output. The 8085 can also be clocked by an external oscillator (making it feasible to use the 8085 in synchronous multi-processor systems using a system-wide common clock for all CPUs, or to synchronize the CPU to an external time reference such as that from a video source or a high-precision time reference).

The 8085 is a binary compatible follow-up on the 8080. It supports the complete instruction set of the 8080, with exactly the same instruction behavior, including all effects on the CPU flags (except for the AND/ANI operation, which sets the AC flag differently).[5] This means that the vast majority of object code (any program image in ROM or RAM) that runs successfully on the 8080 can run directly on the 8085 without translation or modification. (Exceptions include timing-critical code and code that is sensitive to the aforementioned difference in the AC flag setting or differences in undocumented CPU behavior.) 8085 instruction timings differ slightly from the 8080—some 8-bit operations, including INR, DCR, and the heavily used MOV r,r' instruction, are one clock cycle faster, but instructions that involve 16-bit operations, including stack operations (which increment or decrement the 16-bit SP register) generally one cycle slower. It is of course possible that the actual 8080 and/or 8085 differs from the published specifications, especially in subtle details. (The same is not true of the Z80.) As mentioned already, only the SIM and RIM instructions were officially added (see undocumented instructions) to the 8085.[nb 1]

Programming model

[edit]

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

The processor has seven 8-bit registers accessible to the programmer, named A, B, C, D, E, H, and L, where A is also known as the accumulator. The other six registers can be used as independent byte-registers or as three 16-bit register pairs, BC, DE, and HL (or B, D, H, as referred to in Intel documents), depending on the particular instruction.

Some instructions use HL as a (limited) 16-bit accumulator. As in the 8080, the contents of the memory address pointed to by HL can be accessed as pseudo register M. It also has a 16-bit program counter and a 16-bit stack pointer to memory (replacing the 8008's internal stack). Instructions such as PUSH PSW, POP PSW affect the Program Status Word (accumulator and flags). The accumulator stores the results of arithmetic and logical operations, and the flags register bits (sign, zero, auxiliary carry, parity, and carry flags) are set or cleared according to the results of these operations. The sign flag is set if the result has a negative sign (i.e. it is set if bit 7 of the accumulator is set). The auxiliary or half carry flag is set if a carryover from bit 3 to bit 4 occurred. The parity flag is set to 1 if the parity (number of 1-bits) of the accumulator is even; if odd, it is cleared. The zero flag is set if the result of the operation was 0. Lastly, the carry flag is set if a carryover from bit 7 of the accumulator (the MSB) occurred.

Commands/instructions

[edit]As in many other 8-bit processors, all instructions are encoded in a single byte (including register-numbers, but excluding immediate data), for simplicity. Some of them are followed by one or two bytes of data, which can be an immediate operand, a memory address, or a port number. A NOP "no operation" instruction exists, but does not modify any of the registers or flags. Like larger processors, it has CALL and RET instructions for multi-level procedure calls and returns (which can be conditionally executed, like jumps) and instructions to save and restore any 16-bit register-pair on the machine stack. There are also eight one-byte call instructions (RST) for subroutines located at the fixed addresses 00h, 08h, 10h,...,38h. These are intended to be supplied by external hardware in order to invoke a corresponding interrupt-service routine, but are also often employed as fast system calls. One sophisticated instruction is XTHL, which is used for exchanging the register pair HL with the value stored at the address indicated by the stack pointer.

8-bit instructions

[edit]All two-operand 8-bit arithmetic and logical (ALU) operations work on the 8-bit accumulator (the A register). For two-operand 8-bit operations, the other operand can be either an immediate value, another 8-bit register, or a memory cell addressed by the 16-bit register pair HL. The only 8-bit ALU operations that can have a destination other than the accumulator are the unary incrementation or decrementation instructions, which can operate on any 8-bit register or on memory addressed by HL, as for two-operand 8-bit operations. Direct copying is supported between any two 8-bit registers and between any 8-bit register and an HL-addressed memory cell, using the MOV instruction. An immediate value can also be moved into any of the foregoing destinations, using the MVI instruction. Due to the regular encoding of the MOV instruction (using nearly a quarter of the entire opcode space) there are redundant codes to copy a register into itself (MOV B,B, for instance), which are of little use, except for delays.[nb 2] However, what would have been a copy from the HL-addressed cell into itself (i.e., MOV M,M) instead encodes the HLT instruction, halting execution until an external reset or unmasked interrupt occurs.[nb 3]

16-bit operations

[edit]Although the 8085 is an 8-bit processor, it has some 16-bit operations. Any of the three 16-bit register pairs (BC, DE, HL) or SP can be loaded with an immediate 16-bit value (using LXI), incremented or decremented (using INX and DCX), or added to HL (using DAD). LHLD loads HL from directly addressed memory and SHLD stores HL likewise. The XCHG operation exchanges the values of HL and DE. XTHL exchanges last item pushed on stack with HL. Adding HL to itself performs a 16-bit arithmetic left shift with one instruction. The only 16-bit instruction that affects any flag is DAD (adding BC, DE, HL, or SP to HL), which updates the carry flag to facilitate 24-bit or larger additions and left shifts. Adding the stack pointer to HL is useful for indexing variables in (recursive) stack frames. A stack frame can be allocated using DAD SP and SPHL, and a branch to a computed pointer can be done with PCHL. These abilities make it feasible to compile languages such as PL/M, Pascal, or C with 16-bit variables and produce 8085 machine code. Subtraction and bitwise logical operations on 16 bits is done in 8-bit steps. Operations that have to be implemented by program code (subroutine libraries) include comparisons of signed integers as well as multiplication and division.

Undocumented instructions

[edit]A number of undocumented instructions and flags were discovered by two software engineers, Wolfgang Dehnhardt and Villy M. Sorensen in the process of developing an 8085 assembler. These instructions use 16-bit operands and include indirect loading and storing of a word, a subtraction, a shift, a rotate, and offset operations.[6]

By the time 8085 was designed but not yet announced, many designers found it to be inferior to the competing products already on the market. A next generation 8086 CPU was already in development. Intel made a last minute decision to leave 10 out of 12 new 8085 instructions undocumented to speed up and simplify the design of the upcoming 8086 CPU.[7]

Input/output scheme

[edit]The 8085 supports both port-mapped and memory-mapped I/O. It supports up to 256 input/output (I/O) ports via dedicated Input/Output instructions, with port addresses as operands. Port-mapped IO can be an advantage on processors with limited address space. During a port-mapped I/O bus cycle, the 8-bit I/O address is output by the CPU on both the lower and upper halves of the 16-bit address bus.

Devices designed for memory mapped I/O can also be accessed by using the LDA (load accumulator from a 16-bit address) and STA (store accumulator at a 16-bit address specified) instructions, or any other instructions that have memory operands. A memory-mapped IO transfer cycle appears on the bus as a normal memory access cycle.

Development system

[edit]Intel produced a series of development systems for the 8080 and 8085, known as the MDS-80 Microprocessor System. The original development system had an 8080 processor. Later 8085 and 8086 support was added including ICE (in-circuit emulators). It is a large and heavy desktop box, about a 20" cube (in the Intel corporate blue color) which includes a CPU, monitor, and a single 8-inch floppy disk drive. Later an external box was made available with two more floppy drives. It runs the ISIS operating system and can also operate an emulator pod and an external EPROM programmer. This unit uses the Multibus card cage which was intended just for the development system. A surprising number of spare card cages and processors were being sold, leading to the development of the Multibus as a separate product.

The later iPDS is a portable unit, about 8" × 16" × 20", with a handle. It has a small green screen, a keyboard built into the top, a 5¼ inch floppy disk drive, and runs the ISIS-II operating system. It can also accept a second 8085 processor, allowing a limited form of multi-processor operation where both processors run simultaneously and independently. The screen and keyboard can be switched between them, allowing programs to be assembled on one processor (large programs took a while) while files are edited in the other. It has a bubble memory option and various programming modules, including EPROM, and Intel 8048 and 8051 programming modules which are plugged into the side, replacing stand-alone device programmers. In addition to an 8080/8085 assembler, Intel produced a number of compilers including those for PL/M-80 and Pascal, and a set of tools for linking and statically locating programs to enable them to be burned into EPROMs and used in embedded systems.

A lower cost "MCS-85 System Design Kit" (SDK-85) board contains an 8085 CPU, an 8355 ROM containing a debugging monitor program, an 8155 RAM and 22 I/O ports, an 8279 hex keypad and 8-digit 7-segment LED, and a TTY (Teletype) 20 mA current loop serial interface. Pads are available for one more 2K×8 8755 EPROM, and another 256 byte RAM 8155 I/O Timer/Counter can be optionally added. All data, control, and address signals are available on dual pin headers, and a large prototyping area is provided.

List of Intel 8085 Models

[edit]| Model Number | Technology Process | Process Node | Clock Speed | Temperature Range | Current Rating | Power Tolerance | Package | Date of Release | Price USD[list 1] |

|---|---|---|---|---|---|---|---|---|---|

| 8085A[3] | NMOS | 3 micron | 3 MHz | 170 mA | ± 5% | $6.25 | |||

| P8085AH[3] | HMOS II | 2 micron | 3 MHz | 135 mA | ± 10% | Plastic | July/August 1981 | $4.40 | |

| 8085-2[8] | 5 MHz | ||||||||

| 8085A-2[3] | NMOS | 3 micron | 5 MHz | 170 mA | ± 5% | $8.75 | |||

| P8085AH-2[3] | HMOS II | 2 micron | 5 MHz | 135 mA | ± 10% | Plastic | July/August 1981 | $5.80 | |

| P8085AH-1[3] | HMOS II | 2 micron | 6 MHz | Plastic | July/August 1981 | $12.45 | |||

| ID8085[9] | 3 MHz | Industrial | March/April 1979 | $38.75 | |||||

| M8085A[10] | 3 MHz | Military | March/April 1979 | $110.00 |

- ^ In quantities of 100 and up

Applications

[edit]The 8085 processor was used in a few early personal computers, for example, the TRS-80 Model 100 line used an OKI manufactured 80C85 (MSM80C85ARS). The CMOS version 80C85 of the NMOS/HMOS 8085 processor has several manufacturers. In the Soviet Union, an 80C85 clone was developed under the designation IM1821VM85A (Russian: ИМ1821ВМ85А [ru]) which in[update] 2016 was still in production.[11] Some manufacturers provide variants with additional functions such as additional instructions.[citation needed]

The radiation hardened version of the 8085 has been in on-board instrument data processors for several NASA and ESA space physics missions in the 1990s and early 2000s, including CRRES, Polar, FAST, Cluster, HESSI, the Sojourner Mars Rover,[12] and THEMIS. The Swiss company SAIA used the 8085 and the 8085–2 as the CPUs of their PCA1 line of programmable logic controllers during the 1980s.

Pro-Log Corp. put the 8085 and supporting hardware on an STD Bus format card containing CPU, RAM, sockets for ROM/EPROM, I/O and external bus interfaces. The included Instruction Set Reference Card uses entirely different mnemonics for the Intel 8085 CPU. The product was a direct competitor to Intel's Multibus card offerings.

- Intel 8085 second sources

-

AMD Am9085

-

Mitsubishi M5L8085

-

NZPP Novosibirsk IM1821VM85 (Soviet Union)

-

OKI M80C85

-

Siemens SAB8085

-

Toshiba TMP8085

MCS-85 family

[edit]The 8085 CPU is one part of a family of chips developed by Intel for building a complete system. Many of these support chips were also used with other processors. The original IBM PC based on the Intel 8088 processor used several of these chips; the equivalent functions today are provided by VLSI chips, namely the "Southbridge" chips.

- 8085 – CPU

- 8231 – Arithmetic Processing Unit

- 8232 – Floating-Point Processor

- 8205 – 1 of 8 Binary Decoder

Static RAM

[edit]- 8155 – 2K-bit static MOS RAM with 3 I/O Ports and Timer. The industrial version of ID8155 was available for US$37.50 in quantities of 100 and up.[9][13] The military version of M8155 was available for US$100.00 in quantities of 100.[10] There is a 5 MHz version of Intel 8155–2.[8] The available 8155H was introduced using the HMOS II technology which it uses 30 percent less power than the previous generation. The plastic package version of P8155H (3 MHz) and P8155H-2 (5 MHz) are available for US$5.15 and US$6.40 per 100 in quantities respectively.[3]

- 8156 – 2K-bit static MOS RAM with 3 I/O Ports and Timer. The industrial version of ID8156 was available for US$37.50 in quantities of 100.[9][13] There is a 5 MHz version of Intel 8156–2.[8] The available 8156H was introduced using the HMOS II technology which it uses 30 percent less power than the previous generation. The plastic package version of P8156H (3 MHz) and P8156H-2 (5 MHz) are available for US$5.15 and US$6.40 per 100 in quantities respectively.[3]

- 8185 – 1,024 x 8-bit Static RAM. It included three chip selects and an internal address latch driven directly by the 8085's ALE. The 5 MHz version of Intel 8185-2 was available for US$48.75 in quantity of 100.[8]

ROM memory

[edit]- 8355 – 2,048 × 8-bit ROM, two 8-bit I/O ports. The industrial version of ID8355 was available for US$22.00 in quantities of 1000.[9] There is a 5 MHz version of Intel 8355–2.[8]

- 8604 – 4096-bit (512 ×8) PROM

- 8755 – 2048 x 8-bit EPROM, two 8-bit I/O ports. The Intel 8755A-2 is the 5 MHz version. That version was available for US$81.00 in quantity of 100.[8] There was an Industrial Grade version Intel I8755A-8.[13]

RAM controllers

[edit]- 8202 – Dynamic RAM Controller. This supports the Intel 2104A, 2117, or 2118 DRAM modules, up to 128 KB of DRAM modules. Price was reduced to US$36.25 for quantities of 100 for the D8202 package style around May 1979.[14]

- 8203 – Dynamic RAM Controller. The Intel 82C03 CMOS version dissipates less than 25 mA. It supports up to 16x 64K-bit RAM for a total capacity of up to 256 KB. It refreshes every 10 to 16 microseconds. It supports multiplexing of row and column memory addresses. It generates strobes to latch the address internally. It arbitrates between simultaneous requests for memory access and refresh. It also acknowledges memory-access cycles to the system CPU. The 82C03 was available in either ceramic or plastic packages for US$32.00 in 100 pieces quantity.[15]

- 8207 – DRAM Controller

Periphery

[edit]- 8206 – Error Detection & Correction Unit

- 8210 – TTL To MOS Shifter & High Voltage Clock Driver

- 8212 – 8-bit I/O Port. The industrial version of ID8212 was available for US$6.75 in quantities of 100.[9]

- 8216 – 4-bit Parallel Bidirectional Bus Driver. The industrial version of ID8216 was available for US$6.40 in quantities of 100.[9]

- 8218/8219 – Bus Controller

- 8226 – 4-bit Parallel Bidirectional Bus Driver. The industrial version of ID8226 was available for US$6.40 in quantities of 100.[9]

- 8237 – DMA Controller

- 8251 – USART Communication Controller

- 8253 – Programmable Interval Timer

- 8254 – Programmable Interval Timer. The 82C54 CMOS version was outsourced to Oki Electronic Industry Co., Ltd.[16]

- 8255 – Programmable Peripheral Interface

- 8256 – Multifunction Peripheral. This multifunction chip uses Serial Communications, Parallel I/O, Counter/Timers and Interrupts. The Intel 8256AH was available for US$21.40 in quantities of 100.[17] This integrated circuit chip integrates the chips with the following functionality:

- Intel 8251A Programmable Communications Interface

- Intel 8253 Programmable Interval Timer

- Intel 8255A Programmable Peripheral Interface

- Intel 8259A Programmable Interrupt Controller.

- 8257 – DMA Controller

- 8259 – Programmable Interrupt Controller

- 8271 – Programmable Floppy Disk Controller

- 8272 – Single/Double Density Floppy Disk Controller. It is compatible with IBM 3740 and System 34 formats and provides both Frequency Modulation (FM) or Modified Frequency Modulation (MFM). This version was available for US$38.10 in quantities of 100.[18]

- 8273 – Programmable HDLC/SDLC Protocol Controller. This device supports ISO/CCITT's HDLC and IBM's SDLC communication protocols. These were available for US$33.75 (4 MHz) and US$30.00 (8 MHz) in quantities of 100.[18]

- 8274 – Multi-Protocol Serial Controller. This support three different protocols using the following feature of Asynchronous Operation, Byte Synchronous Operation and Bit Synchronous Operation. The Byte Synchronous mode is compatible to IBM's Bisync signal protocol. The Bit Synchronous mode is compatible to IBM's SDLC and the International Standards Organization's HDLC protocol and is compatible with CCITT X.25 international standard as well. It was packaged in 40-pin product using the Intel's HMOS technology. The available version is rated up to 880 kilobaud for US$30.30 in the quantities of 100.[19] NEC μPD7201 was also compatible.

- 8275 – Programmable CRT Controller. It refreshes the raster scan display by buffering from main memory and keeping track of the display portion. This version was available for US$32.00 in quantities of 100.[18]

- 8276 – Small System CRT Controller

- 8278 – Programmable Key Board Interface

- 8279 – Key Board/Display Controller

- 8282 – 8-bit Non-Inverting Latch with Output Buffer

- 8283 – 8-bit Inverting Latch with Output Buffer

- 8291 – GPIB Talker/Listener. This controller can operate from 1 to 8 MHz. It was available for US$23.75 in quantities of 100.[18]

- 8292 – GPIB Controller. Designed around Intel 8041A which it has been programmed as an controller interface element. It also controls the bus using three lock-up timers to detect issues on the GPIB bus interface. It was available for US$21.25 in quantities of 100.[18]

- 8293 – GPIB Transceiver. This chipset supports up to 4 different modes: Mode 0 Talker/Listener Control Lines, Mode 1 Talker/Listener/Controller Control Lines, Mode 2 Talker/Listener/Controller Data Lines, and Mode 3 Talker/Listener Data Lines. It was available for US$11.50 in quantities of 100. At the time of release, it was available in samples then full production in the first quarter of 1980.[20]

- 8294 – Data Encryption/Decryption Unit + 1 O/P Port. It encrypts and decrypts 64-bit blocks of data using the Federal Information Processing Data Encryption Standard algorithm. This also uses the National Bureau of Standards encryption algorithm. This DEU operates using a 56-bit user-specified key to generate 64-bit cipher words. It was available for US$22.50 in quantities of 100.[18]

- 8295 – Dot Matrix Printer Controller. This interfaces with LRC 7040 Series dot matrix printers and other small printers as well. It was available for US$20.65 in quantities of 100.[18]

Educational use

[edit]In many engineering schools the 8085 processor is used in introductory microprocessor courses. Trainer kits composed of a printed circuit board, 8085, and supporting hardware are offered by various companies. These kits usually include complete documentation allowing a student to go from soldering to assembly language programming in a single course. Also, the architecture and instruction set of the 8085 are easy for a student to understand. Shared Project versions of educational and hobby 8085-based single-board computers are noted below in the External Links section of this article.

Simulators

[edit]Software simulators are available for the 8085 microprocessor, which allow simulated execution of opcodes in a graphical environment.

See also

[edit]- IBM System/23 Datamaster gave IBM designers familiarity with the 8085 support chips used in the IBM PC.

Notes

[edit]- ^ Note that the Z80 assigns different instructions—two of the Z80's 6 relative jumps—to the opcodes that the 8085 uses for RIM and SIM, making 8085 programs that use these instructions generally unable to run on the Z80 without modification. Since use of these instructions usually relates to 8085-specific hardware features, the necessary program modification would typically be nontrivial.

- ^ Even so, there is no need for seven different effectively identical delay instructions, and they are also identical in effect and form to the NOP instruction, except that NOP conveniently has the opcode 00 hex.

- ^ (The TRAP interrupt, being an NMI, can always bring the 8085 out of the HALT state.)

References

[edit]- ^ "The Life Cycle of a CPU". www.cpushack.com.

- ^ "Intel® Microprocessor Quick Reference Guide - Year". www.intel.com.

- ^ a b c d e f g h Intel Corporation, "New Products: HMOS MCS-85 Chips Uses 20 to 30 Percent Less Power", Solutions, July/August 1981, Page 22

- ^ The history of the microcomputer-invention and evolution, S Mazor - Proceedings of the IEEE, 1995

- ^ The MCS-80/85 Family User's Manual (PDF). Intel. January 1983. pp. 1–8. Archived (PDF) from the original on August 29, 2017.

The 8085A CPU is 100% software compatible with the Intel 8080A CPU.

- ^ Dehnhardt, Wolfgang; M. Sorensen, Villy (January 1979). "Unspecified 8085 op codes enhance programming". Electronics. McGraw-Hill: 144–145. ISSN 0013-5070.

- ^ Mazor, Stanley (January–March 2010). "Intel's 8086". IEEE Annals of the History of Computing. IEEE Computer Society: 75–79. ISSN 1058-6180.

- ^ a b c d e f Intel Corporation, "New EPROM completes 5MHz capability for MCS-85™ family", Intel Preview, January/February 1980, p. 24.

- ^ a b c d e f g Intel Corporation, "Microcomputer Component: New industrial grade product line answers the demand for high-reliability components to operate in industrial applications.", Intel Preview, March/April 1979, p. 11.

- ^ a b Intel Corporation, "Military Products: Intel marches on!", Intel Preview, March/April 1979, p. 19.

- ^ "Микропроцессорный комплект М1821" [Microprocessor system M1821] (in Russian). Novosibirsk: AO NZPP. Retrieved May 31, 2016.

- ^ "Description of the Rover Sojourner". mars.jpl.nasa.gov.

- ^ a b c Intel Corporation, "8086 Available for industrial environment", Intel Preview Special Issue: 16-Bit Solutions, May/June 1980, p. 29.

- ^ Intel Corporation, "Microcomputer Components: Intel reduces prices on the 8202, the first single chip, complete solution to dynamic RAM control", Intel Preview, May/June 1979, p. 11.

- ^ Intel Corporation, "New Product Focus Components: A Refreshing New Dynamic RAM Controller", Solutions, July/August 1984, Page 12.

- ^ Intel Corporation, "NewsBit: Intel Licenses Oki on CMOS Version of Several Products", Solutions, July/August 1984, Page 1.

- ^ Intel Corporation, "New Product Focus Components: Peripheral Vision: The 8256AH Combines Four Chips In One", Solutions, July/August 1984, Page 13.

- ^ a b c d e f g Intel Corporation, "Intel peripherals enhance 8086 system design", Intel Preview Special Issue: 16-Bit Solution, May/June 1980, p. 22.

- ^ Intel Corporation, "New Products: High-Speed Controller Supports Three Protocols", Solutions, July/August 1981, Page 18

- ^ Intel Corporation, "Feature: 8293 Transceiver completes Intel GPIB family", Intel Preview, January/February 1980, p. 13.

Further reading

[edit]- Books

- Stallings, William (2009). Computer Organization and Architecture: Designing for Performance (8th ed.). Prentice Hall. ISBN 978-0-13-607373-4.

- Yadav, Abhishek (2008). Microprocessor 8085, 8086. Firewall Media. ISBN 978-81-318-0356-1.

- Gaonkar, Ramesh (December 2000). Microprocessor Architecture, Programming and Applications with the 8085. Penram International Publishing. ISBN 81-87972-09-2.

- Bill Detwiler Tandy TRS-80 Model 100 Teardown Tech Republic, 2011 Web

- Leventhal, Lance (1978). 8080A/8085 Assembly Language Programming (1st ed.). Adam Osborne & Associates.[dead link]; 495 pages

- Zaks, Rodnay; Lesea, Austin (1979). Microprocessor Interfacing Techniques (3rd ed.). Sybex. ISBN 978-0-89588-029-1.; 466 pages

- Sen, S.K. (2010). Understanding 8085/8086 Microprocessors and Peripheral ICs Through Questions and Answers (2nd ed.). New Age International Publishers. ISBN 978-8122429749.[dead link]; 303 pages

- Reference Cards

- Intel 8085 Reference Card; Saundby; 2 pages. (archive)

- Intel 8080 / 8085 Assembly Reference Card (HEX opcodes)

External links

[edit]- Shirriff, Ken (July 2013). "Reverse-engineering the 8085's ALU and its hidden registers".

Simulators:

- GNUSim8085 - simulator, assembler, debugger

Boards: