## NANO LETTERS

2002 Vol. 2, No. 7 755-759

## High-Mobility Nanotube Transistor Memory

M. S. Fuhrer,\* B. M. Kim, T. Dürkop, and T. Brintlinger

Department of Physics, University of Maryland, College Park, Maryland 20742-4111

Received April 9, 2002; Revised Manuscript Received May 16, 2002

## **ABSTRACT**

A high-mobility (9000 cm²/V·s) semiconducting single-walled nanotube transistor is used to construct a nonvolatile charge-storage memory element operating at room temperature. Charges are stored by application of a few volts across the silicon dioxide dielectric between nanotube and silicon substrate, and detected by threshold shift of the nanotube field-effect transistor. The high mobility of the nanotube transistor allows the observation of discrete configurations of charge corresponding to rearrangement of a single or few electrons. These states may be reversibly written, read, and erased at temperatures up to 100 K.

Decreasing the power required to write and erase memory devices requires either a reduction of the write voltage or a reduction in the number of electrons representing one bit. The former is fundamentally limited by the thermal energy at room temperature, and efforts have focused on the latter. The ultimate reduction, i.e., the storage of a single electronic charge, offers advantages over storing quasi-continuous quantities of charge:1 the Coulomb energy associated with adding additional charges to the storage node can be used to guarantee a discrete charge state,<sup>2</sup> and the quantized nature of the charge stored makes the device characteristics less sensitive to the details of the device structure. However, the operation of a single-electron memory at useful temperatures presents two major challenges: the capacitance of the storage node must be small enough that its Coulomb charging energy is significantly larger than the thermal energy at the operating temperature, and the readout device must be sufficiently sensitive to detect a single nearby electronic charge. Efforts to date have focused on floating-gate charge storage nodes either patterned lithographically<sup>3–5</sup> or formed serendipitously in a polycrystalline channel. Detection of single charges at elevated temperatures has been demonstrated with singleelectron transistors<sup>5</sup> or very narrow silicon- or polysiliconon-insulator field-effect transistors (FETs).<sup>1,3,4</sup> However, single-electron transistors that can operate at room temperature remain extremely difficult to fabricate, and the fieldeffect transistors demonstrated so far have modest mobilities.

Here we report on a charge-storage memory using a single semiconducting nanotube FET as the readout. Charge is reversibly injected and removed from the dielectric by applying a moderate voltage (<10 V) across the dielectric

between nanotube and substrate. The nanotube FET is ideal as a charge detecting device; it has extremely high mobility (e.g. 9000 cm²/V·s for the device described here), large geometrical capacitance, and its one-dimensional nature guarantees that local changes in charge density affect the global conductance. In the device reported here, discrete charge states corresponding to differences of a single or at most a few stored electrons are observed and can be written, read, and erased at temperatures up to 100 K, with changes in current of more than 50 nA. This rather crude device demonstrates the significant advantages of nanotube transistors for single-electron or few-electron memories; significant improvement is expected for shorter gate length devices and optimization of the charge storage node.

The carbon nanotube in this study was synthesized via chemical vapor deposition over iron nanoparticles at 900 °C, with methane as the feedstock gas,<sup>6</sup> on a conducting silicon substrate capped by 500 nm of thermally grown SiO<sub>2</sub>. Source and drain electrical contacts to the nanotube are made via evaporated Cr/Au electrodes; the conducting substrate acts as a gate electrode. Room temperature and low temperature electrical measurements were carried out with the samples mounted on a cryostat in flowing helium gas. While all data presented here correspond to this device, qualitatively similar behavior was obtained with other semiconducting nanotube devices fabricated in a similar fashion.

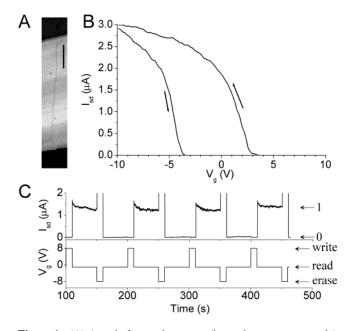

We begin by discussing the room-temperature characteristics and charge-storage memory operation of our device. Figure 1A shows an atomic force microscope topograph of the device; the nanotube has a length  $L=4.8~\mu \mathrm{m}$  and a diameter  $d=2.7~\mathrm{nm}$  as determined from the height profile of this image. Figure 1B shows the drain current I as a function of gate voltage  $V_{\mathrm{g}}$  with  $V_{\mathrm{sd}}=500~\mathrm{mV}$  applied to the source electrode. The semiconducting nanotube acts as

<sup>\*</sup> Corresponding author. Tel: (301) 405–6143. Fax: (301) 314–9465. E-mail: mfuhrer@physics.umd.edu. Web: http://www.physics.umd.edu/condmat/mfuhrer/

Figure 1. (A) Atomic force microscope (intermittent-contact mode) topograph of the nanotube device used in this study. The nanotube is the thin, nearly vertical gray line between the two electrodes (dark blocks at top and bottom). Scale bar: 1 micron. (B) Drain current as a function of gate voltage at room temperature and a source-drain bias of 500 mV. As the gate voltage is swept from positive to negative and back a pronounced hysteresis is observed, as indicated by the arrows denoting the sweep direction. (C) Four read/write cycles of the nanotube memory at room temperature. The upper panel shows the drain current at a source-drain bias of 500 mV, while the lower panel shows the gate voltage. The time axis is the same for both graphs. The memory state was read at -1 V, and written with pulses of  $\pm 8$  V.

a p-type FET, conducting at negative gate voltage and becoming insulating at positive gate voltage, as previously reported. As the gate voltage is swept back and forth between +10 V and -10 V, a large hysteresis is evident in the  $I-V_{\rm g}$  curves; the threshold gate voltage  $V_{\rm th}$  at which the nanotube begins to conduct is shifted by more than 6 V.

Figure 1C demonstrates that this hysteresis may be used as the basis of a stable memory at room temperature. Here the state of the device is read at  $V_{\rm sd} = 500$  mV,  $V_{\rm g} = -1$  V, and written and erased with pulses of the gate voltage to  $\pm 8$  V. A current of > 1 $\mu$ A may be switched. After an initial slow decay ( $\sim 50$  s) the current remains constant; the hold time of the memory exceeds 5000 seconds.

$I-V_{\rm g}$  curves in Figure 1B we calculate a hole mobility of  $\sim 9000~{\rm cm^2/V^{\bullet}s}$ , greatly exceeding pure silicon ( $\sim 450~{\rm cm^2/V^{\bullet}s}$ ). This mobility value also greatly exceeds the earlier values reported for laser-ablation-synthesized semiconducting nanotubes<sup>8,10</sup> but agrees with other recent results on CVD-synthesized semiconducting nanotubes.<sup>11–13</sup>

We now discuss the mechanism of charge storage in the nanotube memory device. The threshold shift indicates that a reconfiguration of charge near the nanotube occurs under the application of a gate voltage. This reconfiguration of charge could occur either via the movement of local charges already present in the system, e.g., electrons or ions in the dielectric, or by injection or removal of electrons from the dielectric through the electrodes or nanotube. The "sign" of the hysteresis loop, i.e., *positive* gate voltage *increases* the threshold voltage, indicates that charges are being injected into the dielectric from the nanotube, similar to a floating gate memory (the opposite sign hysteresis is observed for mobile ions or electrons, for example the "proton memory," which uses mobile hydrogen ions in SiO<sub>2</sub>).

We propose the following mechanism to explain the memory effect in our nanotube devices. Due to the geometry of the device, the electric field is much higher at the nanotube than at the Si/SiO<sub>2</sub> interface; for this reason we concentrate on the nanotube as the source of charge injection. The nanotube diameter is small compared to the dielectric thickness, and the geometry may be approximated by a cylindrical capacitor with the nanotube as the center electrode. Because of the small size of the nanotube, the electric field at the nanotube surface is very high:  $E = V_g/KR_t ln(R_g/R_g)$  $R_{\rm t}$ )  $\approx V_{\rm g}/23R_{\rm t}$  where  $R_{\rm t}=1.35$  nm is the nanotube radius,  $R_{\sigma} = 500$  nm is the dielectric thickness, and K = 3.9 is the dielectric constant of SiO<sub>2</sub>. Thus the electric field at the nanotube/SiO<sub>2</sub> interface for  $V_g = 10$  V is greater than 0.3 V/nm, comparable to the breakdown field for  $SiO_2$  ( $\sim 0.25$ V/nm), so it is reasonable to expect movement of charge in the dielectric. (Note that "breakdown field" is typically expressed as the potential difference across the dielectric divided by the dielectric thickness, i.e., does not include K, so the typically quoted value of  $\sim 1.0$  V/nm for SiO<sub>2</sub> translates to an internal electric field of  $\sim 0.25$  V/nm). We propose that at these high fields, electrons are easily injected into the dielectric from the nanotube and remain trapped in metastable states until the polarity is reversed. It is notable that a nonvolatile memory based on charge storage in a thick SiO<sub>2</sub> gate dielectric was recently reported in organic thinfilm transistors; in this parallel-plate geometry  $V_g = 100 \text{ V}$  $(E \approx 0.03 \text{ V/nm})$  was sufficient to polarize the SiO<sub>2</sub> dielectric.15 The same sign hysteresis was observed as in our case, indicating injection of charge into the dielectric.

Other possible mechanisms for charge rearrangement were considered. At such high electric fields the gas around the nanotube may experience corona discharge, and ionized gas could transport charge to the dielectric surface. However, this mechanism would be expected to exhibit a large dependence on the pressure and species of the gas around the nanotube; we found similar operation of the nanotube memory in humid air, dry helium, and dynamic vacuum

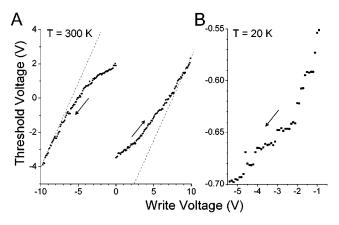

**Figure 2.** (A) Evolution of the threshold voltage (defined in text) after application of write voltage pulses of successively higher magnitudes at room temperature. The dielectric was first polarized at -10 V, and the threshold voltage was measured after successive application of one-second write pulses, increasing the pulse by 0.1 V each time (lower right curve). The dielectric was then polarized at +10 V, and the threshold voltage was again measured after application of one-second write pulses, now decreasing the pulse by 0.1 V each time (upper left curve). The dashed lines indicate a slope of unity. (B) Threshold voltage at 20 K after polarizing at +8 V and applying write voltage pulses successively decreased by 0.1 V. Several discrete plateaus in the threshold voltage are evident.

(10<sup>-3</sup> Torr). It is also possible that the high electric field causes a rearrangement of adsorbates on the nanotube which act as dopants, <sup>16</sup> e.g., oxygen; however, it is difficult to explain the observed shift of the threshold voltage from positive to negative simply through rearrangement of electron acceptors.

Figure 2A illustrates the shift in threshold voltage with the magnitude of the applied pulse in gate voltage at room temperature. Threshold voltage is defined here as the gate voltage at which the conductance was  $0.6 \mu S$  (approximately one-tenth the maximum conductance). This underestimates the onset of conductance; however, for this purpose we are interested in relative shifts of the threshold voltage, not the absolute magnitude. The lower curve represents a starting condition with the dielectric polarized at -10 V. The threshold voltage was measured after successive write voltage pulses of 1 s; after the write pulse the gate voltage was reduced until the conductance was 0.6  $\mu$ S, defining  $V_{th}$ .  $V_{th}$ shifts toward higher values continuously, with no obvious sharp onset of polarization. A similar curve is obtained by starting with the dielectric polarized at  $\pm 10$  V and applying successive negative write voltage pulses (upper curve), followed by increasing the gate voltage until the conductance was 0.6  $\mu$ S to obtain  $V_{th}$ . The smooth behavior of the threshold voltage shift indicates a continuous distribution of energies for the charge trap sites. Interestingly, the slope of the threshold voltage vs write voltage curve approaches unity (dashed lines) at high write voltages. This implies that only a finite range of charge density in the nanotube is accessible through electrostatic doping; at high gate bias the screening of the gate due to injected charge is nearly perfect. This fact should have significant consequences for the understanding of carbon nanotube transistors.

Figure 2B shows a similar measurement of the threshold voltage shift as a function of write voltage pulses, but now at a temperature of 20 K. At lower temperature the threshold voltage shift is smaller, and noticeable discrete steps are evident in the  $V_{\rm th}$  curve. The gate capacitance of the device is approximately 54 aF, or 350 e/V. If we assume that the capacitance of the charges trapped in the dielectric is dominated by capacitance to the nanotube, then the  $V_{\rm th}$  shift of  $\sim$ 0.15 V in Figure 2B then corresponds to a charge of  $\sim$ 50 e added to the nanotube. This number is somewhat larger but of the same order of magnitude as the approximately 10-15 discrete current levels observed in Figure 2B; the difference in conductance between plateaus arises from a change in the oxide charge of one, or at most a few, electrons.

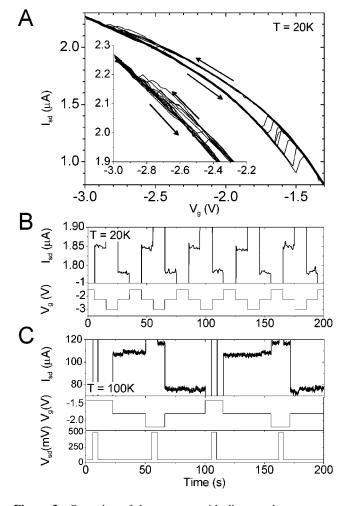

Figure 3A shows the  $I-V_{\rm g}$  characteristics of the device at 20 K. Here  $V_{\rm g}$  is swept back and forth over a particular region (between -1.3 V and -3 V); eight cycles are shown. Two branches of the  $I-V_{\rm g}$  curve are clearly visible, with switching between the branches occurring in specific ranges of  $V_{\rm g}$ . Switching between the two curves occurs in discrete jumps, and no intermediate curves are seen. The gate voltage at which the switch occurs varies from sweep to sweep, indicating a stochastic process. This range of gate voltage was chosen in order to highlight this large hysteresis loop; other hysteresis loops could be observed with much smaller widths by scanning different ranges of gate voltage. This behavior is typical of our nanotube devices, most often only one or two large hysteresis loops may be observed, with switching occurring near the threshold gate voltage.

Figure 3B demonstrates memory operation of the device at 20 K. The drain current is measured at a gate voltage of -2.25 V and a source-drain bias of 500 mV. The drain current is switched between high and low states by application of a gate voltage pulse of  $\pm 0.75$  V (relative to the -2.25 V baseline). The difference in current between high and low states is approximately 60 nA. The memory is stable for at least 100 seconds.

At higher temperatures (T = 100 K) and at high bias ( $V_{\text{sd}}$ = 500 mV), a hysteresis loop with two branches was still seen, but reversible switching between the two branches was observed at all gate voltages, appearing as random telegraph noise in the current at fixed gate voltage with a characteristic switching time of order 1 s at  $V_{\rm g} = -1.8$  V. This random telegraph noise was greatly reduced when  $V_{\rm sd}$  was lowered to 50 mV, with one switching event occurring every few hundred seconds. However, applying a pulse to  $V_g$  alone with  $V_{\rm sd} = 50 \text{ mV}$  was found to be insufficient to ensure a write/ erase switch event. An additional pulse of  $V_{\rm sd}$  to 500 mV applied only during the write/erase gate pulses was found to guarantee switching to the desired state. This resulted in the reliable writing and erasing of the memory at 100 K (Figure 3C), with gate voltage excursions of only  $\pm 0.4$  V from the readout voltage of -1.8 V.

The discrete jumps in threshold voltage in Figure 2B and the discrete  $I-V_{\rm g}$  curves in Figure 3A strongly suggest that single-electron changes in the dielectric charge are responsible for the observed changes in the device characteristics;

**Figure 3.** Operation of the memory with discrete charge states. (A) The drain current as a function of gate voltage at a sourcedrain bias of 500 mV and a temperature of 20 K. The gate voltage is swept between −1.3 and −3 V (toward positive eight times, and back negative seven times). Two discrete branches of the curve are evident, with discrete switching events between the branches occurring at different gate voltages for increasing/decreasing sweeps. The inset shows more clearly the right side of the main figure. (B) Five read/write cycles of the memory at 20 K. The horizontal (time) axis applies to both curves. The memory state was read at a gate voltage of −2.25 V, and written (erased) with pulses of −1.5 V (−3.0 V) to the gate. (C) Two read/write cycles of the memory at 100 K. Here the memory was read at a source-drain bias of 50 mV and gate voltage of −1.8 V, and written (erased) with pulses of −1.4 V (−2.2 V) to the gate and 500 mV to the source.

i.e., that the difference in conductance states in the memory (Figures 3B and 3C) is due to the movement of a single electronic charge. However, the discrete changes in conductance observed in Figure 2B and Figure 3A are somewhat larger than expected from a simple estimation of the threshold shift due to the addition of one electron to the entire nanotube. In Figure 2B, the plateaus are spaced 3–5 times farther apart than would be expected. In Figure 3A, the spacing in gate voltage between the two curves varies from 0.06 to 0.15 V, approximately 20–50 times larger than would be expected. We argue that this is reasonable and expected given the localized nature of the stored charge. The effects of trapped charge and gate charge are different: trapped charges are localized, while the gate charge affects the

nanotube globally. A localized charge may significantly affect the conductance of a small region (within an electrostatic screening length) of the nanotube, but because this region is necessarily in series with the rest of the nanotube, the global resistance is affected. The screening length of the nanotube may be estimated from scanned-gate microscopy (SGM) measurements;<sup>17</sup> SGM is able to resolve features with spacing of 50 nm in a lightly doped nanotube (zero global gate voltage), suggesting that the screening length is comparable to or less than 50 nm. A single electron would shift the potential of a 50-nm section of the nanotube by 300 mV, greater than the largest shift observed in Figure 3A, 150 mV.

The effect of localized charge may be exaggerated by the device being operated at high bias (near pinchoff), which would lead to greater sensitivity to charges near the source electrode, or due to local potential modulations in the nanotube, which cause greater charge sensitivity at specific locations. <sup>18,19</sup> The fact that the spacing in gate voltage between the two curves in Figure 3A varies significantly, becoming larger nearer the threshold (more positive gate voltage), argues that pinchoff is important; indeed, at the upper end of the gate voltage range the source-drain bias (500 mV) is comparable to the difference between the gate voltage (-1.5 to -3.0 V) and the threshold voltage ( $\sim -1.1$  V), and pinchoff should be significant.

These unoptimized nanotube memory devices already show the promise of using carbon nanotube FETs for single-or few-electron charge-storage memories at useful temperatures. Narrow, high-mobility nanotube FETs should significantly outperform other semiconductor FETs in charge detection. Significant improvement should be obtainable with shorter gate lengths and suitable charge traps, such as a floating metal gate or  $SiO_2/Si_3N_4/SiO_2$  trilayer.

**Acknowledgment.** The authors are grateful for discussions with P. L. McEuen, Hongkun Park, and Frank Gac. This research was supported by ARDA and the Office of Naval Research through grant N000140110995, the Director of Central Intelligence Postdoctoral Research Fellowship Program, and the National Science Foundation through grant DMR-0102950.

## References

- Yano, K.; Ishii, T.; Hashimoto, T.; Kobayashi, T.; Murai, F.; Seki, K. IEEE Trans. Electron Dev. 1994, 41, 1628–1638.

- (2) Tiwari, S.; Rana, F.; Chan, K.; Leathen, S.; Hanafi, H. Appl. Phys. Lett. 1996, 69, 1232–1234.

- (3) Guo, L.; Leobandung, E.; Chou, S. Y. Science 1997, 275, 649-651.

- (4) Nakajima, A.; Futatsugi, T.; Kosemura, K.; Fukano, T.; Yokoyama, N. Appl. Phys. Lett. 1997, 70, 1742–1744.

- (5) Yoo, K. H.; Park, J. W.; Jinhee, K.; Park, K. S.; Oh, S. C.; Lee, J. O.; Kim, J. J.; Choi, J. B.; Lee, J. J. Appl. Phys. Lett. 1999, 74, 2073–2075.

- (6) The iron nanoparticle catalyst was prepared following ref 20. The catalyst was reduced at 900 °C in flowing H<sub>2</sub>/Ar, followed by growth under pure methane flowing at 3500 sccm for 6 min. An alumina substrate coated with iron/molybdenum catalyst prepared as in ref 21 placed upstream from the substrate was found to promote nanotube growth.

- (7) Tans, S. J.; Verschueren, R. M.; Dekker, C. Nature 1998, 393, 49–52.

- (8) Martel, R.; Schmidt, T.; Shea, H. R.; Hertel, T.; Avouris, P. Appl. Phys. Lett. 1998, 73, 2447–2449.

- (9) Note that the slope of the  $I-V_{\rm g}$  curve is affected by the memory effect described here. However, the injected charge on application of a gate voltage tends to screen the effect of the gate, reducing the apparent mobility. Our mobility figure is therefore a lower bound.

- (10) McEuen, P. L.; Bockrath, M.; Cobden, D. H.; Yoon, Y.-G.; Louie, S. G. Phys. Rev. Lett. 1999, 83, 5098.

- (11) Dürkop, T.; Brintlinger, T.; Fuhrer, M. S. to appear in *Electronic Properties of Molecular Nanostructures*; Kuzmany, H., Fink, J., Mehring, M., Roth, S., Eds.; AIP Conference Proceedings, American Institute of Physics: New York, 2002.

- (12) Rosenblatt, S.; Yaish, Y.; Park, J.; Gore, J.; McEuen, P. L., to be published.

- (13) McEuen, P. L.; Fuhrer, M. S.; Park, H. to appear in *IEEE Transactions on Nanotechnology*, 2002.

- (14) Vanheusden, K.; Warren, W. L.; Devine, R. A. B.; Fleetwood, D. M.; Schwank, J. R.; Shaneyfelt, M. R.; Winokur, P. S.; Lemnios, Z. J. *Nature* 1997, 386, 587–589.

- (15) Katz, H. E.; Hong, X. M.; Dodabalapur, A.; Sarpeshkar, R. J. Appl. Phys. 2002, 91, 1572–1576.

- (16) Collins, P. G.; Bradley, K.; Ishigami, M.; Zettl, A. Science 2000, 287, 1801–1804.

- (17) Fuhrer, M. S.; Forero, M.; Zettl, A.; McEuen, P. L. In *Electronic Properties of Molecular Nanostructures*; Kuzmany, H., Fink, J., Mehring, M., Roth, S., Eds.; AIP Conference Proceedings; American Institute of Physics: New York, 2001.

- (18) Tans, S. J.; Dekker, C. Nature 2000, 404, 834-835.

- (19) Bachtold, A.; Fuhrer, M. S.; Plyasunov, S.; Forero, M.; Anderson, E. H.; Zettl, A.; McEuen, P. L. Phys. Rev. Lett. 2000, 84, 6082– 6085.

- (20) Hafner, J. H.; Chin-Li, C.; Oosterkamp, T. H.; Lieber, C. M. J. Phys. Chem. B 2001, 105, 743-746.

- (21) Kong, J.; Soh, H. T.; Cassell, A.; Quate, C. F.; Dai, H. Nature 1998, 395, 878.

NL025577O