# Distributed Algorithm Simulation Using Input/Output Automata

by

### Kenneth J. Goldman

S.M. EECS, Massachusetts Institute of Technology (1987) Sc.B. Computer Science, Brown University (1984)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

### September 1990

© Massachusetts Institute of Technology 1990

| Signature of Author                 | Department of Electrical Engineering and Computer Science July 16, 1990                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Certified by                        | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                     | Nancy A. Lynch<br>Professor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                     | Thesis Supervisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                     | term in the control of the control o |

| Accepted by ,                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MASSAUTIOGERFORMOTIFO OF TECHNOLOGY | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                     | Chairman, Departmental Committee on Graduate Students                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NOV 27 1990                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LIDBARIFS                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

**ARCHIVES**

# Distributed Algorithm Simulation Using Input/Output Automata

by

#### Kenneth J. Goldman

Submitted to the Department of

Electrical Engineering and Computer Science on July 16, 1990

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

Abstract: We present the Spectrum Simulation System, a new research tool for the design and study of distributed algorithms. Based on the formal Input/Output automaton model of Lynch and Tuttle, Spectrum allows one to express distributed algorithms as collections of I/O automata and simulate them directly in terms of the semantics of that model. This permits integration of algorithm specification, design, debugging, analysis, and proof of correctness within a single formal framework that is natural for describing distributed algorithms. Spectrum provides a language for expressing algorithms as I/O automata, a simulator for generating algorithm executions, and a graphics interface for constructing systems of automata and observing their executions.

We show that the properties of the I/O automaton model provide a solid foundation for algorithm development tools. For example, using I/O automaton composition, Spectrum users may define composed types hierarchically, study simulations at varying levels of detail, and create specialized debugging and analysis devices. These devices, called spectators, are written in the Spectrum language just as any other system component, and can monitor algorithm executions for correctness and performance without interfering with the algorithm.

The system is designed to support experimentation with algorithms. For example, the system separates algorithms from the system configurations in which they are to run, allowing users to vary them independently. Also, the message system may be modeled explicitly as an automaton, permitting users to study algorithms under different communications assumptions simply by substituting one automaton for another.

3

Motivated by a desire to broaden the class of algorithms that may be studied using Spectrum,

we propose two extensions to the I/O automaton model. First, we extend the I/O automaton

model to allow modelling of shared memory systems, as well as systems that include both shared

memory and message passing communication. This extension supports description, verification,

and analysis of shared memory systems. As an example, Dijkstra's classical shared memory

mutual exclusion algorithm is presented and proved correct. In addition, we illustrate how

the extended model provides a unified formal framework in which shared memory systems and

message passing systems may be related. Second, we extend the I/O automaton model with

a superposition operator that permits system modules to be combined in layers so that higher

layers may observe (but not modify) the variables of lower layers. We show that superposition

does not affect the set of executions of the underlying module, thus preserving all properties

of that module. A formal specification mechanism is presented that allows the set of correct

behaviors of the higher level module to be expressed in terms of the states of the underlying

module. As an illustration of the superposition extension, the global snapshot algorithm of

Chandy and Lamport is presented with a complete proof of correctness. For both of these

model extensions, we propose corresponding extensions to the simulation system.

The final contribution of this thesis is a distributed algorithm that may be used to achieve

distributed simulation of algorithms written as I/O automata. The algorithm solves a new

synchronization problem, logically synchronous multicast, that captures the synchronization

semantics of the I/O automaton model.

Keywords: Distributed systems, distributed algorithms, formal models, I/O automata, pro-

gramming languages, simulation, program visualization, algorithm development, correctness

proofs, shared memory, mutual exclusion, linearizability, superposition, global snapshot, mul-

ticast, synchronization, distributed simulation.

Thesis supervisor: Nancy A. Lynch

Title: Professor

## Acknowledgments

I could not have asked for a better research advisor than Nancy Lynch. She has been a constant source of research ideas, and has provided direction and encouragement at all the right moments. Nancy is a co-author of Chapter 7, and has been involved with the details of many of the other chapters. I also thank the other members of my thesis committee, Baruch Awerbuch and Bill Weihl, whose comments have contributed to the quality of this thesis.

The work in Chapter 7 on proofs for shared object systems is joint work with Kathy Yelick.

I also thank Kathy for her careful reading of the remainder of that chapter.

Many of the past and present members of the Theory of Distributed Systems research group have contributed to this thesis, and all have made this group an exciting place to do research. I thank Christopher Colby for implementing the Spectrum user interface, and for his patience when I would occasionally decide to change the specification. I thank John Leo, Stephen Ponzio, and Mini Gupta for their comments on using the Spectrum Simulation System. In addition, I thank thank Alan Fekete for several discussions during the early part of this work, Jennifer Welch and Mark Tuttle for their detailed comments on both the technical details and the presentation of the logically synchronous multicast algorithm, and Hagit Attiya for several technical discussions. Also, I thank Anna Wiseman for taking care of all that paperwork.

I am grateful to Tom Miller and Paris Kanellakis, who introduced me to computer science research and were influential in my decision to attend graduate school.

I thank my parents, Lester and Judy, for all the love and support they have given me during the past 27 years. I thank the rest of my family for their moral support, and for not asking too many times when I would graduate. In particular, I thank my aunt and uncle, Phyllis and Alfred Schneider, for being a second family to me during my stay in the Boston area. I thank my in-laws, Robert and Marilyn Goldwasser, for their frequent phone calls and visits, for their words of encouragement, and especially for their daughter.

This thesis would not have been possible without the help of my wife, Sally. I thank her for emotional and technical support, for taking on extra responsibilities whenever I faced a deadline, and for never doubting once that we would finish at the same time. Finally, I thank our son, Mark, for providing energy, excitement, and humor whenever it was needed most.

This research was supported in part by the National Science Foundation under Grant CCR-86-11442, by the Office of Naval Research under Contract N00014-85-K-0168, by the Defense Advanced Research Projects Agency (DARPA) under Contract N00014-83-K-0125 and Contract N00014-89-J-1988, and by an Office of Naval Research graduate fellowship.

# Contents

| 1 | oduction                 | 13                       |    |  |  |  |  |  |

|---|--------------------------|--------------------------|----|--|--|--|--|--|

|   | 1.1                      | Distributed Algorithms   | 15 |  |  |  |  |  |

|   | 1.2                      | Design Goals             | 17 |  |  |  |  |  |

|   | 1.3                      | Thesis Overview          | 21 |  |  |  |  |  |

| 2 | The                      | Model                    | 23 |  |  |  |  |  |

|   | 2.1                      | I/O Automata             | 23 |  |  |  |  |  |

|   | 2.2                      | Composition              | 25 |  |  |  |  |  |

|   | 2.3                      | Fairness                 | 26 |  |  |  |  |  |

|   | 2.4                      | Problem Specification    | 27 |  |  |  |  |  |

|   | 2.5                      | Alternative Models       | 28 |  |  |  |  |  |

|   |                          | 2.5.1 CSP                | 28 |  |  |  |  |  |

|   |                          | 2.5.2 UNITY              | 29 |  |  |  |  |  |

|   |                          | 2.5.3 Statecharts        | 30 |  |  |  |  |  |

|   | 2.6                      | Summary                  | 31 |  |  |  |  |  |

| 3 | The Spectrum Language 33 |                          |    |  |  |  |  |  |

|   | 3.1                      | Theoretical Foundations  | 35 |  |  |  |  |  |

|   | 3.2                      | A Separation of Concerns | 38 |  |  |  |  |  |

|   | 3.3                      | Language Constructs      | 39 |  |  |  |  |  |

|   |                          | 3.3.1 Data Types         | 39 |  |  |  |  |  |

|   |                          | 3.3.2 Action Types       | 42 |  |  |  |  |  |

|   |                          | 3 3 3 Automaton Types    | 43 |  |  |  |  |  |

| 8 | CONTENTS |

|---|----------|

|---|----------|

|   | 3.4 | Example                                               | 49 |

|---|-----|-------------------------------------------------------|----|

|   | 3.5 | Support for Verification, Analysis, and Visualization | 51 |

|   |     | 3.5.1 State Invariants                                | 51 |

|   |     | 3.5.2 Spectators                                      | 52 |

|   |     | 3.5.3 Pseudovariables                                 | 54 |

|   | 3.6 | Summary                                               | 55 |

| 4 | The | Spectrum Simulator                                    | 59 |

|   | 4.1 | The Loader                                            | 60 |

|   | 4.2 | The Interpreter                                       | 62 |

|   | 4.3 | The Execution Loop                                    | 62 |

|   | 4.4 | The Scheduler                                         | 65 |

|   | 4.5 | Summary                                               | 66 |

| 5 | The | Spectrum User Interface                               | 69 |

|   | 5.1 | Overview of the Spectrum Interface                    | 70 |

|   | 5.2 | Configure Mode                                        |    |

|   |     | 5.2.1 The Types Menu                                  | 71 |

|   |     | 5.2.2 The Edit Menu                                   | 72 |

|   |     | 5.2.3 Automaton Instances                             | 72 |

|   |     | 5.2.4 Configuration Edges                             | 73 |

|   |     | 5.2.5 Creating Composed Types                         |    |

|   |     | 5.2.6 Summary Mappings                                | 74 |

|   |     | 5.2.7 Undo and Redo                                   | 74 |

|   |     | 5.2.8 Saving and Loading Files                        | 75 |

|   |     | 5.2.9 Data Structures                                 | 75 |

|   | 5.3 | Simulate Mode                                         | 76 |

|   |     | 5.3.1 The Simulate Menu                               | 76 |

|   |     | 5.3.2 The Running Simulation                          | 77 |

|   |     | 5.3.3 State Windows                                   | 78 |

|   |     | 5.3.4 Execution Rollback                              | 78 |

| C( | ONTE             | ENTS   | 9                                          |  |  |

|----|------------------|--------|--------------------------------------------|--|--|

|    |                  | 5,3.5  | Error Messages During Simulation           |  |  |

|    |                  | 5.3.6  | Trace Files                                |  |  |

|    | 5.4              | Summ   | ary                                        |  |  |

| 6  | Sys              | tem Ev | valuation 81                               |  |  |

|    | 6.1              | Comp   | arisons with Related Systems               |  |  |

|    |                  | 6.1.1  | Occam                                      |  |  |

|    |                  | 6.1.2  | UNITY 83                                   |  |  |

|    |                  | 6.1.3  | Statemate                                  |  |  |

|    |                  | 6.1.4  | DEVS                                       |  |  |

|    | 6.2              | Design | Goals Revisited                            |  |  |

|    |                  | 6.2.1  | Spectrum and the I/O Automaton Model       |  |  |

|    |                  | 6.2.2  | Expressive Power                           |  |  |

|    |                  | 6.2.3  | Experimentation                            |  |  |

|    |                  | 6.2.4  | Economy and Integration                    |  |  |

|    | 6.3              | Summ   | ary,                                       |  |  |

| 7  | Shared Memory 97 |        |                                            |  |  |

|    | 7.1              | Share  | d Memory Definitions                       |  |  |

|    |                  | 7.1.1  | Variables                                  |  |  |

|    |                  | 7.1.2  | Shared Memory Actions                      |  |  |

|    |                  | 7.1.3  | Shared Memory Automata                     |  |  |

|    |                  | 7.1.4  | Augmentation and Augmented-Composition     |  |  |

|    |                  | 7.1.5  | The Closeout Operator                      |  |  |

|    |                  | 7.1.6  | Closeout for behaviors                     |  |  |

|    |                  | 7.1.7  | Discussion                                 |  |  |

|    | 7.2              | Exam   | ple: Dijkstra's mutual exclusion algorithm |  |  |

|    |                  | 7.2.1  | The Mutual Exclusion Problem               |  |  |

|    |                  | 7,2,2  | Dijkstra's Mutual Exclusion Algorithm      |  |  |

|    |                  | 7.2.3  | Safety Proof                               |  |  |

|    |                  | 7.2.4  | Progress Proof                             |  |  |

|    |                  |        |                                            |  |  |

|   | 7.3  | Proofs for Shared Object Systems                       |

|---|------|--------------------------------------------------------|

|   |      | 7.3.1 Invocation-Response Systems                      |

|   |      | 7.3.2 Simulating Atomic Access Systems with IR Systems |

|   | 7.4  | Supporting Shared Memory in Spectrum                   |

|   | 7.5  | Summary                                                |

| 8 | Sup  | erposition 149                                         |

|   | 8.1  | Superposition Extensions                               |

|   |      | 8.1.1 Unconstrained Automata                           |

|   |      | 8.1.2 Superposition                                    |

|   |      | 8.1.3 Partial Execution Modules                        |

|   |      | 8.1.4 Superposition for Partial Executions             |

|   | 8.2  | Example: Global Snapshot                               |

|   |      | 8.2.1 Problem Specification                            |

|   |      | 8.2.2 The Algorithm                                    |

|   |      | 8.2.3 Proof of Correctness                             |

|   | 8.3  | Supporting Superposition in Spectrum                   |

|   | 8.4  | Summary                                                |

| 9 | Dist | ributed Simulation 183                                 |

|   | 9.1  | The Problem                                            |

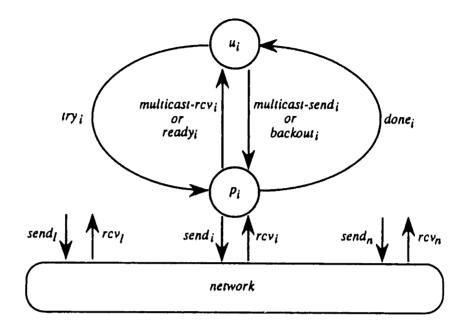

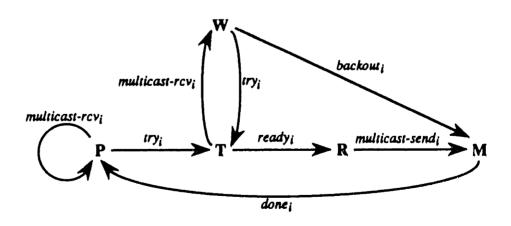

|   |      | 9.1.1 The Architecture                                 |

|   |      | 9.1.2 Correctness                                      |

|   | 9.2  | The Algorithm ,                                        |

|   | 9.3  | Proof of Correctness                                   |

|   |      | 9.3.1 Safety Proof                                     |

|   |      | 9.3.2 Liveness Proof                                   |

|   | 9.4  | Complexity Analysis                                    |

|   |      | 9.4.1 Message Complexity                               |

|   |      | 9.4.2 Time Complexity                                  |

|   |      | 9.4.3 Possible Optimizations                           |

| C( | ONTE       | ENTS                   | 11  |

|----|------------|------------------------|-----|

|    | 9.5        | Summary and Discussion | 219 |

| 10 | Con        | clusion                | 223 |

| A  | Lang       | guage Syntax           | 27  |

| В  | Fun        | ctions                 | 231 |

|    | B.1        | Generic                | 231 |

|    | <b>B.2</b> | Integers               | 232 |

|    | <b>B.3</b> | Booleans               | 232 |

|    | B.4        | Strings                | 233 |

|    | B.5        | Configuration Data     | 233 |

|    | <b>B.6</b> | Sets                   | 234 |

|    | B.7        | Multisets              | 235 |

|    | B.8        | Sequences              | 236 |

|    | <b>B.9</b> | Mappings               | 237 |

|    | B.10       | Conditionals           | 237 |

| Bi | bliog      | raphy 2                | 39  |

•

12 CONTENTS

# Chapter 1

# Introduction

We are experiencing a dramatic increase in the use of computer communication in both our professional and personal lives. A global electronic infrastructure is fast becoming a reality, and is bringing with it sweeping changes in the way people communicate, do business, and conduct their daily lives. Electronic communication for mail, information exchange, and financial and consumer services are becoming commonplace. And the continued proliferation of distributed computing will undoubtedly inspire new uses for the technology. These applications will bring increased demands for software performance and reliability, as well as an abundance of new software for distributed computing.

Distributed algorithms will be at the heart of this new software. Distributed algorithms are the protocols by which the computers in a distributed system cooperate towards the solution of a problem. Unlike sequential algorithms, used to solve problems on a single processor, distributed algorithms must cope with arbitrary communication delays and both processor and communication failures. The fact that communication delays are unpredictable means that distributed algorithms must also cope with arbitrary interleaving of processor steps. Since a given program's computation may unfold nondeterministically, designing and reasoning about distributed algorithms is inherently difficult. Therefore, researchers have turned to formal models of distributed systems in order to reason about their algorithms. For example, the I/O automaton model of Lynch and Tuttle [47, 48] is particularly well suited for the study of distributed algorithms; it allows one to state natural correctness conditions, give precise algorithm descriptions, and construct careful correctness proofs.

We claim that formal models are important not only as a means to analyzing and proving the correctness of distributed algorithms, but also as the basis of software tools for designing better algorithms. The aim of this thesis is to demonstrate how distributed algorithm specification, design, debugging, analysis, and proof of correctness may be integrated within a single formal framework that is natural for describing a wide range of distributed algorithms. Such integration not only saves one from translation between different models and languages, but also allows facts discovered during simulation and debugging to be more easily incorporated into the correctness proof, and allows properties used in the proof to be checked mechanically during simulation.

We present the Spectrum Simulation System, a new research tool for the design and study of distributed algorithms. Spectrum consists of a programming language and simulator based on the I/O Automaton model. Users express distributed algorithms as collections of I/O automata and simulate them directly, in a way that is faithful to the semantics of the formal model. A graphical user interface is provided for constructing systems of automata and animating their executions. In presenting the system, we describe how the salient features of the I/O automaton model provide a solid foundation for distributed algorithm development tools. For example, using I/O automaton composition, Spectrum users may define composed types hierarchically, study simulations at varying levels of detail, and create specialized debugging and analysis devices.

The Spectrum implementation is faithful to the original I/O automaton model, as presented by Lynch and Tuttle. This model is particularly well suited for describing collections of asynchronous processes that communicate through message passing. However, not all distributed algorithms are best described using private local state and message-passing communication. It is sometimes convenient to describe a distributed algorithm as a collection of processes that communicate through shared variables, or as a collection of system layers, arranged so that each layer makes use of the internal states of lower layers. With a view towards broadening the class of algorithms to which our simulation system is applicable, we present two extensions of the I/O automaton model. The first extension permits automata to communicate through atomic accesses to shared variables. The second extension, called *superposition*, allows programs to be constructed in layers, such that higher layers may observe the internal states of lower layers. We propose new language constructs and simulation system enhancements to support each of

#### 1.1. DISTRIBUTED ALGORITHMS

these model extensions.

Another contribution of this thesis is the formulation of a general problem called *logically* synchronous multicast and a highly concurrent protocol to solve it. We show how this protocol could be used in the Spectrum Simulation System to achieve distributed simulation of algorithms expressed as I/O automata.

We now turn to a brief introduction to distributed algorithms. Following this, we present the design goals for the Spectrum Simulation System, and draw distinctions between simulation systems and other sorts of software development tools. The chapter concludes with an overview of the thesis.

### 1.1 Distributed Algorithms

A distributed system consists of a collection of geographically separated computers linked together by a network. In general, the network topology, the arrangement of communication links between processors, may be arbitrary. Processes, program threads running on the computers, may communicate with each other by sending messages over the network, but do not have any other means of communication, such as a shared memory. Processes are autonomous, meaning that they determine when to send messages to other processes. That is, a process cannot prevent another process from sending a message. Processes do not have synchronized clocks, and their instruction execution rates may differ. This implies that processes are asynchronous; their steps may be arbitrarily interleaved. Network communication is also asynchronous, meaning that the acts of sending and receiving a message are separated (often arbitrarily) in time.

Like any computer system, distributed systems are prone to failures. However, unlike centralized systems, portions of a distributed system may continue to be useful while other portions are "down." We classify the types of failures that may occur in a distributed system into process failures and communication failures. Process failures range from simple stopping faults (crashes) to malicious faults, in which faulty processors attempt to corrupt the computation of the rest of the system by sending incorrect or conflicting messages. If we assume that a communication link is supposed to deliver each message exactly once and in the order sent, then communication failures may involve losing messages, reordering messages, delivering messages that were never sent, or delivering messages multiple times.

In order to coordinate the activities of processes in a distributed system, it is necessary to have agreed-upon protocols. These protocols are called distributed algorithms. Typical problems solved by distributed algorithms include:

- leader election: Choose exactly one distinguished "leader" process (to coordinate some computation).

- mutual exclusion: Grant permission for the use of a shared resource (e.g., a printer) in response to user requests so that no two users have permission simultaneously.

- global snapshot: Construct a recent consistent picture of the state of the entire system (as in an audit of a distributed banking system).

Distributed algorithms are usually designed with particular assumptions about the underlying system in mind. For example, one might assume that the only process failures are crash failures and that all messages sent eventually arrive. In addition to failure assumptions, one might make assumptions about the network topology or about the existence of unique process identifiers. The set of assumptions makes a great impact on the algorithmic solution. It is often interesting to consider what happens when an algorithm's assumptions are violated. For example, consider a distributed algorithm designed with the assumption that messages are delivered in order. Depending on the particular algorithm, delivering messages out of order might cause the algorithm to produce an incorrect result, might have no effect whatsoever, or might cause the algorithm to produce a correct result but with degraded (or superior!) performance.

The particular combination of process and communication failures that an algorithm must tolerate forms part of the problem specification. A specification is usually presented in terms of the input/output relationship between the algorithm and its environment. Since an algorithm has no control over its environment, a problem specification usually says that an algorithm will satisfy certain safety and liveness conditions, provided that its inputs are well-formed. The safety conditions essentially say that the algorithm never does anything "wrong", and the liveness (progress) properties essentially say that the algorithm eventually does something "right". An algorithm is said to be correct if it satisfies both the safety and liveness conditions (whenever its inputs from the environment are well-formed).

1,2. DESIGN GOALS

We need formal models to help overcome the inherent difficulty of designing distributed algorithms that stems from the arbitrary interleaving of process steps. Informal arguments and software testing are inadequate substitutes for formal methods, since anything short of a complete proof is likely to miss "bad" executions — executions in which the particular choice of process step interleaving leads to the violation of safety or liveness requirements. Formal models, such as the I/O automaton model, are useful for stating problem specifications, describing algorithms precisely, and constructing careful proofs of correctness. However, formal proofs of correctness are often long, hard, and tedious. If an algorithm is incorrect, much effort can be wasted in attempting to prove its correctness. Testing can help one to discover many errors in algorithms quickly and easily, before delving into a correctness proof. Furthermore, simply constructing a correctness proof for an algorithm may not reveal enough intuition into how the algorithm works in order to lead to improvements in the algorithm. For these reasons, it is important to have research tools for simulating distributed algorithms.

Simulation allows one to test and debug algorithms, and can reveal intuition that is helpful in understanding algorithms and constructing correctness proofs for them. In conjunction with appropriate graphical visualization techniques, simulation facilitates the study of algorithm performance under varying conditions, something not easily done in the context of a proof. But because successful testing alone is not sufficient cause to believe that an algorithm is correct, one must still construct a correctness proof as part of the algorithm development cycle. Therefore, it is important that the semantics of the simulation language be consistent with the formal model in which the proof is to be constructed. In addition, using an appropriate formal model as the basis of a simulation tool leaves open the possibility of integrating the entire algorithm development process: specification, design, debugging, analysis, and proof of correctness. The purpose of this thesis is to demonstrate how this can be achieved. We now elaborate on the design philosophy behind the Spectrum Simulation System.

### 1.2 Design Goals

We have said that the aim of this work is to construct a research tool for the design and study of distributed algorithms that integrates theoretical modelling techniques with algorithm simulation, visualization, and testing. In this section, we become more specific about this

objective. In designing any software tool, it is important to formulate and adhere to a set of design principles. The philosophy behind the Spectrum simulation system is described by the design principles that follow. We argue generally for the importance of each principle, and describe lower-level design goals that follow naturally from them.

The design must be faithful to a formal model. Since our aim is to integrate theoretical modelling techniques with algorithm simulation, the simulation language and its semantics (as well as the implementation of the simulator) must remain faithful to the formal model. Any departure from the formal model jeopardizes effective integration of the two. For example, it is only possible to mechanically check executions of an algorithm against properties stated in the proof if the semantics of the simulation match the semantics of the model. By remaining faithful to a theoretical model, we also benefit from having a well-defined semantics on which to base the language and implementation. Of course, we must choose a sufficiently simple model so that the resulting language mechanisms encourage writing straightforward algorithm descriptions, and so that the resulting simulations are easily comprehended. This brings us to the next design principle.

The language should be natural for expressing a large class of distributed algorithms. This design principle has as much to do with the choice of a formal model on which the language is based, as it has to do with the design of particular programming language constructs. The inherent properties of distributed algorithms and systems lead us to the following specific requirements. The model and language should reflect the fact that processes in distributed systems generate outputs autonomously and may receive inputs at arbitrary times. Also, since distributed algorithms can be designed with many different communication assumptions, the system should provide support for varying these assumptions. Therefore, one should be able to model communication mechanisms explicitly. Many distributed algorithms make use of unbounded state, such as message counters or history information. In order not to rule out such algorithms, we require that the language allow processes to have infinite state sets (in principle). Finally, we require that the language have built-in data types and control flow mechanisms that are convenient for describing distributed algorithms.

The language and simulation system should encourage experimentation. Often, a researcher does not know exactly where to look for new insights, but discovers them through

1.2. DESIGN GOALS

a process of exploration and experimentation. It is important that a research tool facilitate this process. This principle implies a number of specific design goals:

- 1. The write/simulate/modify cycle should be short. That is, the length of time required to modify an algorithm and start the simulation should be small.

- 2. The language should provide mechanisms for modularity, so that algorithm components may be studied individually or replaced with other components. This modularity should have a hierarchical structure, so that simulations can be studied at different levels of detail. In addition, the system should support writing user-defined debugging and analysis tools as separate modules.

- 3. Logically independent concerns should be orthogonal. It should be possible to modify each of the following aspects of a simulation independently: the algorithm being studied, the system configuration, the control of visualization, and the mechanisms for debugging and analysis. Extraneous information for the configuration, visualization, and debugging should not clutter up the algorithm code or interfere with its execution.

- 4. User effort should be focused on experimenting with algorithms rather than finding obscure program errors. This means providing a statically type-checked language with a rich set of built-in data types.

- 5. Flexible mechanisms should be provided for controlling and studying executions. For example, the system should provide automatic detection of invariant violations, flexible and simple graphical mechanisms for configuring systems and controlling visualization, a choice of scheduling options, and the ability to go backward/forward in an execution and to generate a trace file.

In general, support for experimentation means that it should be easy to modify the algorithm and manipulate the simulation.

Finally, it is important to design for economy and integration. In general, a system is easier to build, learn, and use when a small set of tools provide all the necessary functionality. The main goal here is to use the same language mechanisms for writing programs, creating

debugging tools, specifying invariants, and setting up visualization. In addition, a single graphical interface should be used for both constructing the system configuration and controlling the simulation.

The above design principles are a concise description of the design philosophy for the Spectrum Simulation System. Their influence is evident in the Spectrum design. We will use these principles in Chapter 6 to evaluate Spectrum and compare it with related languages and systems.

At this point, we should say a few words to distinguish simulation systems from other kinds of software development tools. The purpose of a simulation system, and Spectrum in particular, is to generate executions of algorithms for study and analysis. The difference between a simulation system and an animation system, such as BALSA [10, 11], is subtle but important. In general, the purpose of an animation system is to teach an already well-understood algorithm to others. An animation system typically has two kinds of users, those who set up the animation and those who watch the animation in order to understand the algorithm. Animations are typically rather involved, are constructed by embedding extra procedure calls in the algorithm itself, and are often tailored to a particular algorithm execution or input. In a simulation system like Spectrum, the person setting up the visualization does not necessarily fully understand the algorithm. Since the purpose of the simulation system is to allow an algorithm designer to experiment with the algorithm in order to understand it more fully, we are not interested in fancy animation tricks that require special knowledge of the algorithm executions. We want visualization techniques that are simple enough to be set up quickly, general enough to accommodate any possible execution of the algorithm, and flexible enough to encourage experimentation. Also, as mentioned in our design goals, we want the visualization mechanisms to be clearly separated from the algorithm itself.

A simulation system is also not a theorem prover. A simulation system may be used to assist in program verification by checking properties of particular executions. However, it does not prove properties about all possible executions (as do theorem provers such as LP [21, 22] or Isabelle [52]), and it does not perform exhaustive search to check properties of all possible states (as does the Statemate system [26], which we will discuss later).

One final note of clarification is that we are primarily concerned with the simulation of complex asynchronous algorithms on a sequential machine, with an eye to understanding these algorithms and proving their correctness. A large amount of research has been done in the area of discrete event simulation, where the emphasis is on fast simulation of algorithms with real-time constraints in order to study their time performance. That research has emphasized improving simulation performance through concurrency. (For example, see Misra [49].) However, despite the difference in emphasis, some ideas from discrete event simulation are relevant to this thesis, particularly to Chapter 9 which addresses distributed simulation.

### 1.3 Thesis Overview

This thesis is divided into two parts. In the first part (Chapters 2 to 6), we present the Spectrum Simulation System, beginning with a review of its theoretical foundations and ending with an evaluation in terms of the design goals we have just stated. Motivated by this evaluation, the second part of the thesis (Chapters 7 to 9) proposes several extensions to the model and system. We now present a detailed overview of both parts of the thesis.

We have said that the Spectrum Simulation System is a research tool for the design and study of distributed algorithms expressed as collections of I/O automata. The tool consists of three main components, the programming language, the simulator, and the user interface. Central to the design of Spectrum is a clear separation of automaton types, which are the different kinds of components in an automaton system, and the configuration, which defines the number of instances of each of those types and the relationships among them. The programming language, defined in Chapter 3, provides constructs for describing distributed algorithms as I/O automaton types. The language provides constructs that support algorithm visualization and mechanical checking of state invariants. I/O automaton types are separately instantiated in order to form an automaton system configuration. The Spectrum simulator, described in Chapter 4, provides facilities for generating executions of these automaton systems. The graphical user interface, described in Chapter 5, is used both for defining the configuration and for controlling the simulation. Spectrum is written entirely in C [34] and runs on DEC Microvax workstations. The user interface is built on top of the X11 window system [56]. In Chapter 6, we conduct an evaluation of Spectrum using the design goals described in Section 1.2. In

that chapter, we draw comparisons with related languages and systems, and reflect upon the experiences of Spectrum users.

Motivated by the evaluation of Spectrum, Chapters 7 and 8 propose two extensions to the I/O automaton mcdel in order to express (and eventually simulate) a wider class of distributed algorithms. The first extension, shared memory, allows a collection of automata to make atomic accesses to shared variables. This extension results in a unified model for expressing two large classes of distributed algorithms (message-passing algorithms and shared memory algorithms), A complete assertional proof of Dijkstra's classical shared memory mutual exclusion algorithm [15] is presented to illustrate the shared memory definitions. Another way to model shared state in the I/O automaton model is to model the shared variables as I/O automata that respond to requests to access the variables. We present a general theorem that relates atomically accessed shared memory to the asynchronous invocation-response implementation. The second extension, superposition, allows one to describe an algorithm as a series of layers such that higher layers may observe the internal state of lower layers. Besides adding to the expressive power of the Spectrum language, this extension will be particularly useful for monitoring global state invariants during simulation. To illustrate the superposition definitions, the global snapshot algorithm of Chandy and Lamport [13] is presented with a complete proof of correctness. For both model extensions, corresponding language and simulation system extensions are proposed.

Most of the thesis is concerned with simulation of distributed algorithms on a single sequential machine. Distributing the simulation, besides being an interesting exercise in itself, can also reduce the simulation time. In Chapter 9, we define the logically synchronous multicast problem, which imposes a natural and useful structure on message delivery order in an asynchronous system. In this problem, a computation proceeds by a sequence of multicasts, in which a process sends a message to some arbitrary subset of the processes, including itself. A logically synchronous multicast protocol must make it appear to every process as if each multicast occurs simultaneously at all participants of that multicast (sender plus receivers). Furthermore, if a process continually wishes to send a message, it must eventually be permitted to do so. We present a highly concurrent solution to the logically synchronous multicast problem and describe how the logically synchronous multicast protocol can be used to distribute the simulation system. Related broadcast protocols are also discussed.

# Chapter 2

# The Model

The I/O Automaton model [47, 48] has been chosen as the foundation of the Spectrum Simulation System primarily because it is a natural model for describing distributed algorithms. Careful proofs using this model have been constructed using a variety of techniques for a wide range of algorithms (for examples, see [9, 19, 24, 41, 43, 45, 46, 47, 58, 59]). In this chapter, we present a review of the I/O automaton model adapted from [48]. Interested readers are referred to that paper for more details, motivation, examples, and results. In the course of presenting the model, we highlight those properties that help make the model a solid foundation for a distributed algorithm simulation system. The final sections of this chapter compare the I/O automaton model with related models and justify our selection of the I/O automaton model as formal framework for the Spectrum Simulation System. Further discussion of our choice of this model is contained in Chapter 6.

## 2.1 I/O Automata

I/O automata are best suited for modelling systems in which the components operate asynchronously. Each system component is modeled as an I/O automaton, which is essentially a nondeterministic (possibly infinite state) automaton with an action labeling each transition. An automaton's actions are classified as either 'input', 'output', or 'internal'. An automaton can establish restrictions on when it will perform an output or internal action, but it is unable to block the performance of an input action. An automaton is said to be closed if it has no

input actions; it models a closed system that does not interact with its environment.

Formally, an action signature S is a partition of a set acts(S) of actions into three disjoint sets in(S), out(S), and int(S) of input actions, output actions, and internal actions, respectively. We denote by  $ext(S) = in(S) \cup out(S)$  the set of external actions. We denote by  $local(S) = out(S) \cup int(S)$  the set of locally controlled actions. An I/O automaton A consists of five components:

- an action signature sig(A),

- a set states(A) of states,

- a nonempty set  $start(A) \subseteq states(A)$  of  $start\ states$ ,

- a transition relation  $steps(A) \subseteq states(A) \times acts(A) \times states(A)$  with the property that for every state s' and input action  $\pi$  there is a transition  $(s', \pi, s)$  in steps(A), and

- an equivalence relation part(A) partitioning the set local(A) into at most a countable number of equivalence classes.

The equivalence relation part(A) will be used in the definition of fair computation. Each class of the partition may be thought of as a separate process. We refer to an element  $(s', \pi, s)$  of steps(A) as a step of A. If  $(s', \pi, s)$  is a step of A, then  $\pi$  is said to be enabled in s'. Since every input action is enabled in every state, automata are said to be input-enabled. This means that an automaton is unable to block its input.

An execution of A is a finite sequence  $s_0, \pi_1, s_1, \ldots, \pi_n, s_n$  or an infinite sequence  $s_0, \pi_1, s_1, \pi_2, \ldots$  of alternating states and actions of A such that  $(s_i, \pi_{i+1}, s_{i+1})$  is a step of A for every i and  $s_0 \in start(A)$ . The schedule of an execution  $\alpha$  is the subsequence of  $\alpha$  consisting of the actions appearing in  $\alpha$ . The behavior of an execution or schedule  $\alpha$  of A is the subsequence of  $\alpha$  consisting of external actions. The sets of executions, finite executions, schedules, finite schedules, behaviors, and finite behaviors are denoted execs(A), finexecs(A), scheds(A), finscheds(A), behs(A), and finbehs(A), respectively. The same action may occur several times in an execution or a schedule; we refer to a particular occurrence of an action as an event.

2.2. COMPOSITION 25

## 2.2 Composition

We can construct an automaton modelling a complex system by composing automata modelling the simpler system components. When we compose a collection of automata, we identify an output action  $\pi$  of one automaton with the input action  $\pi$  of each automaton having  $\pi$  as an input action. Consequently, when one automaton having  $\pi$  as an output action performs  $\pi$ , all automata having  $\pi$  as an action perform  $\pi$  simultaneously (automata not having  $\pi$  as an action do nothing).

Since we require that at most one system component controls the performance of any given action, we must place some compatibility restrictions on the collections of automata that may be composed. A countable collection  $\{S_i\}_{i\in I}$  of action signatures is said to be strongly compatible if for all  $i, j \in I$  satisfying  $i \neq j$  we have

- 1.  $out(S_i) \cap out(S_j) = \emptyset$ ,

- 2.  $int(S_i) \cap acts(S_i) = \emptyset$ , and

- 3. no action is contained in infinitely many sets  $acts(S_i)$ .

We say that a collection of automata is strongly compatible if the corresponding collection of action signatures is strongly compatible.

The composition  $S = \prod_{i \in I} S_i$  of a countable collection of strongly compatible action signatures  $\{S_i\}_{i \in I}$  is defined to be the action signature with

- $in(S) = \bigcup_{i \in I} in(S_i) \bigcup_{i \in I} out(S_i),$

- $out(S) = \bigcup_{i \in I} out(S_i)$ , and

- $int(S) = \bigcup_{i \in I} int(S_i)$ .

The composition  $A = \prod_{i \in I} A_i$  of a countable collection of strongly compatible automata  $\{A_i\}_{i \in I}$  is the automaton defined as follows:

•

$$sig(A) = \prod_{i \in I} sig(A_i)$$

,

<sup>&</sup>lt;sup>1</sup>Here start(A) and states(A) are defined in terms of the ordinary Cartesian product, while sig(A) is defined in terms of the composition of action signatures just defined. Also, we use the notation s[i] to denote the *i*th component of the state vector  $\vec{s}$ .

- $states(A) = \prod_{i \in I} states(A_i),$

- $start(A) = \prod_{i \in I} start(A_i),$

- steps(A) is the set of triples  $(\vec{s_1}, \pi, \vec{s_2})$  such that, for all  $i \in I$ , if  $\pi \in acts(A_i)$  then  $(\vec{s_1}[i], \pi, \vec{s_2}[i]) \in steps(A_i)$ , and if  $\pi \notin acts(A_i)$  then  $\vec{s_1}[i] = \vec{s_2}[i]$ , and

- $part(A) = \bigcup_{i \in I} part(A_i)$ .

Given an execution  $\alpha = \vec{s_0}\pi_1\vec{s_1}\dots$  of A, let  $\alpha|A_i$  (read " $\alpha$  projected on  $A_i$ ") be the sequence obtained by deleting  $\pi_j\vec{s_j}$  when  $\pi_j \notin acts(A_i)$  and replacing the remaining  $\vec{s_j}$  by  $\vec{s_j}[i]$ .

### 2.3 Fairness

Of all the executions of an I/O automaton, we are primarily interested in the 'fair' executions — those that permit each of the automaton's primitive components (i.e., its classes or processes) to have infinitely many chances to perform output or internal actions. The definition of automaton composition says that an equivalence class of a component automaton becomes an equivalence class of a composition, and hence that composition retains the essential structure of the system's primitive components. In the model, therefore, being fair to each component means being fair to each equivalence class of locally controlled actions. A fair execution of an automaton A is defined to be an execution  $\alpha$  of A such that the following conditions hold for each class C of part(A):

- 1. If  $\alpha$  is finite, then no action of C is enabled in the final state of  $\alpha$ .

- 2. If  $\alpha$  is infinite, then either  $\alpha$  contains infinitely many events from C, or  $\alpha$  contains infinitely many occurrences of states in which no action of C is enabled.

We denote the set of fair executions of A by fairexecs(A). We say that  $\beta$  is a fair behavior of A if  $\beta$  is the behavior of a fair execution of A, and we denote the set of fair behaviors of A by fairbehs(A). Similarly,  $\beta$  is a fair schedule of A if  $\beta$  is the schedule of a fair execution of A, and we denote the set of fair schedules of A by fairscheds(A).

The definitions of composition and fairness imply certain natural relationships between the (fair) executions of a composition and the (fair) executions of the individual components. For

example, the following lemma from [48] states that (fair) executions of component automata can often be pasted together to form a (fair) execution of the composition.

Lemma 2.1: Let  $\{A_i\}_{i\in\mathcal{I}}$  be a strongly compatible collection of automata and let  $A=\prod_{i\in\mathcal{I}}A_i$ . Suppose  $\alpha_i$  is a (fair) execution of  $A_i$  for every  $i\in I$ , and suppose  $\beta$  is a sequence of actions in acts(A) such that  $\beta|A_i=sched(\alpha_i)$  for every  $i\in\mathcal{I}$ . Then there is an (fair) execution  $\alpha$  of A such that  $\beta=sched(\alpha)$  and  $\alpha_i=\alpha|A_i$  for every  $i\in\mathcal{I}$ . Moreover, the same result holds when acts and sched are replaced by ext and beh, respectively.

### 2.4 Problem Specification

A 'problem' to be solved by an I/O automaton is formalized as a set of (finite and infinite) sequences of external actions. An automaton is said to solve a problem P provided that its set of fair behaviors is a subset of P. Although the model does not allow an automaton to block its environment or eliminate undesirable inputs, we can formulate our problems (i.e., correctness conditions) to require that an automaton exhibits some behavior only when the environment observes certain restrictions on the production of inputs.

We want a problem specification to be an interface together with a set of behaviors. We therefore define a schedule module H to consist of two components, an action signature sig(H), and a set scheds(H) of schedules. Each schedule in scheds(H) is a finite or infinite sequence of actions of H. Subject to the same restrictions as automata, schedule modules may be composed to form other schedule modules. The resulting signature is defined as for automata, and the schedules scheds(H) is the set of sequences  $\beta$  of actions of H such that for every module H' in the composition,  $\beta|H'$  is a schedule of H'.

It is often the case that an automaton behaves correctly only in the context of certain restrictions on its input. A useful notion for discussing such restrictions is that of a module 'preserving' a property of behaviors. A set of sequences  $\mathcal{P}$  is said to be prefix-closed if  $\beta \in \mathcal{P}$  whenever both  $\beta$  is a prefix of  $\alpha$  and  $\alpha \in \mathcal{P}$ . A module M (either an automaton or schedule module) is said to be prefix-closed provided that finbehs(M) is prefix-closed. Let M be a prefix-closed module and let  $\mathcal{P}$  be a nonempty, prefix-closed set of sequences of actions from a set  $\Phi$  satisfying  $\Phi \cap int(M) = \emptyset$ . We say that M  $preserves \mathcal{P}$  if  $\beta \pi | \Phi \in \mathcal{P}$  whenever  $\beta | \Phi \in \mathcal{P}$ ,

$\pi \in out(M)$ , and  $\beta \pi | M \in finbehs(M)$ . Informally, a module preserves a property  $\mathcal{P}$  iff the module is not the first to violate  $\mathcal{P}$ : as long as the environment only provides inputs such that the cumulative behavior satisfies  $\mathcal{P}$ , the module will only perform outputs such that the cumulative behavior satisfies  $\mathcal{P}$ . One can prove that a composition preserves a property by showing that each of the component automata preserves the property.

#### 2.5 Alternative Models

The I/O automaton model is only one of a number of formal models that have been used for reasoning about concurrent systems. A review of alternative models, with an emphasis on techniques for proving algorithm correctness, is contained in [47]. But one's choice of a formal model not only influences the way in which one reasons about algorithms, but also has a strong influence on the way in which one describes algorithms, and particularly the ease with which this is done. Therefore, as we stated in our design goals for the Spectrum Simulation System, it is important to be sure that one chooses a formal model that is natural for expressing the class of algorithms one wishes to describe. In this section, we briefly describe three popular formal models that have been used for describing distributed systems: CSP [31], Unity [14] and Statecharts [27, 28]. In the course of this discussion, we highlight those differences in expressive power that led us to choose the I/O automaton model as the basis of the Spectrum Simulation System. Here, we discuss only the formal models. We will discuss related programming languages and systems in our evaluation of Spectrum in Chapter 6.

#### 2.5.1 CSP

Hoare's Communicating Sequential Processes (CSP) [31] is a close relative of the I/O automaton model. A CSP program consists of a set of processes written as sequential programs. Each program may contain statements that attempt to send or receive data over channels connected to other processes. The channels are synchronous, meaning that the data transfer occurs simultaneously at both ends of the channel, only after both the sender and the receiver are at the appropriate points in their programs. Thus, unlike in the I/O automaton model, a process that is not prepared to receive data may block a process that is prepared to send the data. This

makes CSP unnatural for describing systems in which the individual processes are autonomous.

Many distributed algorithms have the property that different processes in a system may be at completely different points in the execution of their protocols. In such algorithms, a process typically must be able to service requests from other processes (such as a request for a resource) at any time. Thus, describing a component in a distributed system as a single sequential thread of control is rather awkward, since this sequential thread must continually "poll" its incoming channels for such requests. Partially addressing this problem, CSP provides a language construct that allows a process to attempt to send or receive data over multiple channels at a given point in its program; whichever of these data transfers succeeds first is the one executed. This is a powerful construct, but its inherent synchrony does not fit well with the properties of a distributed system. The nondeterministic control flow and input-enabling property of I/O automata combine to provide a more suitable mechanism for expressing this kind of distributed algorithm.

In Chapter 6, we will discuss the Occam programming language [32, 53] based on CSP.

#### 2.5.2 UNITY

Another programming model, UNITY (which stands for Unbounded Nondeterministic Iterative Transformations) [14], abandons the sequential control flow of CSP in favor of nondeterministic choice. A UNITY program consists of a set of statements that access a global shared memory. At each step in the (infinite) execution, a statement is selected and executed. Schedules are constrained to be fair, meaning that each statement is executed infinitely often. One may think of each statement as a separate process, which is given fair turns to take steps. Since UNITY programs do not terminate, the notion of algorithm termination is defined in terms of a fixed point in the execution, after which no statements cause state changes. The UNITY model has a programming logic that is useful for constructing rigorous correctness proofs of algorithms.