#### **PRO-DASP**

Power Reduction for Digital Audio Signal Processing

Using Transformations to Implement Hardware-Macros for a Low Power Design Methodology

Nikolaus Voß and Bärbel Mertsching

Prof. Wolfgang Nebel, Prof. Bärbel Mertsching, Prof. Birger Kollmeier

- 1. Macro-Module Library for Audio-Processing

- 2. Power-Reduction Strategy

- 3. Design-Flow

- 4. Module-Hierarchy

- 5. Examples (Module and Algorithm)

- 6. Conclusion

#### **Audio Signal Processing**

- Filters are the Central Concept of Signal Processing

- Two main mathematical principles: FIR & IIR

TVA-Kolloquium 2002

Universität Hambu

#### Library

Audio algorithms can be partitioned to a set of filters

=> Library approach is sensible

#### Macro-Library

#### Design-goals:

- 1. Technology independence

- => Low-level (automatic) optimization possible

- => Extensive applicability (technology, size)

- 2. High level of optimization

- 3. Easy useability

- => Development of a software-framework

VIVA-Kolloquium 2002

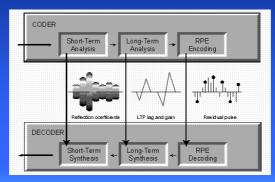

### Audio Filter Example: GSM-Compression 1

GSM 06.10 audio compressor model for human speech

Universität OLDENBURG

VIVA-Kolloquium 2002

#### **GSM** Compression 2

- Two filters: 1. Short term prediction 2. Long term prediction

- Exploits correlation in speech to reduce data-rate

- Implemented in every cellular phone

- 3G: advanced compression scheme

OSSITE OLDENBURG

VIVA-Kolloquium 2002

- 1. Macro-Module Library for Audio-Processing

- 2. Power-Reduction Strategy

- 3. Design-Flow

- 4. Module-Hierarchy

- 5. Examples (Module and Algorithm)

- 6. Conclusion

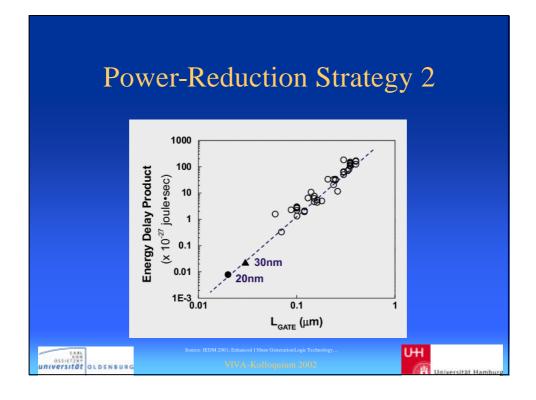

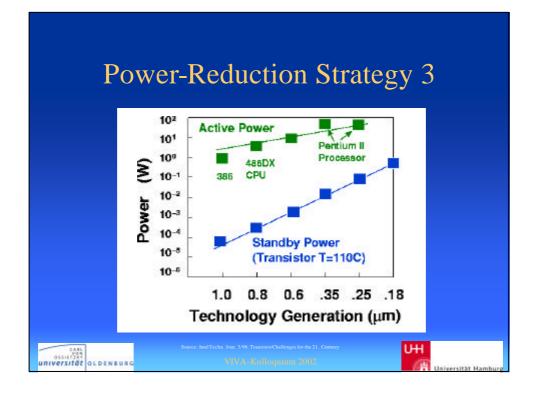

#### Power-Reduction Strategy 1

- Two trends related to Moore's Law:

- Reduction of energy-delay product

- Standby-power is becoming more important

OSSILIZAT Universität OLDENBURG

IVA-Kolloguium 2002

#### Power-Reduction Strategy 4

#### Reason:

As Supply Voltages become smaller, the relative Gate-Overdrive has to be reduced as the delay depends on the gate-overdrive

For modern technologies, Vdd-Reduction is limited due to relatively high gate-delay for smaller Voltages

OSSIGNATION DENBURG

#### Power-Reduction Strategy 5

#### Consequence for PRO-DASP:

Reduction of switched capacitance by exploiting locality (modularisation, library approach)

VIVA-Kolloquium 2002

- 1. Macro-Module Library for Audio-Processing

- 2. Power-Reduction Strategy

- 3. Design-Flow

- 4. Module-Hierarchy

- 5. Examples (Module and Algorithm)

- 6. Conclusion

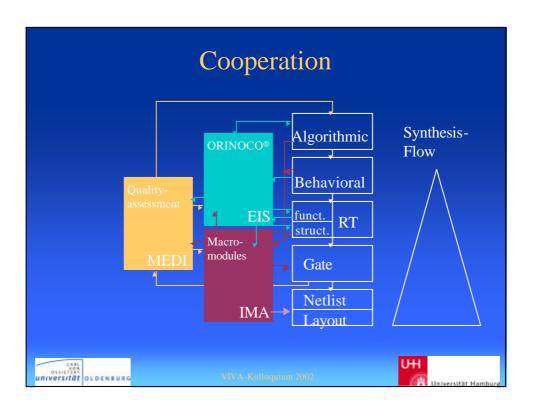

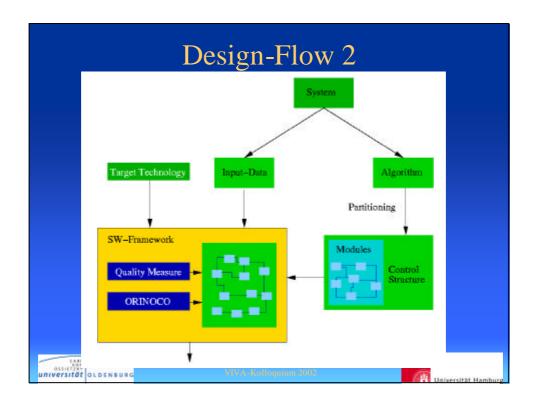

#### Design-Flow 1

- Partitioning of algorithm to modules

- Heuristical/probabilistical refinement

- Quality assurance via MEDI testbench

- Further optimization through ORINOCO

- Optimization through compiler/back-end tools

VIVA-Kolloquium 2002

#### Structure

- 1. Macro-Module Library for Audio-Processing

- 2. Power-Reduction Strategy

- 3. Design-Flow

- 4. Module-Hierarchy

- 5. Examples (Module and Algorithm)

- 6. Conclusion

OSSICIZATI Universität OLDENBURG

VIVA-Kolloquium 2002

#### Module-Hierarchy 1

- Two-level approach:

- Low-level modules for number systems and number representation

- High-level modules for actual filter architecture

- "Glue-layers"

#### Module-Hierarchy 2 Low-Power Macro-Module Library Level of Abstraction Filter High-Level Number System / Arch. of Arithm. Number Repres. Architecture Filter-Interface Operators Twos-Compl. FIR direct FIR Ripple IIR direct IIR Signed Magnitude CLA LNS CSA DCM Fourier Transf. RNS DECOR Adaptive Array Floating-Point Baugh-Wooley DAT Booth SMT Wallache Tree Radix-n-FFT UΗ universität OLDENBURG

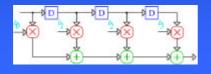

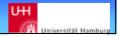

#### Example-Module: DECOR 1

- DECoRrelation transform: exploitation redundancy of coefficients to reduce strength of multiplication by only multiplying differences of coefficients (cf. DCM)

- Mathmatically a multiplication of the Z-transfer-function with unity

OSSILIZAT Universität OLDENBURG

/IVA-Kolloguium 2002

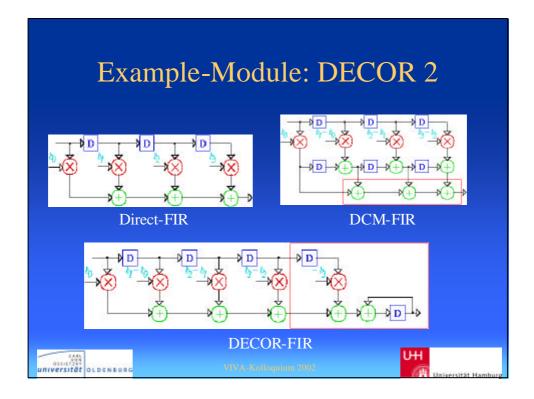

## Example-Module: DECOR 3 $V(z) = H(z)^{(1+az^{-b})^m} V(z)$

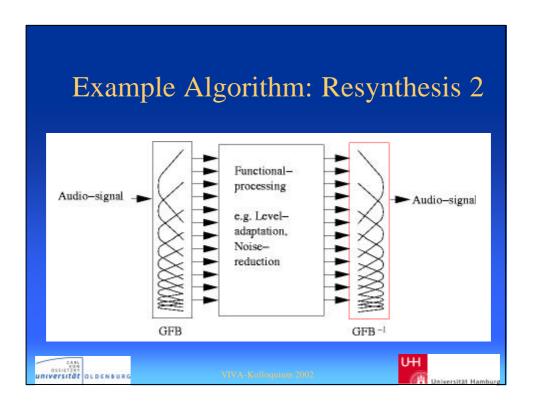

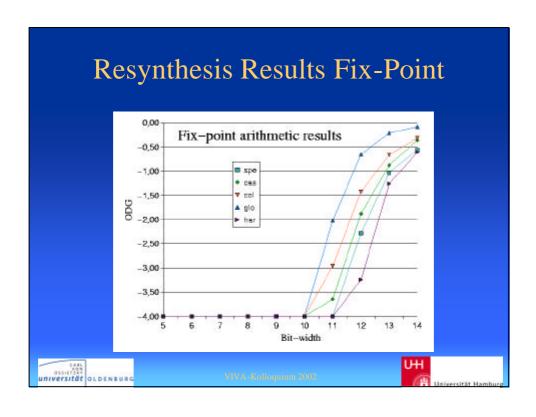

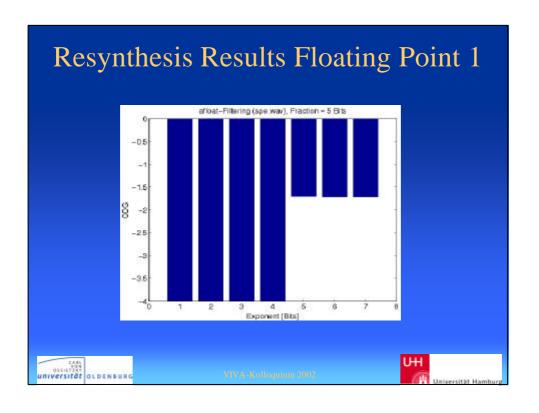

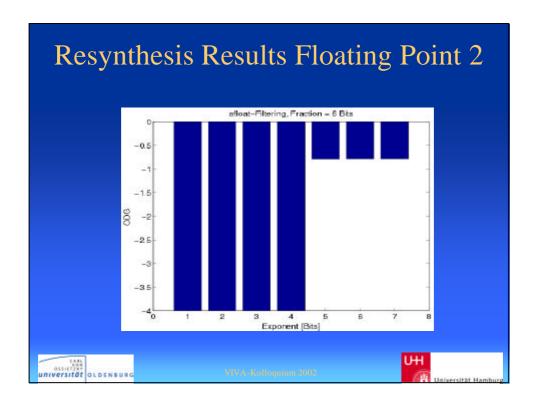

#### Example Algorithm: Resynthesis 1

- Gammatone-resynthesis is used as pre and post-Processing for audio algorithms

- Set of band-pass filters, frequency selection is approximation of basilar membrane filtering of inner ear

# Resynthesis Results Floating Point 3 afloat-Filtering for various Samples -0.5 Snapper 5 Cembalo Coleman Cembalo Sample resp Exponent-Bits WMA Kolloquium 2002

- 1. Macro-Module Library for Audio-Processing

- 2. Power-Reduction Strategy

- 3. Design-Flow

- 4. Module-Hierarchy

- 5. Examples (Module and Algorithm)

- 6. Conclusion

#### Conclusion

- Modularization is a sensible approach

- Energy savings for modern technologies

- Audio algorithms are easily partitioned to modules

- Modules can be optimized by external tools

OSSILIZAT UNIVERSITÄT OLDENBURG

VIVA-Kolloquium 2002

#### Conclusion

- Modules are embedded into a SW-frame

- Application of probablistic/heuristic methods for selection and optimization of modules

- Exploration of a multi-dimensional solution space possible

#### Conclusion

• Independent of target technology through focusing on algorithmic level (in contrast to existing high-level tools like HYPER-LP)

/IVA-Kolloquium 2002

#### Outlook

- Integration of probabilistic/heuristic methods for module selection

- Automatic generation of VHDL hardware description in SW-FW

- VLSI chip-design for example algorithm